(经典)集电极开路,漏极开路,推挽,上拉电阻,弱上拉,三态门,准双向口

(经典)集电极开路,漏极开路,推挽,上拉电阻,弱上拉,三态门,准双向口

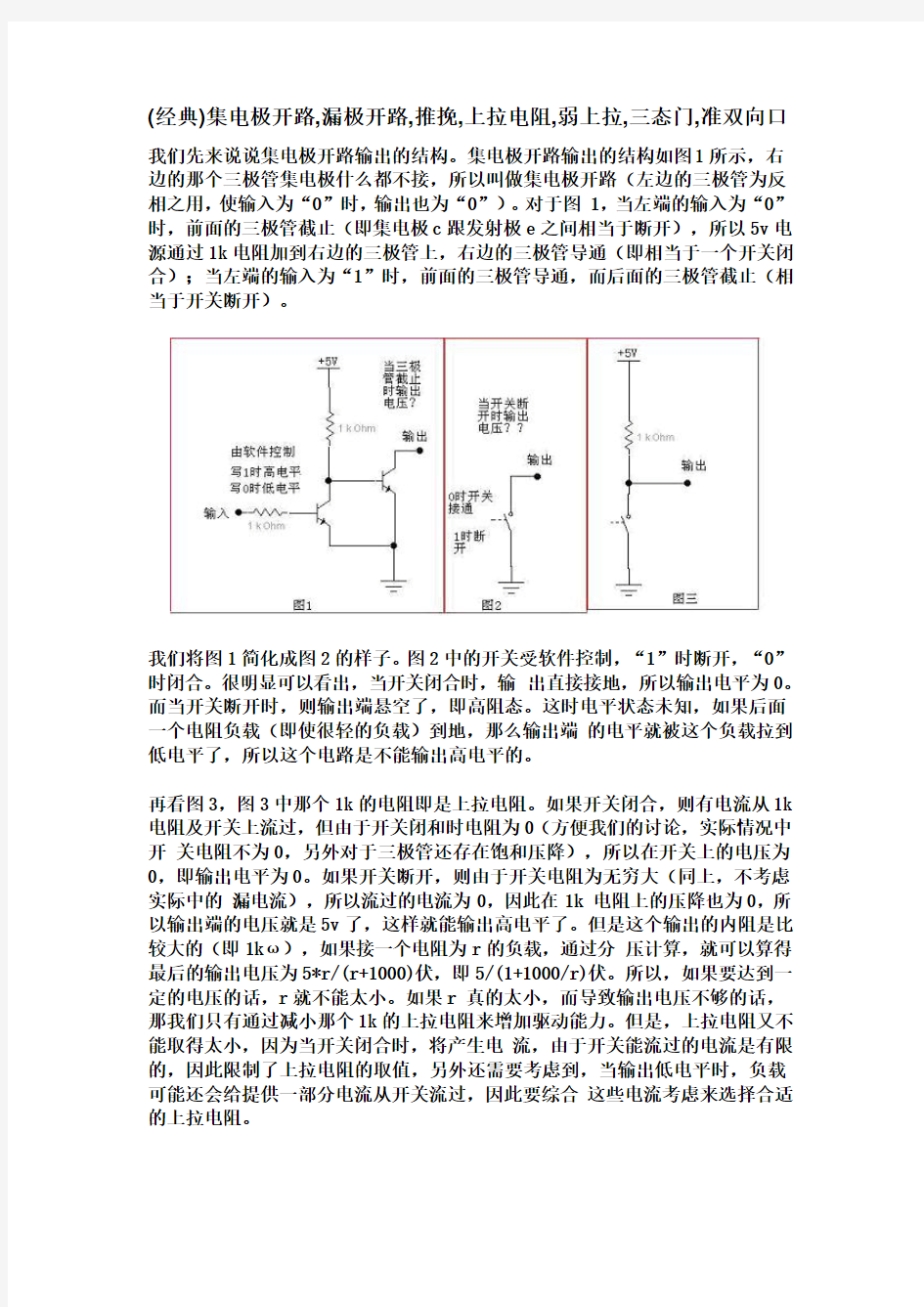

我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为“0”时,输出也为“0”)。对于图 1,当左端的输入为“0”时,前面的三极管截止(即集电极c跟发射极e之间相当于断开),所以5v电源通过1k电阻加到右边的三极管上,右边的三极管导通(即相当于一个开关闭合);当左端的输入为“1”时,前面的三极管导通,而后面的三极管截止(相当于开关断开)。

我们将图1简化成图2的样子。图2中的开关受软件控制,“1”时断开,“0”时闭合。很明显可以看出,当开关闭合时,输出直接接地,所以输出电平为0。而当开关断开时,则输出端悬空了,即高阻态。这时电平状态未知,如果后面一个电阻负载(即使很轻的负载)到地,那么输出端的电平就被这个负载拉到低电平了,所以这个电路是不能输出高电平的。

再看图3,图3中那个1k的电阻即是上拉电阻。如果开关闭合,则有电流从1k 电阻及开关上流过,但由于开关闭和时电阻为0(方便我们的讨论,实际情况中开关电阻不为0,另外对于三极管还存在饱和压降),所以在开关上的电压为0,即输出电平为0。如果开关断开,则由于开关电阻为无穷大(同上,不考虑实际中的漏电流),所以流过的电流为0,因此在1k 电阻上的压降也为0,所以输出端的电压就是5v了,这样就能输出高电平了。但是这个输出的内阻是比较大的(即1kω),如果接一个电阻为r的负载,通过分压计算,就可以算得最后的输出电压为5*r/(r+1000)伏,即5/(1+1000/r)伏。所以,如果要达到一定的电压的话,r就不能太小。如果r 真的太小,而导致输出电压不够的话,那我们只有通过减小那个1k的上拉电阻来增加驱动能力。但是,上拉电阻又不能取得太小,因为当开关闭合时,将产生电流,由于开关能流过的电流是有限的,因此限制了上拉电阻的取值,另外还需要考虑到,当输出低电平时,负载可能还会给提供一部分电流从开关流过,因此要综合这些电流考虑来选择合适的上拉电阻。

如果我们将一个读数据用的输入端接在输出端,这样就是一个io口了(51的

io口就是这样的结构,其中p0口内部不带上拉,而其它三个口带内部上拉),当我们要使用输入功能时,只要将输出口设置为1即可,这样就相当于那个开关断开,而对于p0口来说,就是高阻态了。

对于漏极开路(od)输出,跟集电极开路输出是十分类似的。将上面的三极管换成场效应管即可。这样集电极就变成了漏极,oc就变成了od,原理分析是一样的。

另一种输出结构是推挽输出。推挽输出的结构就是把上面的上拉电阻也换成一个开关,当要输出高电平时,上面的开关通,下面的开关断;而要输出低电平时,则刚好相反。比起oc或者od来说,这样的推挽结构高、低电平驱动能力都很强。如果两个输出不同电平的输出口接在一起的话,就会产生很大的电流,有可能将输出口烧坏。而上面说的oc或od输出则不会有这样的情况,因为上拉电阻提供的电流比较小。如果是推挽输出的要设置为高阻态时,则两个开关必须同时断开(或者在输出口上使用一个传输门),这样可作为输入状态,avr 单片机的一些io 口就是这种结构。

---------------------------------------------------------------------------

单片机内部的逻辑经过内部的逻辑运算后需要输出到外面,外面的器件可能需要较大的电流才能推动,因此在单片机的输出端口必须有一个驱动电路。这种驱动电路有两种形式:

其中的一种是采用一只N型三极管(npn或n沟道),以npn三极管为例,就是e接地,b接内部的逻辑运算,c引出,b受内部驱动可以控制三极管是否导通但如果三极管的c极一直悬空,尽管b极上发生高低变化,c极上也不会有高低变化,因此在这种条件下必须在外部提供一个电阻,电阻的一端接c(引出脚)另一端接电源,这样当三极管的b有高电压是三极管导通,c电压为低,当b为低电压时三极管不通,c极在电阻的拉动下为高电压,这种驱动电路有个特点:低电压是三极管驱动的,高电压是电阻驱动的(上下不对称),三极管导通时的ec内阻很小,因此可以提供很大的电流,可以直接驱动led甚至继电器,但电阻的驱动是有限的,最大高电平输出电流=(vcc-Vh)/r;

另一种是互补推挽输出,采用2只晶体管,一只在上一只在下,上面的一只是n 型,下面为p型(以三极管为例),两只管子的连接为:npn(上)的c连 vcc,pnp(下)的c接地,两只管子的ee,bb相连,其中ee作为输出(引出脚),bb接内部逻辑,这个电路通常用于功率放大点路的末级(音响),当bb接高电压时npn管导通输出高电压,由于三极管的ec电阻很小,因此输出的高电压有很强的驱动能力,当bb接低电压时npn截至,pnp导通,由于三极管的ec 电阻很小因此输出的低电压有很强的驱动能力,简单的例子,9013导通时ec电阻不到10欧,以Vh=2.5v,vcc=5v计算,高电平输出电流最大=250MA,短路电流500ma,这个计算同时告诉我们采用推挽输出时一定要小心千万不要出现外部电路短路的可能,否则肯定烧毁芯片,特别是外部驱动三极管时别忘了在三极管的基极加限流电阻。推挽输出电路的形式很多,有些单片机上下都采用n

型管,但内部逻辑提供互补输出,以上的说明仅仅为了说明推挽的原理,为了更深的理解可以参考功率放大电路。

---------------------------------------------------------------------------

集电极开路门(集电极开路OC或源极开路OD)

漏极开路输出相当于集电极开路输出。漏极开路是对mos管而言,集电极开路是对三极型管而言。一般用于线或、线与、电流驱动,匹配电平。

开漏形式的电路有以下几个特点:

1.利用外部电路的驱动能力,减少IC内部的驱动,或驱动比芯片电源电压高的负载。

2.可以将多个开漏输出的Pin,连接到一条线上。通过一只上拉电阻,在不增加任何器件的情况下,形成“与逻辑”关系。这也是I2C,SMBus等总线判断总线占用状态的原理。

3.由于漏级开路,所以后级电路必须接一上拉电阻,上拉电阻的电源电压就可以决定输出电平。这样就可以进行任意电平的转换了。

4.源极开路提供了灵活的输出方式,但是也有其弱点,就是带来上升沿的延时。因为上升沿是通过外接上拉无源电阻对负载充电,所以当电阻选择小时延时就小,但功耗大;反之延时大功耗小。所以如果对延时有要求,则建议用下降沿输出。

---------------------------------------------------------------------------

上拉电阻很大,提供的驱动电流很小,叫弱上拉;反之叫强上拉。

---------------------------------------------------------------------------

OC门,又称集电极开路(漏极开路)与非门门电路,Open Collector(Open Drain)。为什么引入OC门?实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态电平)用同一条导线输送出去。因此,需要一种新的与非门电路--OC门来实现“线与逻辑”。OC门主要用于3个方面:实现与或非逻辑,用做电平转换,用做驱动器。由于OC门电路的输出管的集电极悬空,使用时需外接一个上拉电阻Rp到电源VCC。OC门使用上拉电阻以输出高电平,此外为了加大输出引脚的驱动能力,上拉电阻阻值的选择原则,从降低功耗及芯片的灌电流能力考虑应当足够大;从确保足够的驱动电流考虑应当足够小。

为什么要使用拉电阻:

上拉就是将不确定的信号通过一个电阻嵌位在高电平,电阻同时起限流作用。下拉同理。

上拉是对器件注入电流,下拉是输出电流,弱强只是上拉电阻的阻值不同,没有什么严格区分。

对于非集电极(或漏极)开路输出型电路(如普通门电路)提升电流和电压的

能力是有限的,上拉电阻的功能主要是为集电极开路输出型电路输出电流通道。

上拉电阻应用:

1、当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS 电路的最低高电平(一般为3.5V),这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。

2、OC门电路要输出“1”时才需要加上拉电阻,不加根本就没有高电平。

3、为加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻,但在有时用OC门作驱动(例如:控制一个LED)灌电流工作时就可以不加上拉电阻。或者说:对于非集电极(或漏极)开路输出型电路(如普通门电路)提升电流和电压的能力是有限的,上拉电阻的功能主要是为集电极开路输出型电路输出电流通道。

4、在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗,提供泄荷通路。

5、提高总线的抗电磁干扰能力。管脚悬空就比较容易接受外界的电磁干扰。

6、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

上拉电阻阻值的选择原则包括:

1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。

2、从确保足够的驱动电流考虑应当足够小;电阻小,电流大。

3、对于高速电路,过大的上拉电阻可能边沿变平缓。

综合考虑以上三点,通常在1k到10k之间选取。对下拉电阻也有类似道理。

---------------------------------------------------------------------------

高阻态时引脚对地电阻无穷,此时读引脚电平时可以读到真实的电平值。高阻态的重要作用就是I/O(输入/输出)口在输入时读入外部电平用。

一般门与其它电路的连接,无非是两种状态,1或者0,在比较复杂的系统中,为了能在一条传输线上传送不同部件的信号,研制了相应的逻辑器件称为三态门三态门,除了有这两种状态以外还有一个高阻态,就是高阻抗(电阻很大,相当于开路)。相当于该门和它连接的电路处于断开的状态。三态门是一种扩展逻辑功能的输出级,也是一种控制开关。主要是用于总线的连接,因为总线只允许同时只有一个使用者。通常在数据总线上接有多个器件,每个器件通过OE/CE之类的信号选通。如器件没有选通的话它就处于高阻态,相当于没有接在总线上,不影响其它器件的工作。

---------------------------------------------------------------------------

准双向口只能有效的读取0,而对1则是采用读取非零的方式,就是读入的时候要先向io上写1,再读。

真正的双向口正如其名,就是真正的双向io不需要任何预操作可直接读入读出。三态io的读入没有区别,只是输出带三态。

上拉,三态门,准双向口

集电极开路输出

集电极开路输出 我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为“ 0”时,输出也为“ 0”)。对于图1,当左端的输入为“0”时,前面的三极管截止(即集电极c跟发射极e之间相当于断开),所以5v 电源通过1k电阻加到右边的三极管上,右边的三极管导通(即相当于一个开关闭合);当左端的输入为“ T时,前面的三极管导通,而后面的三极管截止(相当于开关断开)。 我们将图1简化成图2的样子。图2中的开关受软件控制,“ 1”时断开,“0”时闭合。很明显可以看出,当开关闭合时,输出直接接地,所以输出电平为0。而当开关断开时,则输出端悬空了,即高阻态。这时电平状态未知,如果后面一个电阻负载(即使很轻的负载)到地,那么输出端的电平就被这个负载拉到低电平了,所以这个电路是不能输出高电平的。 再看图三。图三中那个1k的电阻即是上拉电阻。如果开关闭合,贝U有电流从1k电阻及开关上流过,但由于开关闭和时电阻为0 (方便我们的讨论,实际情况中开关电阻不为0,另外对于三极管还存在饱和压降),所以在开关上的电压为0,即输出电平为0。如果开关断开,则由于开关电阻为无穷大(同上,不考虑实际中的漏电流),所以流过的电流为0,因此在1k电阻上的压降也为0, 所以输出端的电压就是5v 了,这样就能输出高电平了。但是这个输出的内阻是比较大的(即1k?),如果接一个电阻为r的负载,通过分压计算,就可以算得最后的输出电压为5*r/(r+1000)伏,即5/(1+1000/r)伏。所以,如果要达到一定的电压的话,r就不能太小。如果r真的太小,而导致输出电压不够的话,那我们只有通过减小那个1k的上拉电阻来增加驱动能力。但是,上拉电阻又不能取得太小,因为当开关闭合时,将产生电流,由于开关能流过的电流是有限的,因此限制了上拉电阻的取值,另外还需要考虑到,当输出低电平时,负载可能还会给提供一部分电流从开关流过,因此要综合这些电流考虑来选择合适的上拉电阻。 如果我们将一个读数据用的输入端接在输出端,这样就是一个io 口了(51的io 口就是这样的结构,其中p0 口内部不带上拉,而其它三个口带内部上拉),当我们要使用输入功能时,只要将输出口设置为1即可,这样就相当于那个开关断开,而对于p0 口来说,就是高阻态了。 对于漏极开路(od)输出,跟集电极开路输出是十分类似的。将上面的三极管换成场效应管即可。这样集电极就变成了漏极,oc就变成了od,原理 分析是一样的。 另一种输出结构是推挽输出。推挽输出的结构就是把上面的上拉电阻也换成一个开关,当要输出高电平时,上面的开关通,下面的开关断;而要输出低电平时,则刚好相反。比起oc或者od来说,这样的推挽结构高、低电平驱动能力都很强。如果两个输出不同电平的输出口接在一起的话,就会产生很大的电流,有可能将输出口烧坏。而上面说的oc或od输出则不会有这样的情况,因为上拉电阻提供的电流比较小。如果是推挽输出的要设置为高阻态时,则两个开关必须同时断开 (或者在输出口上使用一个传输门),这样可作为输入状态,avr单片机的一些

(完整word版)巧用电阻等效法“秒杀”一类变压器问题

巧用电阻等效法“秒杀”一类变压器问题 2014年新课标高考考纲中知识点“理想变压器”由“Ⅰ”级要求变为 “Ⅱ”级要求后,近两年高考中变压器问题在考查的难度上有所增加,有一类这样的问题在高考中频频出现,那就是在变压器原线圈中串入电阻,使问题变的很复杂,如果用常规解法,计算量很大,令学生感到望而生畏.笔者在教学研究中发现这类问题如果用电阻等效法进行计算,能降低难度,使问题简单明了,实现“秒杀“这类问题.下面就理想变压器等效负载电阻公式的推导和应用做以分析. 一、变压器等效负载电阻公式的推导 设理想变压器原、副线圈的匝数分别为1n 、2n ,原、 副线圈电压分别为1U 、2U ,副线圈负载电阻为R ,如 图(a )所示,在变压器正常工作时,我们分析一下a 、 b 间的等效电阻. 先画出等效电路图如图1(b )所示,设变压器等效负载电阻为R ',在图1(a )中由变压器的电压规律:2121n n U U = 解得:U n n U 221 1=, 所以负载电阻R 消耗的功率为:R n U n R U P 212122 22== 在图1(b )中等效电阻消耗的功率为:P U R ''=12 有P P '=,解得a 、b 间的等效电阻为:R n n R '=1 222 通过以上的分析可知:在只有一个副线圈的理想变压器电路中,原线圈的匝数为1n ,副线圈的匝数为2n ,副线圈负载电阻为R ,则变压器的原、副线和负载电阻可以等效为一个电阻R n n R '=1 222,这个方法叫理想变压器电阻等效法.下面举例说明一下这个方法的应用.

二、电阻等效法的应用 例1 (2016年全国1理综)一含有理想变压器的电路如图所示,图中电阻R 1,R 2和R 3的阻值分别为3Ω ,1Ω ,4Ω ,为理想交流电流表,U 为正弦交流电压源,输出电压的有效值恒定.当开关S 断开时,电流表的示数为I ;当S 闭合时,电流表的示数为4I .该变压器原、副线圈匝数比 为 A.2 B.3 C.4 D.5 解析 设原、副线圈的匝数比为k,当开关S 断开时,负载等效电阻为()322R R k R += 根据欧姆定律()() []32211R R k R I R R I U ++=+= 当开关S 闭合时,负载等效电阻为22R k R =' 根据欧姆定律()() 221144R k R I R R I U +='+= 联立以上两式解得3=k . 点评 本题如果用常规解法就需要根据原、副线圈电压和电流比与匝数比的关系将副线圈中的电流和电压都用原线圈的电流和电压来表示,然后根据电压U 不变,列方程求出副 线圈匝数之比,这种解法运算量较大;但如果用 电阻等效法就会非常简单. 例2 (2015年全国新课标I 卷)理想变压器的 原、副线圈的匝数比为3 :1,在原、副线圈的回 路中分别接有阻值相同的电阻,原线圈一侧接有电压为220V 的正弦交流电源上,如图所示,设副线圈回路中电阻两端的电压为U ,原、副线圈回路中电阻消耗的功率之比为k ,则 A .U=66V ,k=1/9 B . U=22V ,k=1/9 C .U=66V ,k=1/3 D . U=22V ,k=1/3 解析 根据电阻等效法原、副线圈和负载电阻的等效电阻:

集电极开路门与三态输出门的应用

实验 4 集电极开路门与三态输出门的应用 实验目的 1. 掌握 TTL 集电极开路(OC)门的逻辑功能及应用。 2. 掌握 TTL 三态(3S)输出门的逻辑功能及应用。 实验仪器设备与元器件 1.硬件基础电路实验箱,双踪示波器,数字万用表。 2.74LS00,74LS03,CC4011,74LS125 各一块。 实验概述 1.TTL 集电极开路门 图1.4-1所示是一个TTL 二输入集电极开路与非门的逻辑符号和内部电路。 OC 门的使用方法如下: (1) 利用OC 门“线与”特性完成特定逻辑功能。 图1.4.2所示,输出端实现了线与的逻辑功能: 若有一个门的输出为低电平,则F 输出为低,当所有门的输出为高电平,F 输出为高,即在输出端实现了线与的逻辑功能。 (2) 利用OC 门可实现逻辑电平的转换 改变上拉电阻R L 的电源V L 的电压,输出端的逻辑电平会跟V L 改变。不同电平的逻辑电

路可以用OC 门连接。 (3) OC 门用于驱动 OC 门的输出电流较大,可驱动工作电流较大的电子器件。图1.4.3所示是用OC 门驱动发光二级管的低电平驱动电路。 3. TTL 三态门图1. 4.4所示为三态门的逻辑符号和内部结构图,控制端为低有效。 实验内容 1. OC 门的特性及其应用 (1) 参考图1.4.2,用OC 门74LS03验证 OC 门的“线与”功能。R L 为1k Ω时,写出输出F 的表 达式,观测输出与输入信号的逻辑关系,将数据填入自制表格中。 (2) 参考图1.4.7, 验证OC 门74LS03的特性,输入A 、B 接逻辑电平输出信号,输出端Y 接直流电 压表。V L 接+5V,电阻R L 为4.7k, 观测输出与输入信号的逻辑关系,如果去掉R L , 观测输出信号 的变化。V L 改接+15V , 检测输出信号的高电平和低电平电压。 (3) 参考图1.4-8,用OC 门74LS03驱动COMS 电路与非门CD4011,V L 接+5V ,调节电位器R w ,

实验四TTL集电极开路门和三态输出门测试_图文(精)

实验四 TTL 集电极开路门和三态输出门测试 一、实验目的 1 、掌握 TTL 集电极开路门 (OC 门的逻辑功能及应用。 2 、了解集电极负载电阻 RL 对集电极开路门的影响。 3 、掌握 TTL 三态输出门 (3S 门的逻辑功能及冈山。 二、实验原理 数字系统中有时需要把两个或两个以上集成逻辑门的输出端直接并接在一起完成一定的逻辑功能。对于普通的 TTL 电路 , 由于输出级采用了推拉式输出电路 , 无论输出是高电平还是低电平 , 输出阻抗都很低。因此 , 通常不允许将它们的输出端并接在一起使用 , 而集电极开路门和三态输出门是两种特殊的 TTL 门电路 , 它们允许把输出端直接并按在一起使用 , 也就是说 , 它们都具有 " 线与 " 的功能。 1 、 TTL 集电极开路门 (OC 门 本实验所用 OC 门型号为 2 输入四与非门 74LS03, 引脚排列见附录。工作时 , 输出端必须通过一只外接电阻 RL 和电源 Ec 相连接 , 以保证输出电平符合电路要求。 OC 门的应用主要有下述三个方面 : (l 电路的 " 线与 " 特性方便的完成某些特定的逻辑功能。图4 · l 所示 , 将两个 OC 门输出端直接并接在一起 , 则它们的输出 F=FA·FB=A1A2·B1B2 =A1A2+B1B2 图 4-1 0C 与非门 " 线与 " 电路图 4-2 0C 与非门负载电阻 RL 的确定 即把两个 ( 或两个以上〉 OC 与非门 " 线与 " 可完成 " 与或非 " 的逻辑功能。 (2 实现多路信息采集 , 使两路以上的信息共用一个传输通道 ( 总线。

(3 实现逻辑电平转换 , 以推动荧光数码管、继电器、 MOS 器件等多种数字集成电路。 OC 门输出并联运用时负载电阻 RL 的选择 : 如图 43 所示 , 电路由 n 个 OC 与非门 " 线与 " 驱动有 m 个输入端的 N 个 TTL 与 1Hl, 为保证 OC 门输出电平符合逻辑要求 , 负载屯阻 RI 阻值的选抨范围为: 式中 :IOH 一一 -OC 门输出管截止时 ( 输出高电平 VOEf 〉的漏电流〈约为 50uA ILM 一一一 OC 门输出低电平 VOL 时允许最大灌入负载电流 ( 约为 2OmA ItH 一一 -负载门高电平输入电流 (<5011A Itl, 一一负载门低电平输入电流 (<1.6mA Ec 一 -RL 外接电源电压 n 一一 OC 门个数 N 一一负载门个数 M 一一接入电路的负载门输入端总个数 RL 值须小于 RLmax, 否则 VOEt 将下降 ,RL 值须大于 RLmiI1, 否则 VOL 将上升 , 又 RL 的大小会影响输出波形的边沿时间 , 在工作速度较高时 ,RL 应尽量选取接近 RIAin 。 2 、 TTL 三态输出门 (3S 门

浅谈等效电阻的几种求法

万方数据

浅谈等效电阻的几种求法 作者:钱来富 作者单位:江苏泰兴市职业教育中心校电工电子教研室 刊名: 中国科技信息 英文刊名:CHINA SCIENCE AND TECHNOLOGY INFORMATION 年,卷(期):2005(24) 本文读者也读过(10条) 1.张成亮.卢振亮.ZHANG Cheng-liang.LU Zhen-liang关于对称线性电阻电路等效变换的探讨[期刊论文]-青海师专学报(自然科学)2002,22(5) 2.徐昌智.何宝钢电阻Y联接和△联接的等效变换关系的求证[期刊论文]-云南民族大学学报(自然科学版)2004,13(3) 3.黄新民二端线性网络等效电阻的求解[期刊论文]-科技信息(学术版)2007(16) 4.安生立.AN Sheng-li星形三角形转换在汽车发电机中的应用[期刊论文]-沈阳师范大学学报(自然科学版)2008,26(3) 5.赖昭胜.LAI Zhao-sheng多边形电阻网络的等效电阻分析[期刊论文]-赣南师范学院学报2007,28(3) 6.李建新.刘栓江.LI Jian-xin.LIU Shuan-jiang规则联接的多边形电阻网络的等效电阻研究[期刊论文]-大学物理2008,27(11) 7.谭志中.陆建隆.TAN Zhizhong.LU Jianlong多边形电阻网络等效电阻的统一建构[期刊论文]-河北师范大学学报(自然科学版)2011,35(2) 8.黄伟物理竞赛中纯电阻电路的简化[期刊论文]-中学物理(初中版)2010(4) 9.吴学伍巧算等效电阻[会议论文]-2000 10.张耀宇.贾利群.ZHANG Yao-yu.JIA Li-qun二维非对称无规二端电阻网络的等效电阻[期刊论文]-平顶山学院学报2006,21(5) 本文链接:https://www.360docs.net/doc/011728926.html,/Periodical_zgkjxx200524128.aspx

集电极开路TT门(OC门)

集电极开路TTL门(OC门) ⑴TTL与非门输出端并联后出现的问题 在实际应用与非门时,某些场合希望能将多个门的输出端连在同一根导线上。在数字系统中,称公共导线为总线(BUS),为传输各门信息的公共通道。但是对于推拉输出的TTL与非门,当各个门的输出不是相同的逻辑状态时不能这样使用。有两个推拉输出的TTL与非门,若在一个门输出为高电平(即该门关门),另一个门输出为低电平(即该门开门)时, 图1 两个TTL与非门输出端直接相连的错误接法

将两个门的输出端并联成图1所示电路。由于在具有推拉式输出级的电路中,无论输出是高电平还是低电平,输出电阻都很小,输出端并接后将有很大的电流i同时流过两个门的输出级,该电流远远超过了与非门的正常工作电流,足以使V3、V4 过载而损坏,更为严重的是并联后的输出电压既非逻辑1亦非逻辑0,这种不确定状态是不允许出现的。因此,推拉输出的TTL与非门输出端是不允许并联使用的。 ⑵集电极开路的与非门结构和符号 避开低阻通路,把输出级改为集电极开路的结构就可以解决推拉输出的TTL与非门的输出不允许接至同一总线上的问题。如图2(a)所示,这种门称为集电极开路的与非门(OC门)。它与推拉输出的与非门的区别是用外接电阻RC代替R4、V3、VD3,电源VC与VCC可以不是同一个。这种门电路在工作时需要外接负载电阻和电源。只要电阻的阻值和电源电压的数值选择得当,就能够做到既保证输出的高、低电平符合要求,输出端三极管的负载电流又不过大。

图2 TTL开路门(a)电路结构;(b)符号。 当几个OC门的输出端相连时,一般可共用一个电阻RC和电源VC,如图3(a)、(b)分别给出它们的符号和电路结构。 图3 OC门的线与连接图4 OC门上拉电阻的计算 图3中Y1输出高电平,Y2输出低电平时,负载电流同样会通过RC 流向Y2的输出管V4。但可以把外接电阻RC选得足够大,使得电流很小,确保Y1的输出管能可靠饱和,输出Y为低电平。当然RC也不能过大,否则会降低OC门的输出高电平。图4中,当相连的OC门中至少有一个输出为低电平时,总输出为低电平;当两个OC门的输出都为高电平时,则总输出为高电平。可见它能实现输出端相“与”的功能。输出

复杂电路等效电路

复杂电阻网络的处理方法 在物理竞赛过程中经常遇到,无法直接用串联和并联电路的规律求出整个电路电阻的情况,这样的电路也就是我们说的复杂电路,复杂电路一般分为有限网络和无限网络。那么,处理这种复杂电路用什么方法呢?下面,我就结合自己辅导竞赛的经验谈谈复杂电路的处理方法。 一:有限电阻网络 原则上讲解决复杂电路的一般方法,使用基尔霍夫方程组即可。它包含的两类方程出自于两个自然的结论:(1)对电路中任何一个节点,流出的电流之和等于流入的电流之和。电路中任何一个闭合回路,都符合闭合电欧姆定律。下面我介绍几种常用的其它的方法。 1:对称性简化 所谓的对称性简化,就是利用网络结构中可能存在的对称性简化等效电阻的计算。它的效果是使计算得以简化,计算最后结果必须根据电阻的串、并联公式;电流分布法;极限法等来完成。 在一个复杂的电路中,如果能找到一些完全对称的点,那么当在这个电路两端加上电压时,这些点的电势一定是相等的,即使用导线把这些点连接起来也不会有电流(或把连接这些点的导线去掉也不会对电路构成影响),充分的利用这一点我们就可以使电路大为简化。 例(1)如图1所示的四面体框架由电阻都为R的6根电阻丝连接而成,求两顶点A、B间的等效电阻。 图1 图2 分析:假设在A、B两点之间加上电压,并且电流从A电流入、B点流处。因为对称性,图中CD两点等电势,或者说C、D 间的电压为零。因此,CD间的电阻实际上不起作用,可以拆去。原网络简化成简单的串、并联网络,使问题迎刃而解。 解:根据以上分析原网络简化成如图2所示的简单的串、并联网络,由串、并联规律得 R AB=R/2 例(2)三个相同的金属圈两两正交地连成如图所示的形状,若每一个金属圈的原长电阻为R,试求图中A、B两点之间的等效电阻。 图3 图4 图5 分析:从图3中可以看出,整个电阻网络相对于AB的电流流入、流出方式上具有上下对称性,因此可上下压缩成如图所时的等效减化网络。从如图4所示的网络中可以看出,从A点流到O电流与从O点到B电流必相同;从A1点流到O电流与从O点到B1电流必相同。据此可以将O点断开,等效成如图5所示的简单网络,使问题得以求解。解:根据以上分析求得R AB=5R/48 例(3)如图6所示的立方体型电路,每条边的电阻都是R。求A、G之间的电阻是多少? 分析: 假设在A 、G两点之间加上电压时,显然由于对称性D、B、E 的电势是相等的,C、F、H的电势也是相等的,把这些点各自连起来,原电路就变成了如图7 A D B C D C A B A A B ' B' B A B' A E B G C H D F 6 图 A 7 图

器件集电极开路门与三态输出门的应用实验报告

集电极开路门与三态输出门的应用实验报告 一、 实验目的 掌握TTL 集电极开路(OC)门和三态(3S)输出门的逻辑功能及应用。 二、 实验器件 试验箱、万用表 三、 实验内容及数据 1. OC 门的特性及其应用 (1) 参考图1.4.2,用OC 门74LS03验证 OC 门的“线与”功能。R L 为1k Ω时,写出输出F 的表达式,观测输出与输入信号的逻辑关系,将数据填入自制表格中。 电路接线:5V :14 GND :7 十六位逻辑电平输出:4、5、13、12 十六位逻辑电平显示:电阻(1K ) 电阻(1K ):6(6与11相连) A B C D F 0 0 0 0 1 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 0 1 0 0 1 0 1 0 1 1 0 1 1 0 1 0 1 1 1 0 1 0 0 0 1 1 0 0 1 1 1 0 1 0 1 1 0 1 1 0 1 1 0 0 0 1 1 0 1 0 1 1 1 0 0 1 1 1 1

原理:两个与非门相连,逻辑公式为:逻辑公式:F=(AB)’(CD)’ (2) 参考图1.4.7, 验证OC 门74LS03的特性,输入A 、B 接逻辑电平输出信号,输出端Y 接直流电压表。V L 接+5V,电阻R L 为4.7k, 观测输出与输入信号的逻辑关系,如果去掉R L , 观测输出信号的变化。V L 改接+15V , 检 测输出信号的高电平和低电平电压。 电路接线:5V :14 GND :7 十六位逻辑电平输出:4、5 十六位逻辑电平显示:电阻(1K ) 电阻(1K ):6 原理:两个与非门相连,逻辑公式为:逻辑公式:Y=(AB)’ 逻辑关系表: A B Y 0 0 1 0 1 0 1 0 0 1 1 (3) 参考图1.4-8,用OC 门74LS03驱动COMS 电路与非门CD4011,V L 接+5V ,调节电位器R w ,观察上拉电阻的取值对输出端Y 的电平的影响。要求输出信号Y 的高电平不小于3.5V, 低电平不大于0.3V,实验求出上拉电阻的取值范围。 去掉R L ,信号灯亮度增加,逻辑关系不变。 V L 改接+15V ,高电平电压:3.05 低电平电压:0.22 V L 改接+15V ,高电平电压:9.60 低电平电压:0.10

三极管集电极开路输出结构图解

三极管集电极开路输出结构图解

————————————————————————————————作者:————————————————————————————————日期:

三极管集电极开路输出结构图解 集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做集电极开路;左边的三极管为反相之用,使输入为“0”时,输出也为“0”。 对于图 1,当左端的输入为“0”时,前面的三极管截止,所以5v 电源通过1k电阻加到右边的三极管上,右边的三极管导通;当左端的输入为“1”时,前面的三极管导通,而后面的三极管截止。 我们将图1简化成图2的样子,很明显可以看出,当开关闭合时,输出直接接地,所以输出电平为0。而当开关断开时,则输出端悬空了,即高阻态。这时电平状态未知,如果后面一个电阻负载到地,那么输出端的电平就被这个负载拉到低电平了,所以这个电路是不能

输出高电平的。 图3中那个1k的电阻即是上拉电阻。如果开关闭合,则有电流从1k电阻及开关上流过,但由于开关闭和时电阻为0(方便我们的讨论,实际情况中开关电阻不为0,另外对于三极管还存在饱和压降),所以在开关上的电压为0,即输出电平为0。如果开关断开,则由于开关电阻为无穷大(同上,不考虑实际中的漏电流),所以流过的电流为0,因此在1k 电阻上的压降也为0,所以输出端的电压就是5v了,这样就能输出高电平了。 但是这个输出的内阻是比较大的——即1k,如果接一个电阻为r的负载,通过分压计算,就可以算得最后的输出电压为5*r/(r+1000)伏,所以,如果要达到一定的电压的话,r就不能太小。如果r 真的太小,而导致输出电压不够的话,那我们只有通过减小那个1k的上拉电阻来增加驱动能力。但是,上拉电阻又不能取得太小,因为当开关闭合时,将产生电流,由于开关能流过的电流是有限的,因此限制了上拉电阻的取值。另外还需要考虑到,当输出低电平时,负载可能还会给提供一部分电流从开关流过,因此要综合这些电流考虑来选择合适的上拉电阻。 如果我们将一个读数据用的输入端接在输出端,这样就是一个IO口了,51的IO口就是这样的结构,其中P0口内部不带上拉,而其它三个口带内部上拉。当我们要使用输入功能时,只要将输出口设置为1即可,这样就相当于那个开关断开,而对于P0口来说,就是高阻态了。

第二章-电阻电路的等效变

第二章-电阻电路的等效变

————————————————————————————————作者:————————————————————————————————日期:

第二章 电阻电路的等效变换 2.1 学习要点 1. 电阻的等效变换:电阻的串并联, Y 与△的等效变换。 2. 电源的串联、并联及等效变换。 3. “实际电源”的等效变换。 4. 输入电阻的求法。 2.2 内容提要 2.2.1 电阻的等效变换 1. 电阻的串联:等效电阻: R eq = ∑ 1 =k n k R ;分压公式:u k =eq k eq ×R R u ; 2. 电阻的并联:等效电导:G eq = ∑ 1 =k n k G ;分流公式:q e G G i i k eq k ×=; 2.2.2. 电阻的Y 与△的等效变换 1. △→Y :一般公式: Y 形电阻= 形电阻之和 形相邻电阻的乘积 ??; 即 31 232331********* 231231212 311++= ++= ++R R R R R R R R R R R R R R R R R R 2312= 2. Y →△:一般公式:形不相邻电阻 形电阻两两乘积之和 形电阻= Y Y ?;

u - R i u u - - i + + + 图 G i 即: 2 1 33221311 1 33221233 1 3322112++= ++= ++= R R R R R R R R R R R R R R R R R R R R R R R R 2.2.3 电源的串联、并联等效变换 电源的串联、并联等效变换见表2.1。 表2.1 电源的串联、并联等效变换 连接情况 等效结果或计算公式 说 明 n 个电压源的串联 sn s s s s u u u u u ±±±=k 21 u s 为等效电压源,当u k 与u s 的参考方向相同时,u sk 前取“+”号,反之取“-”号 n 个电流源的并联 sn sk s s s i i i i i ±±±=21 i s 为等效电流源,当i sk 与i s 的参考方向相同时,i sk 前取“+”号,反之取“-”号 电压源u s 与一个非理想电压源支路并联 对外电路可等效成该电压源u s ⑴与电压源u s 并联可以是电阻、电流源,也可是复杂的支路 ⑵仅是对外电路等效 电流源i s 与一个非理想电流源支路串联 对外电路可等效成该电流源i s ⑴与电流源i s 串联可以是电阻、电压源,也可是复杂的支路 ⑵仅是对外电路等效 2.2.4 “实际电源”的等效变换 1. “实际电压源”→“实际电流源” R i =R u 或 G i =1/R u i s =u s /R u 2. “实际电流源”→“实际电压源”

集电极开路输出

集电极开路输出 在应用PLC、变频器和伺服电机等自动控制设备使时,通常会遇到集电极开路输出的接口输出形式,那么什么是集电极开路输出呢? 集电极开路(Open Collector,在数字电路中简称OC门)电路中的“集”就是指三极管的集电极。集电极开路输出其实就是控制三极管工作在截止区或者饱和区的一种工作状态。三极管符号如图1所示: 图1:左边为PNP型三极管,右边为NPN型三极管。其中,基极用B(base)表示,集电极用C(collector)表示,发射极用E(emitter)表示。 典型的集电极开路电路如图2所示。电路中右侧晶体管的集电极(output)什么都不接,所以叫做集电极开路。右侧的三极管用作反向作用,即左侧(input)输入为0时左侧的三极管截至,VCC通过电阻加到右侧三极管基极,右侧的三极管导通,右侧输出端连接到地,输出0。 图2典型集电极开路电路

从图2中可以看出,集电极开路输出是无法输出高电平的。如果想要输出高电平,;可以在输出端加上上拉电阻。因此集电极开路输出可以用作电平转换,通过上拉电阻上拉至不同的电压,来实现不同的电平转换。用做驱动器时,由于OC门电路的输出管的集电极悬空,使用时需外接一个上拉电阻Rp到电源VCC。OC门通过上拉电阻可以输出高电平,此外,为了加大输出引脚的驱动能力,从降低功耗及芯片的灌电流能力考虑,上拉电阻应当选择足够大,从确保足够的驱动电流考虑应当足够小。 将OC门输出连接在一起时,在通过一个电阻接外电源,可以实现“线与”逻辑关系。只要电阻的阻值和外电源电压的数值选择得当,就即能保证输出的高低电平符合要求,也能保证三极管的负载电流不至于过大。 集电极开路输出除了可以实现多门的线与逻辑关系外,通过使用大功率的三极管还可以直接驱动交大电流的负载,如继电器、脉冲变压器、指示灯等。

串并联电路中的等效电阻计算公式

串、并联电路中的等效电阻及计算公式 串、并联电路中的等效电阻 学习目标要求: 1.知道串、并联电路中电流、电压特点。 2.理解串、并联电路的等效电阻。 3.会计算简单串、并联电路中的电流、电压和电阻。 4.理解欧姆定律在串、并联电路中的应用。 5.会运用串、并联电路知识分析解决简单的串、并联电路问题。 中考常考内容: 1.串、并联电路的特点。 2.串联电路的分压作用,并联电路的分流作用。 3.串、并联电路的计算。 知识要点: 1.串联电路的特点 (1)串联电路电流的特点:由于在串联电路中,电流只有 一条路径,因此,各处的电流均相等,即;因此,在对串联电路的分析和计算中,抓住通过各段导体的电流相等这个条件,在不同导体间架起一座桥梁,是解题的一条捷径。

(2)由于各处的电流都相等,根据公式,可以得到 ,在串联电路中,电阻大的导体,它两端的电压也大,电压的分配与导体的电阻成正比,因此,导体串联具有分压作用。串联电路的总电压等于各串联导体两端电压之和,即 。 (3)导体串联,相当于增加了导体的长度,因此,串联导体的总电阻大于任何一个串联导体的电阻,总电阻等于各串联导 体电阻之和,即。如果用个阻值均为的 导体串联,则总电阻。 2.并联电路的特点 (1)并联电路电压的特点:由于在并联电路中,各支路两端分别相接且又分别接入电路中相同的两点之间,所以各支路两 端的电压都相等,即。因此,在电路的分析和计算中,抓住各并联导体两端的电压相同这个条件,在不同导体间架起一座桥梁,是解题的一条捷径。 (2)由于各支路两端的电压都相等,根据公式,可得 到,在并联电路中,电阻大的导体,通过它的电流小,电流的分配与导体的电阻成反比,因此,导体并联具有分流作用。并联电路的总电流等于各支路的电流之和,即 。

[课程]集电极开路输出

[课程]集电极开路输出 集电极开路输出 我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为“0”时,输出也为“0”)。对于图1,当左端的输入为“0”时,前面的三极管截止(即集电极c跟发射极e之间相当于断开),所以5v电源通过1k电阻加到右边的三极管上,右边的三极管导通(即相当于一个开关闭合);当左端的输入为“1”时,前面的三极管导通,而后面的三极管截止(相当于开关断开)。 我们将图1简化成图2的样子。图2中的开关受软件控制,“1”时断开,“0”时闭合。很明显可以看出,当开关闭合时,输出直接接地,所以输出电平为0。而当开关断开时,则输出端悬空了,即高阻态。这时电平状态未知,如果后面一个电阻负载(即使很轻的负载)到地,那么输出端的电平就被这个负载拉到低电平了,所以这个电路是不能输出高电平的。 再看图三。图三中那个1k的电阻即是上拉电阻。如果开关闭合,则有电流从1k电阻及开关上流过,但由于开关闭和时电阻为0(方便我们的讨论,实际情况中开关电阻不为0,另外对于三极管还存在饱和压降),所以在开关上的电压为0,即输出电平为0。如果开关断开,则由于开关电阻为无穷大(同上,不考虑实际中的漏电流),所以流过的电流为0,因此在1k电阻上的压降也为0,所以输出端的电压就是5v了,这样就能输出高电平了。但是这个输出的内阻是比较大的(即 1kω),如果接一个电阻为r的负载,通过分压计算,就可以算得最后的输出电压为5*r/(r+1000)伏,即5/(1+1000/r)伏。所以,如果要达到一定的电压的话,r 就不能太小。如果r真的太小,而导致输出电压不够的话,那我们只有通过减小那个1k的上拉电阻来增加驱动能力。但是,上拉电阻又不能取得太小,因为当开关

集电极开路输出(OC)、漏极开路输出(OD)、推挽输出

集电极开路输出(OC)、漏极开路输出(OD)、推挽输出一、集电极开路(OC)-->(输出低电平电流大,输出高电平电流小) 我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个三极管的集电极什么都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为“0”时,输出也为“0”)。 对于图1,当左端的输入为“0”时,前面的三极管截止(即集电极c 跟发射极e之间相当于断开),所以5v电源通过1k电阻加到右边的三极管上,右边的三极管导通(即相当于一个开关闭合);当左端的输入为“1”时,前面的三极管导通,而后面的三极管截止(相当于开关断开)。 我们将图1简化成图2的样子。图2中的开关受软件控制,“1”时断开,“0”时闭合。很明显可以看出,当开关闭合时,输出直接接地,所以输出电平为0。而当开关断开时,则输出端悬空了,即高阻态。这时电平状态未知,如果后面一个电阻负载(即使很轻的负载)到地,那么输出端的电平就被这个负载拉到低电平了,所以这个电路是不能输出高电平的。 再看图3,图3中那个1k的电阻即是上拉电阻。如果开关闭合,则有电流从1k电阻及开关上流过,但由于开关闭和时电阻为0(方便我们的讨论,实际情况中开关电阻不为0,另外对于三极管还存在饱和压降),所以在开关上的电压为0,即输出电平为0。如果开关断开,则由于开关电阻为无穷大(同上,不考虑实际中的漏电流),所以流过的电流为0,

因此在1k电阻上的压降也为0,所以输出端的电压就是5v了,这样就能输出高电平了。但是这个输出的内阻是比较大的(即1kω),如果接一个电阻为r的负载,通过分压计算,就可以算得最后的输出电压为 5*r/(r+1000)伏,即5/(1+1000/r)伏。所以,如果要达到一定的电压的话,r就不能太小。如果r真的太小,而导致输出电压不够的话,那我们只有通过减小那个1k的上拉电阻来增加驱动能力。但是,上拉电阻又不能取得太小,因为当开关闭合时,将产生电流,由于开关能流过的电流是有限的,因此限制了上拉电阻的取值,另外还需要考虑到,当输出低电平时,负载可能还会给提供一部分电流从开关流过,因此要综合这些电流考虑来选择合适的上拉电阻。 如果我们将一个读数据用的输入端接在输出端,这样就是一个IO 口了(51的IO口就是这样的结构,其中P0口内部不带上拉,而其它三个口带内部上拉),当我们要使用输入功能时,只要将输出口设置为1即可,这样就相当于那个开关断开,而对于P0口来说,就是高阻态了。

例析纯电阻电路中求等效电阻的常用方法

例析纯电阻电路中求等效电阻的几种方法 计算一个电路的电阻,通常要分析电路的串并联关系,运用欧姆定律求解。实际电路中,电阻的连接千变万化,需要应用相应的方法,通过等效变换将复杂电路转换成简单直观的串并联电路。本文介绍几种常用的计算复杂电路等效电阻的方法。 一、“基本单元”法 找出电路中的“基本单元”,再利用电阻的串并联关系求解。 1、片状导体求等效电阻 【例1】如图1所示,ABCD 为一块均匀的半圆形薄电阻合金片,当A 、B 接入电路时电阻为R ,试求当C 、D 接入电路时电阻为________。 【解析】设“基本单元”为沿对称轴AB 切开的 4 1 圆,由于A 、B 间电阻为R (可视为两个并联的“基本单元”),所以,“基本单元”的电阻为2R ,当C 、D 接入电路时,相当于两个“基本单元”串联,等效电阻为4 R 。 【例2】如图2甲所示,一材质均匀的正方形薄片导体的阻值为R ,若在其正中挖去一 小正方形,挖去的正方形边长为原边长的3 1 ,则剩余部分的电阻为_______。 【解析】设挖去的小正方形为“基本单元”,由于原来的电阻为R (3个并联的“基本单元”,串3个并联的“基本单元”,再串3个并联的“基本单元”),所以“基本单元”的电阻也为R ;挖去后,如图2乙所示,电路相当于3个并联的R 、串2个并联的R ,再串3个 并联的R ,等效电阻为.6 7323R R R R =++ 2、一维有限网络求等效电阻 【例3】如图3甲所示,已知R 1=R 2=R 3=…=R n =R n+1=R m =R m+1=R /2,则A 、B 间的电阻R AB =__________。 图 1 图2甲 图2乙 图3甲

例析纯电阻电路中求等效电阻的常用方法

例析纯电阻电路中求等效电阻的几种方法 计算一个电路的电阻, 通常要分析电路的串并联关系, 运用欧姆定律求解。实际电路中, 电阻的连接千变万化, 需要应用相应的方法, 通过等效变换将复杂电路转换成简单直观的串 并联电路。本文介绍几种常用的计算复杂电路等效电阻的方法。 一、“基本单元”法 找出电路中的“基本单元”,再利用电阻的串并联关系求解。 1、片状导体求等效电阻 【例1】如图1所示,ABCD 为一块均匀的半圆形薄电阻合金片,当 A 、B 接入电路时 电阻为R ,试求当C 、D 接入电路时电阻为 _____________ 。 1 【解析】设“基本单元”为沿对称轴 AB 切开的丄圆,由于A 、B 间电阻为R (可视为 两个并联的“基本单元”),所以,“基本单元”的电阻为 2R ,当C 、D 接入电路时,相当于 两个“基本单元”串联,等效电阻为 4 Ro 【例2】如图2甲所示,一材质均匀的正方形薄片导体的阻值为 R ,若在其正中挖去 1 小正方形,挖去的正方形边长为原边长的 丄,则剩余部分的电阻为 _________ o 【解析】设挖去的小正方形为“基本单元” ,由于原来的电阻为 R ( 3个并联的“基本 单元”,串3个并联的“基本单元”,再串3个并联的“基本单元”),所以“基本单元”的电 阻也为R ;挖去后,如图2乙所示,电路相当于 3个并联的R 、串2个并联的R ,再串3个 并联的R ,等效电阻为-R R =^ R . 2、一维有限网络求等效电阻 【例3】如图3甲所示,已知 R 1=R 2=R 3= - =R n = R n+1 = R m =R m+1 = R/2,贝U A 、B 间的电阻 R AB = _________ o 图

集电极开路、漏极开路、上拉电阻、下拉电阻等接口相关基本概念

集电极开路、漏极开路、上拉电阻、下拉电阻等接口相关基本概念 1.1.1 接口相关电路及概念 1. 集电极开路输出 在电路中常会遇到漏极开路(Open Drain)和集电极开路(Open Collector)两种情形。漏极开路电路概念中提到的“漏”是指MOSFET的漏极。同理,集电极开路电路中的“集”就是指三极管的集电极。在数字电路中,分别简称OD门和OC门。 典型的集电极开路电路如图所示。电路中右侧的三极管集电极什么都不接,所以叫做集电极开路,左侧的三极管用于反相作用,即左侧输入“0”时左侧三极管截止,VCC通过电阻加到右侧三极管基极,右侧三极管导通,右侧输出端连接到地,输出“0”。

从图中电路可以看出集电极开路是无法输出高电平的,如果要想输出高电平可以在输出端加上上拉电阻。因此集电极开路输出可以用做电平转换,通过上拉电阻上拉至不同的电压,来实现不同的电平转换。 用做驱动器。由于OC门电路的输出管的集电极悬空,使用时需外接一个上拉电阻Rp到电源VCC。OC门使用上拉电阻以输出高电平,此外为了加大输出引脚的驱动能力,上拉电阻阻值的选择原则,从降低功耗及芯片的灌电流能力考虑应当足够大;从确保足够的驱动电流考虑应当足够小。 将OC门输出连在一起时,再通过一个电阻接外电源,可以实现“线与”逻辑关系。只要电阻的阻值和外电源电压的数值选择得当,就能做到既保证输出的高、低电平符合要求,而且输出三极管的负载电流又不至于过大。 集电极开路输出除了可以实现多门的线与逻辑关系外,通过使用大功率的三极管还可用于直接驱动较大电流的负载,如继电器、脉冲变压器、指示灯等。 2. 漏极开路输出 和集电极开路一样,顾名思义,开漏电路就是指从MOSFET的漏极输出的电路。典型的用法是在漏极外部的电路添加上拉电阻到电源如图所示。完整的开漏电路应由开漏器件和开漏上拉电阻组成。这里的上拉电阻R的阻值决定了逻辑电平转换的上升/下降沿的速度。阻值越大,速度越低,功耗越小。因此在选择上拉电阻时要兼顾功耗和速度。标准的开漏脚一般只有输出的能力。添加其它的判断电路,才能具备双向输入、输出的能力。

关于电阻网络等效电阻的求法

选修3-2电磁感应复习学案 知识结构: 课标要求: 1、收集资料,了解电磁感应现象的发现过程,体会人类探索自然规律的科学态度和科学精神。 2、通过实验,理解感应电流的产生条件。举例说明电磁感应在生活和生产中的应用。 3、通过探究,理解楞次定律。理解法拉第电磁感应定律。 4、通过实验了解自感现象和涡流现象。举例说明自感现象和涡流现象在生活中和生产中的应用。 知识要点: 1.电磁感应现象: 2.感应电流的产生条件①② 3.楞次定律:感应电流具有这样的方向,即感应电流的磁场总要阻碍 。这里的阻碍可以理解为“反抗增大、补偿减小”。 4.从磁通量变化的角度来看,感应电流“阻碍磁通量变化”。由磁通量的计算式 Φ=BS cosα(α是指B、S之间的夹角),可知,磁通量变化ΔΦ=Φ2-Φ1有多种形式,主要有: ①S、α不变,B改变,这时ΔΦ= ②B、α不变,S改变,这时ΔΦ= ③B、S不变,α改变,这时ΔΦ=BS(cosα2-cosα1) ④另外还有B、S、α中有两个或三个一起变化的情况。此时只能使用公式ΔΦ=Φ2-Φ1。 从阻碍相对机械运动的角度来看,感应电流总是阻碍。 从阻碍自身电流变化的角度来看,感应电流“阻碍自身电流变化”。这就是。5.楞次定律的应用,可以分为五步:①确定研究对象②确定原磁场方向; ③;④(增反减同); ⑤根据判定感应电流的方向。 6.对一部分导线在磁场中切割磁感线产生感应电流的情况,右手定则和楞次定律的结论是完全一致的。 右手定则的内容:让磁感线垂直穿过手心,大拇指指向方向,四指的指向就是导体内部所产生的的方向.四指的指向还可以代表等效电源的极。7.法拉第电磁感应定律:感应电动势的大小与,其数学表达式E = 。一般情况下该关系式表示的是电动势的值。

开漏输出、开集输出

开漏输出、开集输出 推挽输出:可以输出高,低电平,连接数字器件; 开漏输出:输出端相当于三极管的集电极.要得到高电平状态需要上拉电阻才行.适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内). 推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止. 我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为“0”时,输出也为“0”)。对于图1,当左端的输入为“0”时,前面的三极管截止(即集电极C跟发射极E之间相当于断开),所以5V电源通过1K电阻加到右边的三极管上,右边的三极管导通(即相当于一个开关闭合);当左端的输入为“1”时,前面的三极管导通,而后面的三极管截止(相当于开关断开)。

我们将图1简化成图2的样子。图2中的开关受软件控制,“1”时断开,“0”时闭合。很明显可以看出,当开关闭合时,输出直接接地,所以输出电平为0。而当开关断开时,则输出端悬空了,即高阻态。这时电平状态未知,如果后面一个电阻负载(即使很轻的负载)到地,那么输出端的电平就被这个负载拉到低电平了,所以这个电路是不能输出高电平的。 再看图三。图三中那个1K的电阻即是上拉电阻。如果开关闭合,则有电流从1K电阻及开关上流过,但由于开关闭其它三个口带内部上拉),当我们要使用输入功能时,只要将输出口设置为1即可,这样就相当于那个开关断开,而对于P0口来说,就是高阻态了。

对于漏极开路(OD)输出,跟集电极开路输出是十分类似的。将上面的三极管换成场效应管即可。这样集电极就变成了漏极,OC就变成了OD,原理分析是一样的。 另一种输出结构是推挽输出。推挽输出的结构就是把上面的上拉电阻也换成一个开关,当要输出高电平时,上面的开关通,下面的开关断;而要输出低电平时,则刚好相反。比起OC或者OD来说,这样的推挽结构高、低电平驱动能力都很强。如果两个输出不同电平的输出口接在一起的话,就会产生很大的电流,有可能将输出口烧坏。而上面说的OC或OD输出则不会有这样的情况,因为上拉电阻提供的电流比较小。如果是推挽输出的要设置为高阻态时,则两个开关必须同时断开(或者在输出口上使用一个传输门),这样可作为输入状态,AVR单片机的一些IO口就是这种结构。 开漏电路特点及应用 在电路设计时我们常常遇到开漏(open drain)和开集(open collector)的概念。