晶圆级封装产业

晶圆级封装产业(WLP)

晶圆级封装产业(WLP),晶圆级封装产业(WLP)是什么意思

一、晶圆级封装(Wafer Level Packaging)简介晶圆级封装(WLP,Wafer Level Package) 的一般定义为直接在晶圆上进行大多数或是全部的封装测试程序,之后再进行切割(singulation)制成单颗组件。而重新分配(redistribution)与凸块(bumping)技术为其I/O绕线的一般选择。WLP

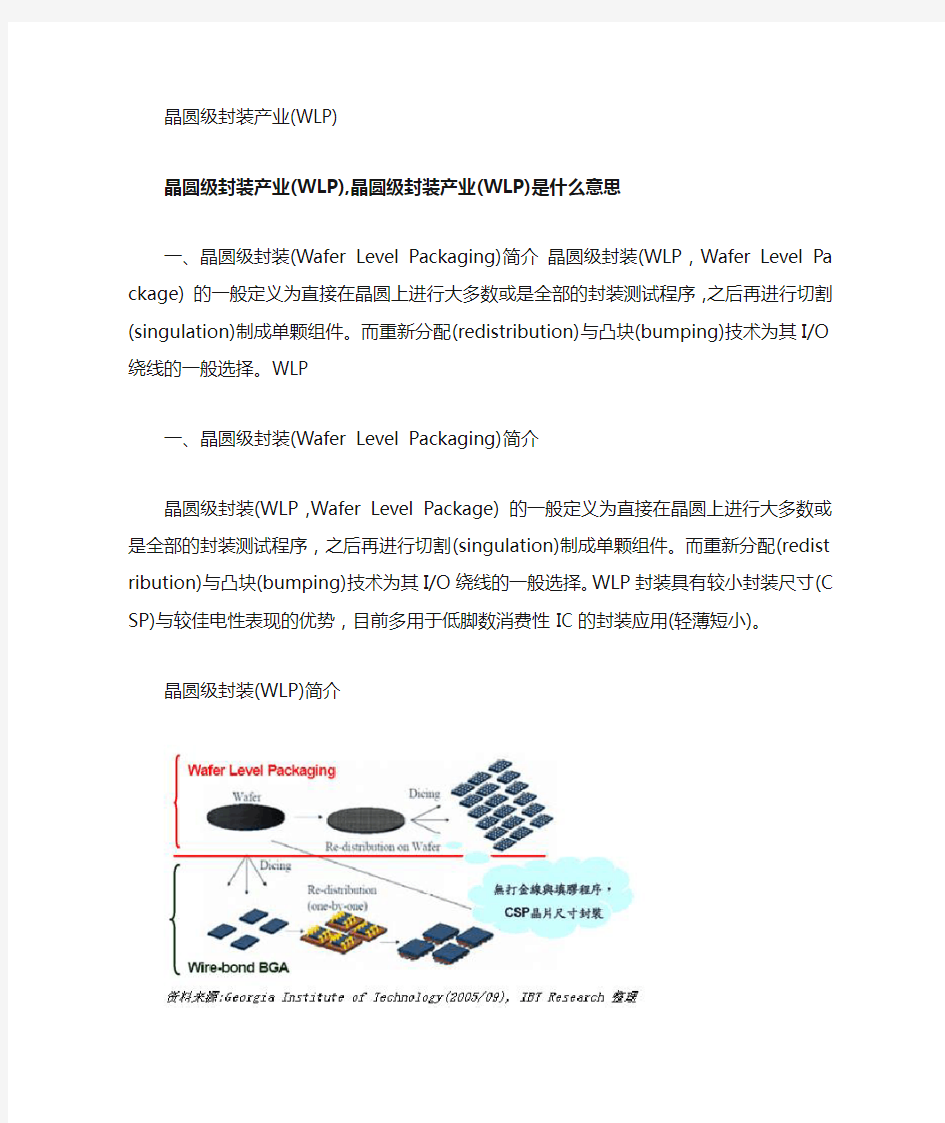

一、晶圆级封装(Wafer Level Packaging)简介

晶圆级封装(WLP,Wafer Level Package) 的一般定义为直接在晶圆上进行大多数或是全部的封装测试程序,之后再进行切割(singulation)制成单颗组件。而重新分配(redistribution)与凸块(bumping)技术为其I/O绕线的一般选择。WLP封装具有较小封装尺寸(CSP)与较佳电性表现的优势,目前多用于低脚数消费性IC的封装应用(轻薄短小)。

晶圆级封装(WLP)简介

常见的WLP封装绕线方式如下:1. Redistribution (Thin film), 2. Encapsulated Glass substrate, 3. Gold

stud/Copper post, 4. Flex Tape等。此外,传统的WLP封装多采用Fan-in 型态,但是伴随IC信号输出pin 数目增加,对ball pitch的要求趋于严格,加上部分组件对于封装后尺寸以及信号输出脚位位置的调整需求,因此变化衍生出Fan-out 与Fan-in + Fan-out 等各式新型WLP封装型态,其制程概念甚至跳脱传统WLP

封装,目前德商英飞凌与台商育霈均已经发展相关技术。

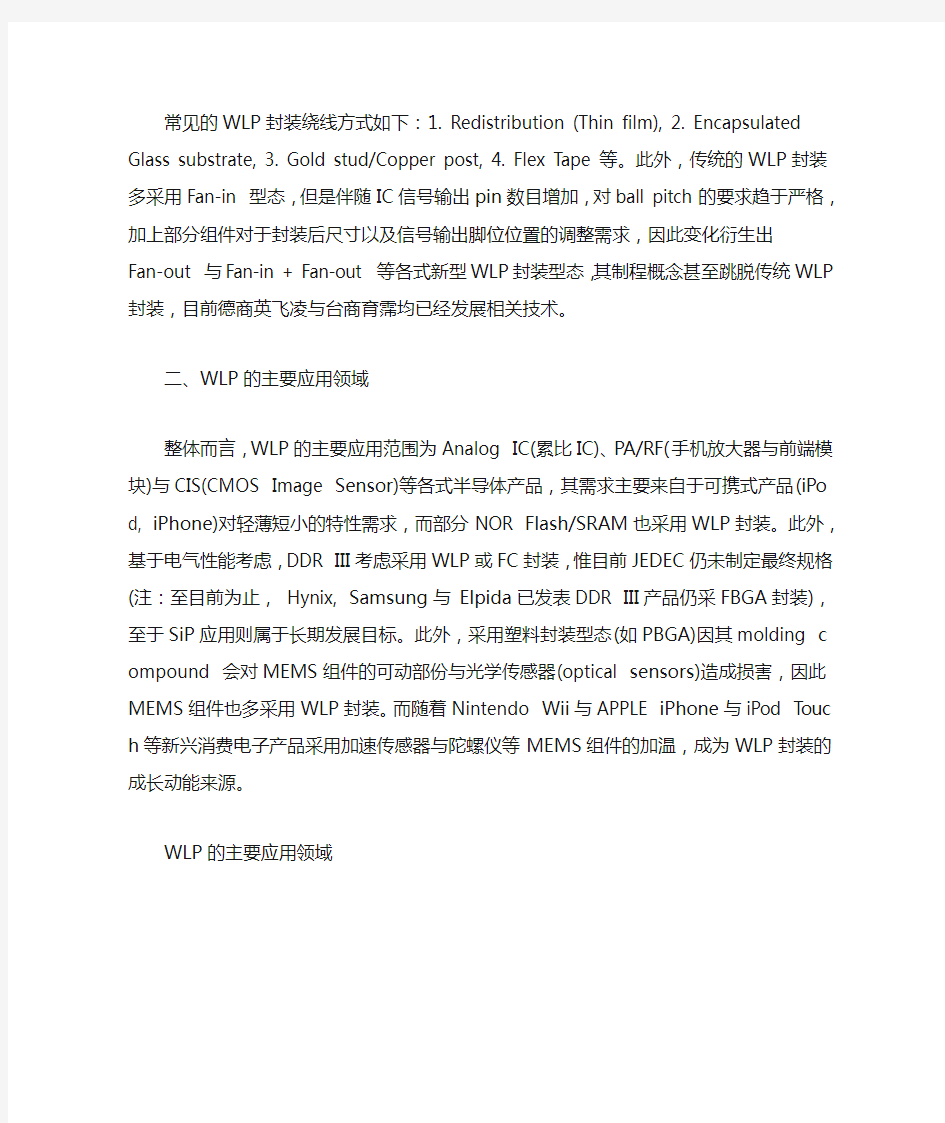

二、WLP的主要应用领域

整体而言,WLP的主要应用范围为Analog IC(累比IC)、PA/RF(手机放大器与前端模块)与CIS(CMOS Ima ge Sensor)等各式半导体产品,其需求主要来自于可携式产品(iPod, iPhone)对轻薄短小的特性需求,而部分NOR Flash/SRAM也采用WLP封装。此外,基于电气性能考虑,DDR III考虑采用WLP或FC封装,惟目前JEDEC仍未制定最终规格(注:至目前为止,Hynix, Samsung与Elpida已发表DDR III产品仍采F BGA封装),至于SiP应用则属于长期发展目标。此外,采用塑料封装型态(如PBGA)因其molding compo und 会对MEMS组件的可动部份与光学传感器(optical sensors)造成损害,因此MEMS组件也多采用WLP

封装。而随着Nintendo Wii与APPLE iPhone与iPod Touch等新兴消费电子产品采用加速传感器与陀螺仪等MEMS组件的加温,成为WLP封装的成长动能来源。

WLP的主要应用领域

三、WLP的优点与挑战

仅就以下四点讨论WLP发展的挑战,至于优点请参考下图。

1.组件缩小化

伴随制程微缩的组件缩小化(footprint change),对WL-CSP的设计造成挑战,特别是Fan-in型态的WL-CS P的Ball diameter与ball pitch的技术难度提升,甚至造成封装良率的提升瓶颈,进而导致成本上升,此议题必须妥善因应,否则WLP的应用将局限于小尺寸与低脚数组件,市场规模也将受限。

2.价格

WLP必须与传统封装如TSOP接近甚至更低,而其设计架构、使用材料与制造流程将对最终生产良率扮演最重要的价格因素,更是WLP封测厂商能否成功的关键要素。

3.可靠度

晶粒与基板之间的thermal mismatch随尺次越大越加严重,其所造成的solder ball fatigue(锡铅球热疲劳)导致WLP 输出脚数多局限于输出脚数小于60的产品,而随着半导体组件输出信号脚数的增加,加强bum ping 连结强度的重要性日趋提高。

4.测试方法(Wafer level testing and burn-in)

KGD(Known Good Die)的价格必须与TSOP相近,而WLP对于高密度接触点与接触点共平面性/压力的要求相当严格,成本不易压低。而WLP相关治具套件的开发与规模经济成为WLP cost-down以及市场成长的重要关键,毕竟最终价格效能(C/P ratio)还是封装型态选择的关键要素。

WL-CSP的优点

四、WLP市场规模与主要供货商

2005年WLP封装市场规模达到2.1亿美元,预计于2010年将成长至5.5亿美元,期间产值CAGR达到21%,成长率不仅优于整体半导体产业,亦优于整体封装产业,而如前所述消费性电子产品对轻薄短小特性的需求,以及加速传感器与陀螺仪等MEMS组件的封装需求为WLP市产的主要成长动能来源。目前WLP主要的供货商包括主要如STM等IDM大厂(一贯化整合制程需求)、日月光等主要封测委外代工厂(具有bump ing技术与产能优势)、聚焦WLP技术的专业封测厂如台积电与OV合资的精材科技(以CMOS组件封装为主,并发展TSV- Through Silicon Vias等多元新兴封装技术),以及台商育霈与大陆长江电子等厂商。

2005~2010 WLP封装市场规模

WLP(晶圆级封装):超越IC封装的技术

圆级封装(WLP)是一项公认成熟的工艺,元器件供货商正寻求将WLP用于更多的领域,而业界对WLP 技术的支持推动着该技术快速走向成熟。WLP中一个关键工艺是晶圆凸点,其技术发展已进入实用阶段,日趋成熟稳定。随着组件供货商(包括功率和光电子器件)正积极转向WLP应用,其使用范围也在不断扩大。

晶圆级封装的背景

晶圆级封装技术源自于倒装芯片。晶圆级封装的开发主要是由集成器件制造厂家(IBM)率先启动。196 4年,美国IBM公司在其M360计算器中最先采用了FCOB焊料凸点倒装芯片器件。1969年,美国De lco公司在汽车中使用了焊料凸点器件。二十世纪70年代,NEC、日立等日本公司开始在一些计算器和超级计算器中采用FCOB器件。到了二十世纪90年代,世界上成立了诸如Kulicke and Soffa’s Flip Ch ip Division、Unitive、Fujitsu Tohoku Electronics、IC Interconnect等众多晶圆凸点的制造公司,这些公司拥有的基础技术是电镀工艺与焊膏工艺。这些公司利用凸点技术和薄膜再分布技术开发了晶圆级封装技术。FCD公司和富士通公司的超级CSP(Ultra CSP与Supper CSP)是首批进入市场的晶圆级封装产品。

1999年,晶圆凸点的制造公司开始给主要的封装配套厂家发放技术许可证。这样,倒装芯片和晶圆级封装也就逐渐在世界各地推广开来。例如,台湾的ASE公司和Siliconware公司以及韩国的Amkor公司就是按照FCD公司的技术授权来制造超级CSP(Ultra CSP)的。

晶圆级封装技术的现状

随着IC芯片技术的发展,芯片封装技术也不断达到新的水平,目前已可在单芯片上实现系统的集成。

在众多的新型封装技术中,晶圆级封装技术最具创新性、最受世人瞩目,是封装技术取得革命性突破的标志。晶圆级封装技术的构思是在整片晶圆上进行CSP封装技术的制造,也就是在晶圆级基本完成了大部分的封装工作。因此,晶圆级封装结构,则可省略覆晶技术点胶的步骤,目前可采用弹性体或是类弹性体来抵消应力,而这些弹性体的制程,可在整片晶圆上完成,因此省去了对一个个组件分别点胶的复杂制程。方形晶圆封装技术的设计理念,首先为增加组件与底材之间的距离,亦即选用更大的锡铅焊料球实现导电性,现有的晶圆级封装技术,采用重新布局技术来加大锡铅焊料球的间距,以达到加大锡铅焊料球体积的需求,进而降低并承受由基板与组件之间热膨胀差异而产生的应力,提高组件的可靠性。

晶圆级封装和晶圆级芯片尺寸封装(WLCSP)是同一概念,它是芯片尺寸封装的一个突破性进展,表示的是一类电路封装完成后仍以晶圆形式存在的封装,其流行的主要原因是它可将封装尺寸减小到和IC芯片一样大小以及其加工的成本低,晶圆级封装目前正以惊人的速度增长,其平均年增长率(CAGR)可达210%,推动这种增长的器件主要是集成电路、无源组件、高性能存储器和较少引脚数的器件。

目前有5种成熟的工艺技术可用于晶圆凸点,每种技术各有利弊。其中金线柱焊接凸点和电解或化学镀金焊接凸点主要用于引脚数较少的封装(一般少于40),应用领域包括玻璃覆晶封装(COG)、软膜覆晶封装(COF)和RF模块。由于这类技术材料成本高、工序时间长,因此不适合I/O引脚多的封装件。另一种技术是先置放焊料球,再对预成形的焊料球进行回流焊接,这种技术适用于引脚数多达300的封装件。目前用得最多的两种晶圆凸点工艺是电解或化学电镀焊料,以及使用高精度压印平台的焊膏印刷。

印刷焊膏的优点之一是设备投资少,这使很多晶圆凸点加工制造厂家都能进入该市场,为半导体制造厂家服务。随着WLP逐渐为商业市场所接受,全新的晶圆凸点专业加工服务需求持续迅速增长。的确,大多数晶圆凸点加工厂都以印刷功能为首要条件,并提供一项或多项其它技术。业界许多人士都认为焊膏印刷技术将主导多数晶圆凸点的应用。

最近几年,将四种不同类型的CSP确定为区别新涌现出的封装方法的商业化途径:作为小型化的BGA的刚性和柔性互连、引线框架基和晶圆级封装。由于经济方面的考虑推动着封装技术向着晶圆级封装(WLP)的方向发展,以便在布局定位之前,使每种芯片的封装定形,并确定测试方法。向300mm晶圆尺寸过渡推动着越来越多的晶圆级封装程序的定形方法的出台。WLP对于低针脚数无源组件、EEPROM、闪存、D RAM、ASIC和微处理机已是一种经济的方法。用于互连的面数组对于IC的I/O间距与印制电路板(PC B)的布线密度匹配也是很有必要的,这对于将用于微电子系统的不同组件或模块组合到一起是很必要的。因此,10年前开发出的重新布局技术对于WLP来说是一种最基本的工艺步骤。

目前的大容量WLP与Phoenix, Arizona和Unitive(自1999年在台湾)(开始从MCNC分离出来,现在属于Amkor的一部分)的FCI(前者倒装芯片技术)的技术类似。他们的商标名为UltraCSP(FCI)和Xtreme(Unitive/Amkor)的这种技术制定了标准,现在WLP每星期的出货量达百万件。

WLP是在市场不断地追求小型化的压力下,倒装芯片技术与SMT和BGA结合的产物。业内对于晶圆级封装理念的命名还不明确,定义上有些混乱。关键是在组装前是否需要对器件进行进一步的封装。如果不需要的话,就应将这种技术定义为晶圆级封装。对于多数高I/O微处理机和ASIC来说,在实施最后表面组装焊接前,芯片是装在互连载体上的,这样的话,就不是晶圆级封装了。缩略语FCIP(封装内倒装芯片,Flip Chip in Package)应用于这些方法中。

用于CSP的所有晶圆级方法的独特性能是在封装内没有采用(圆片级)键合技术。其是集BGA/CSP、倒装芯片和晶圆处理的经济性优点于一体,使其成为一种低成本的封装方法。

新的和改良的微电子系统要求更加复杂的器件,由于板上的子系统布线方面的因素,这类器件会限制性能。堆栈的各塑料封装不仅有成本高的缺点,而且不能够为实现缩小整体封装尺寸和像电阻、电容、电感和滤波器这样的无源组件的集成提供有效的方法。3D系统集成提供了一种可以克服这些缺点的技术。

采用倒装芯片进行垂直集成要求有一个重新布局轨迹的基体芯片,使其与二个芯片的I/O布局匹配。这样,就能够使倒装芯片的性能优点与集成到重新布局层中的无源组件的选择相结合。图2所示是在重新布局的IC焊盘的第二个硅芯片上装有倒装芯片的微控制器的堆栈式FC-WLP。从基体芯片到WLCSP基板的互连是使用线焊的方法完成的。

在这种方法中,晶圆级上的功能基体芯片被用作第二个芯片的倒装芯片键合的有源基板。使用共晶或无铅焊料球实现电子和机械互连,其方法是采用电镀技术沉积无铅焊料。将基体芯片重新布局在可焊的UBM

的面数组。重新布局是由电镀铜轨迹达到低电氘率。

使用低K成像的BCB实现介质隔离

目前,晶圆级封装正向更广泛的应用领域过渡:MEMS和MOEMS乃至被应用于生物医学领域。

1995年,Shellcase公司将用于光学组件的WLP应用于两块平行玻璃板之间的芯片密封。外部焊盘扩充到芯片的划线。

然后,将晶圆的有源面胶粘到玻璃板,使晶圆的厚度减薄到100μm。将第二块玻璃板胶粘到晶圆的反面,并将其局部锯开,使延长的焊盘裸露出来。操作员在UBM焊盘的数组面上进行镀覆,粘附焊料球,通过切片使最终的晶圆定位。在这个封装中的芯片的有源面有通路。

Schott电子封装公司已推出了以光学应用为重点的新的封装技术。光学封装和多数MEMS封装必须解决一个最基本的问题,即当将SMT组装技术应用于器件中时:必须使传感器表面与环境相互作用而不会出现由于封装所造成的任何限制,同时,保护传感器器件不受环境的影响。

如果传感器的有源面是在器件的一面,而用于互连的栅数组触点布设在图像传感器芯片反面的话,用于传感器的WLP是可制造的。硅-导通孔-触点对于这种方法来说是至关重要的。这种方法对以光学应用为重点的新的封装技术是一种将WLP和MEMS工艺技术智能的组合,是Schott 电子封装公司所获得的结果,而且柏林的Fraunhofer IZM公司为生产进行的共同深层次开发。这种新技术的特性是在完成了低成本组装后能够完全接触到传感器前面的硅-导通孔-触点。因此,是可以采用晶圆级封装的,因为传感器的有源面是在键合到玻璃晶圆器件的一面和在底部对互连的栅数组触点重新布局。

基本工艺步骤是将传感器晶圆键合到玻璃晶圆上,研磨传感器晶圆,在硅中蚀刻导通孔,以便在反面开出一个焊盘,采用喷涂的方法,在反面重新布局触点,进行深层金属板印刷,最后植球。所有的工艺步骤都是高产量的全自动生产。像CCD这样的光学传感器的性能没有变化。

这种新的高可靠性技术将会进一步降低传感器的封装成本,为客户或汽车产品市场开发出一种新的应用方法。还开发出了晶圆级封装的一个新的应用领域。可移植的无线中枢神经界面这种新的封装理念正在开发中。完全集成的、无线中枢神经记录器件将使患者从与联机相关的感染和障碍的风险中解脱出来,允许接口节点网络穿过中心和外围神经系统分布。长期可移植的无线神经中枢界面要求在湿电化学环境下感应、数据处理、通讯和操作功率的生物配伍和长期稳定的高密度集成。此项研究的目的是为下一代无线犹他神经中枢界面的硅聚酰亚胺、陶瓷和SMD组件的堆栈混合组装开发一种生物配伍晶圆级集成和互连技术。

晶圆级封装的未来趋势

使用无铅和细间距凸点的晶圆级封装(WLP)在全球WLP的市场需求中所占份额还较小。尽管根据国际半导体技术蓝图(ITRS)预测:到2009年,凸点间的间距(相邻凸点中心到中心的距离)为100mm。但对于量产的凸点制造商来说,目前市场对间距<100mm凸点的需求量非常低。例如,焊料凸点的先导者IBM,仍在许多产品中使用间距为220mm的C4凸点技术。对细间距互连来说,目前一个很小但增长迅速的应用领域是在高密度象素探测器数组上的应用。与此同时,很多市场和实际应用对无铅焊料的需求也呈快速增长态势。大量汽车电子产品和手机的OEM供货商发现,客户对于无铅产品的需求正持续增长。

结论

随着越来越多晶圆焊料凸点专业厂家将焊膏印刷工艺用于WLP封装,批量压印技术开始在半导体封装领域广泛普及。然而,大型EMS企业也走进了WLP领域。封装和板卡之间的边界,以及封装与组装工艺之间的边界日渐模糊,迫使企业必须具备晶圆级和芯片级工艺技术来为客户服务。当然,这些企业对精密丝网印刷工艺已很熟悉,多年来一直采用这种工艺技术进行器件贴装前的焊膏涂敷。因此,将印刷技术转向WLP工艺相对比较容易。

在十年内,晶圆级封装在半导体工业中的基础结构已发生变化。集成的无源组件、3D集成和MEMS/MO EMS采用了可靠的WLP理念。3D集成系统在与降低了互连长度结合时对板子的空间要求小,为高频应用提供了较小的寄生效应。集成的无源组件将进一步推动着WLP向前发展。因此,WLP将向着SiP方向发展。因为工艺技术、工艺设备和材料以及人们通常的思维方式在许多方面达成了共识,WLP和SiP在业界的应用将会从倒装芯片和晶圆凸点植球基础结构方面受益,目前正以惊人的步伐向前发展。此外,WLP 必须转变成复杂的系统集成和实现无铅化,以迎接快速发展的半导体的需求和满足客户日益提高的功能性需求。

晶圆封装测试工序和半导体制造工艺流程

晶圆封装测试工序和半导体制造工艺流程 A.晶圆封装测试工序 一、 IC检测 1. 缺陷检查Defect Inspection 2. DR-SEM(Defect Review Scanning Electron Microscopy) 用来检测出晶圆上是否有瑕疵,主要是微尘粒子、刮痕、残留物等问题。此外,对已印有电路图案的图案晶圆成品而言,则需要进行深次微米范围之瑕疵检测。一般来说,图案晶圆检测系统系以白光或雷射光来照射晶圆表面。再由一或多组侦测器接收自晶圆表面绕射出来的光线,并将该影像交由高功能软件进行底层图案消除,以辨识并发现瑕疵。 3. CD-SEM(Critical Dimensioin Measurement) 对蚀刻后的图案作精确的尺寸检测。 二、 IC封装 1. 构装(Packaging) IC构装依使用材料可分为陶瓷(ceramic)及塑胶(plastic)两种,而目前商业应用上则以塑胶构装为主。以塑胶构装中打线接合为例,其步骤依序为晶片切割(die saw)、黏晶(die mount / die bond)、焊线(wire bond)、封胶(mold)、剪切/成形(trim / form)、印字(mark)、电镀(plating)及检验(inspection)等。 (1) 晶片切割(die saw) 晶片切割之目的为将前制程加工完成之晶圆上一颗颗之晶粒(die)切割分离。 举例来说:以0.2微米制程技术生产,每片八寸晶圆上可制作近六百颗以上的64M 微量。

欲进行晶片切割,首先必须进行晶圆黏片,而后再送至晶片切割机上进行切割。切割完后之晶粒井然有序排列于胶带上,而框架的支撐避免了胶带的皱褶与晶粒之相互碰撞。 (2) 黏晶(die mount / die bond) 黏晶之目的乃将一颗颗之晶粒置于导线架上并以银胶(epoxy)粘着固定。黏晶完成后之导线架则经由传输设备送至弹匣(magazine)内,以送至下一制程进行焊线。 (3) 焊线(wire bond) IC构装制程(Packaging)则是利用塑胶或陶瓷包装晶粒与配线以成集成电路(Integrated Circuit;简称IC),此制程的目的是为了制造出所生产的电路的保护层,避免电路受到机械性刮伤或是高温破坏。最后整个集成电路的周围会向外拉出脚架(Pin),称之为打线,作为与外界电路板连接之用。 (4) 封胶(mold) 封胶之主要目的为防止湿气由外部侵入、以机械方式支持导线、內部产生热量之去除及提供能够手持之形体。其过程为将导线架置于框架上并预热,再将框架置于压模机上的构装模上,再以树脂充填并待硬化。 (5) 剪切/成形(trim / form) 剪切之目的为将导线架上构装完成之晶粒独立分开,并把不需要的连接用材料及部份凸出之树脂切除(dejunk)。成形之目的则是将外引脚压成各种预先设计好之形状,以便于装置于电路板上使用。剪切与成形主要由一部冲压机配上多套不同制程之模具,加上进料及出料机构所組成。 (6) 印字(mark)及电镀(plating) 印字乃将字体印于构装完的胶体之上,其目的在于注明商品之规格及制造者等资讯。

晶圆级封装产业

晶圆级封装产业(WLP) 晶圆级封装产业(WLP),晶圆级封装产业(WLP)是什么意思 一、晶圆级封装(Wafer Level Packaging)简介晶圆级封装(WLP,Wafer Level Package) 的一般定义为直接在晶圆上进行大多数或是全部的封装测试程序,之后再进行切割(singulation)制成单颗组件。而重新分配(redistribution)与凸块(bumping)技术为其I/O绕线的一般选择。WLP 一、晶圆级封装(Wafer Level Packaging)简介 晶圆级封装(WLP,Wafer Level Package) 的一般定义为直接在晶圆上进行大多数或是全部的封装测试程序,之后再进行切割(singulation)制成单颗组件。而重新分配(redistribution)与凸块(bumping)技术为其I/O绕线的一般选择。WLP封装具有较小封装尺寸(CSP)与较佳电性表现的优势,目前多用于低脚数消费性IC的封装应用(轻薄短小)。 晶圆级封装(WLP)简介 常见的WLP封装绕线方式如下:1. Redistribution (Thin film), 2. Encapsulated Glass substrate, 3. Gold stud/Copper post, 4. Flex Tape等。此外,传统的WLP封装多采用Fan-in 型态,但是伴随IC信号输出pin 数目增加,对ball pitch的要求趋于严格,加上部分组件对于封装后尺寸以及信号输出脚位位置的调整需求,因此变化衍生出Fan-out 与Fan-in + Fan-out 等各式新型WLP封装型态,其制程概念甚至跳脱传统WLP 封装,目前德商英飞凌与台商育霈均已经发展相关技术。 二、WLP的主要应用领域 整体而言,WLP的主要应用范围为Analog IC(累比IC)、PA/RF(手机放大器与前端模块)与CIS(CMOS Ima ge Sensor)等各式半导体产品,其需求主要来自于可携式产品(iPod, iPhone)对轻薄短小的特性需求,而部分NOR Flash/SRAM也采用WLP封装。此外,基于电气性能考虑,DDR III考虑采用WLP或FC封装,惟目前JEDEC仍未制定最终规格(注:至目前为止,Hynix, Samsung与Elpida已发表DDR III产品仍采F BGA封装),至于SiP应用则属于长期发展目标。此外,采用塑料封装型态(如PBGA)因其molding compo und 会对MEMS组件的可动部份与光学传感器(optical sensors)造成损害,因此MEMS组件也多采用WLP

电子封装技术发展现状及趋势

电子封装技术发展现状及趋势 摘要 电子封装技术是系统封装技术的重要内容,是系统封装技术的重要技术基础。它要求在最小影响电子芯片电气性能的同时对这些芯片提供保护、供电、冷却、并提供外部世界的电气与机械联系等。本文将从发展现状和未来发展趋势两个方面对当前电子封装技术加以阐述,使大家对封装技术的重要性及其意义有大致的了解。 引言 集成电路芯片一旦设计出来就包含了设计者所设计的一切功能,而不合适的封装会使其性能下降,除此之外,经过良好封装的集成电路芯片有许多好处,比如可对集成电路芯片加以保护、容易进行性能测试、容易传输、容易检修等。因此对各类集成电路芯片来说封装是必不可少的。现今集成电路晶圆的特征线宽进入微纳电子时代,芯片特征尺寸不断缩小,必然会促使集成电路的功能向着更高更强的方向发展,这就使得电子封装的设计和制造技术不断向前发展。近年来,封装技术已成为半导体行业关注的焦点之一,各种封装方法层出不穷,实现了更高层次的封装集成。本文正是要从封装角度来介绍当前电子技术发展现状及趋势。

正文 近年来,我国的封装产业在不断地发展。一方面,境外半导体制造商以及封装代工业纷纷将其封装产能转移至中国,拉动了封装产业规模的迅速扩大;另一方面,国内芯片制造规模的不断扩大,也极大地推动封装产业的高速成长。但虽然如此,IC的产业规模与市场规模之比始终未超过20%,依旧是主要依靠进口来满足国内需求。因此,只有掌握先进的技术,不断扩大产业规模,将国内IC产业国际化、品牌化,才能使我国的IC产业逐渐走到世界前列。 新型封装材料与技术推动封装发展,其重点直接放在削减生产供应链的成本方面,创新性封装设计和制作技术的研发倍受关注,WLP 设计与TSV技术以及多芯片和芯片堆叠领域的新技术、关键技术产业化开发呈井喷式增长态势,推动高密度封测产业以前所未有的速度向着更长远的目标发展。 大体上说,电子封装表现出以下几种发展趋势:(1)电子封装将由有封装向少封装和无封装方向发展;(2)芯片直接贴装(DAC)技术,特别是其中的倒装焊(FCB)技术将成为电子封装的主流形式;(3)三维(3D)封装技术将成为实现电子整机系统功能的有效途径;(4)无源元件将逐步走向集成化;(5)系统级封装(SOP或SIP)将成为新世纪重点发展的微电子封装技术。一种典型的SOP——单级集成模块(SLIM)正被大力研发;(6)圆片级封装(WLP)技术将高速发展;(7)微电子机械系统(MEMS)和微光机电系统(MOEMS)正方兴未艾,它们都是微电子技术的拓展与延伸,是集成电子技术与精密

什么是晶圆级晶片尺寸封装

什么是晶圆级晶片尺寸封装(Wafer Level Chip Scale Packaging) 1. 晶圆级晶片尺寸封装(Wafer Level Chip Scale Packaging)是先在整片晶圆上进行封装和测试,然后经切割并将IC直接用机台以pick up & flip方式将其放置于Carrier tape中,并以Cover tape保护好后,提供后段SMT (Surface Mounting technology)直接以机台将该IC自Carrier tape取料后,置放于PCB上。 WLCSP选用较大的锡铅球来形成接点藉以进行电性导通,其目的是增加元件与基板底材之间的距离,进而降低并承受来自于基板与元件间因热膨胀差异产生的应力,增加元件的可靠性。利用重分布层技术则可以让锡球的间距作有效率的安排,设计成矩阵式排列(grid array)。采用晶圆制造的制程及电镀技术取代现有打金线及机械灌胶封模的制程,不需导线架或基板。晶圆级封装只有晶粒般尺寸,且有较好的电性效能,因系以每批或每片晶片来生产, 故能享有较低之生产成本。 2.特点:

WLCSP 少掉基材、铜箔等,使其以晶圆形态进行研磨、切割后完成的IC 厚度和一般QFP 、BGA……等等比较起来为最薄、最小、最轻,较符合未来产品轻、薄之需求;且因其不需再进行封装,即可进行后段SMT 制程,故其成本价格可以较一般传统封装为低。 ● 封装技术比较: 封装方式 优 点 缺 点 传统封装(QFP 、BGA ) 1. 技术成熟 2. 制程稳定 1. 无法达到未来细间距要求 2. 制程较复杂 3. 完成的IC 成本高 晶圆级晶片尺寸封装 1. 尺寸小 2. 成本低 3. 简化制程 4. 可达Fine Pitch 要求 1. I/O 数少(<100) 3.产品应用面: 3.1 Power supply (PMIC/PMU, DC/DC converters, MOSFET' s,...) 3.2 Optoelectronic device 3.3 Connectivity (Bluetooth, WLAN) 3.4 Other features (FM, GPS, Camera) 4.生产流程简介

晶圆封装测试工序和半导体制造工艺流程

A.晶圆封装测试工序 一、IC检测 1. 缺陷检查Defect Inspection 2. DR-SEM(Defect Review Scanning Electron Microscopy) 用来检测出晶圆上是否有瑕疵,主要是微尘粒子、刮痕、残留物等问题。此外,对已印有电路图案的图案晶圆成品而言,则需要进行深次微米范围之瑕疵检测。一般来说,图案晶圆检测系统系以白光或雷射光来照射晶圆表面。再由一或多组侦测器接收自晶圆表面绕射出来的光线,并将该影像交由高功能软件进行底层图案消除,以辨识并发现瑕疵。 3. CD-SEM(Critical Dimensioin Measurement) 对蚀刻后的图案作精确的尺寸检测。 二、IC封装 1. 构装(Packaging) IC构装依使用材料可分为陶瓷(ceramic)及塑胶(plastic)两种,而目前商业应用上则以塑胶构装为主。以塑胶构装中打线接合为例,其步骤依序为晶片切割(die saw)、黏晶(die mount / die bond)、焊线(wire bond)、封胶(mold)、剪切/成形(trim / form)、印字(mark)、电镀(plating)及检验(inspection)等。 (1) 晶片切割(die saw) 晶片切割之目的为将前制程加工完成之晶圆上一颗颗之晶粒(die)切割分离。举例来说:以0.2微米制程技术生产,每片八寸晶圆上可制作近六百颗以上的64M微量。 欲进行晶片切割,首先必须进行晶圆黏片,而后再送至晶片切割机上进行切割。切割完后之晶粒井然有序排列于胶带上,而框架的支撐避免了胶带的皱褶与晶粒之相互碰撞。 (2) 黏晶(die mount / die bond) 黏晶之目的乃将一颗颗之晶粒置于导线架上并以银胶(epoxy)粘着固定。黏晶完成后之导线架则经由传输设备送至弹匣(magazine)内,以送至下一制程进行焊线。 (3) 焊线(wire bond) IC构装制程(Packaging)则是利用塑胶或陶瓷包装晶粒与配线以成集成电路(Integrated Circuit;简称IC),此制程的目的是为了制造出所生产的电路的保护层,避免电路受到机械性刮伤或是高温破坏。最后整个集成电路的周围会向外拉出脚架(Pin),称之为打线,作为与外界电路板连接之用。

集成电路封装的发展现状及趋势

集成电路封装的发展现 状及趋势 公司内部档案编码:[OPPTR-OPPT28-OPPTL98-OPPNN08]

序号:39 集成电路封装的发展现状及趋势 姓名:张荣辰 学号: 班级:电科本1303 科目:微电子学概论 二〇一五年 12 月13 日

集成电路封装的发展现状及趋势 摘要: 随着全球集成电路行业的不断发展,集成度越来越高,芯片的尺寸不断缩小,集成电路封装技术也在不断地向前发展,封装产业也在不断更新换代。 我国集成电路行业起步较晚,国家大力促进科学技术和人才培养,重点扶持科学技术改革和创新,集成电路行业发展迅猛。而集成电路芯片的封装作为集成电路制造的重要环节,集成电路芯片封装业同样发展迅猛。得益于我国的地缘和成本优势,依靠广大市场潜力和人才发展,集成电路封装在我国拥有得天独厚的发展条件,已成为我国集成电路行业重要的组成部分,我国优先发展的就是集成电路封装。近年来国外半导体公司也向中国转移封装测试产能,我国的集成电路封装发展具有巨大的潜力。下面就集成电路封装的发展现状及未来的发展趋势进行论述。 关键词:集成电路封装、封装产业发展现状、集成电路封装发展趋势。 一、引言 晶体管的问世和集成电路芯片的出现,改写了电子工程的历史。这些半导体元器件的性能高,并且多功能、多规格。但是这些元器件也有细小易碎的缺点。为了充分发挥半导体元器件的功能,需要对其进行密封、扩大,以实现与外电路可靠的电气连接并得到有效的机械、绝缘等

方面的保护,防止外力或环境因素导致的破坏。“封装”的概念正事在此基础上出现的。 二、集成电路封装的概述 集成电路芯片封装(Packaging,PKG)是指利用膜技术及微细加工技术,将芯片及其他要素在框架或基板上布置、粘贴固定及连线,引出接线端并通过可塑性绝缘介质灌封固定,构成整体立体结构的工艺。此概念称为狭义的封装。 集成电路封装的目的,在于保护芯片不受或少受外界环境的影响,并为之提供一个良好的工作条件,以使集成电路具有稳定、正常的功能。封装为芯片提供了一种保护,人们平时所看到的电子设备如计算机、家用电器、通信设备等中的集成电路芯片都是封装好的,没有封装的集成电路芯片一般是不能直接使用的。 集成电路封装的种类按照外形、尺寸、结构分类可分为引脚插入型、贴片型和高级封装。 引脚插入型有DIP、SIP、S-DIP、SK-DIP、PGA DIP:双列直插式封装;引脚在芯片两侧排列,引脚节距,有利于散热,电气性好。 SIP:单列直插式封装;引脚在芯片单侧排列,引脚节距等特征与DIP基本相同。

光刻和晶圆级键合技术在3D互连中的研究

光刻和晶圆级键合技术在3D互连中的研究 作者:Margarete Zoberbier、Erwin Hell、Kathy Cook、Marc Hennemayer、Dr.-Ing. Barbara Neuber t,SUSS MicroTec 日益增长的消费类电子产品市场正在推动当今半导体技术的不断创新发展。各种应用对增加集成度、降低功耗和减小外形因数的要求不断提高,促使众多结合了不同技术的新结构应运而生,从而又催生出诸多不同的封装方法,因此可在最小的空间内封装最多的功能。正因如此,三维集成被认为是下一代的封装方案。 本文将探讨与三维互连技术相关的一些光刻挑战。还将讨论三维封装使用的晶圆键合技术、所面临的各种挑战、有效的解决方案及未来发展趋势。 多种多样的三维封装技术 为了适应更小引脚、更短互连和更高性能的要求,目前已开发出系统封装(SiP)、系统芯片(SoC)和封装系统(SoP)等许多不同的三维封装方案。SiP即“单封装系统”,它是在一个IC封装中装有多个引线键合或倒装芯片的多功能系统或子系统。无源元件、SAW/BA W滤波器、预封装IC、接头和微机械部件等其他元件都安装在母板上。这一技术造就了一种外形因数相对较小的堆叠式芯片封装方案。 SoC可以将所有不同的功能块,如处理器、嵌入式存储器、逻辑心和模拟电路等以单片集成的方式装在一起。在一块半导体芯片上集成系统设计需要这些功能块来实现。通常,So C设计与之所取代的多芯片系统相比,它的功耗更小,成本更低,可靠性更高。而且由于系统中需要的封装更少,因而组装成本也会有所降低。 SoP采用穿透通孔和高密度布线以实现更高的小型化。它是一种将整个系统安装在一个芯片尺寸封装上的新兴的微电子技术。过去,“系统”往往是一些容纳了数百个元件的笨重的盒子,而SoP可以将系统的计算、通信和消费电子功能全部在一块芯片上完成,从而节约了互连时间,减少了热量的产生。 最近穿透硅通孔(TSV)得到迅速发展,已成为三维集成和晶圆级封装(WLP)的关键技术之一。三维TSV已显现出有朝一日取代引线键合技术的潜力,因此它可以使封装尺寸进

晶圆级封装WLP优势

晶圆级封装W L P优势 The Standardization Office was revised on the afternoon of December 13, 2020

晶圆级封装(WLP)优势 晶圆级封装(WLP)以BGA技术为基础,是一种经过改进和提高的CSP(芯片级封装),充分体现了BGA、CSP的技术优势。它具有许多独特的优点。 晶圆级封装(Wafer Level Package,WLP)采用传统的IC工艺一次性完成后道几乎所有的步骤,包括装片、电连接、封装、测试、老化,所有过程均在晶圆加工过程中完成,之后再划片,划完的单个芯片即是已经封装好的成品;然后利用该芯片成品上的焊球阵列,倒装焊到PCB板上实现组装。WLP的封装面积与芯片面积比为1:1,而且标准工艺封装成本低,便于晶圆级测试和老化。 晶圆级封装以BGA技术为基础,是一种经过改进和提高的CSP,充分体现了BGA、CSP的技术优势。它具有许多独特的优点: (1)封装加工效率高,它以晶圆形式的批量生产工艺进行制造; (2)具有倒装芯片封装的优点,即轻、薄、短、小; 图5 WLP的尺寸优势 (3)晶圆级封装生产设施费用低,可充分利用晶圆的制造设备,无须投资另建封装生产线; (4)晶圆级封装的芯片设计和封装设计可以统一考虑、同时进行,这将提高设计效率,减少设计费用; (5)晶圆级封装从芯片制造、封装到产品发往用户的整个过程中,中间环节大大减少,周期缩短很多,这必将导致成本的降低;

(6)晶圆级封装的成本与每个晶圆上的芯片数量密切相关,晶圆上的芯片数越多,晶圆级封装的成本也越低。晶圆级封装是尺寸最小的低成本封装。晶圆级封装技术是真正意义上的批量生产芯片封装技术。 WLP的优势在于它是一种适用于更小型集成电路的芯片级封装(CSP)技术,由于在晶圆级采用并行封装和电子测试技术,在提高产量的同时显著减少芯片面积。由于在晶圆级采用并行操作进行芯片连接,因此可以大大降低每个I/O 的成本。此外,采用简化的晶圆级测试程序将会进一步降低成本。利用晶圆级封装可以在晶圆级实现芯片的封装与测试。

晶圆级封装(WLP)优势

晶圆级封装(WLP)优势 晶圆级封装(WLP)以BGA技术为基础,是一种经过改进和提高的CSP(芯片级封装),充分体现了BGA、CSP的技术优势。它具有许多独特的优点。 晶圆级封装(Wafer Level Package,WLP)采用传统的IC工艺一次性完成后道几乎所有的步骤,包括装片、电连接、封装、测试、老化,所有过程均在晶圆加工过程中完成,之后再划片,划完的单个芯片即是已经封装好的成品;然后利用该芯片成品上的焊球阵列,倒装焊到PCB板上实现组装。WLP的封装面积与芯片面积比为1:1,而且标准工艺封装成本低,便于晶圆级测试和老化。 晶圆级封装以BGA技术为基础,是一种经过改进和提高的CSP,充分体现了BGA、CSP的技术优势。它具有许多独特的优点: (1)封装加工效率高,它以晶圆形式的批量生产工艺进行制造; (2)具有倒装芯片封装的优点,即轻、薄、短、小; 图5 WLP的尺寸优势 (3)晶圆级封装生产设施费用低,可充分利用晶圆的制造设备,无须投资另建封装生产线; (4)晶圆级封装的芯片设计和封装设计可以统一考虑、同时进行,这将提高设计效率,减少设计费用; (5)晶圆级封装从芯片制造、封装到产品发往用户的整个过程中,中间环节大大减少,周期缩短很多,这必将导致成本的降低;

(6)晶圆级封装的成本与每个晶圆上的芯片数量密切相关,晶圆上的芯片数越多,晶圆级封装的成本也越低。晶圆级封装是尺寸最小的低成本封装。晶圆级封装技术是真正意义上的批量生产芯片封装技术。 WLP的优势在于它是一种适用于更小型集成电路的芯片级封装(CSP)技术,由于在晶圆级采用并行封装和电子测试技术,在提高产量的同时显著减少芯片面积。由于在晶圆级采用并行操作进行芯片连接,因此可以大大降低每个I/O的成本。此外,采用简化的晶圆级测试程序将会进一步降低成本。利用晶圆级封装可以在晶圆级实现芯片的封装与测试。 (注:文档可能无法思考全面,请浏览后下载,供参考。可复制、编制,期待你的好评与关注)

晶圆封装测试工序和半导体制造工艺流程_百度文库(精)

晶圆封装测试工序和半导体制造工艺流程.txt-两个人同时犯了错,站出来承担的那一方叫宽容,另一方欠下的债,早晚都要还。-不爱就不爱,别他妈的说我们合不来。A.晶圆封装测试工序 一、 IC检测 1. 缺陷检查Defect Inspection 2. DR-SEM(Defect Review Scanning Electron Microscopy 用来检测出晶圆上是否有瑕疵,主要是微尘粒子、刮痕、残留物等问题。此外,对已印有电路图案的图案晶圆成品而言,则需要进行深次微米范围之瑕疵检测。一般来说,图案晶圆检测系统系以白光或雷射光来照射晶圆表面。再由一或多组侦测器接收自晶圆表面绕射出来的光线,并将该影像交由高功能软件进行底层图案消除,以辨识并发现瑕疵。 3. CD-SEM(Critical Dimensioin Measurement 对蚀刻后的图案作精确的尺寸检测。 二、 IC封装 1. 构装(Packaging) IC构装依使用材料可分为陶瓷(ceramic)及塑胶(plastic)两种,而目前商业应用上则以塑胶构装为主。以塑胶构装中打线接合为例,其步骤依序为晶片切割(die saw)、黏晶(die mount / die bond)、焊线(wire bond)、封胶(mold)、剪切/成形(trim / form)、印字(mark)、电镀(plating)及检验(inspection)等。 (1 晶片切割(die saw) 晶片切割之目的为将前制程加工完成之晶圆上一颗颗之晶粒(die)切割分离。举例来说:以0.2微米制程技术生产,每片八寸晶圆上可制作近六百颗以上的64M微量。 欲进行晶片切割,首先必须进行晶圆黏片,而后再送至晶片切割机上进行切割。切割完后之晶粒井然有序排列于胶带上,而框架的支撐避免了胶带的皱褶与晶粒之相互碰撞。 (2 黏晶(die mount / die bond) 黏晶之目的乃将一颗颗之晶粒置于导线架上并以银胶(epoxy)粘着固定。黏晶完成后之导线架则经由传输设备送至弹匣(magazine)内,以送至下一制程进行焊线。 (3 焊线(wire bond) IC构装制程(Packaging)则是利用塑胶或陶瓷包装晶粒与配线以成集成电路(Integrated Circuit;简称IC),此制程的目的是为了制造出所生产的电路的保护层,避免电路受到机械性刮伤或是高温破坏。最后整个集成电路的周围会向外拉出脚架(Pin),称之为打线,作为与外界电路板连接之用。 (4 封胶(mold)

晶圆级封装技术的发展现状

晶圆级封装技术的发展现状 2016-04-18 12:36来源:内江洛伯尔材料科技有限公司作者:研发部 晶圆级封装随着IC芯片技术的发展,芯片封装技术也不断达到新的水平,目前已可在单芯片上实现系统的集成。 在众多的新型封装技术中,晶圆级封装技术最具创新性、最受世人瞩目,是封装技术取得革命性突破的标志。晶圆级封装技术的构思是在整片晶圆上进行CSP封装技术的制造,也就是在晶圆级基本完成了大部分的封装工作。因此,晶圆级封装结构,则可省略覆晶技术点胶的步骤,目前可采用弹性体或是类弹性体来抵消应力,而这些弹性体的制程,可在整片晶圆上完成,因此省去了对一个个组件分别点胶的复杂制程。方形晶圆封装技术的设计理念,首先为增加组件与底材之间的距离,亦即选用更大的锡铅焊料球实现导电性,现有的晶圆级封装技术,采用重新布局技术来加大锡铅焊料球的间距,以达到加大锡铅焊料球体积的需求,进而降低并承受由基板与组件之间热膨胀差异而产生的应力,提高组件的可靠性。 晶圆级封装和晶圆级芯片尺寸封装(WLCSP)是同一概念,它是芯片尺寸封装的一个突破性进展,表示的是一类电路封装完成后仍以晶圆形式存在的封装,其流行的主要原因是它可将封装尺寸减小到和IC芯片一样大小以及其加工的成本低,晶圆级封装目前正以惊人的速度增长,其平均年增长率(CAGR)可达210%,推动这种增长的器件主要是集成电路、无源组件、高性能存储器和较少引脚数的器件。 目前有5种成熟的工艺技术可用于晶圆凸点,每种技术各有利弊。其中金线柱焊接凸点和电解或化学镀金焊接凸点主要用于引脚数较少的封装(一般少于40),应用领域包括玻璃覆晶封装(COG)、软膜覆晶封装(COF)和RF模块。由于这类技术材料成本高、工序时间长,因此不适合I/O引脚多的封装件。另一种技术是先置放焊料球,再对预成形的焊料球进行回流焊接,这种技术适用于引脚数多达300的封装件。目前用得最多的两种晶圆凸点工艺是电解或化学电镀焊料,以及使用高精度压印平台的焊膏印刷。 印刷焊膏的优点之一是设备投资少,这使很多晶圆凸点加工制造厂家都能进入该市场,为半导体制造厂家服务。随着WLP逐渐为商业市场所接受,全新的晶圆凸点专业加工服务需求持续迅速增长。的确,大多数晶圆凸点加工厂都以印刷功能为首要条件,并提供一项或多项其它技术。业界许多人士都认为焊膏印刷技术将主导多数晶圆凸点的应用。

电子行业先进封装深度报告

电子行业先进封装深度报告 一、未来先进封装是驱动摩尔定律的核心驱动力 1、半导体产业链和摩尔定律 (1)半导体产业链自上而下分为芯片设计、晶圆代工、封装和测试四个环节。 设计公司研发人员首先完成芯片的寄存器级的逻辑设计和晶体管级的物理设计,验证通过的电路版图交付给代工厂; 晶圆代工厂专门从事半导体晶圆制造生产,接受IC 设计公司委托制造,自身不从事设计,其产品是包含成百上千颗晶粒(每颗晶粒就是一片IC)的晶圆; 封装厂通过多道封装工序引出晶粒I/O 焊盘上的电子信号并制作引脚/焊球,实现芯片与外界的电气互连; 测试环节是IC制造的最后一步,作用是验证IC 是否能按设计功能正常工作。 图:半导体产业链

(2)半导体行业摩尔定律指出,单位面积芯片上集成的晶体管数每隔18 个月增加一倍(芯片面积减小50%),其背后驱动力是行业对高性能、低功耗芯片的不断追求,并导致芯片不断小型化,同时从降低芯片流片成本、节约电路板空间考虑也要求芯片面积缩减。 纳米级工艺制程降低可降低集成电路的工作电压和CMOS 晶体管驱动电流,从而减少功耗,同时小尺寸的器件减小了晶体管和互连线寄生电容,提高了芯片的工作频率和性能。 图:半导体工艺与I/O 密度趋势图

2、从PC →NB →手机/平板→可穿戴设备,半导体产业小型化需求不减 (1)PC、笔记本电脑、手机/平板等传统消费电子产品的工业设计美观性、便携性、功能性以及电池续航时间的消费需求驱动半导体元器件产业不断朝小型化、低功耗方向发展。 (2)未来电子行业的发展方向是可穿戴设备和MEMS(微机电系统),可穿戴设备/MEMS自身产品特性和应用场合(可穿戴设备要求轻薄化和智能化,MEMS工作在微小空间)对半导体元器件小型化的要求进一步加大。 苹果iWatch 包含无线/蓝牙、生物感测、电源管理和微控制器等模块,屏幕表面弯曲且尺寸不超过1.5英寸,电路板芯片布局布线难度增加,同时还需要考虑和iPhone相同的电池使用时间问题,小型低功耗芯片是最好的解决方案; MEMS是集微型传感器和执行器于一体的微型机电系统,广泛应用于消费电子、生物医疗、汽车电子和军工领域,如iPhone/iPad中使用的加速度传感器和陀螺仪,进行精细外科手术必备的微型机器人和汽车发动和刹车系统中使用的压力传感器。 3、晶圆制程接近极限已难驱动摩尔定律

晶圆封装测试工序和半导体制造工艺流程(精)

A.晶圆封装测试工序 一、IC 检测 1.缺陷检查Defect Inspection 2.DR-SEM(Defect Review Scanning Electron Microscopy) 用来检测出晶圆上是否有瑕疵,主要是微尘粒子、刮痕、残留物等问题。此外,对已印有电 路图案的图案晶圆成品而言,则需要进行深次微米范围之瑕疵检测。一般来说,图案晶圆检测系统系以白光或雷射光来照射晶圆表面。再由一或多组侦测器接收自晶圆表面绕射出来的光线,并将该影像交由高功能软件进行底层图案消除,以辨识并发现瑕疵。 3.CD-SEM(Critical Dimensioin Measurement) 对蚀刻后的图案作精确的尺寸检测。 二、IC 封装 1.构装( Packaging ) IC 构装依使用材料可分为陶瓷( ceramic )及塑胶( plastic )两种,而目前商业应用上则以塑胶构装为主。以塑胶构装中打线接合为例,其步骤依序为晶片切割( die saw)、黏晶(die mount / die bond)、焊线(wire bond)、圭寸胶(mold )、剪切/ 成形(trim / form )、印字(mark)、电镀( plating )及检验( inspection )等。 (1)晶片切割( die saw ) 晶片切割之目的为将前制程加工完成之晶圆上一颗颗之晶粒( die )切割分离。举例来说: 以 0.2微米制程技术生产,每片八寸晶圆上可制作近六百颗以上的64M微量。 欲进行晶片切割,首先必须进行晶圆黏片,而后再送至晶片切割机上进行切割。切割完后之 晶粒井然有序排列于胶带上,而框架的支撐避免了胶带的皱褶与晶粒之相互碰撞。 (2)黏晶( die mount / die bond ) 黏晶之目的乃将一颗颗之晶粒置于导线架上并以银胶 ( epoxy )粘着固定。黏晶完成后之导线架则经由传输设备送至弹匣( magazine )内,以送至下一制程进行焊线。 (3)焊线( wire bond ) IC 构装制程( Packaging )则是利用塑胶或陶瓷包装晶粒与配线以成集成电路( Integrated Circuit ;简称IC ),此制程的目的是为了制造出所生产的电路的保护层,避免电路受到机械性刮伤或是高温破坏。最后整个集成电路的周围会向外拉出脚架( Pin ),称之为打线,作为与外界电路板连接之用。

半导体芯片行业全梳理 (附股)

半导体芯片行业全梳理(附股) 去年开始,半导体芯片行业得到了资金的认可,直到现在,仍有很多上市公司被持续爆炒。在信息技术高速发展的今天,大数据是资源,堪比新经济的石油;5G是道路,决定信息的传输速度;芯片是核心,是数据分析的大脑。不管是工业互联网、人工智能、虚拟现实、影音娱乐、汽车数码,新产业的发展都要围绕这三个行业进行,所以大数据、5G 和半导体芯片是工业4.0的根基,是所有新兴行业的根本。今天聊半导体!长期以来,我国集成电路产业都是逆差,严重依赖国外进口,每年进口芯片超2000亿美元。2014年9月,千亿规模的国家集成电路产业基金(以下简称“大基金”)成立,扮演着产业扶持与财务投资的双重角色。目前大基金已成为11家A股上市公司的股东,而且大基金还将参与多家公司的增发而获得股权。大基金代表国家集成电路产业的发展方向,其投资的上市公司值得投资者关注,下面梳理一下大基金持股A股公司情况。国科微:持股15.79%,二股东;三安光电、兆易创新、通富微电、北斗星通:持股超10%;长电科技:9.54%晶方科技:9.32%北方华创:7.5%长川科技:7.5%纳斯达:4.29%同时,大基金将参与长电科技、通富微电、万盛股份、景嘉微、雅克科技、耐威科技的增发,增发完成后,大基金持股情况如下:长电科技:19%通富微

电:15.7%万盛股份:7.41%雅克科技:5.73%此外大基金 还投资了华天科技的子公司,入股士兰微生产线,与巨化股份合作发展电子化学材料。大基金加持的A股公司可以重点关注,但半导体到底是怎样的一个行业,我们简单梳理一下。半导体分为四类产品,分别是集成电路、光电子器件、分立器件和传感器。其中规模最大的是集成电路,市场规模达到2,753 亿美元,占半导体市场的81%,所以有时大家会把半导体行业跟集成电路混为一谈。从半导体产业链上下游来看:半导体产业链上中下游全梳理:上游:IC设计、半导体材料、半导体设备一、IC设计重点关注:兆易创新:国内存储器及MCU芯片产业的龙头企业,主营业务存储芯片是国家战略 支持的IC细分方向。大基金战略入股,公司将成为国家存 储器战略落地的产业平台之一。韦尔股份:模拟芯片龙头。公司是国内鲜有的同时具备强大半导体设计和IC分销实力 的公司,业务模式独特。公司主营业务为半导体分立器件、电源管理IC等半导体这些产品广泛应用于移动通信、车载 电子、安防、网络通信、家用电器等领域。国科微:公司是国家高新技术企业和经工业和信息化部认定的集成电路设 计企业,长期致力于大规模集成电路的设计、研发及销售。在广播电视芯片市场,公司长期保持直播卫星市场的龙头地位,占有绝对的市场份额。弘信电子:高速成长的国内柔性印制电路板(FPC)龙头。公司当前主营FPC研发、设计、