altium designer如何布蛇形线

蛇行等长线布线方法

Altium Designer 6.x 软件更新速度很快,现在都有AD7了,以前一直用99SE,没想到AD6的功能越来越强大了,在操作方面做了很大改进,特别是在布等长线时,蛇行线的布线那是太容易了。

一.设置需要等长的网络组

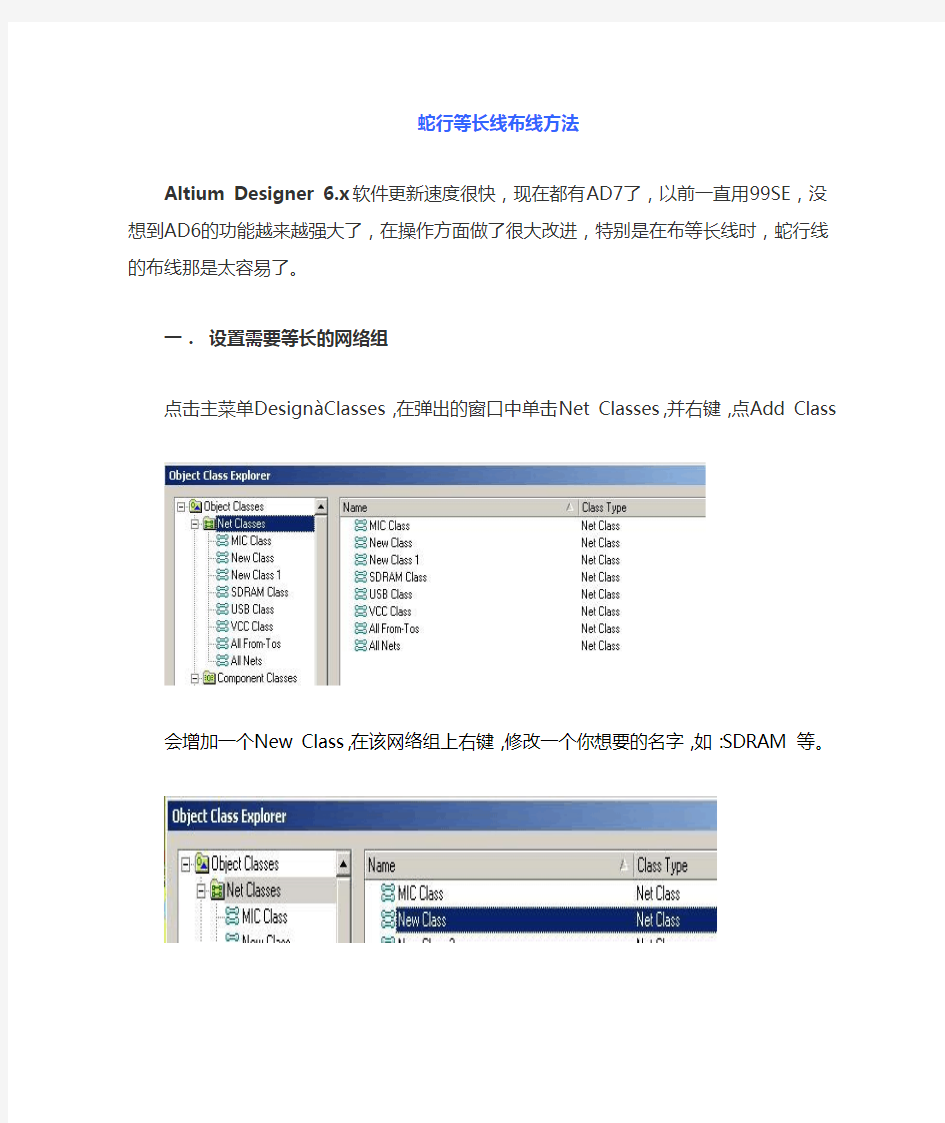

点击主菜单DesignàClasses,在弹出的窗口中单击Net Classes,并右键,点Add

Class

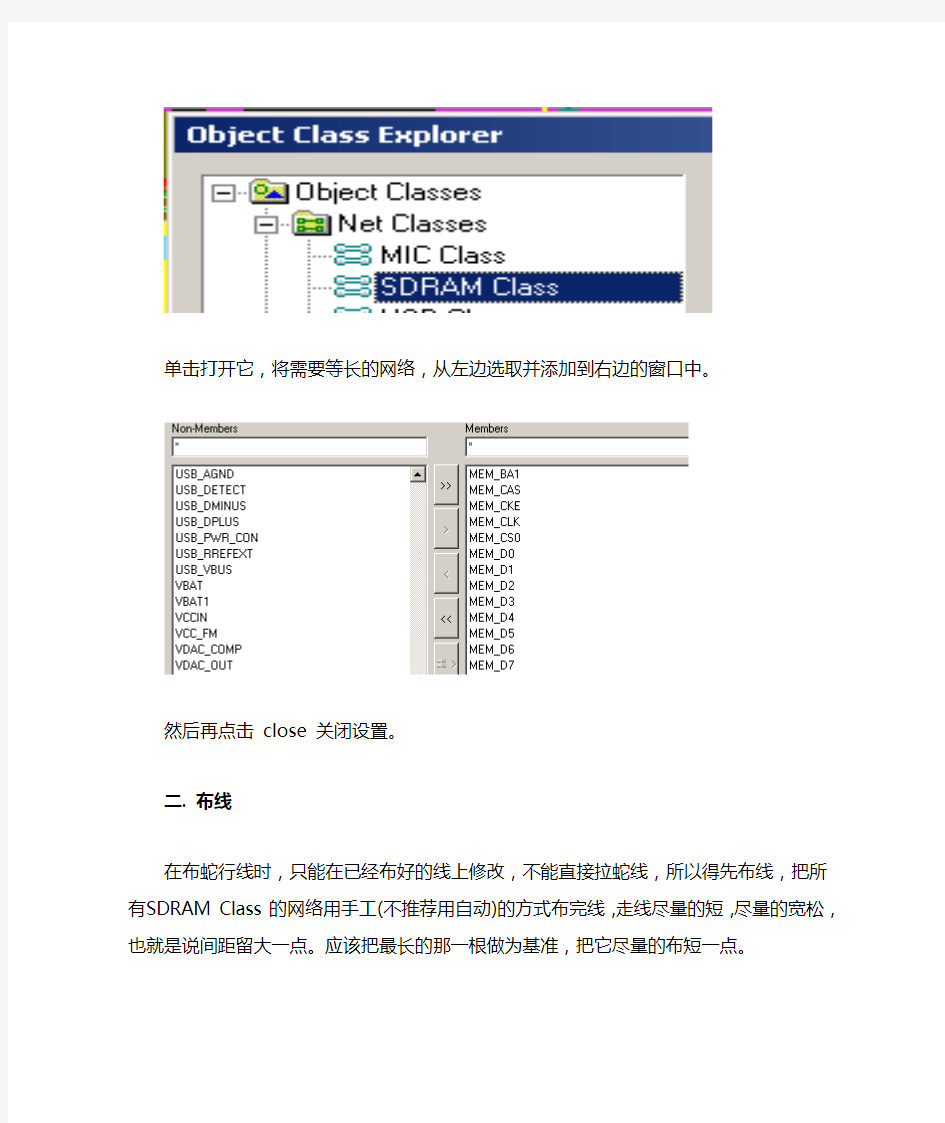

会增加一个New Class,在该网络组上右键,修改一个你想要的名字,如:SDRAM 等。

单击打开它,将需要等长的网络,从左边选取并添加到右边的窗口中。

然后再点击close 关闭设置。

二. 布线

在布蛇行线时,只能在已经布好的线上修改,不能直接拉蛇线,所以得先布线,把所有SDRAM Class 的网络用手工(不推荐用自动)的方式布完线,走线尽量的短,尽量的宽松,也就是说间距留大一点。应该把最长的那一根做为基准,把它尽量的布短一点。

三. 走蛇行线等长

按T ,R键,单击一根走线,再按TAB键,设置一下先

1.选中Form NET 在右边的网络中,选中一根你想要长度的网络,一般选最长的那

根

2.

也就是说,以后的自动等长中,将会以些为基准,所有需等长的线将会跟它一样长。2.蛇行设置

这里为蛇行线的样式,可以根据自己

的需要选择.

2. 布蛇行线的快捷键控制:

在布蛇行线时,按快捷键“1”“2”“3”“4”“,”“。”可以在走线时随时控制蛇行线的形状。

快捷键: 1 与2,改变蛇行线的拐角与弧度。

快捷键: 3 与4 改变蛇行线的宽度。

快捷键:,与。改变蛇行线的幅度。

了解了这些,就可以开始布蛇行线了,单击OK 退出设置,在刚才那条线上,按装走线的方向,

拉动鼠标,一串漂亮的蛇行线就出来了。

蛇行线幅度

步长

幅度递增量

步长递增量

规定了蛇线的长度,在拉蛇线时,就不用在乎到底走了多长,总之,拉到蛇线不再出现为止,

在有些空隙大的地方,就可以按“逗号”与“句号”键来控制幅度的大小。

四. 检查网络长度

布完线后,按R ,L 输出报告,查看网络是否是等长的。

OK,蛇行等长线搞定。

注,另外还可以自动等长,但那样出来的线条很难看,所以还是用手动的好。

PCBLayout中的直角走线、差分走线和蛇形线

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout 得以实现并验证,由此可见,布线在高速PCB 设计中是至关重要的。下面将针对实际布线中可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。 主要从直角走线,差分走线,蛇形线等三个方面来阐述。 1.直角走线 直角走线一般是PCB布线中要求尽量避免的情况,也几乎成为衡量布线好坏的标准之一,那么直角走线究竟会对信号传输产生多大的影响呢?从原理上说,直角走线会使传输线的线宽发生变化,造成阻抗的不连续。其实不光是直角走线,顿角,锐角走线都可能会造成阻抗变化的情况。 直角走线的对信号的影响就是主要体现在三个方面: 一是拐角可以等效为传输线上的容性负载,减缓上升时间; 二是阻抗不连续会造成信号的反射; 三是直角尖端产生的EMI。 传输线的直角带来的寄生电容可以由下面这个经验公式来计算: C=61W(Er)[size=1]1/2[/size]/Z0 在上式中,C 就是指拐角的等效电容(单位:pF),W指走线的宽度(单位:inch),εr 指介质的介电常数,Z0就是传输线的特征阻抗。举个例子,对于一个4Mils的50欧姆传输线(εr为4.3)来说,一个直角带来的电容量大概为0.0101pF,进而可以估算由此引起的上升时间变化量: T10-90%=2.2*C*Z0/2 = 2.2*0.0101*50/2 = 0.556ps 通过计算可以看出,直角走线带来的电容效应是极其微小的。 由于直角走线的线宽增加,该处的阻抗将减小,于是会产生一定的信号反射现象,我们可以根据传输线章节中提到的阻抗计算公式来算出线宽增加后的等效阻抗,然后根据经验公式计算反射系数: ρ=(Zs-Z0)/(Zs+Z0) 一般直角走线导致的阻抗变化在7%-20%之间,因而反射系数最大为0.1左右。而且,从下图可以看到,在W/2线长的时间内传输线阻抗变化到最小,再经过W/2时间又恢复到

PCB蛇形走线

Altium Designer PCB实用技巧拾遗 Ling.Ju 2011.7 -1-

-2- 问题1:AD 布蛇形线方法........................................................................................................................................................................................................................................................................................................................................................................................................................................................33问题2:大电流走线中去除阻焊层........................................................................................................................................................................................................................................................................................................................................................................................................................1010问题3:总线画法......................................................................................................................................................................................................................................13问题4:从原理图到PCB ........................................................................................................................................................................................................................................................................................................................................................................................................................................................1414问题5:走线中换层、操作过孔、操作走线..........................................................................................................................................................................................................................................................................................................................................................................................1717问题6:走线推挤与连线方式快速设置....................................................................................................................................................................................................20问题7:简易图元的PCB 黏贴...................................................................................................................................................................................................................22问题8:复杂图元(:复杂图元(LOGO LOGO LOGO)的)的PCB 制作....................................................................................................................................................................................................23问题9:栅格设置与捕获......................................................................................................................................................................................................................................................................................................................................................................................................................................................2626问题1010:丝印文字反色输出及位置设置:丝印文字反色输出及位置设置..................................................................................................................................................................................................27问题1111:各种:各种:各种~~多边形填充.......................................................................................................................................................................................................................29问题1212::PCB 中高亮选中网络..................................................................................................................................................................................................................30问题1313:单层操作与定制操作:单层操作与定制操作.................................................................................................................................................................................................................32问题1414:多层线的操作:多层线的操作..........................................................................................................................................................................................................................................................................................................................................................................................................................................................4040问题1515:走线切片的操作:走线切片的操作.........................................................................................................................................................................................................................42问题1616:对等差分线的设置与走线:对等差分线的设置与走线....................................................................................................................................................................................................................................................................................................................................................................................................................4545问题1717::3D 显示操作................................................................................................................................................................................................................................................................................................................................................................................................................................................................4848问题1818:快速放大缩小视图 :快速放大缩小视图 (50)

AltiumDesigner使用教程

A l t i u m D e s i g n e r使 用教程 -CAL-FENGHAI.-(YICAI)-Company One1

设计并生成PCB 根据WEBENCH生成的电源原理图,就可以在AltiumDesigner中画出设计电路的原理图和PCB图。 1.Ultra Librarian的安装和使用 1)在TI官网下载并安装Ultral Librarian并安装,下载地址:。 2)在TI官网找到要使用的芯片,在“符号和封装”项目下点击下载CAD文件(后缀 为.bxl),如下图所示: 3)打开Ultral Librarian软件,首先点击“Load Data”装载刚刚下载.bxl文件,在选择“Se lect Tools”中的“Altium Designer”,最后点击“Export to Selected Tools”。如下图所示:

4)随后会生成一个.txt文档,如下图所示。其中红色方框表示生成的PCB库和原理图所 在位置。 5)打开红色方框中的路径,里面有一个“”,用AltiumDesigner打开,如下图所示。

6)双击图中的1,在点击图中的2,会出现以下界面: 7)选择生成Ultral Librarian生成的文件夹中的“.txt”文件,然后点击“Start Import”那么就生 成了所需芯片的封装和原理图的库,只要在原件库中安装即可使用。如下图所示: 注意:这里生成的PCB库和原理图库首次打开可能会没有,解决的方法是先关闭然后再打开就可以了。

2.设计电路原理图 1)打开AD软件,依次选择:文件->新建(new)->工程(project)->PCB工程,在建立 工程之后一定要保存工程。如下图所示: 2)在新建的PCB项目下创建原理图项目(Schematic)。 3)在库中选择相应的原件,拖入原理图,如下图所示:

dxp设计技巧实例笔记(包含蛇形走线)

1)如何使PCB图的背景和边框一致? 按住shift选中所有边框,Design->Board shape->Define from selected objects 2)线条形成回路就自动删除原来的线 解决办法:place line就不会改变原来的。Place route会改变。 3)同一个项目几个原理图的同一个网络,用不同的网络标号,结果生成网络表时用第一个 标注的网络标号。 4)检查PowerPCB印制板图的网络表的方法: 把印制板图生成的网络表转换成protel格式,在protel99里先随便导入一个PCB图,然后import两个网络表,用protel99的网络表-》高级-》菜单-》比较网络表 在DXP里用reports-》report single pin nets检查没有连线的空管脚是否有遗漏。 5)Pb-free Package 无铅 6) 元器件自动编号:Tools >> annotate 7) 材料表:Reports >>bill of materials,或Reports >>simple BOM 8) 测量尺寸:Ctrl+M 9) PROTEL走线时改线宽:按TAB键。 10) QFP封装元器件管脚间距≥0.5mm 11) 反面一般只能放2PIN器件,多PIN器件重量不能超过2克 12) QFP、BGA器件周围3mm不放其他器件 13) 表贴元器件最小0603封装 14) DCP010505BP输入电容用2.2uF/0805封装陶瓷电容,输出电容用一个1uF/0805封装陶瓷 电容和一个10V/10uF电解电容 15) 多上下拉电阻用0603封装电阻,用表贴排阻的话供货厂家少 16) 如何让相同的器件依次编号?先RESET ALL(先打开所有项目文档,在不LOCK状态 下RESET ALL),然后全部LOCK(鼠标右键FIND SIMILATE OBJECT,选勾select matching,选择OPEN DOCUMENT,在INSPECTOR中选择LOCK DESIGNATOR),然后过滤某种器件,解除LOCK,然后用Tools >> annotate对该种器件编号,然后不用(清除过滤和LOCK编好号的器件),直接过滤另外一种器件,解除LOCK,其后步骤同上。 17) 在PowerPCB里导出网络表:File >>Report >>PowerPCB V3.0 Format Netlist 18) Dxp2004点亮网络:编辑(E),选择(S),物理连接(C)快捷键:Ctrl+H 19) 如何将修改应用到多个图纸? 在Find Similar Objects对话框,下面的复选框除了“Create Expression”不选,其他全选,下拉列表选“Open Documents”。在Inspector对话框Include xxx from open documents。 20) Tools >> annotate 里也可以把元器件编号全部复位。 21) PCB图改变连线为任意角度或弧线的快捷方式:shift+空格。每按一次,改变一种连线 方式。 22) 过孔是默认不加阻焊层(绿油)的,可在过孔的属性:Force complete tenting on top 和Force complete tenting on bottom两项中进行选择,打勾即加阻焊层。 23) TOP PASTE:表面意思是指顶层焊膏层,就是说可以用它来制作印刷锡膏的钢网,这 一层只需要露出所有需要贴片焊接的焊盘,并且开孔可能会比实际焊盘小。这一层资料不需要提供给PCB厂。

蛇形走线参数设置

1.简介 蛇形走线是布线中经常使用的一种走线方式。其主要目的就是为了调节延时,满足系统时序设计要求。但是设计者首先要有这样的认识:蛇形走线会破坏信号质量,改变传输时延,布线时要尽量避免使用。但实际设计中,为了保证信号有走过足够的保持时间,或者减小同组信号之间的时间偏移,往往不得不故意进行绕线。 当在长度规则设置下开始走线时,有时需要通过使用蛇形走线以达到所需的走线长度。蛇形走线的示例如图10-60 所示,其中最关键的两个参数就是耦合幅度(Ap) 和耦合距离(Gap)。很明显,信号在蛇形走线上传输时,相互平行的线段之间会发生耦合,呈差模形式,Gap 越小,Ap 越大,则耦合程度也越大。 图10-60 蛇形走线的示例 尽管蛇形走线会引起引起耦合,从而降低信号质量,但是在布线时,蛇形走线对于调节时延和时序是重要的方法。因此在高速信号布线时,可以使用蛇形走线,但是蛇形走线的Ap 和Gap 的设置必须符合信号的要求。在PADS Router 中,可以设置蛇形走线的Ap 和Gap,并且在布线过程中添加蛇形布线。

2.设置蛇形走线的Ap 和Gap 参数 ●执行Tools/Options 菜单命令,或者单击标准工具栏中的Options 图标,系统会弹出选 项对话框,然后选择Routing(布线)选型卡。 ●然后在Routing to length constaints 区域设置蛇形走线参数,如图10-61 所示。 ㊣在Minimum amplitude (幅度)编辑框中将最小值设为20 ,则蛇形走线的幅度最小值 被设置为走线宽度的20 倍。 ㊣在minimum gap(间距)编辑框中将最小值设为2,则蛇形走线的间隔最小值被设置 为走线到拐角间距的2 倍。 ●最后单击OK 按钮完成设置。 注意:在使用蛇形走线时,应该注意以下几个技术要点: 1.尽量增加平行线段的距离S,至少大于3H,H 指信号走线到参考平面的距离。 通俗的说就是绕大弯走线,只要S 足够大,就几乎能完全避免相互之间的耦合效应。 2.减小耦合幅度Lp,当两倍的Lp 时延接近或超出信号上升时间时,产生的串绕将达到饱和。 3.带状线(Strip-Line)或者埋式微带线(Embedded Micro-strip)的蛇形走线引起的信号传输时延小于微带线走线(Micro-strip)。理论上,带状线不会因为差模串扰影响传输速率。 4.高速以及对时序要求较为严格的信号线,尽量不要走蛇形线,尤其不能在小范围内蜿蜒走线。 5.高速PCB 设计中,蛇形走线没有所谓滤波和抗干扰的能力,只可能降低信号质量,所以只作时序匹配之用而无其他目的。 3. 蛇形线的拓扑 对于DDR2和DDR3,其中信号DQ、DM和DQS都是点对点的互联方式,

蛇形线的走线方式

挖掘蛇形线的走线方式 蛇形线是Layout中经常使用的一类走线方式。其主要目的就是为了调节延时,满足系统时序设计要求。设计者首先要有这样的认识:蛇形线会破坏信号质量,改变传输延时,布线时要尽量避免使用。但实际设计中,为了保证信号有足够的保持时间,或者减小同组信号之间的时间偏移,往往不得不故意进行绕线。 那么,蛇形线对信号传输有什么影响呢?走线时要注意些什么呢?其中最关键的两个参数就是平行耦合长度(Lp)和耦合距离(S),如图1-8-21所示。很明显,信号在蛇形走线上传输时,相互平行的线段之间会发生耦合,呈差模形式,S越小,Lp越大,则耦合程度也越大。可能会导致传输延时减小,以及由于串扰而大大降低信号的质量,其机理可以参考第三章对共模和差模串扰的分析。 下面是给Layout工程师处理蛇形线时的几点建议: 1.尽量增加平行线段的距离(S),至少大于3H,H指信号走线到参考平面的距离。通俗的说就是绕大弯走线,只要S 足够大,就几乎能完全避免相互的耦合效应。 2.减小耦合长度Lp,当两倍的Lp延时接近或超过信号上升时间时,产生的串扰将达到饱和。 3.带状线(Strip-Line)或者埋式微带线(Embedded Micro-strip)的蛇形线引起的信号传输延时小于微带走线(Micro-strip)。理论上,带状线不会因为差模串扰影响传输速率。 4.高速以及对时序要求较为严格的信号线,尽量不要走蛇形线,尤其不能在小范围内蜿蜒走线。 5.可以经常采用任意角度的蛇形走线,如图1-8-20中的C结构,能有效的减少相互间的耦合。 6.高速PCB 设计中,蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以只作时序匹配之用而无其它目的。 7.有时可以考虑螺旋走线的方式进行绕线,仿真表明,其效果要优于正常的蛇形走线。

AltiumDesigner教程

快捷键: 快速复制放置元件:按住Shift键并拖动要放置的元件 Q:尺寸单位转换 J+C:查找元件 V+F:显示全屏元件 V+Z:显示上次比例 Ctrl+A:全选 Ctrl+C:复制 Ctrl+V:粘贴 Shift+s:单层显示 Shift+空格:改变走线模式 L:层面设置 G/shift+G/ctrl+shift+G:栅格设置 封装集成库的建立 新建集成库工程File→New→Project→Integrated Library 在集成库工程下新建原理图封装和PCB封装可在File →New→Library中新建,也可鼠标右键点击集成库名添加库文件 绘制需要的原理图封装和PCB封装原理图封装不需要太多尺寸要求,可通过编辑→Jump设置原点在器件中心或任意位置,PCB封装则需要根据实物尺寸绘制,可通过Edit(编辑)→Set Reference(设置参考点)将原点设置在元件中心、Pin1或任意位置(一般将原点设置在PCB封装中心或管脚1上,否则导入PCB图后布局拖动元件时光标可能会跑到离元件很远的地方)。点击Tool →New comment(新元件)可开始下一个元件的绘制。在界面右下方单击Sch →Sch Library/PCB→PCB Library可调出相对的库面板,原理图封装更改元件名字可通过Tools →Rename Comment修改,也可双击元件名称,在弹出的属性框Symbol Reference一栏中修改。PCB封装通过双击封装名字修改。注:单击右下方System→supplier Search(供应商查找),输入元件名称,显示的元件信息可拖动到原理图封装界面的空白处,从而显示在元件属性框内。 确定原理图封装和PCB封装的链接关系在原理图封装界面右下方点击Show Model展开箭头。点击Add Footprint→Browse,在PCB封装库里选择对应的PCB封装(可选择多个),点击OK、OK,就可形成链接关系。 编译点击左下方Project切换到Project,File→Save All,填写各文件名称和要保存的位置,右键点击集成库名称,点击“Compile Intergrated Library ×××” PC B工程的建立 新建PCB工程File→New→Project→PCB Project,右键单击,保存工程。 2.1原理图的绘制 ①新建原理图文件File→New→Schematics(原理图),或右键单击工程名为工程添加新文件,选择原理图。右击文件名保存 ②设置图纸参数Design→Document Options(文档选项),切换到Sheet Options选项卡进行设置,还可直接双击纸张外空白处进入Sheet Options选项卡进行设置 ③调入元件单击界面右侧Library…(库…)可在里面查找放置元件。 注:Edit→Align(对齐)可使选中的元件对齐 注释元件编号:Tools→Annotate Schematics(注释)在弹窗中设置好注释顺序及开始注释的序

PCB设计中蛇形线要点

PCB设计中蛇形线要点 一、直角走线 直角走线一般是PCB布线中要求尽量避免的情况,也几乎成为衡量布线好坏的标准之一,那么直角走线究竟会对信号传输产生多大的影响呢?从原理上说,直角走线会使传输线的线宽发生变化,造成阻抗的不连续。其实不光是直角走线,顿角,锐角走线都可能会造成阻抗变化的情况。直角走线的对信号的影响就是主要体现在三个方面: 1.拐角可以等效为传输线上的容性负载,减缓上升时间; 2.阻抗不连续会造成信号的反射; 3.直角尖端产生的EMI。 传输线的直角带来的寄生电容可以由下面这个经验公式来计算: 在上式中,C就是指拐角的等效电容(单位:pF),W指走线的宽度(单位: 就是传输线的特征阻抗。举个例子,对于一inch),εr指介质的介电常数,Z 个4Mils的50欧姆传输线(εr为4.3)来说,一个直角带来的电容量大概为0.0101pF,进而可以估算由此引起的上升时间变化量: /2 = 2.2*0.0101*50/2 = 0.556ps =2.2*C*Z 通过计算可以看出,直角走线带来的电容效应是极其微小的。 由于直角走线的线宽增加,该处的阻抗将减小,于是会产生一定的信号反射现象,我们可以根据传输线章节中提到的阻抗计算公式来算出线宽增加后的等效阻抗,然后根据经验公式计算反射系数:ρ=(Zs-Z0)/(Zs+Z0),一般直角走线导致的阻抗变化在7%-20%之间,因而反射系数最大为0.1左右。而且,从下图可以看到,在W/2线长的时间内传输线阻抗变化到最小,再经过W/2时间又恢复到正常的阻抗,整个发生阻抗变化的时间极短,往往在10ps之内,这样快而且微小的变化对一般的信号传输来说几乎是可以忽略的。

AD如何走蛇形线

来源:https://www.360docs.net/doc/1810890221.html,/thread-4906766-1-5.html 阿莫电子论坛 第一种方法:先布好线,再改蛇形。 从Tool 里选的Interactive length tuning ,就是要先布好线再改成蛇形, 但实际使用的时候,发现只有这2种蛇形线! (原文件名:111111111.jpg) 想要这种圆弧状的蛇形线,可是就是画不出来!

虽然Tools 下拉中的Interactive length tuning 有 (原文件名:33333333333.jpg) 但实际就是画不出这种形状 原因:左边那个是距离小了, 自动生成不了, 要么把圆弧的半径设小点右边那张也是如此, 另外设成圆弧。

(原文件名:33333333333.JPG) 找到原因了,是倒角半径太小。 调整走线长度的状态下,一直按住数字2.就可以调整成圆弧型。谢谢1L的大侠。 布线完成在走蛇形线可以实时显示长度

第二种方法:布线时直接走蛇形线。 布线时直接走蛇形: 先P->T 布线, 再Shift + A 切换成蛇形走线(ad 里叫Accordions ... 这是P->T 后按` 快捷键时显示的当前可用操作)

(原文件名:2011-07-25 10 25 03.png) 然后按Tab 设置属性, 类型了选用圆弧, Max Amplitude 设置最大的振幅 Gap 就是间隔(不知这么翻译对不) 下面左边是振幅增量, 右边是间隔增量, 后面有用

(原文件名:2011-07-25 10 18 53.png)然后开始布线

(整理)谈谈PCB布线中的蛇形走线

谈谈PCB布线中的蛇形走线 一般的蛇形线 一般的差分线 差分蛇形线 PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关”信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是时钟线,通常它不需经过任何其它逻辑处理,因而其延时会小于其它相关信号。 高速数字PCB板的等线长是为了使各信号的延迟差保持在一个范围内,保证系统在同一周期内读取的数据的有效性(延迟差超过一个时钟周期时会错读下一周期的数据),一般要求延迟差不超过1/4时钟周期,单位长度的线延迟差也是固定的,延迟跟线宽,线长,铜厚,板层结构有关,但线过长会增大分布电容

和分布电感,使信号质量,所以时钟IC引脚一般都接RC端接,但蛇形走线并非起电感的作用,相反的,电感会使信号中的上升元中的高次谐波相移,造成信号 质量恶化,所以要求蛇形线间距最少是线宽的两倍,信号的上升时间越小就越 易受分布电容和分布电感的影响。 因为应用场合不同具不同的作用,如果蛇形走线在电脑板中出现,其主要起到一个滤波电感的作用,提高电路的抗干扰能力,电脑主机板中的蛇形走线, 主要用在一些时钟信号中,如PCIClk,AGPClk,它的作用有两点:1、阻抗 匹配2、滤波电感。对一些重要信号,如INTELHUB架构中的HUBLink,一 共13根,跑233MHz,要求必须严格等长,以消除时滞造成的隐患,绕线是唯一的解决办法。一般来讲,蛇形走线的线距>=2倍的线宽。PCI板上的蛇 行线就是为了适应PCI 33MHzClock 补充一: 有条件的朋友可以观察一下手边的主板。CPU插座-->北桥芯片、北桥-->AGP 插槽、频率发生器背面、内存DIMM槽附近,这些是集中使用蛇行线的地方。究其原因,还是这些都是工作在高频,并且还需要稳定的电流信号。 在PROTEL中一般先大致手工画好线,然后把要设置的所有线为一个CLASS,选Tools/Interactive Length Tuning,或者Tools/Equalize net lengths。 补充二: 减轻线与线的串扰最主要的就是增加线间距,而和绕蛇行无关,蛇行线反而 会带入导线自身的串扰问题,计算机主版个部分信号对时序要求非常严格, 所以必须对每种信号进行长度匹配,以满足足够的建立和保持时间,走蛇行 线仅仅是和时序设计相关,和高频信号完整性无关。我看过的国外多本信号

PCB板蛇形走线作用及绘制

沈阳单片机开发网——帮您精确掌握电子器件的使用细节 https://www.360docs.net/doc/1810890221.html, PCB板蛇形走线的作用及绘制方法 PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关”信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是时钟线,通常它不需经过任何其它逻辑处理,因而其延时会小于其它相关信号。 高速数字PCB板的等线长是为了使各信号的延迟差保持在一个范围内,保证系统在同一周期内读取的数据的有效性(延迟差超过一个时钟周期时会错读下一周期的数据),一般要求延迟差不超过1/4时钟周期,单位长度的线延迟差也是固定的,延迟跟线宽,线长,铜厚,板层结构有关,但线过长会增大分布电容和分布电感,使信号质量,所以时钟IC引脚一般都接RC 端接,但蛇形走线并非起电感的作用,相反的,电感会使信号中的上升元中的高次谐波相移,造成信号质量恶化,所以要求蛇形线间距最少是线宽的两倍,信号的上升时间越小就越易受分布电容和分布电感的影响。 因为应用场合不同具不同的作用,如果蛇形走线在电脑板中出现,其主要起到一个滤波电感的作用,提高电路的抗干扰能力,电脑主机板中的蛇形走线,主要用在一些时钟信号中,如PCIClk,AGPClk,它的作用有两点: 1、阻抗匹配 2、滤波电感。 对一些重要信号,如INTEL HUB架构中的HUBLink,一共13根,跑233MHz,要求必须严格等长,以消除时滞造成的隐患,绕线是唯一的解决办法。一般来讲,蛇形走线的线距>=2倍的线宽。PCI板上的蛇行线就是为了适应PCI 33MHzClock的线长要求。若在一般普通PCB板中,是一个分布参数的 LC 滤波器,还可作为收音机天线的电感线圈,短而窄的蛇形走线可做保险丝等等. 蛇形线的绘制方法: 1.尽量增加平行线段的距离(S),至少大于3H,H指信号走线到参考平面的距离。通俗的说就是绕大弯走线,只要S足够大,就几乎能完全避免相互的耦合效应。 2.减小耦合长度Lp,当两倍的Lp延时接近或超过信号上升时间时,产生的串扰将达到饱和。3.带状线(Strip-Line)或者埋式微带线(Embedded Micro-strip)的蛇形线引起的信号传输延时小于微带走线(Micro-strip)。理论上,带状线不会因为差模串扰影响传输速率。4.高速以及对时序要求较为严格的信号线,尽量不要走蛇形线,尤其不能在小范围内蜿蜒走线。 5.可以经常采用任意角度的蛇形走线,能有效的减少相互间的耦合。 6.高速PCB设计中,蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以只作时序匹配之用而无其它目的。 7.有时可以考虑螺旋走线的方式进行绕线,仿真表明,其效果要优于正常的蛇形走线。 8.用Reports →Measure Selected Objects菜单项测量蛇形线的长度。

详解“蛇形走线的作用“

详解“蛇形走线的作用“ 本人和同行讨论也参考了一些资料,蛇形走线作用大致如下:希望大家补 充纠正。 PCB 上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时, 蛇形走线的主要作用是补偿同一组相关信号线中延时较小的部分,这些部分通 常是没有或比其它信号少通过另外的逻辑处理;最典型的就是时钟线,通常它不 需经过任何其它逻辑处理,因而其延时会小于其它相关信号。 高速数字PCB 板的等线长是为了使各信号的延迟差保持在一个范围内,保证 系统在同一周期内读取的数据的有效性(延迟差超过一个时钟周期时会错读下一 周期的数据),一般要求延迟差不超过1/4 时钟周期,单位长度的线延迟差也是固 定的,延迟跟线宽,线长,铜厚,板层结构有关,但线过长会增大分布电容和分布电感,使信号质量,所以时钟IC 引脚一般都接RC 端接,但蛇形走线并非起电感的作用,相 反的,电感会使信号中的上升元中的高次谐波相移,造成信号质量恶化, 所以要 求蛇形线间距最少是线宽的两倍,信号的上升时间越小就越易受分布电容和分布 电感的影响. 因为应用场合不同具不同的作用,如果蛇形走线在电脑板中出现,其主要起到 一个滤波电感的作用,提高电路的抗干扰能力,电脑主机板中的蛇形走线,主 要用在一些时钟信号中,如PCIClk,AGPClk,它的作用有两点:1、阻抗匹配 2、滤波电感。对一些重要信号,如INTEL HUB 架构中的HUBLink,一共13 根,跑233MHz,要求必须严格等长,以消除时滞造成的隐患,绕线是唯一的 解决办法。一般来讲,蛇形走线的线距=2 倍的线宽。PCI 板上的蛇行线就是为了适应PCI 33MHzClock 的线长要求。若在一般普通PCB 板中,是一个分布参数的LC 滤波器,还可作为收音机天线的电感线圈,短而窄的蛇形走线可

PADS蛇形走线技巧V0[1].2

PADS功能使用技巧V0.2 一、如何走蛇形线? 蛇形线是布线过程中常用的一种走线方式,其主要目的是为了调节延时满足系统时序设计要求,但是设计者应该有这样的认识:蛇形线会破坏信号质量,改变传输延时,布线时要尽量避免使用,因此一块PCB上的蛇形线越多并不意味着越“高级”。实际设计中,为了保证信号有足够的保持时间,或减小同组信号之间的时间偏移,往往不得不故意进行绕线,例如DDR*(DDR1/DDR2/DDR3)中的DQS与DQ信号组要求要严格等长以降低PCB skew,这时就要用到蛇形线。 (1)设置蛇形线的参数。蛇形线的参数主要有线长、同组线线长的差值、平行线段距离(Gap)及平行线段长度。Router中打开项目浏览器(Project Explorer),展开Net Objects树形列表下的Net项,选择需要等长的网络(此处是DDR_DQ[15..0]以及DDR_DQS[1..0]),右击选择Copy,如下图所示。 (2)点击Nets组上的Matched Length Nets Groups,右击后选择Paste将上述网络粘贴到该项内,如下图所示。

(3)此时在Matched Length Net Groups组内出现一个默认名为MLNetGroup1的网络组,展开就可以看到,拷贝的网络在这里出现,如下图所示。 (4)点击MLNetGroup1网络组,右击后选择Properties,弹出如下图所示的对话框。

其中Tolerance即网络组内最长与最短走线的之间的差值,PADS默认不对走线长度加以限制,若需要,可勾选Restrict length进行相应的设置,此两者的值可根据经验或仿真结果进行设置。 (5)点击工具栏上图标或按热键Ctrl+Enter,选中Options对话框中的Routing页表项, 其中红色框中的参数即针对蛇形线,这里我们把平行线段距离(Gap)设置为3,点击OK,即可完成蛇形线的设置。 (6)在PCB中选定一个引脚,按F3开始走线,在需要走蛇形线的地方停顿,右击后选择Add Accordion,即可开始蛇形走线,如下图所示。控制方面的细节不再赘述。

PCB 20——三种特殊走线技巧

PCB 20——三种特殊走线技巧 下面从直角走线、差分走线、蛇形线三个方面来阐述PCB LAYOUT的走线。 一、直角走线(三个方面) 直角走线的对信号的影响就是主要体现在三个方面:一是拐角可以等效为传输线上的容性负载,减缓上升时间;二是阻抗不连续会造成信号的反射;三是直角尖端产生的EMI,到10GHz以上的RF设计领域,这些小小的直角都可能成为高速问题的重点对象。 二、差分走线(“等长、等距、参考平面”) 何为差分信号(Differential Signal)?通俗地说就是驱动端发送两个等值、反相的信号,接收端通过比较这两个电压的差值来判断逻辑状态“0”还是“1”。而承载差分信号的那一对走线就称为差分走线。差分信号和普通的单端信号走线相比,最明显的优势体现在以下三方面: 1、抗干扰能力强,因为两根差分走线之间的耦合很好,当外界存在噪声干扰时,几乎是同时被耦合到两条线上,而接收端关心的只是两信号的差值,所以外界的共模噪声可被完全抵消。 2、能有效抑制EMI,同样的道理,由于两根信号的极性相反,他们对外辐射的电磁场可以相互抵消,耦合的越紧密,泄放到外界的电磁能量越少。 3、时序定位精确,由于差分信号的开关变化是位于两个信号的交点,而不像普通单端信号依靠高低两个阈值电压判断,因而受工艺,温度的影响小,能降低时序上的误差,同时也更适合于低幅度信号的电路。目前流行的LVDS(low voltage differential signaling)就是指这种小振幅差分信号技术。 三、蛇形线(调节延时) 蛇形线是Layout中经常使用的一类走线方式。其主要目的就是为了调节延时,满足系统时序设计要求。其中最关键的两个参数就是平行耦合长度(Lp)和耦合距离(S),很明显,信号在蛇形走线上传输时,相互平行的线段之间会发生耦合,呈差模形式,S越小,Lp越大,则耦合程度也越大。可能会导致传输延时减小,以及由于串扰而大大降低信号的质量,其机理可以参考对共模和差模串扰的分析。下面是给Layout工程师处理蛇形线时的几点建议: 1、尽量增加平行线段的距离(S),至少大于3H,H指信号走线到参考平面的距离。通俗的说就是绕大弯走线,只要S足够大,就几乎能完全避免相互的耦合效应。 2、减小耦合长度Lp,当两倍的Lp延时接近或超过信号上升时间时,产生的串扰将达到饱和。 3、带状线(Strip-Line)或者埋式微带线(EmbeddedMicro-strip)的蛇形线引起的信号传输延时小于微带走线(Micro-strip)。理论上,带状线不会因为差模串扰影响传输速率。 4、高速以及对时序要求较为严格的信号线,尽量不要走蛇形线,尤其不能在小范围内蜿蜒走线。 5、可以经常采用任意角度的蛇形走线,能有效的减少相互间的耦合。 6、高速PCB设计中,蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以只作时序匹配之用而无其它目的。 7、有时可以考虑螺旋走线的方式进行绕线,仿真表明,其效果要优于正常的蛇形走线。