8位可逆循环计数器

一、概述

随着科技的日益进步,计数器得到了越来越广泛的应用,发展的也越快。在数字系统中使用的最多时序逻辑电路要算是计数器了。计数器不仅能用于对时钟脉冲计数,还可以用于分频、定时、产生节拍脉冲和脉冲序列以及进行数字运算等。本次实验的思路主要是设计一个8位可逆循环计数器,该计数器加计数到最大值(11111111)时输出一个周期的高电平信号(表示计数器达到最大值)并自动变为减计数,减计数到最小值(00000000)是输出一个周期的高电平信号(表示计数器达到最小值)并自动变为加计数。如此循环往复。要求设计层次化。实验中用到的器件主要包括74LS191D、7段显示器、555组成的多谐振荡电路和多个门电路。

二、方案论证

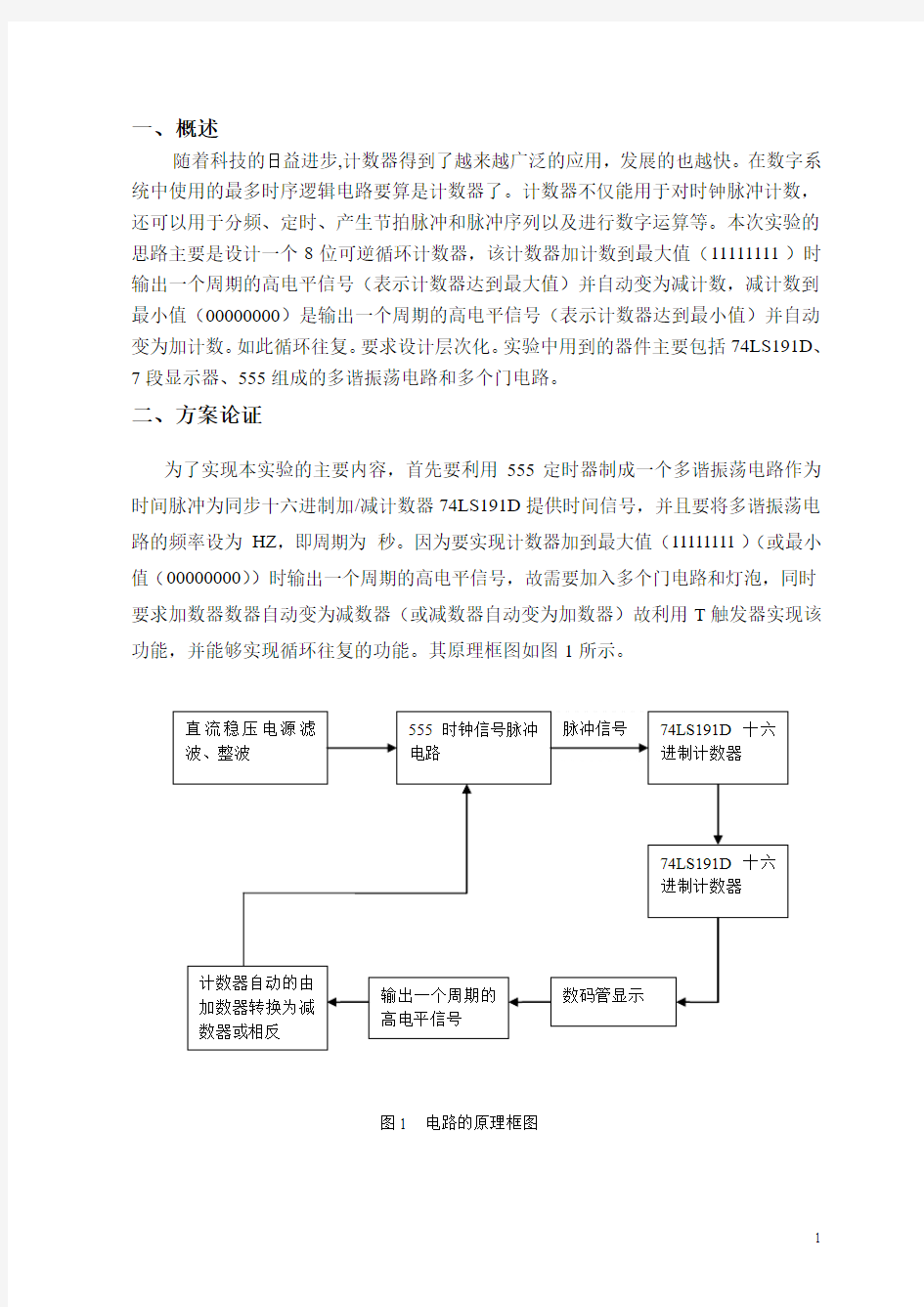

为了实现本实验的主要内容,首先要利用555定时器制成一个多谐振荡电路作为时间脉冲为同步十六进制加/减计数器74LS191D提供时间信号,并且要将多谐振荡电路的频率设为HZ,即周期为秒。因为要实现计数器加到最大值(11111111)(或最小值(00000000))时输出一个周期的高电平信号,故需要加入多个门电路和灯泡,同时要求加数器数器自动变为减数器(或减数器自动变为加数器)故利用T触发器实现该功能,并能够实现循环往复的功能。其原理框图如图1所示。

图1 电路的原理框图脉冲信号

直流稳压电源滤波、整波

555时钟信号脉冲

电路

74LS191D十六

进制计数器

74LS191D十六

进制计数器

数码管显示

输出一个周期的

高电平信号

计数器自动的由加数器转换为减数器或相反

三、电路设计

1.直流稳压电源电路

直流稳压电源包括电源电容电阻;其组成电路如图2所示。

图2 直流稳压电源电路

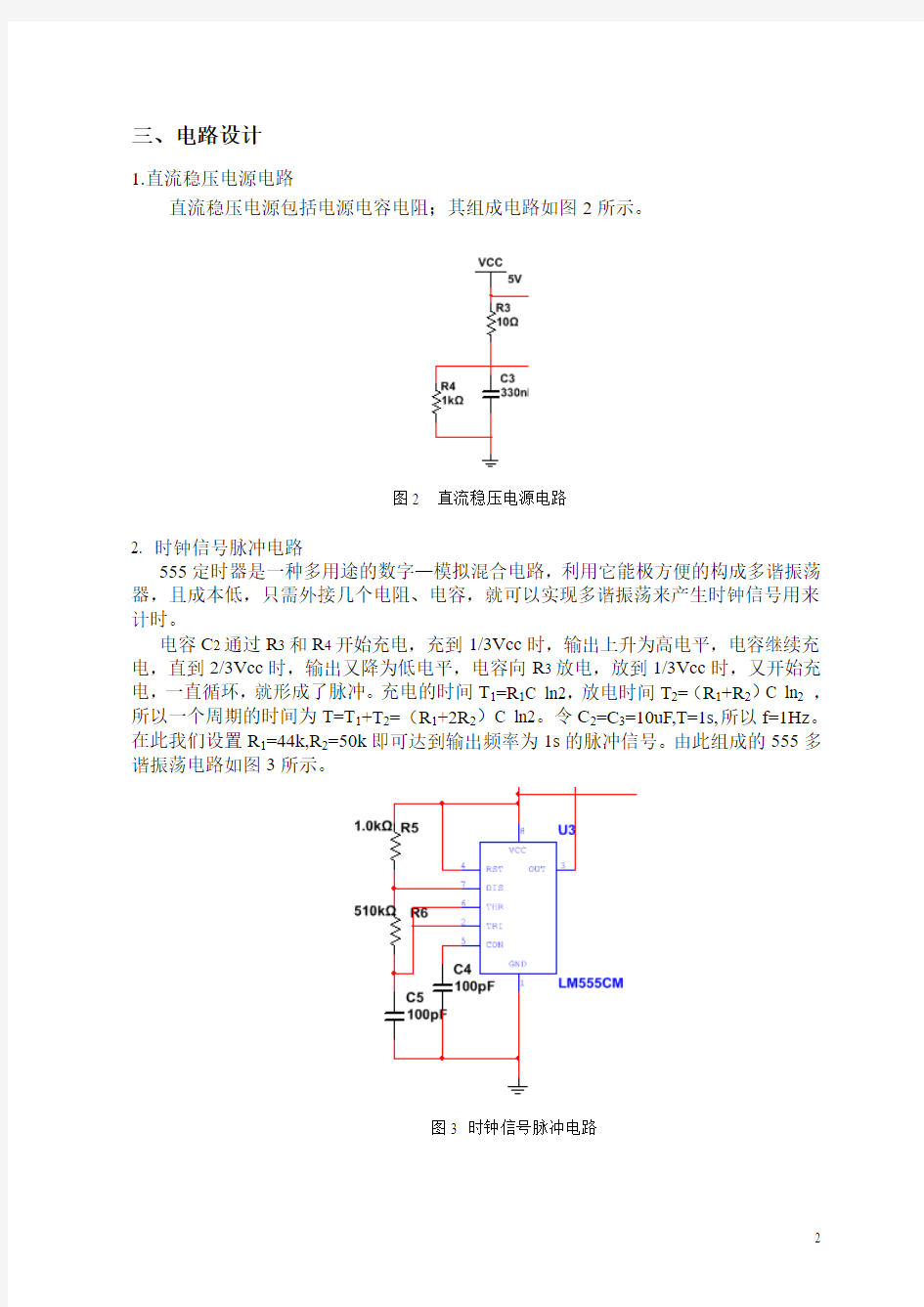

2. 时钟信号脉冲电路

555定时器是一种多用途的数字—模拟混合电路,利用它能极方便的构成多谐振荡器,且成本低,只需外接几个电阻、电容,就可以实现多谐振荡来产生时钟信号用来计时。

电容C2通过R3和R4开始充电,充到1/3Vcc时,输出上升为高电平,电容继续充电,直到2/3Vcc时,输出又降为低电平,电容向R3放电,放到1/3Vcc时,又开始充电,一直循环,就形成了脉冲。充电的时间T1=R1C ln2,放电时间T2=(R1+R2)C ln2,所以一个周期的时间为T=T1+T2=(R1+2R2)C ln2。令C2=C3=10uF,T=1s,所以f=1Hz。在此我们设置R1=44k,R2=50k即可达到输出频率为1s的脉冲信号。由此组成的555多谐振荡电路如图3所示。

图3 时钟信号脉冲电路

3.计数器电路

此电路是由两片74LS191D组成,当所需进制超过本身进制,则需要用芯片间的级联来实现其功能。如图4所示。

图4 计数器电路

4.数码管显示电路。

此部分是在以上部分基础上来实现的,主要有8个数码管组成。显示8位二进制数。其具体的电路图如下图5所示。

图5 数码管显示电路

5.输出与计数器自动转换电路

使用与门,当两计数器74LS191都输出1111(或0000)时输出一个周期的高电平信号,然后用非门、555和T触发器使计数器自动转换进行下一阶段的计数,并且不断循环、转换。如图6所示。

图6 输出与计数器自动转换电路

四、性能的测试

1.直流稳压电源的测试

对直流稳压电源进行测试,利用万能表对输出电压进行测量;其输出电压为5V,在允许的误差范围内,故此电路可行。其测量结果如图7所示。

图7 直流稳压电源测试值

2.时钟信号脉冲电路测试

用示波器对多谐振荡电路输出脉冲进行测量,其信号输出波形如图8所示。

3.电路整体性能测试

1)加数器加到最大值:电路正常工作,数码管显示最大值(11111111),输出一个周期的高电平信号。运行结果如图9所示。

图9 加数器加到最大值状态图

2) 减数器见到最小值时,电路正常工作。如图10所示。

图10 减数器减到最小值

五、结论

经过测试评定该电路能正常工作并能完成课设要求的基本功能。实现的基本功

能如下:

1)加数器能加到最大值,减数器能减到最大值;

2)当最大值(或最小值)时能够输出一个周期高电平信号。 3)电路能够自动装换并循环往复。

六、性价比

此电路的设计主要采用了常见的74LS191D 片子,且只用了两片,电路利用的是555构成的多谐振荡电路,控制电路则采用了多个门电路。总体来说这些元器件在我们数字电子技术领域内都是比较常见的,且价格低廉,利用这些元器件组成的8位循环可逆计数器电路可以说性价比非常高。且电路的设计理念也比较合理。

七、课设体会及合理化建议

本次课设历时两个多星期,通过本次课设我对数字电子技术基础有了更深的了解与体会,充分的体现出了这次课程设计的目的。在刚拿到课设题目时候自己慌了,

U1

74LS191D

A 15

B 1

C 10D

9~U/D 5QA 3QB 2QC 6QD

7

~CTEN 4~LOAD

11~RCO

13MAX/MIN 12

CLK

14

U2

74LS191D

A 15

B 1

C 10D

9~U/D 5QA 3QB 2QC 6QD

7

~CTEN 4~LOAD

11~RCO

13MAX/MIN 12

CLK

14

U3

LM555CM

GND 1

DIS 7

OUT

3

RST 4VCC

8THR 6CON

5

TRI 2U4

LM555CM

GND 1DIS 7OUT

3

RST 4VCC

8THR 6CON

5

TRI 2U5DCD_HEX

U6DCD_HEX U7DCD_HEX U8DCD_HEX U9DCD_HEX U10DCD_HEX U11DCD_HEX U12

DCD_HEX

U13A 74LS08D

U14

D_FF

D Q ~Q

RESET

CLK

SET

U15A

74LS05D

R11.0kΩR2510kΩ

C1100pF

C2100pF

VCC

5V

R310Ω

R41kΩ

C3330nF

R5

1.0kΩR6

510kΩC4100pF

C5100pF

XSC1

A

B

C

D

G T

X1

2.5 V

本来就学的不好对于课设题目更是摸不到头脑,无从下手。考完试后,赶快借书,到网上找资料,可是,我没有找到,于是一切回归于课本,我找到了加减计数器,555,还学会运用门电路等等,才算是刚刚起步,随后一个星期没有进展,还是在老师的帮助下才解决问题。在此次课设中,我学到不少知识,对数电了解的更深了。

合理化建议:1)老师与学生之间的沟通交流应该更多,老师会交给我们更多东西。

2)在学习了新知识后,我们应该多多实践,增强动手能力。

参考文献

[1] 阎石主编. 数字电子技术. [M]北京:高等教育出版社,2006年

[2] 陈振官等编著. 新颖高效声光报警器. [M]北京:国防工业出版社,2005年

[3] 关静主编. 数字电路应用设计. [M]北京:科学出版社,2009年

[4] 童诗白主编. 模拟电子技术基础. [M]北京:高等教育出版社,2009年

[5] 华满清主编.电子技术实验与课程设计.[M]北京:机械工业出版社,2005年

附录I 总电路图

U 1

74L S 191D

A 15

B 1

C 10D

9

~U /D 5

Q A 3Q B 2Q C 6Q D 7

~C T E N 4~L O A D 11~R C O 13M A X /M I N 12

C L K

14

U 2

74L S 191D

A 15

B 1

C 10D

9

~U /D 5

Q A 3Q B 2Q C 6Q D 7

~C T E N

4~L O A D 11~R C O 13M A X /M I N 12

C L K

14

U 3L M 555C M

G N D

1

D I S

7

O U T 3

R S T

4

V C C

8

T H R

6

C O N

5

T R I

2

U 4

L M 555C M

G N D

1

D I S

7

O U T

3

R S T

4V C C

8

T H R

6

C O N

5

T R I

2

U 5

D C D _H

E X

U 6D C D _H E X U 7D C D _H E X U 8D C D _H E X U 9D C D _H E X U 10D C D _H E X U 11D C D _H E X U 12

D C D _H

E X

U 13A 74L S 08D

U 14

D _F F D Q

~Q

R E S E T

C L K

S E T

U 15A 74L S 05D

R 11.0k Ω

R 2510k Ω

C 1100p F

C 2100p F

V C C

5V

R 310Ω

R 41k Ω

C 3330n F

R 5

1.0k ΩR 6

510k Ω

C 4100p F

C 5100p F

X S C 1

A B C D

G

T

X 1

2.5 V

附录II 元器件清单

序号编号名称型号数量

1 U1、U

2 十六进制加/减

计数器

74LS191D 2

2 U3、U4 定时器LM555CM 2

3 C1、C2、C4、C5/C3 电容100pF/330nF 4

4 U14 D触发器D_FF 1

5 U5、U6、U7、U8、

U9、U10、U11、

U12

数码管DCD_HEX 8

6 U13 与门74LS08D 1

7 U15 非门74LS05D

8

9

10

11

可编程可逆计数器

自动化专业电子课程设计报告题目:可编程可逆计数器设计 姓名王振 学号0808020231 指导教师:廖晓纬 评阅成绩等次: 电气信息工程系 2010-2011 第二学期

摘要:本课程设计是基于Altera公司开发的QuartusⅡ软件进行的设计,利用QuartusⅡ设计软件的元件库所提供的集成器件来实现任意进制计数器的设计,此软件是学习EDA(电子设计自动化)技术的重要软件。其中硬件使用高性价比的FPGA/CPLD(元件可编程逻辑闸阵列/复杂可编程逻辑器件)器件,软件利用VHDL(超高速集成电路硬件描述语言)语言,计数器电路的功能取决于硬件描述语言对设计对象建模的描述,经过精心调试使可编程器件的芯片利用效率达到最优,较之以往的数字电路设计和单片机功能设计具有灵活简便的优势,特别是在对复杂计数器设计,可大大减少调试时间,优化系统设计。 关键词:EDA;任意进制计数器;QuartusⅡ;VHDL

目录 前言 (3) 一、设计的任务与要求 (4) 1.1 设计任务 (4) 1.2 设计要求 (4) 二、总体设计和系统框图 (4) 2.1计数器方案 (4) 2.2 数码管驱动显示方案 (4) 2.3 N进制设定设计方案 (5) 2.4电路系统总体设计 (5) 三、硬件设计 (6) 3.1计数器部分设计硬件连接方式 (6) 3.2 驱动译码部分设计 (7) 3.3进制输入部分设计 (7) 3.4整体电路部分 (7) 四、软件设计(系统仿真) (9) 4.1程序工作流程图 (9) 4.2 仿真步骤及结果 (10) 五、设计结果分析 (12) 5.1 系统能实现的功能 (12) 5.2 系统所选用软件及芯片型号 (12) 六、设计总结和体会 (12) 6.1设计总结 (12) 6.2设计的收获及体会 (12) 6.3 设计的完善 (13) 致谢 (13) 参考文献 (13) 程序代码 (14)

计数器的设计实验报告

计数器的设计实验报告 篇一:计数器实验报告 实验4 计数器及其应用 一、实验目的 1、学习用集成触发器构成计数器的方法 2、掌握中规模集成计数器的使用及功能测试方法二、实验原理 计数器是一个用以实现计数功能的时序部件,它不仅可用来计脉冲数,还常用作数字系统的定时、分频和执行数字运算以及其它特定的逻辑功能。 计数器种类很多。按构成计数器中的各触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器。根据计数制的不同,分为二进制计数器,十进制计数器和任意进制计数器。根据计数的增减趋势,又分为加法、减法和可逆计数器。还有可预置数和可编程序功能计数器等等。目前,无论是TTL还是

CMOS集成电路,都有品种较齐全的中规模集成计数器。使用者只要借助于器件手册提供的功能表和工作波形图以及引出端的排列,就能正确地运用这些器件。 1、中规模十进制计数器 CC40192是同步十进制可逆计数器,具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如图5-9-1所示。 图5- 9-1 CC40192引脚排列及逻辑符号 图中LD—置数端CPU—加计数端CPD —减计数端CO—非同步进位输出端BO—非同步借位输出端 D0、D1、D2、D3 —计数器输入端 Q0、Q1、Q2、Q3 —数据输出端CR—清除端 CC40192的功能如表5-9-1,说明如下:表5-9-1 当清除端CR为高电平“1”时,计数

器直接清零;CR置低电平则执行其它功能。当CR为低电平,置数端LD也为低电平时,数据直接从置数端D0、D1、D2、D3 置入计数器。 当CR为低电平,LD为高电平时,执行计数功能。执行加计数时,减计数端CPD 接高电平,计数脉冲由CPU 输入;在计数脉冲上升沿进行8421 码十进制加法计数。执行减计数时,加计数端CPU接高电平,计数脉冲由减计数端CPD 输入,表5-9-2为8421 码十进制加、减计数器的状态转换表。加法计数表5-9- 减计数 2、计数器的级联使用 一个十进制计数器只能表示0~9十个数,为了扩大计数器范围,常用多个十进制计数器级联使用。 同步计数器往往设有进位(或借位)输出端,故可选用其进位(或借位)输出信号驱动下一级计数器。 图5-9-2是由CC40192利用进位

同步二进制加法计数器

同步二进制加法计数器 F0302011 5030209303 刘冉 计数器是用来累计时钟脉冲(CP脉冲)个数的时序逻辑部件。它是数字系统中用途最广泛的基本部件之一,几乎在各种数字系统中都有计数器。它不仅可以计数,还可以对CP 脉冲分频,以及构成时间分配器或时序发生器,对数字系统进行定时、程序控制操作。此外,还能用它执行数字运算。 1、计数器的特点: 在数字电路中,把记忆输入CP脉冲个数的操作叫做计数,能实现计数状态的电子电路称为计数器。特点为(1)该电路一般为Moore型电路,输入端只有CP信号。 (2)从电路组成看,其主要组成单元是时钟触发器。 2、计数器分类 1) 按CP脉冲输入方式,计数器分为同步计数器和异步计数器两种。 同步计数器:计数脉冲引到所有触发器的时钟脉冲输入端,使应翻转的触发器在外接的CP脉冲作用下同时翻转。 异步计数器:计数脉冲并不引到所有触发器的时钟脉冲输入端,有的触发器的时钟脉冲输入端是其它触发器的输出,因此,触发器不是同时动作。 2) 按计数增减趋势,计数器分为加法计数器、减法计数器和可逆计数器三种。 加法计数器:计数器在CP脉冲作用下进行累加计数(每来一个CP脉冲,计数器加1)。 3) 按数制分为二进制计数器和非二进制计数器两类。 二进制计数器:按二进制规律计数。最常用的有四位二进制计数器,计数范围从0000到1111。 异步加法的缺点是运算速度慢,但是其电路比较简单,因此对运算速度要求不高的设备中,仍不失为一种可取的全加器。同步加法优点是速度快,虽然只比异步加法快千分之一甚至几千分之一秒,但对于计数器来讲,却是十分重要的。所以在这个高科技现代社会中,同步二进制计数器应用十分广泛。 下图为三位二进制加法计数器的电路图。 图1 三位二进制计数器 图示电路为对时钟信号计数的三位二进制加法计数器或称为八进制加法计数器。 该电路的经典分析过程: 1.根据电路写出输出方程、驱动方程和状态方程 2. 求出状态图 3.检查电路能否自启动 4.文字叙述逻辑功能 解:

红外可逆计数器设计

《光电子技术》课程设计课题名称:红外可逆计数器设计 指导老师:曾维友

一、课题名称: 红外可逆计数器设计 二、设计任务: 设计一个红外可逆计数器,要求: 1、当一物体沿某一方向经过计数器时,计数器进行加一计数;而物体沿反方向经过计数器时,计数器进行减计数; 2、用数码管显示当前的计数值,最大计数值为1000; 3、设计方案经济、实用、可靠。 三、设计方案: 方案(1):红外发射管 + 一体化按收头:适用于发射管与接收管距离较大的情形 方案(2):槽型光电开关:适用于发射管与接收管距离较小的情形 方 波发生器 TSOP34838 38KHz 单片机系统 显示模块 单 片机系统 显示模块 Vcc

四、方案选择 由以上两种方案的设计框图可以看出:两种方案的唯一不同之处在于光电发射和接收装置,方案一釆用的是红外发射管加上一体化接收头,适用于发射管与接收管距离较大的情形,而且为了防止误动作,在光电发射部分加入了方波调制电路,因而具有较好的抗干扰能力;而方案二的电路比较简单,只用了一个槽型光电开关,外加两个限流电阻和一个反相器,这种电路适用于发射管与接收管距离较小的情形。考虑到越来越多的流水线上的产品和各种公共场所需要进行自动计数,而在这种情形下发射管与接收管距离一般都比较较大,加之方案一有较强的抗干扰能力。综合以上考虑,我们选择了方案一。 五、模块设计 1、方波发生电路 方波发生器的组成方式很多,可以用集成运放构成,可以用一些定时芯片构成,也可以用一些数字门电路构成。由于在数电课程中,我们已经学习了用555定时器构成的方波发生器,对此比较熟悉,电路也比较简单,而且性能良好,因此我们选择了用NE555构成的方波发生器。电路如下:

实验九-可逆计数器的功能测试及应用电路

实验九可逆计数器的功能测试及应用电路 实验目的: (1)掌握可逆计数器74LS191、74LS191、74LS192、74LS193的逻辑功能及使用方法。 (2)熟悉可逆计数器实现任意进制的数码倒计时电路的工作原理。 实验仪器与器件: 实验箱一个;双踪示波器一台;稳压电源一台;函数发生器一台。 74LS191、74LS191、74LS191或74HC48、74LS00和74LS04。 实验内容: 1测试74LS190和74LS191的逻辑功能,并用数码管显示,验证是否与表2-9-4一致,分别画出各单元的电路图,写出各自的状态 实验原理:单时钟74LS191二进制同步加/减计数器的功能表如下: 表2-9-4 单时钟74LS191二进制同步加/减计数器的功能表 单时钟74LS191二进制同步加/减计数器是十进制的,其他功能与74LS191一样。它的有效状态为0000~1001. 实验电路: 如图所示是减计数时当计数器的状态变为0时的电路状态:RCO=0,MAX/=1; MIN

实验现象与结果: 该结果是当CTEN =0,D L =1,D U /=1时,A B C D Q Q Q Q 的 波形图; 该结果是当CTEN =0,D L =1,D U /=1时, RCO 与MIN MAX /的波形图

需要说明的是:当CTEN= D L=1时,电路保持原来的状态。 2测试74LS192和74LS193的逻辑功能,并用数码管显示,验证是否与表2-9-3及2-9-5一致。画出测试电路图。 实验原理: 双时钟74LS192同步十进制可逆计数器的功能表如下表所示,74LS192是十进制计数器。 表2-9-3双时钟74LS192同步十进制可逆计数器的功能表 输入输出工作 状态 U CP UP D CP DOW N CLR D L DCBA A B C D Q Q Q Q U TC D TC **H H ****0000 H H 异步 清零**L L 1001 1001 H H 异步 置数 H ↑L H ****1001→ 0001→ 0000H H H L 减法 计数 ↑H L H ****0000→ 1000→ 1001H L H H 加法 计数 双时钟74LS193二进制同步加/减法计数器的功能表如下表所示,74LS193是一个十六进制的计数器。

十进制可逆加减计数器

时序电路逻辑设计 实验人:周铮班级:中法1202班学号:U201215676 一实验目的 1.掌握用SSI实现简单组合逻辑电路的方法。 2.掌握简单数字电路的安装与测试技术。 3.熟悉使用Verilog HDL描述组合逻辑电路的方法,以及EDA仿真技术。 二实验器件 计算机,可编程实验板 三实验内容 十进制加减可逆计数器设计 功能要求: 拨码开关键SW1为自动可逆加减功能键,当SW1为HIGH时,计数器实现自动可逆模十加减计数功能,即4个七段数码管上几乎同步显示0—1—2—3—4—...9—8—7—...0—1...的模十自动可逆加减计数结果;当SW1为LOW时,计数器按拨码开关键SW0的选择分别执行加减计数功能。即当SW0为HIGH时,计数器实现模十加计数功能,即4个七段数码管上几乎同步显示0—1—2—3—4—...9——0—1...的模十加计数结果;当SW0为LOW时,计数器实现模十减计数功能,即4个七段数码管上几乎同步显示9—8—7—...—1—0— (9) —8—7…的模十减计数结果。 四实验设计 1.原理设计 脉冲发生电路采用555定时器组成的多谐振荡器振荡产生周期为1s的矩形脉冲,从而为计数器提供触发信号。其中,可以通过R1,R2,C来控制充放电的时间。 加/减计数控制电路主要由74LS138构成。74LS138芯片是常用的3-8线译码器,常用在单片机和数字电路的译码电路中,74LS138的引脚排列及 真值表如图

计数单元电路主要由十进制计数器74LS192构成。74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列图如图 功能表如图 2.模拟仿真 用Verilog HDL语言设计二通道数据选择器实验程序如下: ①实验代码 module a( input clk,

同步计数器的设计实验报告文档

2020 同步计数器的设计实验报告文档 Contract Template

同步计数器的设计实验报告文档 前言语料:温馨提醒,报告一般是指适用于下级向上级机关汇报工作,反映情况,答复上级机关的询问。按性质的不同,报告可划分为:综合报告和专题报告;按行文的直接目的不同,可将报告划分为:呈报性报告和呈转性报告。体会指的是接触一件事、一篇文章、或者其他什么东西之后,对你接触的事物产生的一些内心的想法和自己的理解 本文内容如下:【下载该文档后使用Word打开】 同步计数器的设计实验报告 篇一:实验六同步计数器的设计实验报告 实验六同步计数器的设计 学号: 姓名: 一、实验目的和要求 1.熟悉JK触发器的逻辑功能。 2.掌握用JK触发器设计同步计数器。 二、实验仪器及器件 三、实验预习 1、复习时序逻辑电路设计方法。 ⑴逻辑抽象,得出电路的状态转换图或状态转换表 ①分析给定的逻辑问题,确定输入变量、输出变量以及电路的状态数。通常都是取原因(或条件)作为输入逻辑变量,取结

果作输出逻辑变量。 ②定义输入、输出逻辑状态和每个电路状态的含意,并将电路状态顺序编号。 ③按照题意列出电路的状态转换表或画出电路的状态转换图。通过以上步骤将给定的逻辑问题抽象成时序逻辑函数。 ⑵状态化简 ①等价状态:在相同的输入下有相同的输出,并且转换到同一次态的两个状态。 ②合并等价状态,使电路的状态数最少。 ⑶状态分配 ①确定触发器的数目n。因为n个触发器共有2n种状态组合,所以为获得时序电路所需的M个状态,必须取2n1<M2n ②给每个电路状态规定对应的触发器状态组合。 ⑷选定触发器类型,求出电路的状态方程、驱动方程和输出方程 ①根据器件的供应情况与系统中触发器种类尽量少的原则谨慎选择使用的触发器类型。 ②根据状态转换图(或状态转换表)和选定的状态编码、触发器的类型,即可写出电路的状态方程、驱动方程和输出方程。 ⑸根据得到的方程式画出逻辑图 ⑹检查设计的电路能否自启动 ①电路开始工作时通过预置数将电路设置成有效状态的一种。 ②通过修改逻辑设计加以解决。

二进制计数器

课题:二进制计数器 课时:讲三课时练一课时 教学要求: (1)掌握计数器的功能;(除计数外,还可用于分频、定时、测量等) (2)掌握二进制计数器的功能、组成及常见的分类。 教学过程: 一、 异步二进制计数器 1、 电路组成 从图中可知:CP 脉冲直接控制F 0的翻转, Q 0控制F 1的翻转,Q 1控制F 2的翻转。 能够记忆输入脉冲个数的电路称为计数器。 计数器 二进制计数器 十进制计数器 N 进制计数器 加法计数器 同步计数器 异步计数器 减法计数器 可逆计数器 加法计数器 减法计数器 可逆计数器 二进制计数器 十进制计数器 N 进制计数器

2、工作过程 (1)计数器工作前应先清零。使CR=0,则Q2Q1Q0=000。 (2)计数:CR=1。当第一个CP脉冲的下降沿到来时,F0翻转――Q0由0变到1,F1不翻转,F2不翻转。当第二个CP脉冲的下降沿到来 时,F0翻转――Q0由1变到0,此时F1翻转――Q1由0变到1,F2 不翻转。当第三个CP脉冲的下降沿来时,F0翻转――Q0由0变到 1,此时F1不翻转――Q1仍为1,F2还是不翻转。当第四个CP脉 冲的下降沿来时,F0翻转――Q0由1变到0,此时F1翻转――Q1 由1变为0,F2也翻转――Q2由0变为1。依次循环。 波形图:

二、异步二进制减法计数器 电路图:《教材》P234的图给学生分析,下图请学生自己分析。 功能表波形图 F0每输入一个时钟脉冲翻转一次,F1在Q0由1变0时翻转,F2在Q1由1变0时翻转。 三、二进制同步计数器 电路图:《教材》P235的图给学生分析,下图请学生自己分析。 电路分析:F0每输入一个时钟脉冲翻转一次;F1在Q0=1时,在下一个CP触发沿到来时翻转;F2在Q0=Q1=1时,在下一个CP触发沿到来时翻转。

停车场计数器的设计..

电子课程设计 ——停车场计数器 学院:太原科技大学华科学院 专业:电气工程及其自动化 班级:电气122202H班 姓名:白健 学号:201222050201 指导老师:黄庆彩 2014年12月

目录 一、设计任务与要求 (1) 二、总体框图 (2) 三、选择器件 (3) 四、功能模块 (14) 五、总电路图 (19) 心得 (20) 参考文献 (20)

停车场计数器 一、设计任务与要求 1.1 设计目的: (1)掌握可任意预置的定时显示报警系统的构成、原理与设计方法; (2)熟悉集成电路的使用方法。 1.2 基本要求: (1)能够预置初始车位数,能够显示空余车位,从0-999; (2)在出口处里、外分别安装两个传感器(比如红外传感器)A、B,每当有车辆进入时将顺序经过A、B,每当有车辆出去时将顺序经过B、A,设计电路能够区分此车辆进入还是出去。 (3)进入车辆,空余车位数减1;车辆离去,空余车位数加1。 二、总体框图

设计思路 我设计的停车场电子车位计数器电路主要有四大部分,即车位空位数计数部分、译码部分、显示部分和提示灯提示部分。进出的每辆车都会触发门口的红外遥感,给计数器一个脉冲信号,使计数器进行加减计数,由显示部分将所剩余的车位数显示出来,提示灯部分提示是否有空余的车位。 (一)计数部分:用三个可逆计数器74LS192联级组成100进制可逆计数电路,预置最大值999; (二)译码部分:用七段式译码器74LS48将8421BCD码转化为共阴极七段数码管需要的逻辑状态二进制代码; (三)显示部分:采用共阴极七段式显示器,将二进制码以十进制的形式显示出来; (四)提示灯部分:由555定时器组成的单稳态触发器驱动灯泡发光,提示空车位数为0。 三、选择器件

实验九 可逆计数器的功能测试及应用电路

实验九 可逆计数器的功能测试及应用电路 实验目的: (1)掌握可逆计数器74LS191、74LS191、74LS192、74LS193的逻辑功能及使用方法。 (2)熟悉可逆计数器实现任意进制的数码倒计时电路的工作原理。 实验仪器与器件: 实验箱一个;双踪示波器一台;稳压电源一台;函数发生器一台。 74LS191、74LS191、74LS191或74HC48、74LS00和74LS04。 实验内容: 1测试74LS190和74LS191的逻辑功能,并用数码管显示,验证是否与表2-9-4一致,分别画出各单元的电路图,写出各自的状态 实验原理:单时钟74LS191二进制同步加/减计数器的功能表如下: 表2-9-4 单时钟74LS191二进制同步加/减计数器的功能表 单时钟74LS191二进制同步加/减计数器是十进制的,其他功能与74LS191一样。它的有效状态为0000~1001. 实验电路: 如图所示是减计数时当计数器的状态变为0时的电路状态:RCO =0, MIN MAX /=1; CLK D U / CTEN D L DCBA A B C D Q Q Q Q RCO MIN MAX / 工作作状态 ↑ ↓ * H H **** 0000 H L H H 保持 * * * L DCBA DCBA H L 异步置数 ↑ H L H **** 1111 1111→ 0001→0000 H H L(瞬态) H(瞬态) L H 减计数 ↑ L L H **** 0000→1110→ 1111 H H →L (瞬态) L H 加计数

实验现象与结果: 该结果是当CTEN =0,D L =1,D U /=1时,A B C D Q Q Q Q 的 波形图; 该结果是当CTEN =0,D L =1,D U /=1时, RCO 与MIN MAX /的波形图

四位十进同步可逆计数器

四位十进同步可逆计数器. CLK接口接入由脉冲模块产生的脉冲,PL由主持人模块发出信号经过一个非门接入,控制计时开始,D/U’接高电平构成减法器,D0和D3接高电平D1和D2接低电平,E接地,输出Q0~Q3与4511的ABCD 相接4511的输出端Qa~Qg和LED数码管对应的接口相连接,LE接口由锁存模块提供经过一个或门接入控制锁存。 倒计时功能主要是利用74LS190计数芯片来实现,同时利用反馈和置数实现进制的转换,以适合分和秒的不同需要。由于该系统特殊的需要,到各计时器到零时,通过停止控制电路使计数器停止计数并用LED发出警报 74LS190 十进制减计时器

CD4511 是一片CMOS BCD—锁存/7 段译码/驱动器,用于驱动共阴极LED (数码管)显示器的BCD 码—七段码译码器。 编辑本段特点 具有BCD转换、消隐和锁存控制、七段译码及驱动功能的CMOS 电路能提供较大的拉电流。可直接驱动共阴LED数码管。 A0~A3:二进制数据输入端 /BI:输出消隐控制端 LE:数据锁定控制端 /LT:灯测试端 Ya~Yg:数据输出端 VDD:电源正 VSS:电源负 编辑本段推荐工作条件 电源电压范围:3V~18V 输入电压范围:0V~VDD 工作温度范围:M类-55℃~125℃E类-40℃~85℃ 其中a b c d 为BCD 码输入,a为最低位。LT为灯测试端,加高电平时,显示器正常显示,加低电平时,显示器一直显示数码“8”,各笔段都被点亮,以检查显示器是否有故障。BI为消隐功能端,低电平时使所有笔段均消隐,正常显示时,B1端应加高电平。另外CD4511有拒绝伪码的特点,当输入数据越过十进制数9(1001)时,

数电实验报告 可逆计数器

实验报告 实验九可逆计数器的功能测试及应用电路 2.9.1 实验目的 1.掌握可逆计数器74LS190、74LS191、74LS192、74LS193的逻辑功能及使用方法。 2.熟悉可逆计数器实现任意进制的数码倒计时电路的工作原理。 2.9.2 实验仪器与器件 实验箱一个;双踪示波器一台;稳压电源一台;函数发生器一台。74LS190、74LS192、74LS247或74HC48、74LS00和74LS04. 2.9.3 实验原理 1. 4位十进制同步加减法计数器 对于74LS190,D、C、B、A为并行数据输入端;Q D Q C Q B Q A为并行数据输出端;U/D为加减控制信号输入端,当加减控制信号U/D=0时做加法计数;而当加减控制信号U/D=1时做减法计数;CLK为单时钟脉冲输入端;MAX/MIN为最大/最小输出端,也称为进位/错位信号输出端;L D为预置数控制端,低电平有效;CTEN为使能端,进行状态控制,低电平有效;RCO为脉冲时钟。 2. 4位二进制同步加减法计数器 对于74LS192,D、C、B、A为并行数据输入端;Q3Q2Q1Q0为并行数据输出端;CP U为加法计数脉冲输入端;CP D为减法计数脉冲输入端;CLR为异步置零端,高电平有效;TC D为借位信号输出端;TC U为进位信号输出端;L D为异步预置数控制端,低电平有效。 2.9.4 实验内容 1.测试74LS190和74LS191的逻辑功能,并用数码管显示,验证是否与表2-9-4一致。分别画出各单元的电路图,写出各自的状态转换图。

加法计数:0000—0001—0010—0011—0100—0101—0110—0111—1000—1001—0000 减法计数:1001—1000—0111—0110—0101—0100—0011—0010—0001—0000 加法计数:0000—0001—0010—0011—0100—0101—0110—0111—1000—1001—1010—1011—1100—1101—1110—1111—0000 减法计数:1111—1110—1101—1100—1011—1010—1001—1000—0111—0110—0101—0100—0011—0010—0001—0000 2.测试74LS192和74LS193的逻辑功能,并用数码管显示,验证是否与表2-9-3一致。画出电路图。 进行加法计数:

可逆计数器的设计

EDA设计基础实验课程论文 题目可逆计数器的设计 学院电子工程学院 专业班级通信081班 学生姓名王力宏 指导教师大力会 2013年6月12日

摘要 本设计介绍了Verilog-HDL语言在可逆计数器的具体应用,给出了仿真波形并下载到FPGA开发板上实际验证。说明了实现电子电路的自动化设计(EDA)过程和EDA技术在现代数字系统中的重要地位及作用. 关键词:Verilog-HDL EDA FPGA开发板仿真

Abstract This design describes the Verilog-HDL language in reversible counter the specific application, the simulation waveforms downloaded to the FPGA development board and the actual verification. Illustrates the realization of electronic circuit design automation (EDA) process and EDA technology in the modern digital systems in an important position and role. Keywords: State Machine Verilog-HDL EDA FPGA development board Simulation

目录 摘要.................................................................... I Abstract.................................................................. I 第1章绪论. (2) 1.1 概述 (2) 1.1.2 EDA的发展趋势 (2) 1.2 硬件描述语言 (3) 1.3 FPGA介绍 (4) 第2章可逆计数器设计的基本理论 (6) 2.1 设计原理 (6) 2.2 电路设计系统仿真 (6) 2.2.1 编辑文件 (6) 2.3.2 创建工程 (6) 2.3.2 仿真 (7) 第3章系统的仿真结果 (9) 3.1 编译成功 (9) 3.2 波形图 (10) 3.3 原理图 (11) 第4章心得体会 (12) 结论 (13) 参考文献 (14) 附录1 (15) 致谢 (17)

设计任意进制计数器

设计任意进制计数器 一、实验目的 掌握中规模集成计数器的使用方法及功能测试方法。 二、实验内容及要求 采用(74LS192)复位法或预置数法设计一个三位十进制计数器。要求各位同学设计的计数器的计数容量是自己学号的最后三位数字。 三、设计过程 74LS192是中规模同步十进制可逆计数器,具有双时钟输入,并具有清除和置数等功能,其引脚排列如图所示。74LS192(CC40192)的功能如下表所示。 1234A B C D 4 3 2 1 D C B A 161514131211109 Vcc D CR BO CO LD D D D Q Q CP CP Q Q GND 12345678 D 1 1 023 3 u2 74LS192 CR:清除端CP u:加计 数端 LD :置数端CP D:减计 数端 CO :非同步进位输出端 BO :非同步借位输出端 D3、D2、D1、D0:数据输入端 Q3、Q2、Q1、Q0:输出端 74LS192引脚排列图 表74LS192(CC40192)的功能 输入端输出端功能 CR LD CP u CP D D3 D2 D1 D0 Q3 Q2 Q1 Q0 1 ×××××××00 0 0 清零 0 0 ×× d c b a d c b a 置数 0 1 ↑ 1 ××××0000~1001加计数1001时CO=0 0 1 1 ↑××××1001~0000减计数0000时BO=0 用M进制集成计数器可以构成N(任意)进制的计数器。通常用反馈清零 法和反馈置数法。当计数器的计数N>M时,则要用多片M进制计数器构成。 其计数规律为:当低位计数器没有达到计数的最大值时,如74LS192的1001时, 其高位芯片应处于保持状态,只有当低位芯片计数达到最大值时,给相邻的高位 芯片计数器发一个信号,使其脱离保持状态,进入计数状态。现以233为例为计 数容量进行设计。由于233为三位数,因此需用三块74LS192。 1、清零法: CR(R D)=(Q1Q0)百(Q1Q0)拾(Q1)个 初态:0000 终态:233-1=232即:0010 0011 0010 状态转换图:(略)

十进制加减可逆计数器的设计

摘要 计数器是数字电路中最为基本的一个单元电路。本次基础强化的目标是要我们熟悉常用MSI集成计数器的功能和应用;掌握利用集成计数器构成不同功能的计数器的设计方法;学会利用EDA软件(Proteus)对模M的可逆计数器电路进行仿真;掌握可逆计数器电路的安装及调试方法。本次课设报告先是说明了十进制加/减可逆计数器的技术指标,简要地陈述了设计方案和设计思路,然后就对其有关理论知识作了一些简要的介绍,然后在性能指标分析基础上进行单元电路设计,设计出整体电路图并且在软件Proteus中进行仿真,最后通过protel 做出电路板验证是否达到技术要求,总结课设体会。 关键词:手动控制,自动控制,计数器,加减可逆

目录 摘要 (1) 1设计任务与要求 (3) 2设计方案及其比较 (3) 2.1 设计方案 (3) 2.2设计思路 (4) 2.2.1手控自动加、减计数器设计思路 (4) 2.2.2自控可逆方式计数器设计思路 (4) 2.2.3手动脉冲设计思路 (5) 2.3集成电路及元件选择 (6) 3实现方案 (6) 3.1 脉冲发生电路实现方案 (6) 3.1.1 基本原理 (6) 3.1.2 有关参数及计算 (7) 3.2 加/减/计数器控制电路实现方案 (7) 3.3 自动控制可逆计数器实现方案 (9) 3.4译码显示单元电路设计实现方案 (10) 3.4.1译码显示单元电路设计 (10) 3.4.2译码器74LS48 (11) 3.4.3显示器LG5011AH (12) 3.4.4译码显示电路 (13) 3.5 手动脉冲发生电路实现方案 (14) 3.6 清零功能实现方案 (15) 3.7 总原理图的设计实现方案 (16) 4 Proteus仿真 (17) 5 制版与调试 (18) 5.1 DXP注意事项 (18) 5.2 制作PCB板的流程 (19) 5.3 注意事项 (19) 5.4 调试结果与分析 (19) 6 课设总结 (20) 谢辞 (21) 参考文献 (22) 附录 (23)

两位计数器电路设计

课题二:两位计数器电路设计(选做) 一.设计目的 本文通过对两位计数器电路的分析、仿真,阐述了计数器电路的一些设计方法,并论证了计数器电路的实现原理及过程。文中还使用了Hspice电路设计仿真软件,这样能让读者更直观的了解计数器电路的工作原理及组成结构。对数字电子技术课程中计数器有新的认识。对Hspice软件使用进一步的掌握。 二.设计原理 计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,在运算器中作乘法、除法运算时记下加法、减法次数,又如在数字仪器中对脉冲的计数等等。 计数器的种类很多,按时钟脉冲输入方式的不同,可分为同步计数器和异步计数器;按进位体制的不同,可分为二进制计数器和非二进制计数器;按计数过程中数字增减趋势的不同,可分为加计数器、减计数器和可逆计数器。

M10 7 8 0 0 NCH L=1U W=80U M2 1 1 4 4 NCH L=1U W=20U M3 1 1 5 5 NCH L=1U W=20U M4 3 2 0 0 NCH L=1U W=80U M5 4 3 6 6 NCH L=1U W=80U V2 2 0 PULSE .2 4.8 2N 1N 1N 5N 20N V3 8 0 5Vdc M6 6 8 0 0 NCH L=1U W=80U M7 4 5 0 0 NCH L=1U W=80U M8 5 4 0 0 NCH L=1U W=80U C1 4 0 .75P C2 5 0 .75P .MODEL NCH NMOS LEVEL=1 .END 原理图如下所示:

三位十进制计数器综述

数电课程设计说明书 题目三位十进制计数器的设计系(部) 电子与通信工程系 专业(班级) 光电信息工程 姓名 学号 指导教师 起止日期6月11日至6月15日

目录 摘要 (3) 关键词 (3) 一、设计内容 (3) 1、设计要求及设计参数: (3) 2、内容要求: (3) 二、设计任务: (3) 三、设计原理 (3) 1、芯片介绍 (3) (1)74ls192芯片 (3) (2)555芯片 (4) (3)三段稳压器(LM7805) (5) 2、三位十进制计数器的工作原理 (6) 3、+5V直流电源的工作原理 (6) 四、仿真图 (6) 1、MultiSim仿真图 (6) (1)三位十进制减计数器 (6) (2)四位十进制加计数器 (7) (3)+5V直流电源 (8) 2、Protel绘制原理图 (8) (1)三位十进制计数器 (8) (2)+5V直流电源 (8) 五、心得体会 (9) 参考文献 (9)

三位十进制计数器设计 摘要: 本次课程设计的题目是三位十进制计数器的设计。就设计三位十进制计数器方案而言,主要选取了3个74ls192芯片、1个555芯片及若干电容电阻。74ls192芯片是双时钟方式的十进制可逆计数器,这就使得设计电路复杂不起来。本设计采用555芯片意在实现一个脉冲发生器,为计数器提供一个脉冲。然后再对其设计方案进行Multisim仿真,测试和分析电路图性能,并采用Protel 绘制原理图、设计PCB板。本次设计的计数器是三位的十进制加计数器,由上升沿触发,通过CO 输出与其他芯片进行级联。由于设计补充要求设计一个+5V的直流电源,本设计中的直流电源主要是运用了模电知识来设计的,其中采用了变压器、三段稳压器、220V的交流输入电源等器材。设计最后补充完成了计数器的真值表和扩展了计数器的位数。 关键词:三位十进制计数器、74ls192芯片、555芯片、+5V的直流电源、Multisim仿真、 Protel绘制原理图,真值表。 一、设计内容 1、设计要求及设计参数: 1)设计一个能计0—999的三位十进制计数器。 (2)要求用数码管显示。 基本部分:设计制作一个能显示三位的十进制计数器,熟悉计数器的基本原理,电路的连线要求采用直线连接和总线连接两种方式,补充完成LED显示条对应的真值表,并完成直流电源5V的设计。发挥部分:举例说明所设计的三位十进制计数器适用于什么场合,设计增加一位(显示4位)的计数器. 2、内容要求: 2、目录、摘要、关键词、设计方案、性能测试与分析、Multisim9 仿真、Protel绘制原理图、设计PCB板、心得体会(设计方案、参数计算、相关软件的使用、电路仿真及PCB设计调试过程中遇到的问题及解决办法); 二、设计任务: 1、理论设计:网络、图书馆查找资料软件应用:学习MultiSim9软件的操作并完成系统原理图的绘制并要求仿真通过; 2、在MultiSim环境下,检测各课题的电路参数、波形;以备完成课程设计说明书; 3、学习Protel软件的操作并完成SCH原理图的绘制及PCB板图的设计; 三、设计原理 1、芯片介绍 (1)74ls192芯片

可逆计数器设计报告

一、题目(二)2、加/减可逆计数器 二、要求:.设计一个4位二进制加/减可逆计数器。控制信号为1时,加计数;0时,减计数。要求写出Verilog代码,给出仿真波形(能反映出所有工作状态)。 三、思路方法: 题目要求的计数器是一个带有低电平负载和清零输入端的同步4位二进制计数器。内部应该像‘163一样采用D触发器而非T触发器,这样便于实现载入和清零功能。每个D触发器的输入由一个2输入多路复用器驱动,这个复用器由1个或门和2个与门构成。如果输入信号CLR_L有效,多路复用器的输出就为0。反之,如果输入信号LD_L有效,上面那个与门就把输入数据传送到输出端。如果CLR_L和LD_L都无效,下面的与门就把”异-或-非”门(XNOR)的输出传送到多路复用器的输出端。 它的二进制计数顺序既可以按升序进行也可以按降序进行,由输入信号UP/DN的值来控制。当UP/DN为1时,按升序计数;当UP/DN为0时,按降序计数。 四、仿真结果及分析 1、Verilog代码 module _counter(CLK,CLR_L,LD_L,ENP_L,ENT_L,UPDN,D,Q,RCO_L); input CLK,CLR_L,LD_L,ENP_L,ENT_L,UPDN; input [3:0]D ; output [3:0]Q; output RCO_L; reg [3:0]Q;

reg RCO_L; always @ (posedge CLK) //Creat the counter f-f behavior if (!CLR_L) Q <= 4'b0; else if(!LD_L) Q <= D; else if(!ENT_L && !ENP_L && UPDN) Q <= Q+1; else if(!ENT_L && !ENP_L && !UPDN) Q <= Q-1; else Q <=Q; always @ (Q or ENT_L or UPDN) //Creat RCO_L combinational output if (!ENT_L && UPDN && (Q == 4'd15)) RCO_L = 0; else if (!ENT_L && !UPDN && (Q == 4'd0)) RCO_L = 0; else RCO_L = 1; endmodule 2、所有功能的仿真结果 (1)加计数:计数器工作再自由计数模式且UPDN=1,计数器从0000加计数到1111时,RCO_L输出一个周期的低电平,然后计数器跳回0000重新开始计数。 结果分析:从仿真图中可以看到,Q从0000计数到1111然后跳回0000重新开始计数,满足计数要求。 (2)减计数:计数器工作再自由计数模式且UPDN=0,计数器从1111减计数到0000时,RCO_L输出一个周期的低电平,然后计数器跳回1111重新开始计数。

一款由555定时器和四位二进制可逆计数器74193构成的灯泡计时器电路图

本文介绍一款灯泡计时器电路,此电路主要有555定时器和四位二进制可逆计数器74193和一块7447芯片构成。 芯片简介: 555定时器是一种模拟和数字功能相结合的中规模集成器件。555 定时器的功能主要由两个比较器决定。两个比较器的输出电压控制RS 触发器和放电管的状态。使用方便,只需要外接几个电阻、电容,就可以实现多谐振荡器、单稳态触发器及施密特触发器等脉冲产生与变换电路。 74193是“二进制、可预置、加减计数器”。即在D0-D3上预置一个2进制数,PL引脚下跳沿将其送至Q0-Q3,此时如在CPU引脚上出现脉冲,Q0-Q3的数字就递增;如在CPD引脚上出现脉冲,Q0-Q3的数字就递减。当递增的数字超过15,TCU引脚就出现进位低电平。当递减的数字超过0,TCD 引脚就出现借位低电平。MR引脚拉高,输出端Q0-Q3全部置零。 7447是一块BCD码转换成7段LED数码管的译码驱动IC,7447的主要功能是输出低电平驱动的显示码,用以推动共阳极7段LED数码管显示相应的数字。

灯泡计时器电路 定时开关利用一个555振荡器/计时器在非稳态模式下有线运转。该定时器每五分钟就为74193的4比特二进制上下数提供正脉冲。因为74193是在递减速计数模式下运行的,555的输出直接连接74193的递减速计数的输入。 如果您有PCB 打样、中小批量板生产等需求的话,可以访问捷多邦官网 https://www.360docs.net/doc/255208742.html, 在线计价,也可以关注 捷多邦PCB 公众号在微信中直接咨

询或下单。 捷多邦总部位于深圳,在杭州设外贸事业部,在惠州、坪山、沙井设三大线路板厂区。品质先行:捷多邦专业做板,坚持240分钟沉铜电镀,拒绝导电胶。极速交期:捷多邦在业内率先采用航空专线,当日下单最快次日即达。欢迎体验! 原文链接:https://https://www.360docs.net/doc/255208742.html,/circuit/2421.html

可逆计数器

可逆计数器 可逆计数器是一种双向计数器,可以进行递增计数,也可以进行递减计数,根据计数控制信号的不同,在时钟脉冲的作用下,计数器可以进行加1或减1的操作。 下面描述的是一个位宽为4的可逆计数器,即该计数器在不同控制信号下可以分别实现加法计数和减法计数的功能。 rst为同步复位信号,当rst = 1时,dout = 4’b0000;当load = 1时,输入信号din通过dout 输出;若add_en = 1时,计数器在每个时钟上升沿实现加1的操作,即实现加法计数功能;若add_en = 0时,计数器在每个时钟上升沿实现减1的操作,即实现减法计数功能。 其verilog HDL 设计代码如下: 1.module counter_i(clk, rst, load, add_en, din, dout); 2. input clk, rst, load, add_en; 3. input [3:0] din; 4. output [3:0] dout; 5. reg [3:0] dout; 6. 7. always @(posedge clk) 8. begin 9.if(rst == 1'b1) 10. dout <= 4'b0000; 11.else if(load == 1'b1) 12. dout <= din; 13.else if(add_en == 1'b1) 14. begin 15.if(dout == 4'b1111) //如果dout为15时,则输出清零; 16. dout <= 4'b0000; 17.else 18. dout <= dout + 1'b1; 19. end 20.else 21. begin 22.if(dout == 4'b0000) //递减计数器计数到dout = 4'b0000时,则 置位为4'b1111 23. dout <= 4'b1111; 24.else 25. dout <= dout - 1'b1; 26. end 27. end 28.endmodule 测试文件为: