器件管脚图及功能表

1

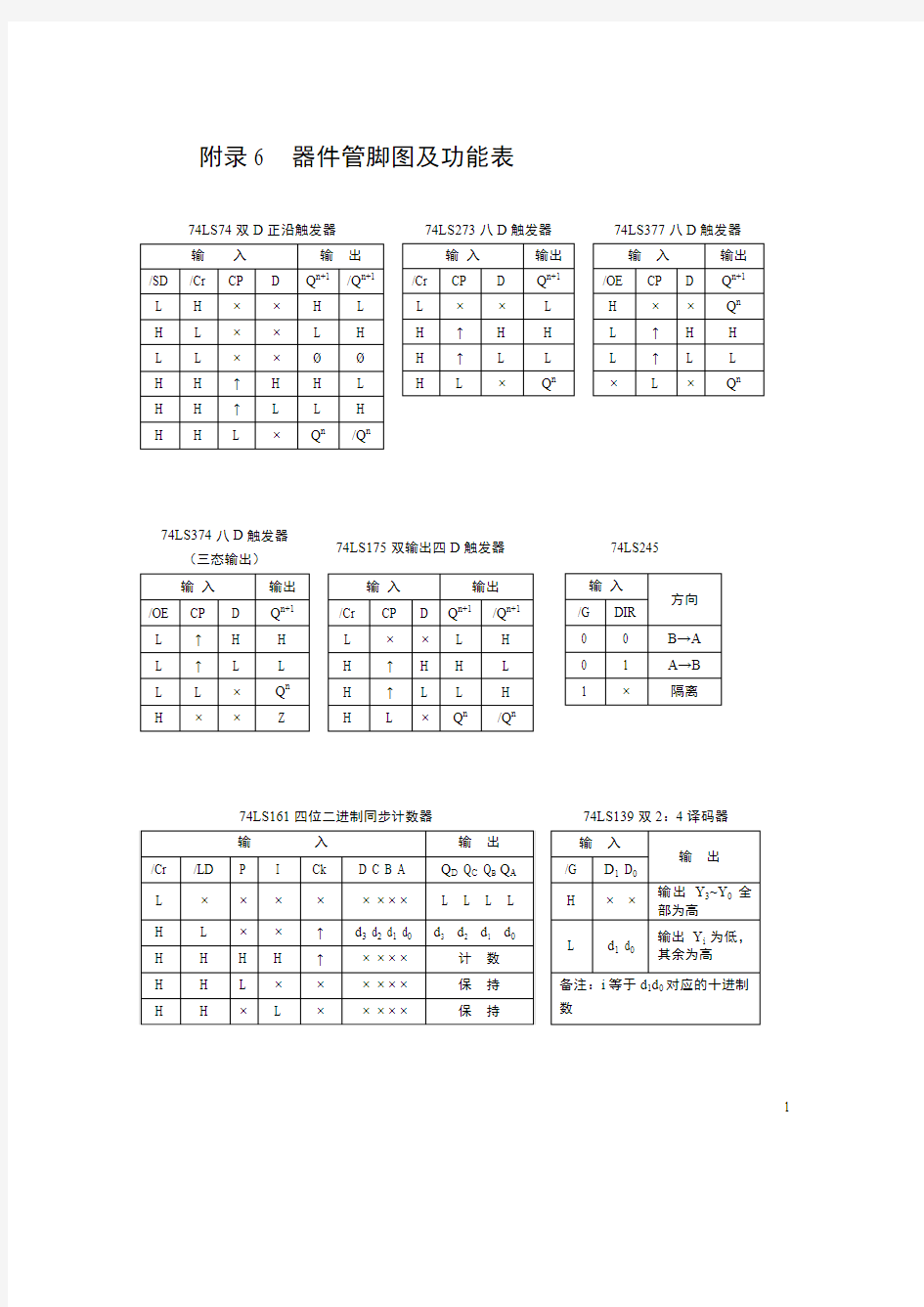

附录6 器件管脚图及功能表

74LS74双D 正沿触发器 74LS273八D 触发器 74LS377八D 触发器

74LS374八D 触发器

(三态输出) 74LS175双输出四D 触发器

74LS245

74LS161四位二进制同步计数器 74LS139双2:4译码器

2

74LS151 八选一选择器

74LS157 四个二选一选择器

74LS257 四个二选一选择器

(非反相三态输出)

注:i 等于d 2d 1d 0对应的十进制数

6116 2K*8 RAM 2716 2K*8 ROM 2732 4K*8 ROM

74LS138 3:8译码器 74LS148 8:3八进制优先编码器

74LS85 四位幅度比较器

附录9微指令寄存器的各字段微操作信号输出去向及功能

指令字段IR7~0

3

附录10 联机通讯指南

一、准备

1、准备一台PC机。

2、把TEC-2机在实验台上放好打开,将TEC-2的随机电源放在TEC-2的左侧,并确认电源开关处在关断的位置。

二、连接电源线

1、将TEC-2机电源的直流输出插头P8插在TEC-2机垂直板左侧的插座P8上;

将TEC-2机电源的直流输出插头P9插在TEC-2水平板左侧的插座P9上。

特别提醒注意:不要接反P8和P9,否则会烧机器或电源。

2、将TEC-2电源的电源线一端接电源的交流输入插孔,另一端接220V交流电源接线盒。

注意:TEC-2电源的交流电源线必须和计算机的电源线接在同一个有地线的电源接线盒上,以保证两设备共地,否则可能烧毁电源或机器。

三、连接TEC-2和PC

1、准备好随机提供的TEC-2和PC的串口通讯电缆。该电缆一端是9孔的插头,另一端是25孔的插头。

注意:TEC-2随机提供多条通讯电缆,请务必正确选用,以免错误连接造成联机失败。

2、把串口通讯电缆的9孔插头接在TEC-2机的上板左下角V70插座上,25孔插头插在计算机的串口上(COM1或COM2)。

如果PC上没有25针的串口或者25针的串口已被其它设备占用,TEC-2 随机提供一个9转25的转换器可以把25孔的插头转换成9孔的插头,接在9针的串口上。

四、TEC-2的初始设置

将TEC-2大板下方钮子开关S2~S0拨成100(向上为“1”,向下为“0”);

FS1~FS4拨成1010(向上为“1”,向下为“0”);

将CONT/STEP钮子开关拨到CONT位置。

五、开机

1、打开计算机电源开关,使计算机正常启动。

2、打开TEC-2电源开关,TEC-2大板左上角一排指示灯亮。

六、加载通讯软件

1、用户可以根据联机PC的软件配置情况选择以下三种方法之一运行联机通讯软件。4

5

? 如果计算机没有硬盘,把用户程序盘插入软驱,并用它启动计算机,然后键入: A :\>CD TEC-2 A :\>PCEC

? 如果计算机有硬盘并且装有DOS 操作系统,则进行以下操作: C :\>MD TEC-2

C :\>COPY A :\TEC-2 C :\TEC-2 C :\>C

D TEC-2 C :\TEC-2>PCEC

? 如果计算机有硬盘并且装有WINDOWS 操作系统,把用户程序盘插入软驱,将软盘中的文件夹“TEC-2”拷贝到C :\盘,点击“开始→运行”,在弹出的窗口中键入:

C :\TEC-2\PCEC ↙

正确执行上述操作就会在计算机屏幕上出现以下界面:

2、用计算机的串口COM1和TEC-2通讯,选择“1”,直接回车; 用计算机的串口COM2和TEC-2通讯,选择“2”,然后按回车键。 此时计算机屏幕上出现以下设置信息:

*************************************************************

Baud Rate = 9600 bits/second Parity = None Stop bit = 1 bit

Character Length = 8 bits Change these characters ? (N )

*************************************************************

F10→Display Main Menu

ALT F10→Copy Screen to File SCA.TMP

RS232 Serial Port Number [1/2]:

1

**********************************************************

此界面的设置为推荐设置,键入“N”键后回车。然后按压TEC-2大板左下角的LDMC/RESET键加载微程序。这时计算机屏幕出现以下界面表示联机成功:****************************************************************

TEC-2 CRT MONITOR

Version 5.0, Jan. 1994

Computer Architecture Lab., Tsinghua University

>

****************************************************************

此时可以运行TEC-2计算机系统的指令,如U、D、T、P、A等或做TEC-2计算机组成原理的实验。

如果按压LDMC/RESET键后屏幕上没有任何反应,这时可按F10屏幕出现以下界面:****************************************************************

0…Return to TEC-2 CRT Monitor

1…Send a file to TEC-2

2…Receive a file from TEC-2

3…Return to PC (MS) –DOS

Enter your choice:[0]

****************************************************************

选(3)或者按Ctrl+Pause键退出联机通讯程序,重新运行程序PCEC,并选择另一个串口再试。

注意:开机时先开计算机的电源,当计算机正常启动后,再打开TEC-2机的电源;关机时应先关掉TEC-2机的电源,再关掉计算机的电源。任何时间一定不要带电操作。

6

7

附录11 并行接口芯片8255A 简介

1.8255A 的内部结构

8255A 的内部结构如图3.11.1所示。它由以下几个部分组成: (1)三个数据端口A 、B 、C

8255A 芯片内部有三个8位的输入输出端口,分别为A 口、B 口和C 口,可用指令将它们分别设置成输入或输出端口。它们在结构和功能上有各自的特点。

图 3.11.1 8255A 的内部结构及引脚

端口A 包含一个8位数据输入锁存器和一个8位的数据输出锁存器/缓冲器。端口A 无论用作输入口还是输出口,其数据均能受到锁存。

端口B 包含一个8位数据输入缓冲器和一个8位的数据输出锁存器/缓冲器。用端口B 作为输出口时,其数据能得到锁存。作为输入口时,它不具有锁存能力,因此外设输入的数据必须维持到被CPU 读取为止。

端口C 包含一个8位数据输入缓冲器和一个8位的数据输出锁存器/缓冲器,作为输入口时,它不具有锁存能力。

端口A 和端口B 一般作为独立的I/O 口使用,与外设的数据线相连。端口C 可以作为一个独立的8位I/O 口,也可以拆分为高4位和低4位的两个4位端口,作为二个独立的4位I/O 口使用;端口C 拆分开的高4位和低4位还可以与端口A 和端口B 配合,用作它们的联络信号线。

(2)A 组控制、B 组控制

8255A 将端口A 、B 、C 分为两组:端口A 和端口C 的高4位构成A 组,由A 组控制逻辑电路进行控制;端口B 和端口C 的低4位构成B 组,由B 组控制逻辑电路进行控制。这两组控制逻辑都从读/

写控制逻辑接收命令信号和读写信号,从内部数据总线接收控制字,并根据控

制字确定各端口的工作方式。

(3)数据总线缓冲器

数据总线缓冲器是一个双向三态的8位缓冲器,它直接与系统数据总线连接,是8255A 与CPU之间传输数据的必经之路,数据的输入输出以及控制字的写入都是通过这个缓冲器传递的。

(4)读/写控制逻辑

读/写控制逻辑电路负责管理8255A的数据传输过程。它接收来自控制总线的控制信号/WR、/RD、RESET和地址总线的A1、A0以及由地址译码输出的片选信号/CS,由这些信号形成对端口的读写控制,并通过A组控制和B组控制电路实现对数据、状态和控制信息的传输。

2.8255A的外部引脚

8255A芯片采用NMOS工艺制造,是一个40引脚双列直插式(DIP)封装组件。其引脚排列如图3.11.1所示,各引脚信号名称和含义如下。

(1)与CPU连接的信号线

D7~D0:8255A的双向三态数据线,和系统的数据总线相连。

A1、A0、/RD、/WR、/CS信号组合所实现的各种端口操作见表3.11.1所示。

表 3.11.1

(2)8255A与外部设备相连的信号线

PA7~PA0:A口与外部设备连接的数据线,由A口的工作方式决定这些引脚用作输入、输出或双向。

PB7~PB0:B口与外部设备连接的数据线,由B口的工作方式决定这些引脚用作输入或输出。

8

9

PC7~PC0:C 口输入输出数据线,这些引脚的用途由A 组,B 组的工作方式决定。 这24根信号线均可用来连接I/O 设备,它们可以传送数字量或开关量信号,C 端口还常常用来传递控制和状态信号。

3.8255A 的控制字

8255A 有两类控制字:一类用于定义各端口的工作方式,称为方式选择控制字;另一类用于对C 端口的一位进行置位或复位操作,称为C 端口置位/复位控制字。这里只介绍方式选择控制字。

(1)方式选择控制字

8255A 共有三种基本工作方式,它们是: 方式0:基本的输入/输出方式。

方式1:选通输入/输出方式(应答方式)。 方式2:双向传输方式。 这里只介绍8255A 的方式0。

8255A 各数据端口的工作方式由方式选择控制字(如图3.11.2所示)进行设置。对8255A 进行初始化编程时,通过向控制字寄存器写入方式选择控制字,可以让三个数据端口以需要的方式工作。

图 3.11.2 8255A 的方式选择控制字

其中,D7位是方式选择控制字的标志位,它必须是1;D6D5位用于选择A 口的工作方式;D2位用于选择B 口的工作方式;D4、D3、D1、D0位分别用于选择A 口、C 口高四位、B 口和C 口低四位的输入输出功能,置1时输入,置0时输出。

端口A可工作在3种工作方式中的任何一种,端口B只能工作在方式0或方式1,端口C则常常配合端口A和端口B工作,为这两个端口的输入/输出传输提供控制信号和状态信号。只有端口A可工作在方式2。

同组的两个端口可以分别作为输入或输出端口,允许它们有不同的传输方向。一个端口用作输入还是输出端口,完全通过对方式选择控制字的编程来确定。

4.8255A的工作方式0—基本输入/输出方式

方式0称为基本输入输出方式,该方式下3个端口24根数据线完全由使用者决定它们的用途。可将三个数据端口划分为四个独立的部分:A口和B口作为两个8位端口,C口的高4位和低4位可以用作两个4位端口(当然也可以作为一个8位端口),各个端口都可以独立用作输入或输出。

方式0使用在无条件传送和查询式传送两种场合。

无条件传送一般用于连接简单的外部设备。例如,键盘和开关状态输入,状态指示灯输出。

进行无条件传送时,接口和外部设备之间不使用联络信号,CPU可以随时对该外部设备进行读写。用8255A进行无条件传送时,可实现三路8位数据或两路8位及两路4位的数据传输。

进行查询式传送时,端口A和端口B作为数据的输入输出口,端口C的若干位用作联络信号。把C端口的一组(4位)设置为输出,用作端口A和端口B的控制信号输出。把C端口的另一组(4位)设置为输入,用作端口A和端口B的外设状态信号输入。两个组中剩余的引脚信号还可以用于其他控制,例如控制指示灯,或者开关输入。这样,利用端口C的配合,可实现端口A和端口B的查询式数据传输。

例:在TEC-2机中8255A的端口A地址为84H、端口B地址为85H、端口C地址为86H、控制端口地址为87H,现要求将其三个数据端口设置为方式0—基本的输入输出方式,其中端口A和端口C的低4位为输出,端口B和端口C的高4位为输入。由图3.11.2可知,该8255A的方式选择控制字应为8AH。其初始化程序如下:

MOV R0,8A

OUT 87

读端口B的汇编语句是:IN 85;端口B的数据送到R0

写端口A的汇编语句是:OUT 84;R0的数据送到端口A

10

11

5.8255A 与CPU 的连接

8255A 和CPU 连接时,数据线和控制线一般直接和系统总线的相应信号相连,片选信号和地址译码器的输出相连,端口选择信号A1、A0和地址总线的A1、A0直接相连,三个端口的数据线和外设的数据线直接相连。在实验中,TEC-2与8255A 的一般的连接方式如图3.11.3所示。

图 3.11.3 TEC-2与8255A 的一般的连接方式

附录12 串行接口芯片8251A简介

1.串行通讯的基本概念

通信方式可分为并行通信和串行通信两种。串行通信是指在单根导线上将二进制数据一位一位顺序传送,与并行通信相比,由于所用的传输线少,并且可以借助现存的电话交换网进行信息传送,因此,特别适合于远距离传送。对于离计算机较近的外部设备如鼠标、绘图仪、终端等,也常常采用串行方式交换数据。所以,串行接口是微机应用系统常用的接口。

串行通信线路有如下3种方式:

(1)单工通信:它只允许一个方向传输数据,如图3.12.1(a)所示。A只作为数据发送器,B只作为数据接收器,不能进行反方向传输。

(2)半双工通信:它允许两个方向传输数据,但不能同时传输,只能交替进行,A发B 收或B发A收,如图3.12.1(b)所示。在这种情况下,为了控制线路换向,必须对两端设备进行控制,以确定数据流向。这种协调可以靠增加接口的附加控制线来实现,也可用软件约定来实现。

(3)全双工通信:它允许两个方向同时进行数据传输,A收B发的同时可A发B收,如图3.12.1(c)所示。显然,两个传输方向的资源必须完全独立,A与B都必须有独立的接收器和发送器,从A到B和从B到A的数据通路也必须完全分开(至少在逻辑上是分开的)。

图 3.12.1 串行通信线路的3种方式

串行通信分为两种类型:异步串行通信和同步串行通信。

所谓异步通信是指通信中字符与字符之间没有严格的定时要求,而字符内位与位之间有严格而精确的定时。异步通信的格式见图3.12.2。通信线路上传送的每个字符包括1个起始位、5~8个数据位(低位先传送)、1个奇偶校验位(可无)以及1~2个停止位。起始位和停止位分别用来表示字符的开始与结束,由此构成的一串数据叫做帧。从图3.12.2可以看到,一帧数据中位与位之间的时间间隔是固定的,而相邻两帧的数据之间其时间间隔是不

固定的。

12

13

图 3.12.2 帧的格式

异步通信时字符是一帧帧传送的,每帧字符的传送靠起始位同步。为了保证正常通信,通信双方在通信之前必须约定:

① 字符格式,即一个字符包含多少个数据位、停止位以及采用何种校验形式。 ② 波特率,即数据传送的速率,用位/秒(bit/s ,或bps )来表示,也就是图3.12.2中二进制位持续时间的倒数,它也是衡量传输通道频宽的指标。例如,设数据传送的速率为120字符/秒,每个字符(帧)包括10个数据位,则传送的波特率为10×120=1200位/秒=1200波特,则每一位传送的时间为Td=1/1200=0.833ms 。

同步传送不给每个字符加起始位和停止位,而是把字符顺序连接起来,组成一个数据块。在数据块的开头设置1~2个同步字符SYNC ,表示数据传送的开始,在数据块的末尾加有一定的差错校验字符。在同步通信时,数据是连续发送的,字符与字符之间没有空隙,严格按照约定的速率发送和接收。

2.8251A 的主要性能和内部结构

825lA 是可编程的串行通信接口芯片,它的基本性能如下:

(1) 可工作在同步方式,也可工作在异步方式。同步方式下波特率为0~64000波特,异步方式下波特率为0~19200波特。

(2) 在同步方式时,每个字符可定义为5、6、7或8位。两种方法实现同步,由内部自动检测同步字符或由外部给出同步信号。允许同步方式下增加奇/偶校验位进行校验。

(3) 在异步方式下,每个字符可定义为5、6、7或8位,用1位作奇偶校验。时钟速率可用软件定义为波特率的l 、16或64倍。另外,8251A 在异步方式下能自动为每个被输出的数据增加1个起始位,并能根据软件编程为每个输出数据设置1位、1.5位或2位停止位。

(4) 能进行出错检测。带有奇偶、溢出和帧错误等检测电路,用户可通过输入状态寄存器的内容进行查询。

8251A 的内部结构框图如图3.12.3所示。从图中可以看出,它由数据总线缓冲器、读

/

写控制逻辑、发送缓冲器、发送控制器、接收缓冲器、接收控制器、调制/解调器控制逻辑、同步字符寄存器及控制各种操作的方式寄存器等组成。各部件实现的功能如下所述。

1) 数据总线缓冲器

数据总线缓冲器通过8位数据线D7~D0和CPU的数据总线相连,负责把接收口接收到的信息送给CPU,或把CPU发来的信息送给发送口。还可随时把状态寄存器中的内容读到CPU 中,在825lA初始化时,分别把方式字、控制字和同步字符送到方式寄存器、控制寄存器和同步字符寄存器中。

2) 读/写控制逻辑

表3.12.1是8251A的控制信号与执行的操作之间的对应关系。

3) 发送缓冲器包括发送移位寄存器和数据输出寄存器,发送移位寄存器通过825lA芯片的TxD管脚将串行数据发送出去。数据输出寄存器寄存来自CPU的数据,当发送移位寄存器空时,数据输出寄存器的内容送给移位寄存器。发送控制电路对串行数据实行发送控制。

表3.12.1 8251A的控制信号与执行的操作之间的对应关系

4) 接收缓冲器与接收控制器

接收缓冲器包括接收移位寄存器和数据输入寄存器。串行输入的数据通过8251A芯片的

14

15

RxD 管脚逐位进入接收移位寄存器,然后变成并行格式进入数据输入寄存器,等待CPU 取走。接收控制电路是用来控制数据接收工作。

5) 调制/解调器控制逻辑

利用8251A 进行远距离通信时,发送方要通过调制解调器将输出的串行数字信号变为模拟信号,再发送出去。接收方也必须将模拟信号经过调制解调器变为数字信号,才能由串行接口接收。在全双工通信方式下,每个收、发口都是要连接调制解调器。调制解调器控制电路是专为调制解调器提供控制信号用的。

3.8251A 的外部特性

(1)8251A 与CPU 的接口信号

8251A 外部引脚如图3.12.4所示,它与CPU 的接口信号可以分为五类,具体如下。

1) 双向的数据信号线D7~D0

825lA 有8条数据线D7~D0。825lA 通过这8根线和CPU 的数据

总线相连接,实际上,数据线上不只是传输数据,还传输CPU 对825lA 的编程命令字和825lA 送往CPU 的状态信息。

2) 片选信号/CS

低电平有效,芯片被选中才能工作,如果8251A 未被选中,数据线D7~D0将处于高阻状态,读/写信号对芯片都不起作用。

3) 读/写控制信号

/RD 为读信号,低电平有效。当该信号有效时,并且/CS 也为低电平,CPU 可以从8251A 读取数据或状态信息。

/WR 为写信号,低电平有效。当该信号有效时,并且/CS 也为低电平,CPU 可以向8251写入数据或控制字。

C/ D 为控制/数据信号,分时复用。用来区分当前读/写的是数据还是控制信息或状态信息。当C/ D 为高电平时,系统处理的是控制信息或状态信息,从D7~D0端写入8251A 的必须是方式字、控制字或同步字符。当C/ D 为低电平时,写入的是数据。

RESET 为复位信号,高电平有效。当该信号为高时,8251A 实现复位功能,内部所有的寄存器都被置为初始状态。

CLK 为主时钟信号,用于芯片内部的定时。对于同步方式,它的频率必须大于发送时

图 12.4 图 3.12.4 8251A

外部引脚

钟/TxC和接收时钟/RxC的30倍。对于异步方式,必须大于它们的4.5倍。

8251A的时钟频率规定在0.74~3.1 MHz的范围内。

8251A共有三种时钟信号:CLK、/TxC和/RxC 。其中发送时钟和接收时钟由波特率和波特率因子来决定。

4)与发送有关的联络信号

TxRDY为发送器准备好信号,高电平有效。当该信号为高电平时,通知CPU,8251A 已经准备好发送一个字符,表示CPU可以输入数据。所谓发送器准备好,就是控制字的第0位TxEN为“1”时,使8251A允许发送,并且调制解调器已做好接收准备,发出信号使8251A 的/CTS信号变低为有效,因此TxRDY为输出缓冲器空与/CTS与TxEN。TxRDY可作为中断申请信号,也可作为查询方式的联络信号使用。

TxE为发送器空信号,状态线,高电平有效。当有效时表示发送器中的并行到串行转换器空,指示发送操作已经结束。8251A从CPU接收待发的字符后,自动复位,字符串发送完毕,TxE又变为高电平。

5)与接收有关的联络信号。

RxRDY为接收器准备好信号,高电平有效。当该信号为高时,表示825lA已从外部设备或调制解调器中收到一个字符,等待CPU取走。它可以作为中断请求信号或查询联络信号与CPU联系。

/RxC接收器时钟,由外部输入。这个钟频率决定8251A接收数据的速率。若采用同步方式,接收器时钟频率等于接收数据的频率;若采用异步方式,可用软件定义接收数据的波特率,情况与发送器时钟/TxC相似。

一般,接收器时钟应与对方的发送器时钟相同。

(2)8251A与外部装置之间的接口信号

8251A与外部装置进行连接的信号可大致分为数据信号和收发联络信号两类。

1)数据信号

TxD为发送数据信号端。CPU送入825lA的并行数据,在825lA内部转换为串行数据,通过TxD端输出。

RxD为接收数据信号端。RxD用来接收外部装置通过传输线送来的串行数据,数据进入825lA后转换为并行数据。

2)发送数据时的联络信号

/RTS为请求发送信号,低电平有效。这是8251A向调制解调器或外设发送的控制信息,初始化时由CPU向825lA写控制命令字来设置。该信号有效时,表示CPU请求通过825lA向调

16

17

制解调器发送数据。

/CTS 为发送允许信号,低电平有效。这是由调制解调器或外设送给8251A 的信号,是/RTS 对的响应信号,只有当/CTS 为低电平时,825lA 才能执行发送操作。

3)接收数据时的联络信号

/DTR 为数据终端准备好信号,低电平有效。是由8251A 送出的一个通用的输出信号,初始化时由CPU 向8251A 写控制命令字来设置。该信号有效时,表示为接收数据做好了准备,CPU 可以通过8251A 从调制解调器接收数据。

/DSR 为数据装置准备好信号,低电平有效。这是由调制解调器或外设向8251A 送入的一个通用的输入信号,是/DTR 的回答信号,CPU 可以通过读取状态寄存器的方法来查询/DSR 是否有效。

以上发送数据和接收数据的联络信号,对于远距离串行通信时要通过调制解调器连接,实际上是和调制解调器之间的连接信号。如果近距离传输时,可不用调制解调器,而直接通过MCl488和MCl489来连接,外设不要求有联络信号时,这些信号可以不用。

使用MC1488和MC1489芯片时,传输时的电平是RS-232 C 标准电平,所能传输的最大距离是30 m ,一般不超过15 m 。数据传输的波特率低于20000波特。连接如图3.12.5。

图 3.12.5 TTL 与EIA 相互转换

4.8251A 的编程地址

从表3.12.1看到,8251A 实际上只需要两个端口地址:一个用于数据端口,一个用于控制端口。数据输入端口和数据输出端口可合用一个端口;状态端口和控制端口也可合用一个端口。只用读信号/RD 和写/WR 信号即可区分是数据输入还是数据输出,是状态端口还是控制端口,状态端口只能读不能写。这样在具体的硬件设计时可简化电路连接。

在TEC-2机中,地址线AB0和C/D 相连接,片选通过地址译码得到,/RD 、/WR 分别与控制总线的/IOR 和/IOW 相连。所进行的操作见表3.12.1。

5.8251A 的控制、状态字

1)方式控制字

方式寄存器是8251A

在初始化时,用来写入方式选择字。方式选择有两种:同步方式和

18 异步方式。此处只介绍异步方式。方式控制字各字段的含义如下图3.12.6所示:

图3.12.6 8251A 方式控制字

例如,要求8251A 芯片作为异步通信、波特率为64、字符长度8位、奇校验、2个停止位的方式选择字应为十六进制的DFH (1101111lB =DFH )。

2)命令控制字

对8251A 初始化时,写入了方式选择字后,接着要写入命令字,格式如图3.12.7所示。

图 3.12.7 8251A 命令控制字

由命令字来规定8251A 的工作状态,才能启动串行通信开始工作或置位。这样就要对控制寄存器输入控制字。

控制寄存器也是8位,每位的定义如下:

(1)D0(TxEN):TxEN 位是发送允许位,只有等于1,发送器才能由TxD 引脚向外部发送数据。

(2)D1(/DTR ):/DTR 位是数据终端准备好。/DTR=1时强制/DTR 引线端输出低电平。 (3)D2(RxE ):RxE 位是允许接收位,RxE=1,8251A 才能从RxD 引脚接收数据。

(4)D3(SBRK):SBRK是发送间断位。SBRK=1,TxD输出连续的空信号。正常情况该位应为“0”。

(5)D4(ER):ER位用来复位状态寄存器的出错位,状态寄存器共有三个出错标志位,分别是奇偶校验错PE、超越错OE、帧格式错FE。ER=1,将同时将这三个出错标志位清“0”。

(6)D5(/RTS):/RTS是请求发送信号控制位,/RTS=1,将使8251A的/RTS引脚输出低电平,表示CPU已作好发送数据准备,请求向调制解调器或外设发送数据。

(7)D6(IR):IR是内部复位控制。IR=1,使8251A进入复位状态。

(8)D7(EH):EH为搜索方式位。EH只对同步方式有效,EH=1,表示开始搜索同步字符。

3)状态寄存器

状态寄存器是反映8251A内部工作状态的寄存器,只能读出,不能写入。CPU可用IN指令来读取状态寄存器的内容。状态寄存器的格式如图3.12.8所示。状态寄存器也是8位,每位的定义如下:

图 3.12.8 8251A状态字

(1)D0(TxRDY):TxRDY位是发送器准备好,TxRDY=1表示发送缓冲器空。注意它与芯片引脚TxRDY意义的区别。引脚TxRDY为“1”除表示发送缓冲器已空外,还满足两个条件/CTS=0和TxEN=1。通常,TxRDY状态位供CPU查询,TxRDY引脚则用作向CPU发出的中断请求信号。

(2)D1(RxRDY):接收器准备好信号,该位为“1”时,表明接收口已接收到一个字符,当前正准备输入CPU中。当CPU从8251A输入一个字符时,RxRDY自动清0。

(3)D2(TxE):与TxE引脚端的状态完全相同。

19

(4)D3(PE):PE是奇偶校验错标志。当发现校验错时,PE=1。

(5)D4(OE):OE是超越错标志。OE=1表示上一个字符还未被CPU读出之前,接收器又收到新的字符,从而使上一字符丢失。

(6)D5(FE):FE是帧出错标志,只对异步方式有效。FE=1表示未检测到停止位。

(7)D6(SYNDET/BRKDET):SYNDET/BRKDET位与同名引脚端的状态完全相同。

(8)D7(/DSR):/DSR位是数据设备准备好,反映芯片引脚/DSR的状态。引脚/DSR=0,/DSR位=1。

6.8251A的编程应用举例

要使8251A工作,必须首先进行芯片初始化。初始化时CPU首先向芯片输出方式控制字,如果选择异步方式,紧接着需输出命令控制字。

在TEC-2机中,监控程序已对两个8251进行了初始化。其程序如下:

MOV R0,4EH ;4EH为01001110B

OUT 81H ;第一个8251A命令寄存器地址

OUT 83H ;第二个8251A命令寄存器地址

MOV R0,37H ;37H为00110111B

OUT 81H

OUT 83H

4EH完成了串行口的方式设定。

D1D0为10,设/TxC和/RxC的工作频率为数据传送波特率的16倍

D3D2为11,字符长度为8位

D5D4为00,不执行奇偶校验

D7D6为01,使用1位停止位

37H完成了命令设定。

D2D1D0为111,使8251处于可以接收与发送状态

D4为1,8251初始化,即清除8251芯片内的出错标志

D5为1,表明CPU请求发送

上述6条指令完成2个串口的工作方式设定、初始化并使其进入运行状态。

8251A在查询方式下,进行数据传输的实例参见实验七中的双机通讯实验。

20

元器件封装及基本管脚定义说明(精)知识讲解

元器件封装及基本管脚定义说明 以下收录说明的元件为常规元件 A: 零件封装是指实际零件焊接到电路板时所指示的外观和焊点的位置。包括了实际元件的外型尺寸,所占空间位置,各管脚之间的间距等,是纯粹的空间概念。因此不同的元件可共用同一零件封装,同种元件也可有不同的零件封装. 普通的元件封装有针脚式封装(DIP与表面贴片式封装(SMD两大类. (像电阻,有传统的针脚式,这种元件体积较大,电路板必须钻孔才能安置元件,完成钻孔后,插入元件,再过锡炉或喷锡(也可手焊),成本较高,较新的设计都是采用体积小的表面贴片式元件(SMD )这种元件不必钻孔,用钢膜将半熔状锡膏倒入电路板,再把SMD 元件放上,即可焊接在电路板上了。 元件按电气性能分类为:电阻, 电容(有极性, 无极性, 电感, 晶体管(二极管, 三极管, 集成电路IC, 端口(输入输出端口, 连接器, 插槽, 开关系列, 晶振,OTHER(显示器件, 蜂鸣器, 传感器, 扬声器, 受话器 1. 电阻: I.直插式 [1/20W 1/16W 1/10W 1/8W 1/4W] AXIAL0.3 0.4 II. 贴片式 [0201 0402 0603 0805 1206] 贴片电阻 0603表示的是封装尺寸与具体阻值没有关系 但封装尺寸与功率有关通常来说 0201 1/20W 0402 1/16W 0603 1/10W

0805 1/8W 1206 1/4W 电容电阻外形尺寸与封装的对应关系是: 0402=1.0x0.5 0603=1.6x0.8 0805=2.0x1.2 1206=3.2x1.6 1210=3.2x2.5 1812=4.5x3.2 2225=5.6x6.5 III. 整合式 [0402 0603 4合一或8合一排阻] IIII. 可调式[VR1~VR5] 2. 电容: I.无极性电容[0402 0603 0805 1206 1210 1812 2225] II. 有极性电容分两种: 电解电容 [一般为铝电解电容, 分为DIP 与SMD 两种] 钽电容 [为SMD 型: A TYPE (3216 10V B TYPE (3528 16V C TYPE (6032 25V D TYP E (7343 35V] 3. 电感: I.DIP型电感 II.SMD 型电感

常用电子器件管脚排列图

常用电子器件管脚排列图 附录1 逻辑符号对照示例 附录表1.1 逻辑非、逻辑极性符号对照示例(以反相器为例) 附录表1.2 几种常用逻辑门的逻辑符号比较示例 附录表1.3 逻辑符号、框图、管脚排列比较示列(以74HC390为例)

附录2 集成电路 1. 集成电路命名方法 集成电路命名方法见附录表2.1 附录表2.1 国产半导体集成电路型号命名法(GB3430-82) 2.集成电路介绍 集成电路IC 是封在单个封装件中的一组互连电路。装在陶瓷衬底上的分立元件或电路有时还和单个集成电路连在一起,称为混合集成电路。把全部元件和电路成型在单片晶体硅材料上称单片集成电路。单片集成电路现在已成为最普及的集成电路形式,它可以封装成各种类型的固态器件,也可以封装成特殊的集成电路。 通用集成电路分为模拟(线性)和数字两大类。模拟电路根据输入的各种电平,在输出端产生各种相应的电平;而数字电路是开关器件,以规定的电平响应导通和截止。有时候集成电路标有LM (线性类型) 或DM(数字类型)符号。 集成电路都有二或三个电源接线端:用CC V 、DD V 、SS V 、V +、V -或GND 来表示。这是一般应用所需要的。 双列直插式是集成电路最通用的封装形式。 其引脚标记有半圆形豁口、标志线、标志圆点 等,一般由半圆形豁口就可以确定各引脚的位置。 双列直插式的引脚排列图如附录图2.1所示。 3.使用TFL 集成电路与CMOS 集成电路的注意事项 (1) 使用TYL 集成电路注意事项 ① TYL 集成电路的电源电压不能高于V 5.5+。 使用时,不能将电源与地颠倒错接,否则将会因为过大电流而造成器件损坏。 附录图 2.1双列直插式集成电路的引脚排列

电子元件识别大全附图简体

1.0目的 制订本指南,规范公司的各层工作人员认识及辨别日常工作中常用的各类元件。 2.0范围 公司主要产品(电脑主机板)中的电子元件认识: 2.1工作中最常用的的电子元件有:电阻、电容、电感、晶体管(包括二极管、发光二极管及三极管)、晶体、晶振(振荡器)和集成电路(IC)。 2.2连接器元件主要有:插槽、插针、插座等。 2.3其它一些五金塑胶散件:散热片、胶针、跳线铁丝等。 4.0电子元件 4.1电阻 电阻用“R”表示,它的基本单位是欧姆(Ω) 1MΩ(兆欧)=1,000KΩ(千欧)=1,000,000Ω 公司常用的电阻有三种:色环电阻、排型电阻和片状电阻。 色环电阻的外观如图示: 图1五色环电阻图2四色环电阻 较大的两头叫金属帽,中间几道有颜色的圈叫色环,这些色环是用来表示该电阻的阻值和范围的,共有12种颜色,它们分别代表不同的数字(其中金色和银色表误差): 我们常用的色环电阻有四色环电阻(如图2)和五色环电阻(如图1): 1).四色环电阻(普通电阻):电阻外表上有四道色环: 这四道环,首先是要分出哪道是第一环、第二环、第三环和第四环:标在金属帽上的那道环叫第一环,表示电阻值的最高位,也表示读值的方向。如黄色表示最高位为四,紧挨第一环的叫第二环,表示电阻值的次高位,如紫色表示次高位为7;紧挨第2环的叫第3环,表示次高位后“0”的个数,如橙色表示后面有3个0;最后一环叫第4环,表示误差范围,一般仅用金色或银色表示,如为金色,则表示误差范围在±10%之间。 例如:某电阻色环颜色顺序为:黄-紫-橙-银,表示该电阻的阻值为:47,000Ω=47KΩ,误差范围:±10%之间。

芯片引脚图及引脚描述

555芯片引脚图及引脚描述 555的8脚是集成电路工作电压输入端,电压为5~18V,以UCC表示;从分压器上看出,上比较器A1的5脚接在R1和R2之间,所以5脚的电压固定在2UCC/3上;下比较器A2接在R2与R3之间,A2的同相输入端电位被固定在UCC/3上。 1脚为地。2脚为触发输入端;3脚为输出端,输出的电平状态受触发器控制,而触发器受上比较器6脚和下比较器2脚的控制。 当触发器接受上比较器A1从R脚输入的高电平时,触发器被置于复位状态,3脚输出低电平; 2脚和6脚是互补的,2脚只对低电平起作用,高电平对它不起作用,即电压小于1Ucc/3,此时3脚输出高电平。6脚为阈值端,只对高电平起作用,低电平对它不起作用,即输入电压大于2 Ucc/3,称高触发端,3脚输出低电平,但有一个先决条件,即2脚电位必须大于1Ucc/3时才有效。3脚在高电位接近电源电压Ucc,输出电流最大可打200mA。 4脚是复位端,当4脚电位小于0.4V时,不管2、6脚状态如何,输出端3脚都输出低电平。 5脚是控制端。 7脚称放电端,与3脚输出同步,输出电平一致,但7脚并不输出电流,所以3脚称为实高(或低)、7脚称为虚高。 555集成电路管脚,工作原理,特点及典型应用电路介绍. 1 555集成电路的框图及工作原理 555集成电路开始是作定时器应用的,所以叫做555定时器或555时基电路。但后来经过开发,它除了作定时延时控制外,还可用于调光、调温、调压、调速等多种控制及计量检测。此外,还可以组成脉冲振荡、单稳、双稳和脉冲调制电路,用于交流信号源、电源变换、频率变换、脉冲调制等。由于它工作可靠、使用方便、价格低廉,目前被广泛用于各种电子产品中,555集成电路内部有几十个元器件,有分压器、比较器、基本R-S触发器、放电管以及缓冲器等,电路比较复杂,是模拟电路和数字电路的混合体,如图1所示。 2. 555芯片管脚介绍 555集成电路是8脚封装,双列直插型,如图2(A)所示,按输入输出的排列可看成如图2(B)所示。其中6脚称阈值端(TH),是上比较器的输入;2脚称触发端(TR),是下比较器的输入;3脚是输出端(Vo),它有O和1两种状态,由输入端所加的电平决定;7脚是放电端(DIS),它是内部放电管的输出,有悬空和接地两种状态,也是由输入端的状态决定;4脚是复位端(MR),加上低电平时可使输出为低电平;5脚是控制电压端(Vc),可用它改变上下触发电平值;8脚是电源端,1脚是地端。 图2 555集成电路封装图 我们也可以把555电路等效成一个带放电开关的R-S触发器,如图3(A)所示,这个特殊的触发器有两个输入端:阈值端(TH)可看成是置零端R,要求高电平,触发端(TR)可看成是置位端S,要求低电平,有一个输出端Vo,Vo可等效成触发器的Q端,放电端(DIS)可看成是由内部放电开关控制的一个接点,由触发器的Q端控制:Q=1时DIS端接地,Q=0时DIS 端悬空。另外还有复位端MR,控制电压端Vc,电源端VDD和 地端GND。这个特殊的触发器有两个特点: (1)两个输入端的触发电平要求一高一低,置零端R即阈值端(TH)要求高电平,而置位端s 即触发端(TR)则要求低电乎; (2)两个输入端的触发电平使输出发生翻转的阈值电压值也不同,当V c端不接控制电压时,对TH(R)端来讲,>2/3VDD是高电平1,<2/3VDD是低电平0:而对TR(S)端来讲,>1/3VDD是

74LS系列芯片引脚图资料大全

74系列芯片引脚图资料大全 作者:佚名来源:本站原创点击数:57276 更新时间:2007年07月26日【字体:大中小】 为了方便大家我收集了下列74系列芯片的引脚图资料,如还有需要请上电子论坛https://www.360docs.net/doc/228562858.html,/b bs/ 反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373

反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│ Y =A+C )│四总线三态门74LS125 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND

器件管脚图及功能表

1 附录6 器件管脚图及功能表 74LS74双D 正沿触发器 74LS273八D 触发器 74LS377八D 触发器 74LS374八D 触发器 (三态输出) 74LS175双输出四D 触发器 74LS245 74LS161四位二进制同步计数器 74LS139双2:4译码器

2 74LS151 八选一选择器 74LS157 四个二选一选择器 74LS257 四个二选一选择器 (非反相三态输出) 注:i 等于d 2d 1d 0对应的十进制数 6116 2K*8 RAM 2716 2K*8 ROM 2732 4K*8 ROM 74LS138 3:8译码器 74LS148 8:3八进制优先编码器 74LS85 四位幅度比较器

附录9微指令寄存器的各字段微操作信号输出去向及功能 指令字段IR7~0 3

附录10 联机通讯指南 一、准备 1、准备一台PC机。 2、把TEC-2机在实验台上放好打开,将TEC-2的随机电源放在TEC-2的左侧,并确认电源开关处在关断的位置。 二、连接电源线 1、将TEC-2机电源的直流输出插头P8插在TEC-2机垂直板左侧的插座P8上; 将TEC-2机电源的直流输出插头P9插在TEC-2水平板左侧的插座P9上。 特别提醒注意:不要接反P8和P9,否则会烧机器或电源。 2、将TEC-2电源的电源线一端接电源的交流输入插孔,另一端接220V交流电源接线盒。 注意:TEC-2电源的交流电源线必须和计算机的电源线接在同一个有地线的电源接线盒上,以保证两设备共地,否则可能烧毁电源或机器。 三、连接TEC-2和PC 1、准备好随机提供的TEC-2和PC的串口通讯电缆。该电缆一端是9孔的插头,另一端是25孔的插头。 注意:TEC-2随机提供多条通讯电缆,请务必正确选用,以免错误连接造成联机失败。 2、把串口通讯电缆的9孔插头接在TEC-2机的上板左下角V70插座上,25孔插头插在计算机的串口上(COM1或COM2)。 如果PC上没有25针的串口或者25针的串口已被其它设备占用,TEC-2 随机提供一个9转25的转换器可以把25孔的插头转换成9孔的插头,接在9针的串口上。 四、TEC-2的初始设置 将TEC-2大板下方钮子开关S2~S0拨成100(向上为“1”,向下为“0”); FS1~FS4拨成1010(向上为“1”,向下为“0”); 将CONT/STEP钮子开关拨到CONT位置。 五、开机 1、打开计算机电源开关,使计算机正常启动。 2、打开TEC-2电源开关,TEC-2大板左上角一排指示灯亮。 六、加载通讯软件 1、用户可以根据联机PC的软件配置情况选择以下三种方法之一运行联机通讯软件。4

基本元器件的规范化图形

基本元器件的规范化图形。 1 2 3 4 5 6、继电器

7、二极管类 8、三极管类

9 10

5.4电源、地的命名要求、规范化图形及注意事项 1、电源、地的命名和规范化图形 建议电源使用图标,方便修理人员查找 其他地名称统一标识为实际的地的名称。 2、注意事项 如果需要使用符号,请注意使用的“SYMBOL”的“NAME”是否与设计中的网络名相同,如果不同,在生成网表时会产生两个网络名。例如通常我们放置的“GND”符号都是

而实际这个符号的“NAME”可能是“GND”也可能是“GND_POWER”、,而系统通常默认的都是“GND_POWER”。如果设计中没有将“GND”与“GND_POWER”连接在一起,网表中就会出现“GND”、“GND_POWER”两个网名,很显然不同的网名在EDA设计时是不能被连接在一起的。 对于有可焊接管脚的金属壳体器件,如:复位按钮、拨码开关、连接器等,在原理图中应该明确表示金属壳体是接哪一种地,如:工作地,还是接ESD防护及屏蔽地。 CMOS电路的不用的输入端不能悬空。 第二部分元器件原理图建库规范 1.目的。 对绘图者在CaptureV10.0平台上建立元器件原理图符合进行规范要求,增加电路图的可读性及确保库资源共享。 2.范围。 本标准规定了在CaptureV10.0平台上元器件原理图符号建库规范。 本标准适用于公司在CaptureV10.0平台上的元器件原理图符号建库和审核。 3.管理建议。 1、由绘图人员来负责Cadence元器件原理图模型的建立和该元器件资料的查询。 2、由EDA元器件库维护人员负责Cadence元器件原理图符号模型的审核。 3、由EDA元器件库维护人员负责将审核通过的元器件原理图符号模型分类加入到Cadence元器件原理图符号库中,如果元器件并不符合已有的库类别,将其加入其它类中。 4.CADENCE元器件建库步骤和要求。 4.1 CADENCE元器件原理图库器件模型的建造总体要求。 库模型根据实际情况权衡制作,遵循的一个原则是通俗易懂。以下提出几点约定须共同遵守: 1、只要元器件上有的管脚,图形库都应体现出来,不允许使用隐含管脚的方式(包括未使用的管脚)。 2、对IC器件,在空间允许的情况下尽量做成矩形或方形;对于管脚的安排,可根据功能模块和管脚号的顺序综合考虑管脚的排列,原则输入放置在左边,输出放置在右边,电源放置在上边,地放置在下面。 3、对连接器、插针等有2列的接插件,管脚号的命名顺序应该和板片中的命名保持一致。 4、对于CPLD/FPGA器件,做成矩形或方形;对于管脚的安排,原则上要求按照管脚顺序号进行排列。 5、对电阻、电容、电感、二极管、发光二极管、三极管、保险丝、过压保护器、复位开关、电池等分立器件及小封装器件,图形使用常见的简易图形表示。 4.2 CADENCE元器件建库步骤和具体要求。 4.2.1 N e w Part Proterties 的设置。 当需要添加一个新的元器件库的时候,首先我们会在capturev16.5中遇到下面这个New Part Properties窗口:

74系列芯片引脚图

74系列芯片引脚图、功能、名称、资料大全(含74LS、74HC等),特别推荐为了方便大家,我收集了下列74系列芯片的引脚图资料。 说明:本资料分3部分:(一)、TXT文档,(二)、图片,(三)、功能、名称、资料。 (一)、TXT文档 反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门 LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373

反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘

1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│ Y =A+C )│四总线三态门 74LS125 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND Vcc -G B1 B2 B3 B4 B8 B6 B7 B8 ┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位总线驱动器 74LS245 │20 19 18 17 16 15 14 13 12 11│ )│ DIR=1 A=>B │ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A └┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘ DIR A1 A2 A3 A4 A5 A6 A7 A8 GND

器件管脚图及功能表上课讲义

器件管脚图及功能表

收集于网络,如有侵权请联系管理员删除 附录6 器件管脚图及功能表 74LS74双D 正沿触发器 74LS273八D 触发器 74LS377八D 触发器 74LS374八D 触发器 (三态输出) 74LS175双输出四D 触发器 74LS245 74LS161四位二进制同步计数器 74LS139双2:4译码器

收集于网络,如有侵权请联系管理员删除 74LS151 八选一选择器 74LS157 四个二选一选择器 74LS257 四个二选一选择器 210 6116 2K*8 RAM 2716 2K*8 ROM 2732 4K*8 ROM 74LS138 3:8译码器 74LS148 8:3八进制优先编码器

附录9微指令寄存器的各字段微操作信号输出去向及功能 收集于网络,如有侵权请联系管理员删除

附录10 联机通讯指南 一、准备 1、准备一台PC机。 2、把TEC-2机在实验台上放好打开,将TEC-2的随机电源放在TEC-2的左侧,并确认电源开关处在关断的位置。 二、连接电源线 1、将TEC-2机电源的直流输出插头P8插在TEC-2机垂直板左侧的插座P8上; 将TEC-2机电源的直流输出插头P9插在TEC-2水平板左侧的插座P9上。 特别提醒注意:不要接反P8和P9,否则会烧机器或电源。 2、将TEC-2电源的电源线一端接电源的交流输入插孔,另一端接220V交流电源接线盒。 注意:TEC-2电源的交流电源线必须和计算机的电源线接在同一个有地线的电源接线盒上,以保证两设备共地,否则可能烧毁电源或机器。 三、连接TEC-2和PC 1、准备好随机提供的TEC-2和PC的串口通讯电缆。该电缆一端是9孔的插头,另一端是25孔的插头。 注意:TEC-2随机提供多条通讯电缆,请务必正确选用,以免错误连接造成联机失败。 收集于网络,如有侵权请联系管理员删除

74系列芯片引脚大全

74系列芯片引脚图资料大全(2008-04-24 17:37:47) 74系列芯片引脚图资料大全 反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373 反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│ Y =A+C )│四总线三态门74LS125 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND Vcc -G B1 B2 B3 B4 B8 B6 B7 B8 ┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐8位总线驱动器74LS245 │20 19 18 17 16 15 14 13 12 11│ )│DIR=1 A=>B │1 2 3 4 5 6 7 8 9 10│DIR=0 B=>A └┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘ DIR A1 A2 A3 A4 A5 A6 A7 A8 GND 页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器 正逻辑与门,与非门:

74ls138管脚图及功能真值表

74ls138引脚图 74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下: 当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为 低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低 电平译出。 利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反 相器还可级联扩展成32 线译码器。 若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器 用与非门组成的3线-8线译码器74LS138

3线-8线译码器74LS138的功能表 无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。 当附加控制门的输出为高电平(S=1)时,可由逻辑图写出

由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。 71LS138有三个附加的控制端、和。当、时,输出为高电平(S=1),译码器处于工作状态。否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。 带控制输入端的译码器又是一个完整的数据分配器。在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。这就不难理解为什么把叫做地址输入了。例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。 【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。 解:由图3.3.8可见,74LS138仅有3个地址输入端。如果想对4位二进制代码,只能利用一个附加控制端(当中的一个)作为第四个地址输入端。 取第(1)片74LS138的和作为它的第四个地址输入端(同时令),取第(2)片的作为它的第四个地址输入端(同时令),取两片的、、,并将第(1)片的和接至,将第(2)片的接至,如图3.3.9所示,于是得到两片74LS138的输出分别为

LM339引脚图与功能简介

LM2901/LM339/LM239/LM139的引脚和原理参数完全一样,只是使用温度不一样。 LM339引脚图与功能简介 LM339集成块内部装有四个独立的电压比较器,该电压比较器的特点是: 1)失调电压小,典型值为2mV; 2)电源电压范围宽,单电源为2-36V,双电源电压为±1V-±18V; 3)对比较信号源的内阻限制较宽; 4)共模范围很大,为0~(Ucc-1.5V)Vo; 5)差动输入电压范围较大,大到可以等于电源电压; 6)输出端电位可灵活方便地选用。 LM339集成块采用C-14型封装,图1为外型及管脚排列图。由于LM339使用灵活,应用广泛,所以世界上各大IC生产厂、公司竟相推出自己的四比较器,如IR2339、ANI339、SF339等,它们的参数基本一致,可互换使用。 LM339类似于增益不可调的运算放大器。每个比较器有两个输入端和一个输出端。两个输入端一个称为同相输入端,用“+”表示,另一个称为反相输入端,用“-”表示。用作比较两个电压时,任意一个输入端加一个固定电压做参考电压(也称为门限电平,它可选择LM339输入共模范围的任何一点),另一端加一个待比较的信号电压。当“+”端电压高于“-”端时,输出管截止,相当于输出端开路。当“-”端电压高于“+”端时,输出管饱和,相当于输出端接低电位。两个输入端电压差别大于10mV就能确保输出能从一种状态可靠地转换到另一种状态,因此,把LM339用在弱信号检测等场合是比较理想的。LM339的输出端相当于一只不接集电极电阻的晶体三极管,在使用时输出端到正电源一般须接一只电阻(称为上拉电阻,选3-15K)。选不同阻值的上拉电阻会影响输出端高电位的值。因为当输出晶体三极管截止时,它的集电极电压基本上取决于上拉电阻与负载的值。另外,各比较器的输出端允许连接在一起使用。

74系列芯片-名字对照表

74LS系列: 74LS00 TTL 2输入端四与非门 74LS01 TTL 集电极开路2输入端四与非门 74LS02 TTL 2输入端四或非门 74LS04 TTL 六反相器 74LS08 TTL 2输入端四与门 74LS10 TTL 3输入端3与非门 74LS112 TTL 带预置清除负触发双J-K触发器 74LS122 TTL 可再触发单稳态多谐振荡器 74LS138 TTL 3-8线译码器/复工器 74LS14 TTL 六反相施密特触发器 74LS151 TTL 8选1数据选择器 74LS153 TTL 双4选1数据选择器 74LS154 TTL 4线—16线译码器 74LS160 TTL 可预置BCD异步清除计数器 74LS161 TTL 可予制四位二进制异步清除计数器74LS166 TTL 八位并入/串出移位寄存器 74LS192 TTL 可预置BCD双时钟可逆计数器 74LS193 TTL 可预置四位二进制双时钟可逆计数器74LS194 TTL 四位双向通用移位寄存器 74LS20 TTL 4输入端双与非门 74LS21 TTL 4输入端双与门 74LS273 TTL 带公共时钟复位八D触发器 74LS30 TTL 8输入端与非门 74LS32 TTL 2输入端四或门 74LS42 TTL BCD—十进制代码译码器 74LS47 TTL BCD—7段高有效译码/驱动器 74LS48 TTL BCD—7段译码器/内部上拉输出驱动74LS51 TTL 2-3/2-2输入端双与或非门 74LS74 TTL 带置位复位正触发双D触发器 74LS76 TTL 带预置清除双J-K触发器 74LS85 TTL 四位数字比较器 74LS86 TTL 2输入端四异或门 74LS90 TTL 可二/五分频十进制计数器

及其他系列芯片引脚图大全

一:分类 74ls00 2输入四与非门 74ls01 2输入四与非门 (oc) 74ls02 2输入四或非门 74ls03 2输入四与非门 (oc) 74ls04 六倒相器 74ls05 六倒相器(oc) 74ls06 六高压输出反相缓冲器/驱动器(oc,30v) 74ls07 六高压输出缓冲器/驱动器(oc,30v) 74ls08 2输入四与门 74ls09 2输入四与门(oc) 74ls10 3输入三与非门 74ls11 3输入三与门 74ls12 3输入三与非门 (oc) 74ls13 4输入双与非门 (斯密特触发) 74ls14 六倒相器(斯密特触发) 74ls15 3输入三与门 (oc) 74ls16 六高压输出反相缓冲器/驱动器(oc,15v) 74ls17 六高压输出缓冲器/驱动器(oc,15v) 74ls18 4输入双与非门 (斯密特触发) 74ls19 六倒相器(斯密特触发) 74ls20 4输入双与非门 74ls21 4输入双与门 74ls22 4输入双与非门(oc) 74ls23 双可扩展的输入或非门 74ls24 2输入四与非门(斯密特触发)

74ls25 4输入双或非门(有选通) 74ls26 2输入四高电平接口与非缓冲器(oc,15v) 74ls27 3输入三或非门 74ls28 2输入四或非缓冲器 74ls30 8输入与非门 74ls31 延迟电路 74ls32 2输入四或门 74ls33 2输入四或非缓冲器(集电极开路输出) 74ls34 六缓冲器 74ls35 六缓冲器(oc) 74ls36 2输入四或非门(有选通) 74ls37 2输入四与非缓冲器 74ls38 2输入四或非缓冲器(集电极开路输出74ls39 2输入四或非缓 冲器(集电极开路输出) 7 4ls40 4输入双与非缓冲器 7 4ls41 bcd-十进制计数器 7 4ls42 4线-10线译码器(bcd输入) 7 4ls43 4线-10线译码器(余3码输 入) 7 4ls44 4线-10线译码器(余3葛莱 码输入) 7 4ls45 bcd-十进制译码器/驱动器 7 4ls46 bcd-七段译码器/驱动器

常用电子器件管脚排列

常用电子器件管脚排列图附录1 逻辑符号对照示例 附录表1.1 逻辑非、逻辑极性符号对照示例(以反相器为例) 逻辑符号逻辑功能 逻辑非 A Y 逻辑极性 附录表1.2 几种常用逻辑门的逻辑符号比较示例 标准非门与门与非门或门或非门异或门国标 GB4728.12 ---85(IEC 617—12) 美国一些公 司的标准 附录表1.3 逻辑符号、框图、管脚排列比较示列(以74HC390为例) 项目逻辑符号框图管脚排列 图形 功能功能标注清晰,但烦 琐。用于原理图中 简单易用,但功能有时提示不全。多用 于原理电路图中 管脚位置确切,但功能可能提示 不全。用于装配电路图、接线图

附录2 集成电路 1. 集成电路命名方法 集成电路命名方法见附录表2.1 附录表 2.1 国产半导体集成电路型号命名法(GB3430-82) 第零部分 第一部分 第二部分 第三部分 第四部分 用字母表示器件符合国家标准 用字母表示器件 的类型 用阿拉伯数字和用字母表示器件的系列品 种代号 用字母表示器件的工作温度范围 用字母表示器件的 封装形式 符号 意义 符号 意义 符号 意义 符号 意义 C 中国制造 T H E C F D W J B M μ TTL HTL ECL CMOS 线性放大器 音响、电视电路 稳压器 接口电路 非线性电路 存储器 微型电路 C E R M 0 ~70℃ -48 ~75℃ -55 ~85℃ -55 ~125℃ W B F D P J K T 陶瓷封装 塑料封装 全密封扁 平 陶瓷直插 塑料直插 黑陶瓷扁 平 金属菱形 金属圆形 2.集成电路介绍 集成电路IC 是封在单个封装件中的一组互连电路。装在陶瓷衬底上的分立元件或电路有时还和单个集成电路连在一起,称为混合集成电路。把全部元件和电路成型在单片晶体硅材料上称单片集成电路。单片集成电路现在已成为最普及的集成电路形式,它可以封装成各种类型的固态器件,也可以封装成特殊的集成电路。 通用集成电路分为模拟(线性)和数字两大类。模拟电路根据输入的各种电平,在输出端产生各种相应的电平;而数字电路是开关器件,以规定的电平响应导通和截止。有时候集成电路标有LM (线性类型) 或DM(数字类型)符号。 集成电路都有二或三个电源接线端:用CC V 、DD V 、SS V 、V +、V -或GND 来表示。这是一般应用所需要的。 双列直插式是集成电路最通用的封装形式。 其引脚标记有半圆形豁口、标志线、标志圆点 等,一般由半圆形豁口就可以确定各引脚的位置。 双列直插式的引脚排列图如附录图2.1所示。 3.使用TFL 集成电路与CMOS 集成电路的注意事项 (1) 使用TYL 集成电路注意事项 附录图 2.1双列直插式集成电路的引脚排列

74系列功能表

7400 TTL 2输入端四与非门 7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门 7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器 7405 TTL 集电极开路六反相器 7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压驱动器7408 TTL 2输入端四与门 7409 TTL 集电极开路2输入端四与门 7410 TTL 3输入端3与非门 74107 TTL 带清除主从双J-K触发器 74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门 74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门 74121 TTL 单稳态多谐振荡器 74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门 74136 TTL 四异或门 74138 TTL 3-8线译码器/复工器 74139 TTL 双2-4线译码器/复工器 7414 TTL 六反相施密特触发器 74145 TTL BCD—十进制译码/驱动器 7415 TTL 开路输出3输入端三与门 74150 TTL 16选1数据选择/多路开关 74151 TTL 8选1数据选择器 74153 TTL 双4选1数据选择器 74154 TTL 4线—16线译码器 74155 TTL 图腾柱输出译码器/分配器 74156 TTL 开路输出译码器/分配器 74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器

器件管脚图及功能表

附录6 器件管脚图及功能表 74LS74双D 正沿触发器 74LS273八D 触发器 74LS377八D 触发器 74LS374八D 触发器 (三态输出) 74LS175双输出四D 触发器 74LS245 74LS161四位二进制同步计数器 74LS139双2:4译码器

74LS151 八选一选择器 74LS157 四个二选一选择器 74LS257 四个二选一选择器 (非反相三态输出) 注:i等于d2d1d0对应的十进制数 6116 2K*8 RAM2716 2K*8 ROM2732 4K*8 ROM 74LS138 3:8译码器 74LS148 8:3八进制优先编码器 74LS85 四位幅度比较器

附录9微指令寄存器的各字段微操作信号输出去向及功能 指令字段IR7~0

附录10 联机通讯指南 一、准备 1、准备一台PC机。 2、把TEC-2机在实验台上放好打开,将TEC-2的随机电源放在TEC-2的左侧,并确认电源开关处在关断的位置。 二、连接电源线 1、将TEC-2机电源的直流输出插头P8插在TEC-2机垂直板左侧的插座P8上; 将TEC-2机电源的直流输出插头P9插在TEC-2水平板左侧的插座P9上。 特别提醒注意:不要接反P8和P9,否则会烧机器或电源。 2、将TEC-2电源的电源线一端接电源的交流输入插孔,另一端接220V交流电源接线盒。 注意:TEC-2电源的交流电源线必须和计算机的电源线接在同一个有地线的电源接线盒上,以保证两设备共地,否则可能烧毁电源或机器。 三、连接TEC-2和PC 1、准备好随机提供的TEC-2和PC的串口通讯电缆。该电缆一端是9孔的插头,另一端是25孔的插头。 注意:TEC-2随机提供多条通讯电缆,请务必正确选用,以免错误连接造成联机失败。 2、把串口通讯电缆的9孔插头接在TEC-2机的上板左下角V70插座上,25孔插头插在计算机的串口上(COM1或COM2)。 如果PC上没有25针的串口或者25针的串口已被其它设备占用,TEC-2 随机提供一个9转25的转换器可以把25孔的插头转换成9孔的插头,接在9针的串口上。 四、TEC-2的初始设置 将TEC-2大板下方钮子开关S2~S0拨成100(向上为“1”,向下为“0”); FS1~FS4拨成1010(向上为“1”,向下为“0”); 将CONT/STEP钮子开关拨到CONT位置。 五、开机 1、打开计算机电源开关,使计算机正常启动。 2、打开TEC-2电源开关,TEC-2大板左上角一排指示灯亮。 六、加载通讯软件 1、用户可以根据联机PC的软件配置情况选择以下三种方法之一运行联机通讯软件。

74ls系列主要芯片引脚及参数.doc

<74LS00引脚图> 74l s00 是常用的2输入四与非门集成电路,他的作用很简单顾名思义就是实现一个与非门。 Vcc 4B 4A 4Y 3B 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ __ │14 13 12 11 10 9 8│ Y = AB )│ 2输入四正与非门 74LS00 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1B 1Y 2A 2B 2Y GND 74LS00真值表: A=1 B=1 Y=0 A=0 B=1 Y=1 A=1 B=0 Y=1 A=0 B=0 Y=1

74HC138基本功能74LS138 为3 线-8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,其74LS138工作原理如下: 当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。 74LS138的作用: 利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器 用与非门组成的3线-8线译码器74LS138

图74ls138译码器内部电路 3线-8线译码器74LS138的功能表 备注:这里的输入端的三个A0~1有的原理图中也用A B C表示(如74H138.pdf中所示,试用于普中科技的HC-6800 V2.2单片机开发板)。<74ls138功能表> 74LS138逻辑图

无论从逻辑图还是功能表我们都可以看到74LS138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。 当附加控制门的输出为高电平(S=1)时,可由逻辑图写出 74ls138逻辑图 由上式可以看出,在同一个时间又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。 71LS138有三个附加的控制端、和。当、时,输出为高电平(S=1),译码器处于工作状态。否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。 带控制输入端的译码器又是一个完整的数据分配器。在图3.3.8电路中如果把作为“数据”输入端(在同一个时间),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。这就不难理解为什么把叫做地址输入了。例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。 例2.74LS138 3-8译码器的各输入端的连接情况及第六脚()输入信号A的波形如下图所示。试画出八个输出管脚的波形。

74LS74内部结构-引脚图-管脚-逻辑图(双D触发器)、原理图和真值表以及波形图分析

74LS74内部结构引脚图管脚逻辑图(双D触发器)、原理图和真值表以及波形图分析下面介绍一下74ls74,74ls74内部结构,74ls74引脚图,74ls74管脚图,74ls74逻辑图。 在TTL电路中,比较典型的d触发器电路有74ls74。74ls74是一个边沿触发器数字电路器件,每个器件中包含两个相同的、相互独立的边沿触发d触发器电路。 (图点击,或下载后可放大)

(图点击,或下载后可放大) ---------------------- 原理图和真值表以及波形图分析 边沿D 触发器: 负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。边沿D触发器也称为维持-阻塞边沿D触发器。 电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

工作原理: SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。当SD =0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。我们设它们均已加入了高电平,不影响电路的工作。工作过程如下: 1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6 =Q5=D。 2.当CP由0变1时触发器翻转。这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。Q3=Q5=D,Q4=Q6=D。由基本RS触发器的逻辑功能可知,Q =D。 3.触发器翻转后,在CP=1时输入信号被封锁。这是因为G3和G4打开后,它们的输出Q 3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。Q4为0时,