74hc595使用方法

74HC595使用心得总结

1、概述:

74HC595是一款漏极开路串行输入转并行输出的CMOS移位寄存器,常用于驱动数码管和扩展单片机IO口。可多个芯片级联。

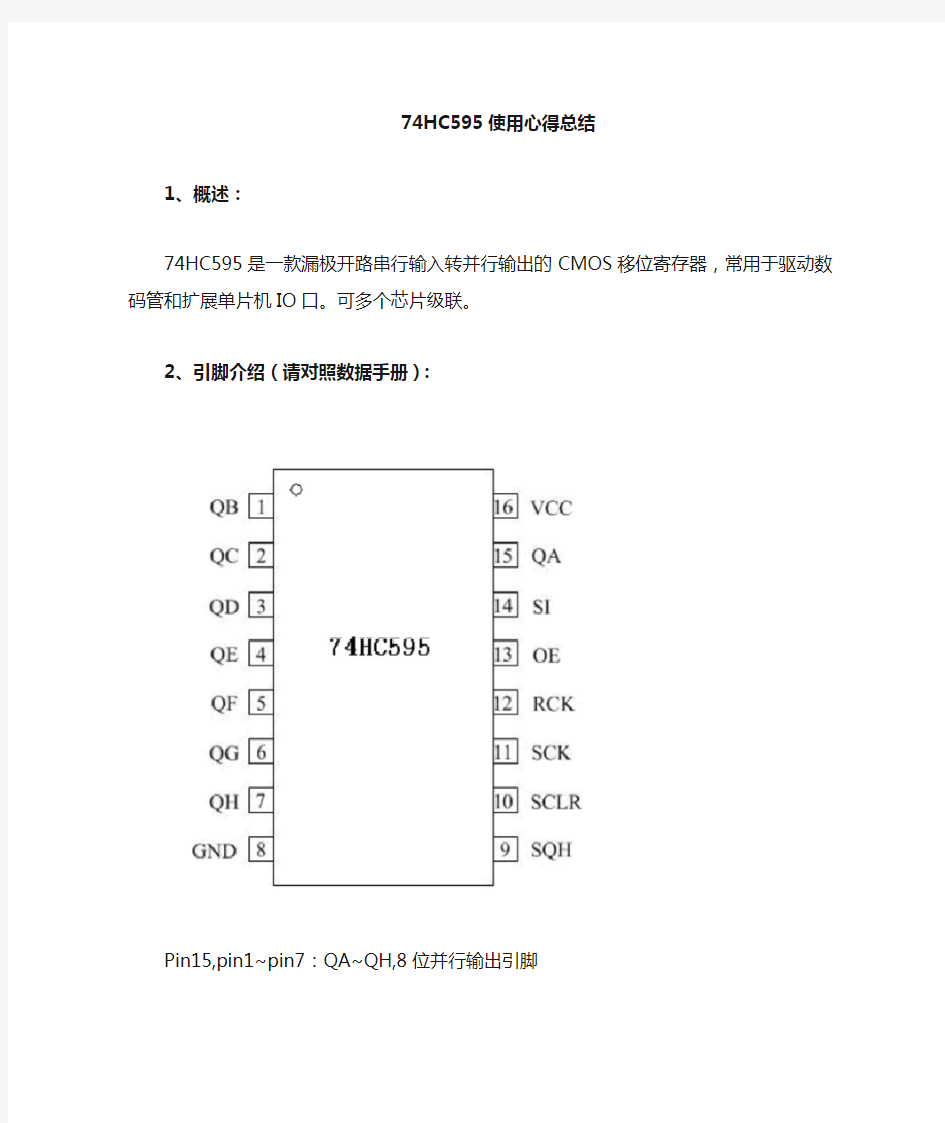

2、引脚介绍(请对照数据手册):

Pin15,pin1~pin7:QA~QH,8位并行输出引脚

Pin8:GND,接地

Pin9:SQH,串行数据输出管脚,常用于多个595芯片级联。

Pin10:SCLR,移位寄存器清零(给一个低电平即可实现,不用该功能可直接接到VCC)

Pin11:SCK,数据输入时钟线,上升沿时实现移位寄存器数据移位,下降沿时实现移位寄存器状态保持

Pin12:RCK,存储寄存器锁存时钟线,上升沿时移位寄存器的数据进入存储寄存器,下降沿时存储寄存器数据保持

Pin13:OE,输出使能,低电平有效,可直接接到GND。

Pin14:SI,串行数据输入接口,按位输入,低字节在前。

Pin16:VCC,工作电源,2~6V。

3、使用方法介绍:

单片机将需要输出的数据,按位发送到595芯片的SI(pin14)引脚上,如果收到的是高电平,则SI=1,反之则SI=0,接收到一位数据后将SCK(pin11)引脚拉低,延时几十us后再拉高,即给SCK一个上升沿,让595芯片把接收到的数据通过移位寄存器将数据向后移,如此循环8次(一个字节8位),就接收完一个字节的数据了。接下来需要接收到的数据送到存储寄存器中通过QA~QH 并行输出,跟SCK一样,给RCK一个上升沿即可实现。

按照上面的步骤即可通过74HC595实现数据的串行数据并行输出。

4、STM32程序实例:

/*SER----PA12(串行数据输入)****

**SRCLK----PA14(操作移位寄存器,上升沿移位,下降沿保持)***

**RCLK----PA13(操作存储寄存器,上升沿数据移入存储寄存器,下降沿数据保持)**/

//以下是74HC595相关引脚的宏定义

#define SER_SET() GPIOA->BSRR = BIT12//SI HIGH

#define SER_CLR() GPIOA->BRR = BIT12//SI LOW

#define RCLK_SET() GPIOA->BSRR = BIT13//RCLK HIGH

#define RCLK_CLR() GPIOA->BRR = BIT13//RCLK LOW

#define SRCLK_SET() GPIOA->BSRR = BIT14//SRCLK HIGH

#define SRCLK_CLR() GPIOA->BRR = BIT14//SRCLK LOW

//向芯片写入一个字节的数据

void HC595_WriteByte(unsigned char data)

{

unsigned char i;

for(i = 0;i < 8;i++)

{

if((data>>i) & 0x01)

SER_SET();

else

SER_CLR();

//给SRCLK一个上升沿,实现数据位的移位

SRCLK_CLR();

Stm32_SystickDly_us(30);

SRCLK_SET();

}

//给RCLK一个上升沿,实现移位寄存器的数据移向存储寄存器RCLK_CLR();

Stm32_SystickDly_us(30);

RCLK_SET();

}

74HC595中文芯片手册

74HC595 8位移位寄存器与输出锁存器 功能描述 这种高速移位寄存器采用先进的硅栅CMOS技术。该装置具有高的抗干扰性和标准CMOS集成电路的低功率消耗,以及用于驱动15个LS-TTL负载的能力。 此装置包含馈送一个8位D型存储寄存器的8位串行入,并行出移位寄存器。存储寄存器具有8 TRI-STATE e输出。提供了用于两个移位寄存器和存储寄存器独立的时钟。 移位寄存器有直接首要明确,串行输入和串行输出(标准)引脚级联。两个移位寄存器和存储寄存器的使用正边沿触发的时钟。如果两个时钟被连接在一起时,移位寄存器的状态 将总是提前存储寄存器的一个时钟脉冲。 该54HC/74HC逻辑系列就是速度,功能和引脚输出与标准54LS/74LS逻辑系列兼容。所有输入免受损害,由于静电放电由内部二极管钳位到VCC和地面。 产品特点 1低静态电流:80 mA最大值(74HC系列) 2低输入电流为1mA最大 38位串行输入,并行出移位寄存器以存储 4宽工作电压范围:2V ± 6V 5级联 6移位寄存器直接明确 7保证移频率:DC至30兆赫

TL/F/5342-1 Top View Order Number MM54HC5S5 or MM74HC595 DuaHn-Line Package RCK SCK SCLR G Function X X X H Q A thruQH = TRI-STATE X X L L Shift Register cleared Q H -O X T H L Shift Register clocked C)N = Qnd ,Qo = SER T X H L Con tents of Shift Register transferred to output latches Operating Conditions Supply Voltage (V QC ) -0.5 to +7.0V DC Input Voltage (V IM ) -1.5 toV C c+15V DC OutpiX Voltage (V OUT ) -0.5 toVcc+0.5V Clamp Diode Current (I IK . I(X ) ±20 mA DC Output Current, per pin (lour) ±35 mA DC Vcc or GND Current, per pin (Icc) ±70 mA Storage Temperature Range (T STG ) -65"Cto+15(rC Power Dissipation (P Q ) (Note 3) 600 mW S.O. Package only 500 mW Lead Temp. (TO (Sobering 10 seconds) 2?TC Min Max Units Supply Voltage (Vcc) 2 6 V DC Input or Outpu* Voltage 0 Vcc V (Vw. VOUT ) Operating Temp. Range (T A ) MM74HC -40 +85 ?c MM54HC -55 + 125 ?c Input Rise or Fall Times VOC-20V 1000 ns V QC -4.5V 500 ns Vcc-6.0V 400 ns Absolute Maximum Ratings (Notes 1&2) If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications ?

实用文档之74HC595完整中文资料

实用文档之"74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。" 74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。 三态。特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出; 标准中等规模集成电路应用串行到并行的数据转换 Remo te control holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。 595是具有8位移位寄存器和一个存储器,三态输出功能。移位寄存器和存储器是分别的时钟。数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz)Vcc=电源电压引脚说明符号引脚描述 内部结构 结合引脚说明就能很快理解 595的工作情况 引脚功能表: 真值表:

串行输595是串入并出带有锁存功能移位寄存器,它的使用方法很简单,如下面的真值表,在正常使用时SCLR为高电平, G为低电平。从SER每输入一位数据,串行输入时钟SCK上升沿有效一次,直到八位数据输入完毕,输出时钟上升沿有效一次,此时,输入的数据就被送到了输出端。入时钟SCK上升沿有效一次,直到八位数据输入完毕,输出时钟上升沿有效一次,此时,输入的数据就被送到了输出端。 其实,看了这么多595的资料,觉得没什么难的,关键是看懂其时序图,说到底,就是下面三步(引用): 第一步:目的:将要准备输入的位数据移入74HC595数据输入端上。 方法:送位数据到 P1.0。 第二步:目的:将位数据逐位移入74HC595,即数据串入 方法:P1.2产生一上升沿,将P1.0上的数据移入74HC595中.从低到高。 第三步:目的:并行输出数据。即数据并出 方法:P1.1产生一上升沿,将由P1.0上已移入数据寄存器中的数据 送入到输出锁存器。 说明:从上可分析:从P1.2产生一上升沿(移入数据)和P1.1产生一上升沿 (输出数据)是二个独立过程,实际应用时互不干扰。即可输出数据的 同时移入数据。 而具体编程方法为 如:R0中存放3FH,LED数码管显示“0” ;*****接口定义: DS_595 EQU P1.0 ;串行数据输入(595-14) CH_595 EQU P1.2 ;移位时钟脉冲(595-11) CT_595 EQU P1.1 ;输出锁存器控制脉冲(595-12) ;*****将移位寄存器内的数据锁存到输出寄存器并显示OUT_595: CALL WR_595 ;调用移位寄存器接收一个字节数据子程序

74HC595完整中文资料

74HC595芯片是一种串入并出的芯片,在电子显示屏制 作当中有广泛的应用。 74HC595是8位串行输入/输出或者并行输出移位寄存器,具有咼阻、关、断状态。 三态。特点8位串行输入8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除100MHz的移位频率输出能力并行输出,总线驱动串行输出; 标准中等规模集成电路应用串行到并行的数据转换Remote c ontrol holding register. 描述595是告诉的硅结构的CMO器件, 兼容低电压TTL电路,遵守JEDEC标准。 595是具有8位移位寄存器和一个存储器,三态输出功能。移位寄存器和存储器是分别的时钟。数据在SCHcp勺上升沿输入,在S Tcp 的上升沿进入的存储寄存器中去。如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。移位寄存器有一个串行移 位输入(Ds),和一个串行输出(Q7 ),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能0E时(为低电平),存储寄存器的数据输出到总线。 CPD决定动态的能耗,PD= CPD< VCC< f1 + 刀(CL X VCC2< f0) F 1=输入频率,。1=输出电容f0 =输出频率(MHZ Vcc=电源电压引脚说明符号引脚描述

内部结构 结合引脚说明就能很快理解595的工作情况功能表: 真值表: 74595的数据端:

QA--QH:八位并行输出端,可以直接控制数码管的8个段。 QH':级联输出端。我将它接下一个595的SI端。 SI:串行数据输入端。 74595的控制端说明: /SRCLR(10脚):低点平时将移位寄存器的数据清零。通常我将它接Vcc。 SRCK(11脚):上升沿时数据寄存器的数据移位。 QA-->QB-->QC-->…-->QH ;下降沿移位寄存器数据不变。(脉冲宽度:5V时,大于几十纳秒就行了。我通常都选微秒级) RCK(12脚):上升沿时移位寄存器的数据进入数据存储寄存器,下降沿时存储寄存器数据不变。(通常我将RCK置为低电平,)当移位结束后,在RCK端产生一个正脉冲(5V时,大于几十纳秒就行了。我通常都选微秒级),更新显示数据。 /G(13脚):高电平时禁止输出(高阻态)。如果单片机的引脚不紧张,用一个引脚控制它,可以方便地产生闪烁和熄灭效果。比通过数据端移位控制要省时省力。 注: 1)74164和74595功能相仿,都是8位串行输入转并行输出移位寄存器。74164的驱动电流(25mA)比74595(35mA)的要小,14脚封装,体积

74HC595D中文资料_数据手册_参数

74HC595; 74HCT595 8-bit serial-in, serial or parallel-out shift register with output latches; 3-state Rev. 6 — 12 December 2011Product data sheet 1. General description The 74HC595; 74HCT595 are high-speed Si-gate CMOS devices and are pin compatible with Low-power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard No.7A. The 74HC595; 74HCT595 are 8-stage serial shift registers with a storage register and 3-state outputs. The registers have separate clocks. Data is shifted on the positive-going transitions of the shift register clock input (SHCP). The data in each register is transferred to the storage register on a positive-going transition of the storage register clock input (STCP). If both clocks are connected together, the shift register will always be one clock pulse ahead of the storage register. The shift register has a serial input (DS) and a serial standard output (Q7S) for cascading. It is also provided with asynchronous reset (active LOW) for all 8 shift register stages. The storage register has 8 parallel 3-state bus driver outputs. Data in the storage register appears at the output whenever the output enable input (OE) is LOW. 2. Features and benefits ?8-bit serial input ?8-bit serial or parallel output ?Storage register with 3-state outputs ?Shift register with direct clear ?100MHz (typical) shift out frequency ?ESD protection: ◆HBM JESD22-A114F exceeds2000V ◆MM JESD22-A115-A exceeds200V ?Multiple package options ?Specified from -40?C to+85?C and from -40?C to+125?C 3. Applications ?Serial-to-parallel data conversion ?Remote control holding register

74ls595芯片中文资料

74595外形图 ________ QB--|1 16|--Vcc QC--|2 15|--QA QD--|3 14|--SI QE--|4 13|--/G QF--|5 12|--RCK QG--|6 11|--SCK QH--|7 10|--/SCLR GND-|8 9|--QH' |________| 74595的数据端: QA--QH: 八位并行输出端,可以直接控制数码管的8个段。 QH': 级联输出端。我将它接下一个595的SI端。 SI: 串行数据输入端。 74595的控制端说明: /SCLR(10脚): 低点平时将移位寄存器的数据清零。通常我将它接Vcc。 SCK(11脚):上升沿时数据寄存器的数据移位。QA-->QB-->QC-->...-->QH;下降沿移位寄存器数据不变。(脉冲宽度:5V时,大于几十纳秒就行了。我通常都选微秒级) RCK(12脚):上升沿时移位寄存器的数据进入数据存储寄存器,下降沿时存储寄存器数据不变。通常我将RCK置为低点平,当移位结束后,在RCK端产生一个正脉冲(5V时,大于几十纳秒就行了。我通常都选微秒级),更新显示数据。 /G(13脚): 高电平时禁止输出(高阻态)。如果单片机的引脚不紧张,用一个引脚控制它,可以方便地产生闪烁和熄灭效果。比通过数据端移位控制要省时省力。 注:74164和74595功能相仿,都是8位串行输入转并行输出移位寄存器。74164的驱动电流(25mA)比74595(35mA)的要小,14脚封装,体积也小一些。 74595的主要优点是具有数据存储寄存器,在移位的过程中,输出端的数据可以保持不变。这在串行速度慢的场合很有用处,数码管没有闪烁感。 与164只有数据清零端相比,595还多有输出端时能/禁止控制端,可以使输出为高阻态。 另外,据网上报价,贴片164每只1元钱,贴片595 0.8元/只。

74hc595中文资料

概述: 74HC595 是一款漏极开路输出的CMOS 移位寄存器,输出端口为可控的三态输出端,亦能串行输出控制下一级进行级联芯片。 特点: 高速移位时钟频率Fmax>25MHz 标准串行(SPI)接口 CMOS 串行输出,可用于多个设备的级联 低功耗:TA =25℃时,Icc=4μA(MAX) 引脚功能表: 管脚编号管脚名管脚定义功能 1、2、3、4、5、6、 QA—QH 三态输出管脚 7、15 8 GND 电源地 9 SQH 串行数据输出管脚 10 SCLR 移位寄存器清零端 11 SCK 数据输入时钟线 12 RCK 输出存储器锁存时钟线 13 OE 输出使能 14 SI 数据线 15 VCC 电源端

图1 74HC595引脚图

图2 74HC595逻辑图 真值表: 输入管脚 输出管脚SI SCK SCLR RCK OE X X X X H QA—QH 输出高阻 X X X X L QA—QH 输出有效值 X X L X X 移位寄存器清零 L 上沿H X X 移位寄存器存储L H 上沿H X X 移位寄存器存储H X 下沿H X X 移位寄存器状态保持 X X X 上沿X 输出存储器锁存移位寄存器中的状态值 X X X 下沿X 输出存储器状态保持 Absolute Maximum Ratings绝对最大额定值 参数数值 Supply Voltage电源电压(VCC)?0.5 to +7.0V DC Input Voltage 直流输入电压(VIN)?1.5 to VCC +1.5V DC Output Voltage 直流输出电压(VOUT)?0.5 to VCC +0.5V Clamp Diode Current 钳位二极管电流(IIK, IOK)±20mA DC Output Current直流输出电流,每个引脚(输出)±35mA DC VCC or GND Current,per pin (ICC)±70mA Storage Temperature Range 储存温度范围(TSTG)?65℃ to +150℃Power Dissipation 功耗(PD) (Note 3)600mW S.O. Package only500mW Lead Temperature (TL) (Soldering 10 seconds)260℃Recommended Operating Conditions建议操作条件 参数最小最大单位Supply Voltage电源电压(VCC)26v DC Input or Output Voltage(VIN, VOUT)输入输出电压0VCC V Operating Temperature Range工作温度范围(TA)?40+85℃Input Rise or Fall Times 输入上升或下降时间 (tr,tf) VCC = 2.0V-1000ns VCC = 4.5V-500ns

74LS595较好中文资料

74LS595,74HC595引脚图,管脚图 ________ QB--|1 16|--Vcc QC--|2 15|--QA QD--|3 14|--SI QE--|4 13|--/G QF--|5 12|--RCK QG--|6 11|--SCK QH--|7 10|--/SCLR GND- |8 9|--QH' |________| 74595的数据端: QA--QH: 八位并行输出端,可以直接控制数码管的8个段。QH': 级联输出端。我将它接下一个595的SI端。 SI: 串行数据输入端。

74595的控制端说明: /SCLR(10脚): 低电平时将移位寄存器的数据清零。通常我将它接Vcc。 SCK(11脚):上升沿时移位寄存器的数据移位。 QA-->QB-->QC-->...-->QH;下降沿移位寄存器数据不变。(脉冲宽度:5V时,大于几十纳秒就行了。我通常都选微秒级) RCK(12脚):上升沿时移位寄存器的数据进入数据存储寄存器,下降沿时存储寄存器数据不变。通常我将RCK置为低电平,当移位结束后,在RCK端产生一个正脉冲(5V时,大于几十纳秒就行了。我通常都选微秒级),更新显示数据。 /G(13脚): 高电平时禁止输出(高阻态)。如果单片机的引脚不紧张,用一个引脚控制它,可以方便地产生闪烁和熄灭效果。比通过数据端移位控制要省时省力。 注:74164和74595功能相仿,都是8位串行输入转并行输出移位寄存器。74164的驱动电流(25mA)比74595(35mA)的要小,14脚封装,体积也小一些。

74595的主要优点是具有数据存储寄存器,在移位的过程中,输出端的数据可以保持不变。这在串行速度慢的场合很有用处,数码管没有闪烁感。 与164只有数据清零端相比,595还多有输出端时能/禁止控制端,可以使输出为高阻态。

M74HC595中文资料

M54HC595M74HC595 April 1993 8BIT SHIFT REGISTER WITH OUTPUT LATCHES (3STATE) B1R (Plastic Package)ORDER CODES : M54HC595F1R M74HC595M1R M74HC595B1R M74HC595C1R F1R (Ceramic Package) M1R (Micro Package)C1R (Chip Carrier) PIN CONNECTIONS (top view) NC = No Internal Connecti o n .HIGH SPEED f MAX =55MHz (TYP.)AT V CC =5V .LOW POWER DISSIPATION I CC =4μA (MAX.)AT T A =25°C .HIGH NOISE IMMUNITY V NIH =V NIL =28%V CC (MIN.).OUTPUT DRIVE CAPABILITY 15LSTTL LOADS FOR QA TO QH 10LSTTL LOADS FOR QH’ .SYMMETRICAL OUTPUT IMPEDANCE |I OH |=I OL =6mA (MIN.)FOR QA TO QH |I OH |=I OL =4mA (MIN.)FOR QH’ .BALANCED PROPAGATION DELAYS t PLH =t PHL .WIDE OPERATING VOLTAGE RANGE V CC (OPR)=2V TO 6V . PIN AND FUNCTION COMPATIBLE WITH LSTTL 54/74LS595 DESCRIPTION The M54/74HC595is a high speed CMOS 8-BIT SHIFT REGISTERS/OUTPUT LATCHES (3-STATE)fabricated in silicon C 2 MOS technology.It has the same high speed performance of LSTTL combined with true CMOS low power consumption.This device contains an 8-bit serial-in,parallel -out shift register that feeds an 8-bit D-type storage reg-ister.The storage register has 83-STATE outputs.Separate clocks are provided for both the shift reg-ister and the storage register. The shift register has a direct-overriding clear,serial input,and serial output (standard)pins for cascad-ing.Both the shift register and storage register use positive-edge triggered clocks.If both clocks are connected together,the shift register state will al-ways be one clock pulse ahead of the storage reg-ister. All inputs are equipp ed with protection circuits against static discharge and transient excess volt-age. 1/13

74HC595完整中文资料

74HC595芯片是一种串入并出的芯片,在电子显示屏 制作当中有广泛的应用。 74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。 三态。特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出; 标准中等规模集成电路应用串行到并行的数据转换 Remote c ontrol holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。 595是具有8位移位寄存器和一个存储器,三态输出功能。移位寄存器和存储器是分别的时钟。数据在SCHcp的上升沿输入,在S Tcp的上升沿进入的存储寄存器中去。如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。 CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F 1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压 引脚说明符号引脚描述

内部结构 结合引脚说明就能很快理解 595的工作情况 功能表: 管脚编号管脚名管脚定义功能 1、2、3、4、5、6、 7、15 QA—QH 三态输出管脚 8 GND 电源地 9 SQH 串行数据输出管脚 10 SCLR 移位寄存器清零端 11 SCK 数据输入时钟线 12 RCK 输出存储器锁存时钟线 13 OE 输出使能 14 SI 数据线 15 VCC 电源端 真值表: 输入管脚 输出管脚 SI SCK SCLR RCK OE X X X X H QA—QH 输出高阻 X X X X L QA—QH 输出有效值 X X L X X 移位寄存器清零 L 上沿H X X 移位寄存器存储L H 上沿H X X 移位寄存器存储H X 下沿H X X 移位寄存器状态保持 X X X 上沿X 输出存储器锁存移位寄存器中的状态值 X X X 下沿X 输出存储器状态保持74595的数据端:

74HC595D

74hc595d中文资料,74hc595d pdf 74HC595中文资料 8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。三态。 特点 8位串行输入 8位串行或并行输出 存储状态寄存器,三种状态 输出寄存器可以直接清除 100MHz的移位频率 输出能力 并行输出,总线驱动 串行输出;标准 中等规模集成电路 应用 串行到并行的数据转换 Remote control holding register. 描述 595是告诉的硅结构的CMOS器件, 兼容低电压TTL电路,遵守JEDEC标准。 595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。 数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。 移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。 74HC595参考数据 CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压 74HC595引脚说明 74HC595功能表

H=高电平状态 L=低电平状态 ↑=上升沿 ↓=下降沿 Z=高阻 NC=无变化 ×=无效 当MR为高电平,OE为低电平时,数据在SHCP上升沿进入移位寄存器,在STCP上升沿输出到并行端口。 74hc595d的生产厂家有NXP Semiconductors和ON Semiconductor 最近闲来无事,想想好久没写点什么了。所以闲余时间就写了个小程序和大家学习交流。虽然通过仿真器调试过,但是由于没有做硬件,所以难免有疏漏之处,希望各位访客在发现后能指正。 硬件电路及程序原理描述:数码管采用8段共阴数码管。两块74HC595分别用来作为段码和片选,U1作为段码驱动(高电平有效),U2作为片选(低电平有效),程序中先发送高8位的片选码,然后发送低8位的段码,每发送一次只能显示以个数码管,通过延时防止闪烁,然后循环发送8次之后,正好8个

74ls595芯片中文资料

74595 外形图____ Q B--|1 16|--VccQC--|2 15|--QAQD--|3 SIQE--|4 13|--/GQF--|5 12|--RCKQG--|6 11|--SCKQH--|7 /SCLRGND-18 9|--QH'| _______ |74595 的数据端: QA--QH: 八位并行输出端,可以直接控制数码管的8个段。 QH': 级联输出端。 我将它接下一个595的SI端。 SI: 串行数据输入端。 74595的控制端说明: /SCLR(10脚): 低点平时将移位寄存器的数据清零。 通常我将它接Vca SCK(11脚): 上升沿时数据寄存器的数据移位。 QA-->QB-->QC-->…-->QH下降沿移位奇存器数据不变。 (脉冲宽度: 5V时,大于几十纳秒就行了。14|-- 10|--

我通常都选微秒级)RCK(12脚): 上升沿时移位寄存器的数据进入数据存储寄存器,下降沿时存储寄存器数据不变。 通常我将RCK置为低点平,当移位结束后,在RCK端产生一个正脉冲(5V 时,大于几十纳秒就行了。 我通常都选微秒级),更新显示数据。 /G(13 脚): 高电平时禁止输出(高阻态)。 如果单片机的引脚不紧张,用一个引脚控制它,可以方便地产生闪烁和熄灭效果。 比通过数据端移位控制要省时省力。 注: 74164和74595功能相仿,都是8位串行输入转并行输出移位寄存器。 74164的驱动电流(25mA)比74595(35mA)的要小,14脚封装,体积也小一些。 74595的主要优点是具有数据存储寄存器,在移位的过程中,输出端的数据可以保持不变。 这在串行速度慢的场合很有用处,数码管没有闪烁感。 与164只有数据清零端相比,595还多有输出端时能/禁止控制端,可以使输出为高阻态。 另外,据网上报价,贴片164每只1元钱,贴片595

sn74hc595中文版

SN74HC595 概述 74HC595包含一个8位串行输入,并行输出的移位寄存器,该寄存器向一个8位D型存储寄存器提供数据。74HC595的存储寄存器具备三态输出。移位寄存器和存储寄存器分别有独立的时钟。74HC595的移位寄存器带有最高优先级的直接清零端(SRCLR)、串行输入端(SER)和用于级联的串行输出端。当输出使能端(OE)为高时,74HC595的输出将处于高阻态。 不管是移位寄存器时钟(SRCLK)还是存储寄存器时钟(RCLK),都是上升沿触发。如果两个时钟绑定在一起,则移位寄存器将一直领先存储寄存器一个时钟脉冲。SN74HC595 参数 74HC595 主要参数 电压 2.0~6.0 驱动电流-6/6 mA 最大传输延迟34 ns 74HC595 其他特性 逻辑电平CMOS 清零异步 74HC595 封装与引脚 PDIP16, SOIC16, SOP16, SSOP1 TSSOP16 SN74HC595 特性 8位串行输入,并行输出移位 宽工作电压范围:2.0~6.0 V 高强度电流三态输出,最多可驱动高达15个LSTTL负载低功耗,最大I CC80μA 典型t pd = 13 ns 5 V下驱动电流为± 6 mA 低输入电流,最大1μA 移位寄存器可直接清零 产品简介 SN74HC595N,8 位移位寄存器,具有三态输出锁存 型号标识/ 参数 SN74HC595N型号标识及主要参数: 封装类型 SN74HC595N封装信息:类型:PDIP 引脚:16 包装规格

SN74HC595N包装规格: 类型:Tube(管装) 每管:25 pcs 产品简介 SN74HC595D,8 位移位寄存器,具有三态输出锁存型号标识/ 参数 SN74HC595D型号标识及主要参数: