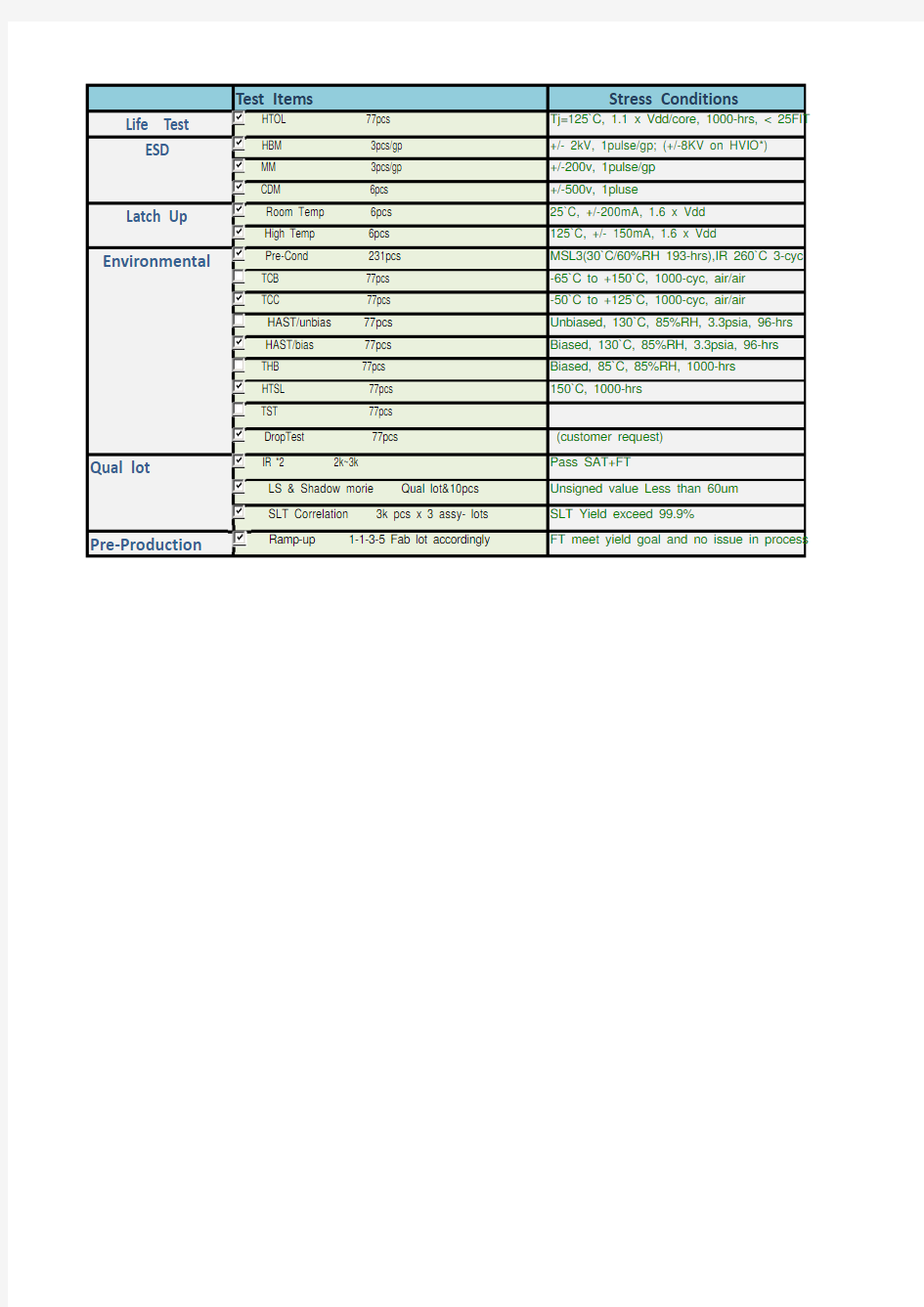

IC封装质量可靠性测试

Test Items

Stress Conditions

Life Test HTOL 77pcs Tj=125`C, 1.1 x Vdd/core, 1000-hrs, < 25FIT HBM 3pcs/gp +/- 2kV, 1pulse/gp; (+/-8KV on HVIO*) MM 3pcs/gp +/-200v, 1pulse/gp CDM 6pcs +/-500v, 1pluse

Room Temp 6pcs 25`C, +/-200mA, 1.6 x Vdd High Temp 6pcs 125`C, +/- 150mA, 1.6 x Vdd

Pre-Cond 231pcs MSL3(30`C/60%RH 193-hrs),IR 260`C 3-cyc TCB 77pcs -65`C to +150`C, 1000-cyc, air/air TCC 77pcs -50`C to +125`C, 1000-cyc, air/air HAST/unbias 77pcs Unbiased, 130`C, 85%RH, 3.3psia, 96-hrs HAST/bias 77pcs Biased, 130`C, 85%RH, 3.3psia, 96-hrs THB 77pcs Biased, 85`C, 85%RH, 1000-hrs HTSL 77pcs 150`C, 1000-hrs

TST 77pcs DropTest 77pcs

(customer request)Qual lot

IR *2 2k~3k

Pass SAT+FT

LS & Shadow morie Qual lot&10pcs Unsigned value Less than 60um SLT Correlation 3k pcs x 3 assy- lots

SLT Yield exceed 99.9%

Pre-Production

Ramp-up 1-1-3-5 Fab lot accordingly

FT meet yield goal and no issue in process

ESD Latch Up Environmental

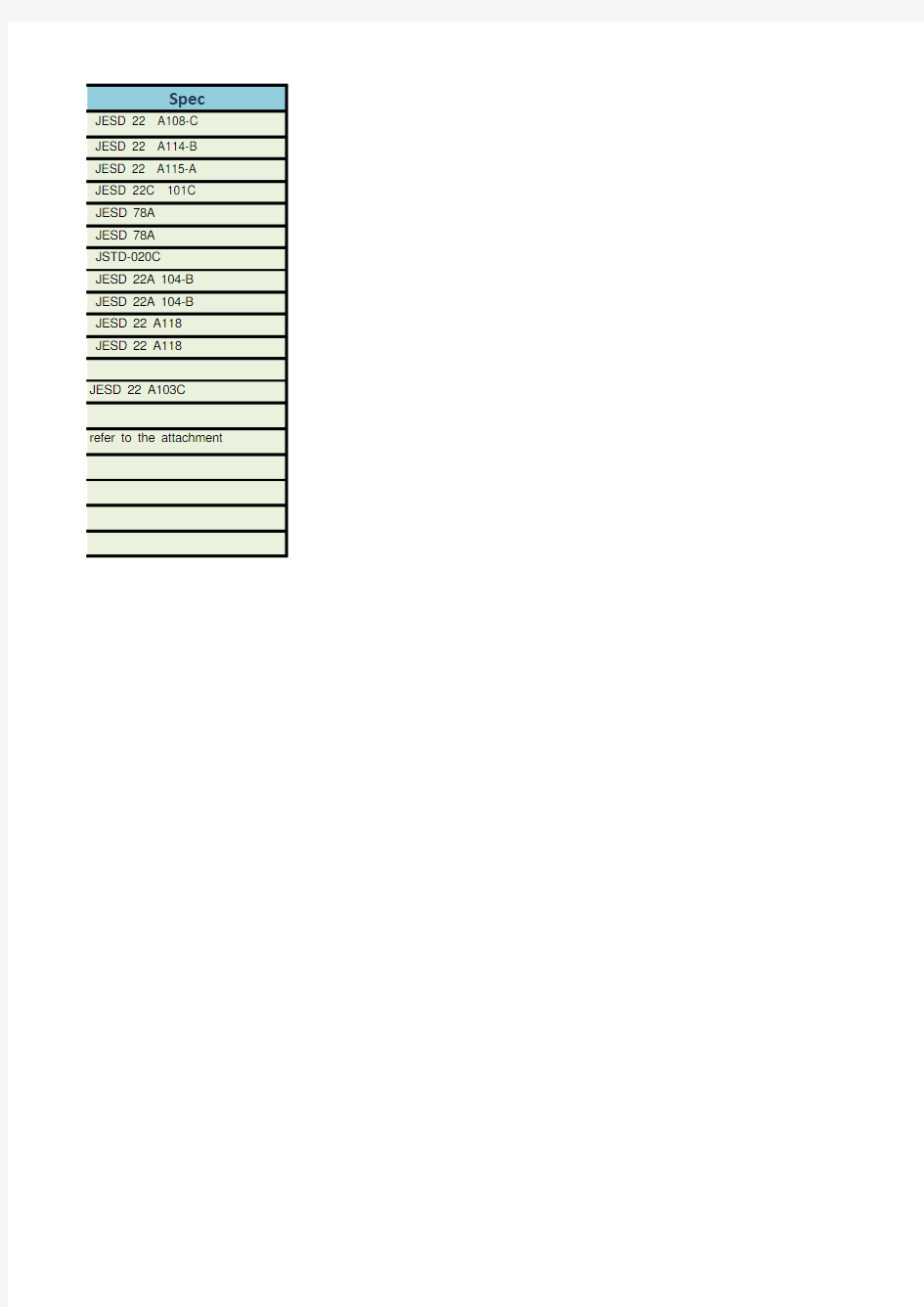

Spec JESD 22 A108-C

JESD 22 A114-B

JESD 22 A115-A

JESD 22C 101C

JESD 78A

JESD 78A

JSTD-020C

JESD 22A 104-B

JESD 22A 104-B

JESD 22 A118

JESD 22 A118

JESD 22 A103C

refer to the attachment