基于FPGA ad数据采集存储处理报告(含Verilog源代码)

基于FPGA AD数据采集存储处理项目报告

(XILINX ALTEARA 都可用)

组员:华、文、杰

一、实验目的

本次实验利用Basys2开发板完成一个开发小项目,即开发AD数据采集存储处理系统,旨在掌握FPGA开发基本方法以及锻炼解决开发过程中出现问题的能力。

二、关键词

Basys2、FPGA、AD转换、RAM、串口通信、MATLAB处理

三、方案设计

要实现本次项目,首先确定器件,其次根据器件时序写出模块的使用程序,最后综合成一个工程,然后进行仿真,上板实验。

本次实验的器件:32M8位模数转换器、Basys2开发板、串口转RS232cp2102模块、基于三极管的电平转换电路。

选择好器件后,根据器件的时序完成模块的代码书写。

写好AD模块、串口通信模块后,现在就需要处理采样速率与串口通讯速率不匹配的问题了。根据香农采样定理,采样频率得高于信号频率的两倍才能完成信号复现,我们这里使用25M的高速采样频率,而串口dps9600传送一个位104us 明显比采样慢许多。所以这里需要解决速率不匹配的问题。我们想到可以利用FPGA的RAM先存储采样来的数据,然后再提取数据经过串口通信送至PC经由MATLAB处理。

本次小项目最为关键的是控制好采样与串口通信的时序问题。关于时序的控制,留到模块介绍里面说明。

方案小结:本次实验基于片内RAM存储AD采样过来的数据,然后待采样完成后提取数据串口通信至PC,最后经由matlab处理。

四、模块介绍

1.Verilog开发程序介绍

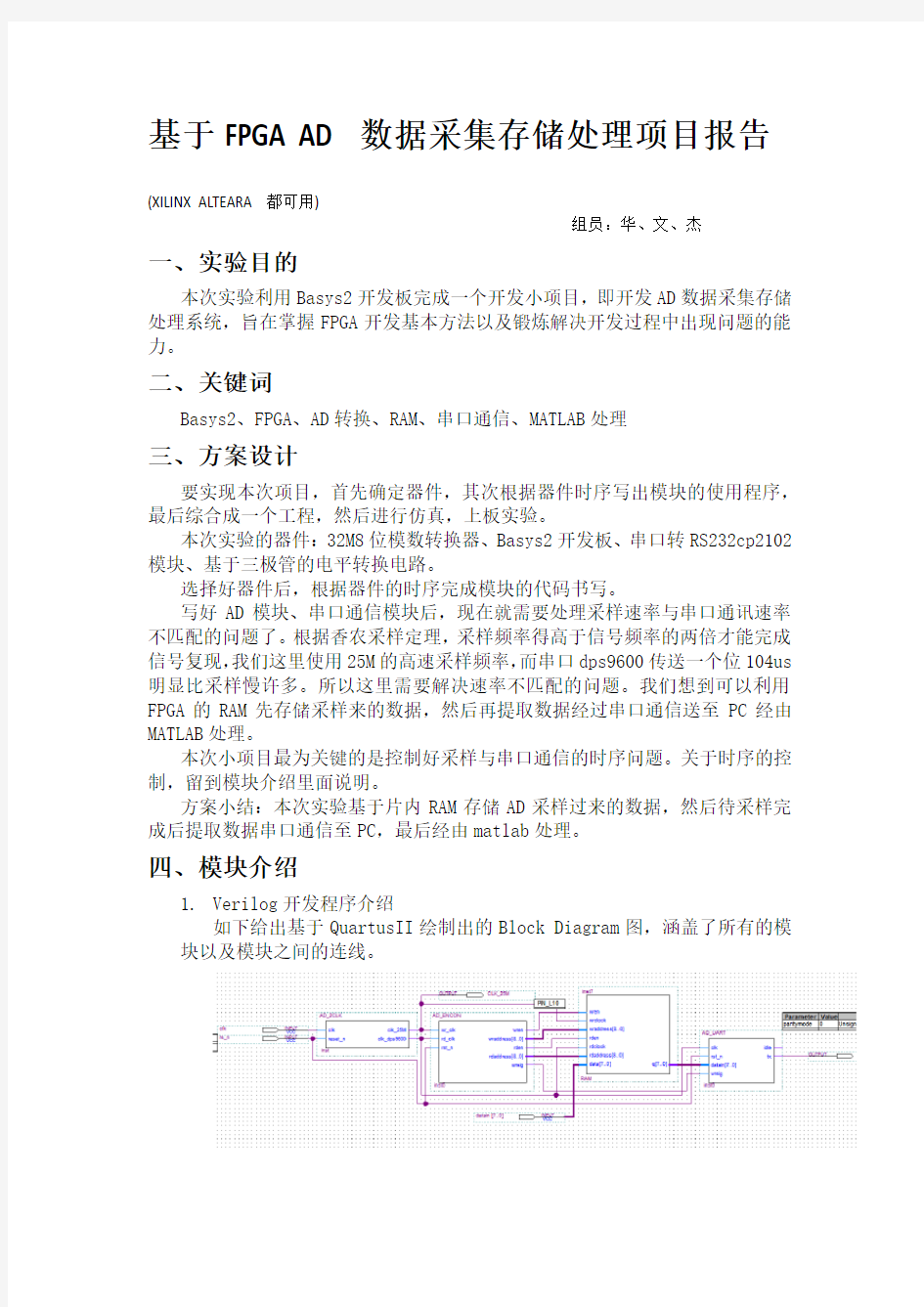

如下给出基于QuartusII绘制出的Block Diagram图,涵盖了所有的模块以及模块之间的连线。

图4.1 综合模块图

如下给出程序目录(txt格式):

现在分别介绍各个模块的端口以及功能。

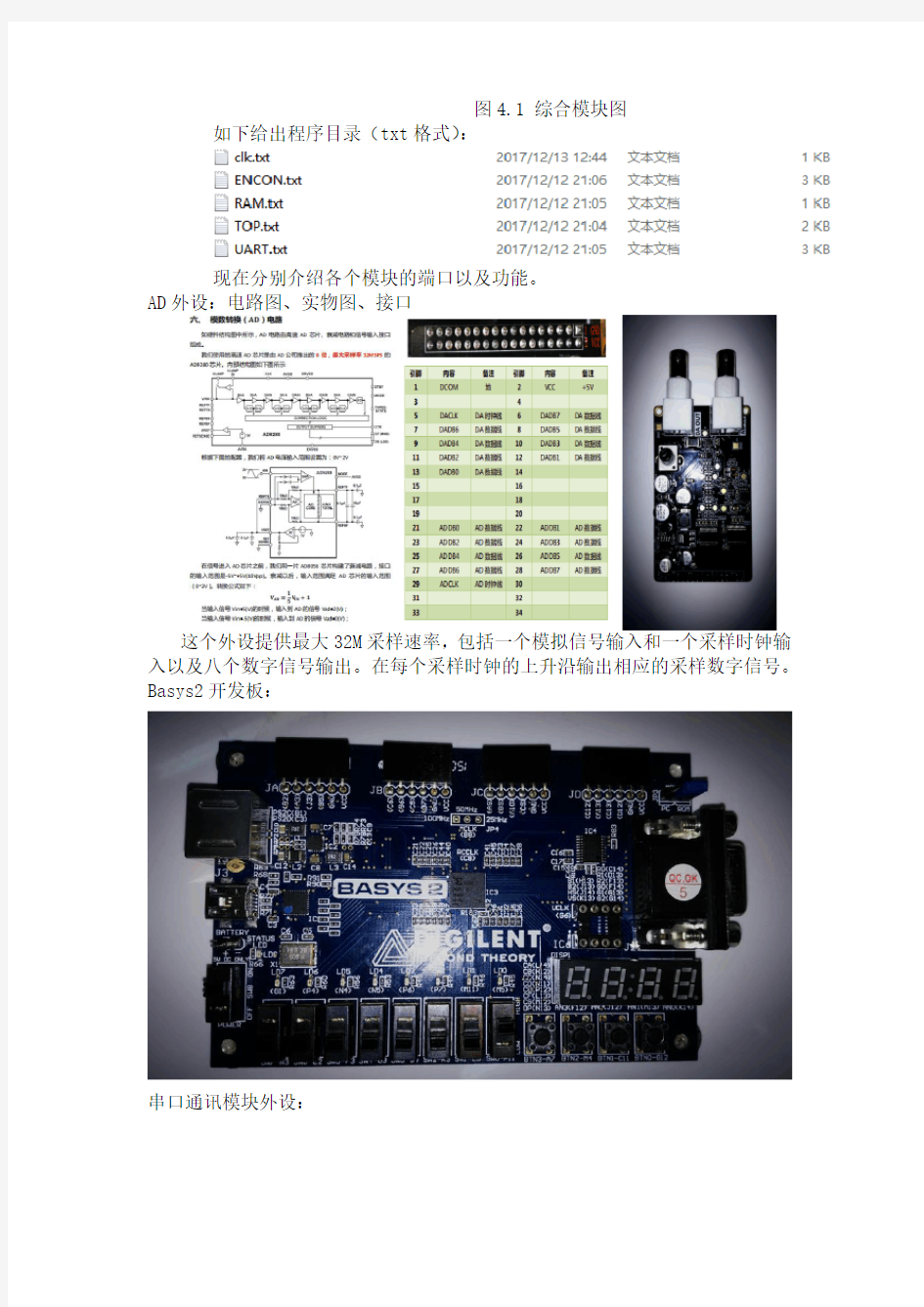

AD外设:电路图、实物图、接口

这个外设提供最大32M采样速率,包括一个模拟信号输入和一个采样时钟输入以及八个数字信号输出。在每个采样时钟的上升沿输出相应的采样数字信号。Basys2开发板:

串口通讯模块外设:

这个模块旨在把Basys2输出的LVTTL转换成RS232的负逻辑高电平,实现串口与PC的通信。

它有五个引脚:GND、3.3V、5V、TXD、RXD。在使用中,只使用RXD和GND。

需要注意的是,倘若GND不与FPGA串口的GND连接,那么串口输出的电平,此模块无法识别,这就是数字地需要共地的重要性。

这里的RXD接Basys的串口输出C6(这是分配的tx输出管脚)。

接线当然用杜邦线的公母线连接。

TOP模块:

TOP模块命名为TEST是当时自己写的非最终版程序用来测试正确性,最

后测试正确后也没修改过来,但是对仿真没影响。

clk是系统时钟输入,用来作为全局时钟并且为调用后面四个子模块提供时钟基础,设置为50M。

rst_n是系统复位设置,复位到初始状态,这里大家都熟悉,不用多说。

input[7:0]datain是AD外设的8位数字信号输入,这个数字信号随着AD采样时钟(clk_25M)变化,在后面CLK模块里面会说明。

output clk_25M为调用CLK模块后输出的AD采样时钟,这个输出用来接AD外设的时钟输入,提供采样时钟。

output tx为调用uart模块后,与PC通信的“桥梁”,即携带数据的信号吧。

CLK模块:

这里模块名字设置为AD_2CLK,旨在表明输出两个CLK,用来AD采样和串口通信。

input clk为系统时钟50Mhz。

Input reset_n为系统复位,低电平有效。

Output reg clk_25M为AD采样时钟,之前做过说明。

Output reg dps9600为输出给uart模块的时钟。

ENCON模块:

这个模块是整个程序的控制核心,下面介绍端口说明。

Input wr_clk为写时钟输入,这里我们接的当然就是AD写入的时钟CLK_25M,这里的写速率要和采样速率匹配才可以保证采样再存储的正确性。

Input rd_clk为读时钟输入,这里接dps9600,符合串口协议。

Input rst_n为系统复位,低电平有效。

Output reg wren为写使能输出,当wren为高时,写有效,即表明AD的八位数字信号写进RAM。

Output reg [8:0]wraddress为写地址,写地址在写时钟下降沿完成加一,

保证每次写完后都是新的地址存储数据保证了ram能够存储512个正确数据。

Output reg rden为读使能输出,当rden为高时,读有效,即表明RAM里面对应地址的信号读出。

Output reg [8:0]rdaddress为读地址,在每个读信号的下降沿完成加一,保证每次读完一个数据后地址指向新的内容,保证读出的512个数据的正确性。

Output reg wrsig 为发送给串口的发送信号,上升沿有效。每一上升沿使串口开始发送送到串口的数据给PC。

RAM模块:

Input wr_clk为RAM的写时钟,上升沿有效在相应地址写入数据。

Input wren为RAM写使能信号,高电平有效,有效时配合wraddress和wrclk 进行写操作。

Input [8:0]wraddress为写地址,在每个wr时钟下降沿完成加一操作,确保每次写入的地址正确性。

Input rd_clk为RAM的读时钟,上升沿有效,在相应的地址读出数据。

Input [8:0]rdaddress为读地址,同写地址功能。

Input rden,同wren。

Output dataout是读出的数据,送至UART模块通信给PC。

UART模块:

Input clk为CLK模块的clk_dps9600,用于配合这个模块打成波特率为9600的串口输出。

Input rst_n为复位,低电平有效。

Input [7:0]datain接RAM模块的数据输出。

Input wrsig上升沿有效,开启串口发送,接ENCON模块wrsig。

Output reg idle 为串口工作状态说明,为高表明正在发送数据。

Output tx为发送的串口信号,接至上面的串口通讯外设模块RXD。

介绍完所有模块后,现在给出仿真波形以及testbench的设置。TOP程序以及子程序调用:

Testbench:

对应的仿真波形:

可见,CLK25M输出正确。

可见,tx的输出也满足设计的10101010B

然后验证每个位的时间,大概为104us,满足通信要求仿真通过。

2.Matlab处理程序介绍:

程序:

串口调试小助手软件以及工作界面:

这个程序提取串口通信至PC的数据(经由串口调试小助手输出),然后将十六进制转换成十进制最后绘图输出。

五、关键问题分析处理

我们小组在代码编写编译过程、仿真过程以及上板过程中出了不少错误,但最终都及时纠正了。在这个发现问题与解决问题的两周里,我们小组对出现的部分问题做了分析与记录有些还自行设计了实验验证。如下列出了一些关键问题的分析处理。

Ⅰ:模块的购置问题与电平是否兼容的处理

我们的小项目设计到两个外设,一个是AD转换模块一个是串口转RS232通信模块。在购置模块时需要考虑引脚电平是否与FPGA电平(我们这里使用的是LVTTL 3.3V引脚电平)兼容,所需要的引脚空间Basys2是否有足够的提供,还需要考虑成本以及模块的时序问题。

本实验过程中,我们购置了兼容LVTTL八位AD转换模块和兼容TTL的串口通信模块。成本很低,串口模块加上AD模块在几十块以内。

网购的模块到了之后,我们开始测试各模块的电平值。

经测试,AD输出高3.34V低0V,符合LVTTL3.3V电平逻辑

经测试,串口模块txd输出高5v,低0V。基于这里,我们通过串口txd接自己的rxd实现了串口模块是否损坏的测试,测试通过,串口是

好的。由于在测量电平时,我们没有完成上板工作,所以我们只好假设

串口模块rxd需要接TTL5V逻辑才可正常工作,因此我们组利用两个三

极管搭建了一个电平转换电路,实现了电平转换。

其实到后面的上板工作之后,发现3.3V的输出接到RXD,也能正常工作。

Ⅱ:源代码的借鉴与部分时序代码设计问题

我们程序需要Verilog串口通信模块,为了节省时间,我们在网上寻找了若干串口通信例程,在掌握了例程的原理后,我们自行又编写了

自己的串口模块和分时模块还有存储模块以及时序控制模块。其中,最

为困难的是采集速率和通信速率不匹配怎么解决的问题。我们采取利用

ram存储并且提取数据以及设计了合理的存储提取时序控制模块解决这

个问题。然而其中困难重重,由于网上资源有限,对ISEramip核理解不

够,我们花了很多时间思考怎么实现这个速率匹配。最终利用[]ram[]

语句构成的模块实现了ram存取功能。之后时序控制也顺利设计出来。Ⅲ:分模块调试

在完成了各个模块的基本书写后,分模块调试是必须的,不然当各个模块整合到主程序之后除了问题,都不好分析。

这里的调试当然还是基于testbench的仿真调试。

Ⅳ:子程序直接的衔接

在主程序里调用子程序的过程中,我们出现了变量格式不匹配的问题,即上个子程序的输出需要用wire型去构成下个子程序的输入。而最

开始,缺少经验的我们用的是reg型变量来衔接子程序。仔细想想两个

变量类型就知道,子程序就当作是一个黑盒子,只有输入输出,输出的

变量类型就是wire型。在这个变量类型的选择上,我们组在这里跌了大

坑,不过最终还是成功解决。顺利完成编译工作。

Ⅴ:主程序里子程序的分块调试

完成编译工作之后,并不代表仿真就可以通过。我们组就遇到了这样的问题。我们在testbench里设计了[7:0]datain的激励输入,结果

得到的tx输出既有高阻态也有红线不确定值输出。简而言之,仿真出错。

所以我们开始在主程序里面执行程序的分块调试。考虑到我们程序的时序逻辑。我们由输入一个个分块仿真一直到最后输出。即先在主程

序仿真CLK模块,注释掉其他模块并做做适当修改(比如在主module

里面添加时钟输出),验证好CLK模块之后,再在主程序里面仿真

CLK+ENCON模块,然后再方向很CLK+ENCON+RAM模块,最后在全部仿真。

经过上述主程序里的分块调试,我们成功完成了软件仿真工作。Ⅵ:串口调试软件的熟悉

我们的项目需要利用到一个软件,串口调试小助手。这个软件我们不是很熟悉,我们自己单独设计了一个串口通信工程,并且利用我们购

置的串口通信模块完成这个熟悉过程。

主要是通过修改数据长度、校验选择、停止位长度,来熟悉他们之间的通信协议。最终大家都对这个软件的应用有了深入了解。

Ⅶ:上板调试

我们组花了两个下午和三个晚上在南一楼完成调试工作,期间出了诸多问题。但是我们冷静的分析问题,并且根据问题的现象给出做出假设,并给出试探性的解决方案。这样一步一步,大概处理了七八个问题之后,我们上板终于通过了。

Ⅷ:最重要的数字地共地问题

这是本次上板实验过程中,出现的最大的问题!

为什么要共地?因为我们需要一个标准去衡量数字电路中的高电平到底有多高。

我们实验有三个地:BASYS2 FPGA PMOD io地、串口模块地、AD模块地(也就是给AD模块供电的电源地,这里使用的是实验室的电源)。

第一个晚上的调试过程中,PMOD地和串口模块地没接,仅仅有一个AD地,结果导致PC上串口调试小助手只能一次接受到512个00数据(这

里我们设计的一次采集512个数据),表明我们的软件模块并没出错,出

错的是硬件连线。

我们冷静分析,在第二个晚上的实验中,把PMOD地与AD地共在一起,发现不能接受到512个数据了,只能随机的不可控的接到诸如FF FE

这样的错误数据,而且只能接收到一两个数据。出了这样的问题,大家

都手足无措。

第三天晚上也就是项目提交的前一天晚上,我们把三个地全部接在一起。兴奋的发现,通过!

可见,共地在数字电路中是多么重要。

六、结果与分析

如下是在实验室验收时的一张图:

写在前面:本实验采样时钟25M,AD是八位而且输出幅度可调,每次采样512个数据。

故每次采样的总时长:512*40ns20000ns=20us,f=50khz

也就是说信号为50khz能够采集一个周期,信号为100KHZ能够采集两个周期……

测量结果:

sin50KHZ:

squ50KHZ:

Tri50KHZ:

Sin150KHZ:

Squ150KHZ:

Tri150KHZ:

sin500KHZ:

Sin1MHZ:

Sin5MHZ:

结果分析:信号源VPP都是2.9V,基于上面的AD转换的算法介绍,我们简单计算一下每个波形最高点对应的十进制数:( 2.9/5+1)/2*255=201

而我们采样出来的一般在180左右。为什么?因为我们说过,这个AD采样器有控制采样输出幅度的功能。如果要实现准确电压复现,可以再通过一个转换算法即可。

根据上述三种波形以及不同频率的波形展示,可以看出,我们基本上完成了项目功能。但是在5M赫兹时,输出波形躁动很大,研究发现,是因为信号发生器的稳定性原因导致。(实验室信号发生器在5Mhz时稳定性很低)

七、总结

经过本次小项目,我们大家经历了很多。从立项到方案设计、模块购置、代码书写调试、仿真调试上板测试等等,大家一起在宿舍与南一实验室直接奔波多次,才完成这个项目,其中的辛苦不易溢于言表。

这个项目,网上基本上找不到完整源代码,所以我们自行设计了除了串口之外的全部代码,这很好的锻炼了我们的应用知识的能力。

在项目工作中,我们知道了发现问题的重要性,清楚的认识到如何设计实验如何设计方案却解决问题更为重要。

我们团结协作大家一起烧脑思考的奋斗经历更是难忘的。

附录:源代码

//////////////////////////////

//////////////////////////////

module TEST(

input clk, //50M

input rst_n, //复位

input [7:0] datain, //AD输入

output clk_25M,

output tx //串口

);

wire clk_dps9600;

ad_2clk u1(

.clk(clk), //系统时钟50Mhz

.reset_n(rst_n), //复位,低电平有效,复位时时钟都低.clk_25M(clk_25M), //用于AD采样的频率

.clk_dps9600(clk_dps9600) //用于串口通信的频率

);

wire wren;

wire [8:0]wraddress;

wire [8:0]rdaddress;

wire rden;

wire wrsig;

ad_encon u2(

.wr_clk(clk_25M), //写时钟输入

.rd_clk(clk_dps9600), //读时钟输入

.rst_n(rst_n), //复位信号,低电平有效

.wren(wren), //写使能输出

.wraddress(wraddress), //写地址输出

.rden(rden), //读使能输出

.rdaddress(rdaddress), //读地址输出

.wrsig(wrsig) //串口发送信号输出

);

wire [7:0]dataout;

ram u3(

.wr_clk(clk_25M), //采集时钟

.rd_clk(clk_dps9600), //串口通讯时钟

.wren(wren), //写使能

.rden(rden), //读使能

.datain(datain), //采集数据入

.wraddress(wraddress), //写地址

VerilogHDL经典程序非常适合新手

一、2线-4线译码器 module counter4(q1,q0,ncr,cp); input cp,ncr; output q1,q0; reg q1,q0; always@(posedge cp or negedge ncr) begin if(~ncr){q1,q0}<=2'b00; else{q1,q0}<={q1,q0}+1'b1; end endmodule 二、4选1数据选择器 module selector4_1(i0,i1,i2,i3,a1,a0,y); input i0,i1,i2,i3,a1,a0; output y; reg y; always@(a1or a0) begin case({a1,a0}) 2'b00:y=i0; 2'b01:y=i1; 2'b10:y=i2; 2'b11:y=i3; default:y=0; 一、2线-4线译码器 module counter4(q1,q0,ncr,cp); input cp,ncr; output q1,q0; reg q1,q0; always@(posedge cp or negedge ncr) begin if(~ncr){q1,q0}<=2'b00; else{q1,q0}<={q1,q0}+1'b1; end endmodule 二、4选1数据选择器 module selector4_1(i0,i1,i2,i3,a1,a0,y); input i0,i1,i2,i3,a1,a0; output y; reg y; always@(a1or a0) begin case({a1,a0}) 2'b00:y=i0;

施工质量控制的内容和方法

22104030施工质量控制的内容和方法 复习要点 1.施工质量控制的基本环节和一般方法 (1)施工质量控制的基本环节包括事前、事中和事后质量控制。 (2)施工质量控制的依据分为共同性依据和专门技术法规性依据。 (3)施工质量控制的一般方法包括质量文件审核和现场质量检查。现场质量检查的内容包括开工前的检查;工序交接检查;隐蔽工程的检查;停工后复工的检查;分项、分部工程完工后的检查以及成品保护的检查。检查的方法主要有目测法、实测法和试验法。试验法又分为理化试验和无损检测。 2.施工准备阶段的质量控制 (1)施工质量控制的准备工作包括工程项目划分与编号以及技术准备的质量控制。 (2)现场施工准备的质量控制包括工程定位和标高基准的控制以及施工平面布置的控制。 (3)材料的质量控制要把好采购订货关、进场检验关以及存储和使用关。 (4)施工机械设备的质量控制包括机械设备的选型、主要性能参数指标的确定以及使用操作要求。 3.施工过程的质量控制 (1)技术交底书应由施工项目技术人员编制,并经项目技术负责人批准实施。交底的形式有:书面、口头、会议、挂牌、样板、示范操作等。 (2)项目开工前应编制测量控制方案,经项目技术负责人批准后实施。 (3)施工过程中的计量工作包括施工生产时的投料计量、施工测量、监测计量以及对项目、产品或过程的测试、检验、分析计量等。其主要任务是统一计量单位制度,组织量值传递,保证量值统一。 (4)工序施工质量控制主要包括工序施工条件质量控制和工序施工质量效果控制。 (5)特殊过程是指该施工过程或工序的施工质量不易或不能通过其后的检验和试验而得到充分验证,或万一发生质量事故则难以挽救的施工过程。其质量控制除按一般过程质量控制的规定执行外,还应由专业技术人员编制作业指导书,经项目技术负责人审批后执行。(6)成品保护的措施一般包括防护、包裹、覆盖、封闭等方法。 4.工程施工质量验收的规定和方法 (1)工程施工质量验收的内容包括施工过程的工程质量验收和施工项目竣工质量验收。(2)施工过程的工程质量验收,是在施工过程中、在施工单位自行质量检查评定的基础上,参与建设活动的有关单位共同对检验批、分项、分部、单位工程的质量进行抽样复验,根据相关标准以书面形式对工程质量达到合格与否做出确认。 (3)施工项目竣工验收工作可分为验收的准备、初步验收(预验收)和正式验收。 一单项选择题

新闻发布系统的设计与实现

1.引言 近年来,Internet 的高速发展带动了整个世界新闻传播的速度,我们每一刻都可以从网络上知晓世界上发生的事情。电脑的普及,移动视频,智能手机等传媒终端的迅速的发展。使传统的信息传播媒体如电视、广播、报纸等逐渐被人们抛弃,满足不了人们对外界瞬息万变的信息的好奇心,因而人们越来越习惯依赖网络新闻媒体。新闻的传播方式发生了巨大的变化,人们更多的开始关注网络新闻媒体。这种媒体不但具备新闻传播的特点:及时、准确。还具有信息量大、方便管理、方便阅读等特点。有了新闻发布系统后,可以随意查询新闻,快速找到自己喜欢的新闻,并可以发表自己的评论,也方便了管理员使其能够更加清晰的管理新闻,很好地提高了管理者的效率。 当今,网络已成为了人们日常生活信息来源的主要途径,人们都习惯于通过上网来获取信息,在这种发展形势下,网络新闻逐渐深入我们的生活,成为获得信息的一个重要手段。由于 Internet 的信息容量大,传播范围广,信息传播及时并且内容准确,大大满足了人们的需要。把所有的信息都上传到网络,供大家相互浏览、评论,使网络的信息量越来越大,所以我们迫切的需要开发一个基于网络的新闻信息浏览系统。 2.新闻发布系统的需求分析 2.1性能需求 该系统在性能功能上应达到如下需求: 1)操作简单、界面友好: 完全控件式的页面布局,使得新闻的录入工作更简便,许多选项包括新闻分类、来源部门等只需要点击鼠标就可以完成;另外,跟踪出现的提示信息也让用户随时清楚自己的操作情况。对常见网站的新闻管理的各个方面:新闻录入、浏览、删除、修改、搜索等方面都大体实现,实现了网站对即时新闻的管理要求; 2)即时可见:对新闻的处理(包括录入、删除)将立即在主页的对应栏目显示出来,达到“即时发布、即时见效”的功能; 3)系统运行应该快速、稳定、高效和可靠; 4)在结构上应具有很好的可扩展性,便于将来的功能扩展和维护。

Verilog编码风格

Verilog编码风格 嵌入式开发2010-05-03 15:28:13 阅读14 评论0 字号:大中小订阅 这是以前公司的对fpga代码编写的要求 良好代码编写风格的通则概括如下: (1)对所有的信号名、变量名和端口名都用小写,这样做是为了和业界的习惯保持一致;对常量名和用户定义的类型用大写; (2)使用有意义的信号名、端口名、函数名和参数名; (3)信号名长度不要太长; (4)对于时钟信号使用clk 作为信号名,如果设计中存在多个时钟,使用clk 作为时钟信号的前缀; (5)对来自同一驱动源的信号在不同的子模块中采用相同的名字,这要求在芯片总体设计时就定义好顶层子模块间连线的名字,端口和连接端口的信号尽可能采用相同的名字; (6)对于低电平有效的信号,应该以一个下划线跟一个小写字母b 或n 表示。注意在同一个设计中要使用同一个小写字母表示低电平有效; (7)对于复位信号使用rst 作为信号名,如果复位信号是低电平有效,建议使用rst_n; (8)当描述多比特总线时,使用一致的定义顺序,对于verilog 建议采用bus_signal[x:0]的表示; (9)尽量遵循业界已经习惯的一些约定。如*_r 表示寄存器输出,*_a 表示异步信号,*_pn 表示多周期路径第n 个周期使用的信号,*_nxt 表示锁存前的信号,*_z 表示三态信号等; (10)在源文件、批处理文件的开始应该包含一个文件头、文件头一般包含的内容如下例所示:文件名,作者,模块的实现功能概述和关键特性描述,文件创建和修改的记录,包括修改时间,修改的内容等; (11)使用适当的注释来解释所有的always 进程、函数、端口定义、信号含义、变量含义或信号组、变量组的意义等。注释应该放在它所注释的代码附近,要求简明扼要,只要足够说明设计意图即可,避免过于复杂; (12)每一行语句独立成行。尽管VHDL 和Verilog 都允许一行可以写多个语句,当时每个语句独立成行可以增加可读性和可维护性。同时保持每行小于或等于72 个字符,这样做都是为了提高代码得可读性; (13)建议采用缩进提高续行和嵌套语句得可读性。缩进一般采用两个空格,如西安交通大学SOC 设计中心 2 如果空格太多则在深层嵌套时限制行长。同时缩进避免使用TAB 键,这样可以避免不同机器TAB 键得设置不同限制代码得可移植能力; (14)在RTL 源码的设计中任何元素包括端口、信号、变量、函数、任务、模块等的命名都不能取Verilog 和VHDL 语言的关键字; (15)在进行模块的端口申明时,每行只申明一个端口,并建议采用以下顺序:

工业自动化数据采集远程控制系统解决方案

工业自动化监控系统解决 方案

目录 一、方案背景 (3) 二、方案简介 (3) 三、方案拓扑图 (3) 四、系统功能简述 (4) 4.1远程数据监控功能 (4) 4.2远程控制功能 (4) 4.3数据存储与分析处理功能 (5) 4.4报警功能 (7) 4.5视频监测功能 (9) 4.6事故追忆功能 (10) 五、方案优势 (10)

一、方案背景 科技发展融合了数字和实体世界,并已经发展成下一个以工业物联网或工业4.0著称的新工业革命。因此,如今工厂面临的是需要更智慧,互联化系统连接到云服务器,通过大数据资料分析驱动更高的生产效率、灵活性能和响应能力。 二、方案简介 中易云工业自动化系统解决方案可以大大降低复杂的工厂物联网系统部署产生的开发管理费用,除了便捷性的生产数据收集、处理、显示来灵活、有序进行生产管理进而提高生产效率外,还可以通过实时监控生产机器的状态以及设备、照明、空调设备的能源消耗,实现运营成本的降低。 三、方案拓扑图

四、系统功能简述 4.1远程数据监控功能 丰富的I/O连接选择,支持TCP、UDP;MQTT、OPC、ModBus等标准通讯协议,能从制造设备、空调设备、加热系统、照明器材以及多种传感器中收集重要数据,适合各种工业自动化领域。通过硬件设备采集到的温湿度、电流电压等数据,通过无线传输,传输到易云系统,完成远程数据的监控。 注:以化工流程自动化操作系统为例,为大家展示易云系统的各种功能和监控界面。便于大家更好的对工业自动化控制系统进行理解。 4.2远程控制功能 参数数据远传至易云系统,实现现场各个设备的数据实时监测,监控人员可以通过电脑网页或是手机app实时查看,还可以自由设置各个参数的标准值上下限,如果数据超限可以给相关的工作人员发送短信或是微信报警提醒,做到提前预警,避免造成不必要的损失,实现在远程就能值守现场设备。如果制造设备、空调设备、加热系统、照明器材等需要进行控制,则从易云系统发送数据指令,控制制造设备、空调设备、加热系统、照明器材的启停。

74LS138Verilog源码

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date: 2020/02/28 13:40:03 // Design Name: // Module Name: _74ls138 // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// module _74ls138(nE1,nE2,E3,B,nY); input nE1,nE2,E3; input [2:0]B; output[7:0]nY; reg[7:0]nY; always@(nE1,nE2,E3,B) if(!nE1 && !nE2 && E3) begin case(B) 3'b000: nY = 8'b1111_1110; 3'b001: nY = 8'b1111_1101; 3'b010: nY = 8'b1111_1011; 3'b011: nY = 8'b1111_0111; 3'b100: nY = 8'b1110_1111; 3'b101: nY = 8'b1101_1111; 3'b110: nY = 8'b1011_1111; 3'b111: nY = 8'b0111_1111; default:nY = 8'b1111_1111; endcase end

全面质量管理的常用方法一

全面质量管理的常用方法一 【本讲重点】 排列图 因果分析法 对策表方法 分层法 相关图法 排列图法 什么是排列图 排列图又叫巴雷特图,或主次分析图,它首先是由意大利经济学家巴雷特(Pareto)用于经济分析,后来由美国质量管理专家朱兰(J.M.Juran)将它应用于全面质量管理之中,成为全面质量管理常用的质量分析方法之一。 排列图中有两个纵坐标,一个横坐标,若干个柱状图和一条自左向右逐步上升的折线。左边的纵坐标为频数,右边的纵坐标为频率或称累积占有率。一般说来,横坐标为影响产品质量的各种问题或项目,纵坐标表示影响程度,折线为累计曲线。 排列图法的应用实际上是建立在ABC分析法基础之上的,它将现场中作为问题的废品、缺陷、毛病、事故等,按其现象或者原因进行分类,选取数据,根据废品数量和损失金额多少排列顺序,然后用柱形图表示其大小。因此,排列图法的核心目标是帮助我们找到影响生产质量问题的主要因素。例如,可以将积累出现的频率百分比累加达到70%的因素成为A类因素,它是影响质量的主要因素。 排列图的绘制步骤 排列图能够从任何众多的项目中找出最重要的问题,能清楚地看到问题的大小顺序,能了解该项目在全

体中所占的重要程度,具有较强的说服力,被广泛应用于确定改革的主要目标和效果、调查产生缺陷及故障的原因。因此,企业管理人员必须掌握排列图的绘制,并将其应用到质量过程中去。 一般说来,绘制排列图的步骤如图7-1所示,即:确定调查事项,收集数据,按内容或原因对数据分类,然后进行合计、整理数据,计算累积数,计算累积占有率,作出柱形图,画出累积曲线,填写有关事项。 图7-1 排列图的绘制步骤 排列图的应用实例 某化工机械厂为从事尿素合成的公司生产尿素合成塔,尿素合成塔在生产过程中需要承受一定的压力,上面共有成千上万个焊缝和焊点。由于该厂所生产的十五台尿素合成塔均不同程度地出现了焊缝缺陷,由此对返修所需工时的数据统计如表7-1所示。 表7-1 焊缝缺陷返修工时统计表 序号项目返修工时fi 频率 pi/% 累计频率 fi/% 类别 1焊缝气孔14860.460.4A 2夹渣5120.881.2A 3焊缝成型差208.289.4B 4焊道凹陷15 6.195.5B 5其他11 4.5100C 合计245100 缝成型差、焊道凹陷及其他缺陷,前三个要素累加起来达到了89.4%。根据这些统计数据绘制出如图7-2所示的排列图:横坐标是所列举问题的分类,纵坐标是各类缺陷百分率的频数。

基于自动化采集数据的设备运行管理系统设计与实现

基于自动化采集数据的设备运行管理系统设计与实现[2006年11月15日] 关键词:设备,系统,数据,采集,运转,运行,scada,实现,信息, 摘要: 本文介绍了如何从油田SCADA系统、原油集输处理站DCS系统中组织、提取设备运行参数信息,如何采用ORACLE数据库来存储这些信息,以及如何对采集的数据进行管理。该系统实现了原油处理站机泵设备、油区抽油机等设备的数据采集、远程存储、自动生成和打印日运转记录报表、设备保养和月运转时间自动清零、设备信息网上发布等管理功能。 关键词: DCS;SCADA;ADO;动态数据交换(DDE) Abstract: The paper brings out the method to obtain the real-time data from SCADA and DCS,and store it to ORACLE database for other application. It has the following function: data acquisition of all kinds of device; remote accessing; creation and printing daily report forms automatically; device maintains; the date find in the LAN. Key words: DCS;SCADA;ADO;Dynamic Data Exchange(DDE) 引言 随着工控技术的高速发展,尤其是计算机技术、网络通信技术、自动化测控技术、信息存储等技术的进一步融合,在作业区内部形成了先进、高速的信息网络化平台,改变了油田的生产和经营管理模式,提高了油田生产自动化水平,实现了低成本、高效率的生产管理。 作业区自建立以来,先后建设了油田生产自动化监控系统(以下简称SCADA系统),原油集输处理集散监控系统(以下简称DCS系统),生产区和市区机关办公楼局域网,并建立了后台数据应用服务器等。这些环境的建成,为各部门提供快速、有效、可靠、全面的信息支持,为全面实现信息化管理奠定了基础。 设备运行管理系统投用前,原油处理站机泵设备、油区抽油机设备运转资料都是通过人工采集,然后形成设备运转纸档案。如今,利用现有自动化系统和设备运行管理系统,实现了设备运行资料采集、保养管理、运转记录报表自动生成、网上查询等功能,并可大幅降低设备管理劳动强度,提高设备资料的共享度。 1系统总体结构 设备资料采集端分别布置在DCS系统和SCADA系统的自动化监控室,它主要完成处理站机泵设备、油区抽油机设备运转资料的采集和远传、自动生成和打印日运转记录报表,提供设备基本资料录入、设备保养管理和月运转时间自动清零等功能。 通过设备资料采集端的远程存储功能,设备数据通过双绞线或光纤、中心交换机存储到ORACLE数据库中。然后,系统采用基于ORACLE数据库的设备数据查询服务,实现了设备数据的分类查询和打印功能。系统总体结构图如图1所示。 2系统软件结构 系统采用C/S/B软件架构进行设计。添加设备模块可以向数据库添加设备基本信息,并且能修改或删除设备信息。对于处理站机泵和抽油井等设备的数据采集,系统可以根据SCADA系统和DCS系统的特点,

全数字锁相环的verilog源代码讲解

支持论坛发展帖出全数字锁相环的verilog源代码,仿真已通过 module dpll(reset,clk,signal_in,signal_out,syn; parameter para_K=4; parameter para_N=16; input reset; input clk; input signal_in; output signal_out; output syn; reg signal_out; reg dpout; reg delclk; reg addclk; reg add_del_clkout; reg [7:0]up_down_cnt; reg [2:0]cnt8; reg [8:0]cnt_N; reg syn; reg dpout_delay; reg [8:0]cnt_dpout_high; reg [8:0]cnt_dpout_low; /******phase detector*****/ always@(signal_in or signal_out begin dpout<=signal_in^signal_out; end /******synchronization establish detector*****/ always@(posedge clk or negedge reset begin if(!reset dpout_delay<='b0; else dpout_delay<=dpout; end always@(posedge clk or negedge reset begin if(!reset begin cnt_dpout_high<='b0; cnt_dpout_low<='b0; end else if(dpout if(dpout_delay==0 cnt_dpout_high<='b0; else if(cnt_dpout_high==8'b11111111 cnt_dpout_high<='b0; else cnt_dpout_high<=cnt_dpout_high+1; else if(!dpout if(dpout_delay==1 cnt_dpout_low<='b0; else if(cnt_dpout_low==8'b11111111 cnt_dpout_low<='b0; else cnt_dpout_low<=cnt_dpout_low+1; end always@(posedge clk or negedge reset begin if(!reset syn<='b0; else if((dpout&&!dpout_delay||(!dpout&&dpout_delay if(cnt_dpout_high[8:0]-cnt_dpout_low[8:0]<=4||cnt_dpout_low[8:0]- cnt_dpout_high[8:0]<=4 syn<='b1; else syn<='b0; end /****up down couter with mod=K****/ always@(posedge clk or negedge reset begin if(!reset begin delclk<='b0; addclk<='b0; up_down_cnt<='b00000000; end else begin if(!dpout begin delclk<='b0; if(up_down_cnt==para_K-1 begin up_down_cnt<='b00000000; addclk<='b0; end else begin up_down_cnt<=up_down_cnt+1; addclk<='b0; end end else begin addclk<='b0; if(up_down_cnt=='b0 begin up_down_cnt<=para_K-1; delclk<='b0; end else if(up_down_cnt==1 begin delclk<='b1; up_down_cnt<=up_down_cnt-1; end else up_down_cnt<=up_down_cnt-1; end end end /******add and delete clk*****/ always@(posedge clk or negedge reset begin if(!reset begin cnt8<='b000; end else begin if(cnt8=='b111 begin cnt8<='b000; end else if(addclk&&!syn begin cnt8<=cnt8+2; end else if(delclk&&!syn

工业自动化数据采集方案

工业自动化数据采集方案 工业自动化数据采集一直是困扰着所有制造工厂的传统痛点,因自动化终端设备品牌类型繁多,不同采购年代的产品厂家和数据接口及支持协议各异,加之国外厂家本地支持有限,费用高昂,只要还有其他人工参与环节,这些数据就不完整,就不能得到实时数据,数据滞后,企业的生产成本就高,产量与效率就相应大打折扣,智能制造业就无从谈起。所以不论智能制造发展到何种程度,工业数据采集都是生产中最实际最高频的需求,也是工业4.0的先决条件。 华辰智通-工业自动化数据采集方案: 大家都认识到实时获取设备层数据、消除自动化孤岛现象是实现智能制造、工业互联网的重要基础环节。但是,工业现场的设备种类繁多,各种工业总线协议并存,这也就导致了数据采集这项工作是一件非常个性化的事情,很难总结出一套放之四海而皆准的方案来。 1.工业数据采集工具:

工具1:工业数据网关 工业数据网关称为工业采集网关,也可以称为工业数据采集网关;它通过以太网接口:RJ45 接口;串行接口:RS485/RS232/RS422接口,可以连接西门子、三菱、欧姆龙、施耐德、台达、汇川、和利时、松下、永宏、海为和MODBUS 系列等。PLC、制器、输入/输出等设备,安全准确传输数据。HINET 系列数据网关是一款单协议单接口的工业数采终端,根据不同的型号HINET 数据网关支持的不同的PLC 品牌。 工业数据网关功能:1、PLC协议解析;2、PLC数据采集;3、数据传输。 HINET 系列数据网关由湖南华辰智通科技有限公司自主研发生产,该网关采用高性能工业级32 位处理器和工业级无线模块,以嵌入式实时操作系统为软件支撑平台,是一款高性能、高性价比、适用于工业互联网便于大规模部署的工业数采终端。 HINET 系列数据网关自带PLC 等工业控制器协议,一次性解决工业设备联网、工业设备数据采集及传输等难题。 工具2:工业智能网关 HINET工业智能网关是一个集成多种互联网通讯技术,面向工业领域的设备通讯终端产品。支持4G、WIFI、以太网等多种互联网接入方式。 1、实现工业现场设备远程控制; 2、实现设备固件远程升级,程序上下载,可灵活接入各种设备管理平台;

verilog有限状态机实验报告(附源代码)

有限状态机实验报告 一、实验目的 ●进一步学习时序逻辑电路 ●了解有限状态机的工作原理 ●学会使用“三段式”有限状态机设计电路 ●掌握按键去抖动、信号取边沿等处理技巧 二、实验内容 用三段式有限状态机实现序列检测功能电路 a)按从高位到低位逐位串行输入一个序列,输入用拨动开关实现。 b)每当检测到序列“1101”(不重叠)时,LED指示灯亮,否则灭,例如 i.输入:1 1 0 1 1 0 1 1 0 1 ii.输出:0 0 0 1 0 0 0 0 0 1 c)用八段数码管显示最后输入的四个数,每输入一个数,数码管变化一次 d)按键按下的瞬间将拨动开关状态锁存 i.注意防抖动(按键按下瞬间可能会有多次的电平跳变) 三、实验结果 1.Rst_n为0时数码管显示0000,led灯不亮,rst_n拨为1,可以开始输入,将输 入的开关拨到1,按下按钮,数码管示数变为0001,之后一次类推分别输入1, 0,1,按下按钮后,数码管为1101,LED灯亮,再输入1,LED灯灭,之后再输 入0,1(即共输入1101101使1101重叠,第二次LED灯不亮),之后单独输入

1101,LED灯亮 2.仿真图像 刚启动时使用rst_n 一段时间后 其中Y代表输出,即控制led灯的信号,sel表示数码管的选择信号,seg表示数码管信号 四、实验分析 1、实验基本结构

其中状态机部分使用三段式结构: 2、整体结构为:

建立一下模块: Anti_dither.v 输入按键信号和时钟信号,输出去除抖动的按键信号生成的脉冲信号op 这一模块实现思路是利用按钮按下时会持续10ms以上而上下抖动时接触时间不超过10ms来给向下接触的时间计时,达到上限时间才产生输出。 Num.v 输入op和序列输入信号A,时钟信号clk和复位信号,复位信号将num置零,否则若收到脉冲信号则将num左移一位并将输入存进最后一位。输出的num即为即将在数码管上显示的值 Scan.v 输入时钟信号,对其降频以产生1ms一次的扫描信号。 Trigger.v 这一模块即为状态机模块,按三段式书写。 整个模块的输入为时钟信号,脉冲信号,序列输入变量,复位信号,输出LED灯控制信号Y。 第一段是状态转换模块,为时序逻辑电路,功能是描述次态寄存器迁移到现态寄存器。即如果收到复位信号将现态置零,否则将上次得到的next_state赋给current_state。

计量自动化系统数据采集成功率低的原因分析

龙源期刊网 https://www.360docs.net/doc/531655535.html, 计量自动化系统数据采集成功率低的原因分析 作者:刘正友 来源:《科技传播》2015年第24期 摘要随着计量自动化系统实用化应用程度的提高,数据采集成功率的重要程度也显得尤 为突出,本文从终端与主站通讯、终端与电能表通讯及计量自动化基础管理方面分析了影响数据采集成功率的原因,提出了提升统数据采集成功率的相关措施。 关键词计量自动化系统;终端;通讯;采集成功率 中图分类号TP3 文献标识码A 文章编号1674-6708(2015)153-0093-01 计量自动化系统承担着厂站终端、负荷管理终端、配变监测终端和低压集抄终端的数据采集、数据处理、数据分析。近年来,随着系统建设和终端全覆盖工作的推进,对系统实用化应用要求在不断提升,系统也从单纯的应用于电费抄核收逐步覆盖到线损管理、停电管理、用电检查、需求侧管理等业务中。由于在系统建设前期只注重系统的建设,忽略了对现场终端安装、调试、参数等相关管理,使系统数据采集成功率不高,远远达不到实用用化应用要求,导致系统数据在相关业务中未得到全面应用,因此,如何提升系统数据采集成功率,是推进计量自动化系统实用化应用的关键环节。 1 数据采集成功率影响原因分析 1.1 终端与主站通讯异常 目前,计量自动化终端与系统主站的通讯方式主要以GPRS为主,终端与主站通过GPRS 通道连接,终端一GPRS通道一主站间构成了一个完整的通讯链路,任何一级通讯链路出现故障,都会影响系统数据采集成功率,造成主站与终端间通讯异常,最直接的状态就是终端掉线,数据不完整或数据丢失,导致数据采集成功率降低。 影响终端与主站通讯的原因主要是现场通讯信号不满足正常通讯要求、通讯卡异常和故障、终端通讯参数错误、终端逻辑地址错误、终端故障等。其中通讯信号不满足要求具体表现为现场无信号、信号强度低于15dB以下、终端天线接触不良或存在人为破坏,导致天线不能正常接收信号等;通讯SIM卡异常主要表现为通讯SIM卡没按要求绑定相关数据业务、通讯SIM损坏、通讯SIM卡装入终端后接触不好;终端通讯参数错误主要表现为主站IP地址、通讯端口号、APN、用户名密码、通讯协议错误;终端逻辑地址错误主要表现为实际终端铭牌标注的终端逻辑地址与终端实际设置的地址不一致;终端故障主要表现为终端在运行过程中频繁

“新闻发布系统”网站制作过程

综合实例:“新闻发布系统”网站 通过一个后台功能较为完备的“新闻发布系统”网站的制作,首页效果如图1所示。 图1 内容 利用https://www.360docs.net/doc/531655535.html,技术开发一个具有后台管理功能的“新闻发布系统”网站,该网站应具备如下功能。 (1)管理员输入用户名和密码,登录成功后可以进入网站后台对新闻进行管理。 (2)管理员能发布新闻,发布的新闻包括标题、内容、提交时间、新闻图片、附件。 (3)管理员能够根据新闻的标题或者新闻的发布时间查找新闻,并能对查找到的新闻进行修改或者删除等操作。 (4)管理员可以修改密码。 (5)用户访问网站首页,可以浏览网站上的所有新闻。 (6)网站要求有较为统一的风格。 网站结构如下图所示。 图2 网站操作流程如下: (1)用户访问网站首页,出现如图1所示的页面。 (2)单击【更多】链接,出现如图3所示的更多新闻页面。 (3)单击第一条新闻的链接,出现如图4所示的新闻明细页面。

图3 图4 (4)管理员访问如图5所示的登录页面,输入正确的用户名和密码,进入后台管理界面,默认显示的是新闻发布页面,如图6所示。 (5)选择【新闻查询】选项,出现如图7所示的新闻查询页面。 (6)单击【修改】链接,跳转到如图8所示的新闻修改页面。 (7)选择【修改密码】选项,出现如图9所示的修改密码页面。 图5

图6 图7 图8

图9 设计“新闻发布系统”程序前的思考 设计“新闻发布系统”前需要思考如下问题。 (1) 如何合理地设计网站目录结构,使得信息能够被有效地分类,同时访问控制又比较方便。由于需要保存新闻的图片和附件,因此需要在网站根目录下分别创建文件夹来保存这两类文件。另外由于本系统存在“管理员”和“用户”两种角色,因此需要把只有管理员才能访问的页面放到同一文件夹中,统一进行权限设置。 (2) 如何合理地设计数据库字段,使得信息维护和检索都较为方便。由于新闻发布系统涉及到的信息项比较少,因此只需要建一张表来保存新闻标题、新闻内容、附件、图片,另外为了保证每条记录的唯一性,需要在表中建自动编号字段。 (3) 采用怎样的导航方式,使得操作界面清晰,便于用户操作。由于本系统涉及页面较少、目录结构比较简单,因此采用导航控件中的Menu 控件、SiteMapPath 控件、TreeView 控件都可以轻松地实现导航功能,其中M enu 控件使用较为方便。 (4) 采用怎样的设计方法,使得页面风格统一。要使页面风格统一,ASP .NET 提供了多种方法如用户控件、母版页、主题、皮肤。在本案例中,为了统一后台界面的风格,采用母版页技术,为了让控件有统一的风格采用主题技术。 (5) 采用怎样的开发方法,开发效率高,程序又不失灵活性。逻辑较为简单的显示部分采用数据访问控件S qlDataSource 结合具有内置分页功能的G ridView 控件,新闻发布和修改等逻辑较为复杂的部分采用代码实现。 有关“新闻发布系统”程序开发的预备知识 (1) 掌握T extBox、L abel、D ropDownList、I mage、F ileUpload、H yperLink 等常用A SP .NET 标准控件的属性、方法和用法。 (2) 掌握验证控件的知识,特别是RequiredFieldValidator 控件的用法。 (3) 了解导航控件,掌握M enu 控件的用法。 (4) 熟悉S QL Server,能够在S QL Server 中创建数据库和表。 (5) 掌握数据访问控件SqlDataSource 以及数据显示控件G ridView、F ormView 的用法。

Verilog的135个经典设计实例

【例3.1】4位全加器 module adder4(cout,sum,ina,inb,cin); output[3:0] sum; output cout; input[3:0] ina,inb; input cin; assign {cout,sum}=ina+inb+cin; endmodule 【例3.2】4位计数器 module count4(out,reset,clk); output[3:0] out; input reset,clk; reg[3:0] out; always @(posedge clk) begin if (reset) out<=0; //同步复位 else out<=out+1; //计数 end endmodule 【例3.3】4位全加器的仿真程序 `timescale 1ns/1ns `include "adder4.v" module adder_tp; //测试模块的名字 reg[3:0] a,b; //测试输入信号定义为reg型 reg cin; wire[3:0] sum; //测试输出信号定义为wire型 wire cout; integer i,j; adder4 adder(sum,cout,a,b,cin); //调用测试对象 always #5 cin=~cin; //设定cin的取值 initial begin a=0;b=0;cin=0; for(i=1;i<16;i=i+1) #10 a=i; //设定a的取值 end - 1 -

initial begin for(j=1;j<16;j=j+1) #10 b=j; //设定b的取值 end initial//定义结果显示格式 begin $monitor($time,,,"%d + %d + %b={%b,%d}",a,b,cin,cout,sum); #160 $finish; end endmodule 【例3.4】4位计数器的仿真程序 `timescale 1ns/1ns `include "count4.v" module coun4_tp; reg clk,reset; //测试输入信号定义为reg型 wire[3:0] out; //测试输出信号定义为wire型 parameter DELY=100; count4 mycount(out,reset,clk); //调用测试对象 always #(DELY/2) clk = ~clk; //产生时钟波形 initial begin//激励信号定义 clk =0; reset=0; #DELY reset=1; #DELY reset=0; #(DELY*20) $finish; end //定义结果显示格式 initial $monitor($time,,,"clk=%d reset=%d out=%d", clk, reset,out); endmodule 【例3.5】“与-或-非”门电路 module AOI(A,B,C,D,F); //模块名为AOI(端口列表A,B,C,D,F) input A,B,C,D; //模块的输入端口为A,B,C,D output F; //模块的输出端口为F - 2 -

几种常见的调度自动化前置系统数据采集模式

几种常见的调度自动化前置系统数据采集模式 发表时间:2017-10-30T12:00:53.993Z 来源:《电力设备》2017年第18期作者:宋博言张炜琦王建树 [导读] 摘要:前置系统属于调度自动化系统的主要组成部分,在电力调度中扮演着重要的角色。本文简要阐述了调度自动化前置系统的构成及功能,列举了几种常见的调度自动化前置系统数据采集模式。希望能够为电力领域提供参考,提高数据采集效率的目的。 (国网河北省电力公司检修分公司河北石家庄 050000) 摘要:前置系统属于调度自动化系统的主要组成部分,在电力调度中扮演着重要的角色。本文简要阐述了调度自动化前置系统的构成及功能,列举了几种常见的调度自动化前置系统数据采集模式。希望能够为电力领域提供参考,提高数据采集效率的目的。 关键词:调度自动化;前置系统;数据采集 不同区域对电力系统供电量的要求不同,因此,电力领域需以用户的需求为基础,通过电力调度的方法,达到平衡用电负荷的目的。将调度自动化前置系统应用到电力调度的过程中,采集各区域用户的用电数据,是提高电力领域运行稳定性的基础。根据数据采集模式的不同,调度效果通常存在差异,因此,有必要对系统的数据采集模式加以研究。 一、调度自动化前置系统的构成及功能 调度自动化系统中,前置系统的功能在于收集电力用户用电所产生的实时数据,而数据采集功能需依靠硬件功能的支撑来实现。 调度自动化系统前置系统硬件主要包括通信扩展板以及解调器等。通信扩展板需属于系统前置机的主要组成部分,功能在于实现对信号接收以及发送过程的实时控制。通信扩展板的路数,需与串行口的个数相同。即,每一路扩展板,均需确保存在1个串行口与之连接。当数据接收完成后,串行口可将接收到的信息,传输给解调器,以使用电数据的收集过程最终得以实现。调度自动化系统前置系统的功能众多,主要体现在以下方面:(1)系统具有处理多种规约的信息的功能,因此能够与RTU实现信息交换。(2)系统能够将交换所得到的RTU信息,通过全网广播的途径,传输到全网范围内,实现信息共享。信息更新时间一般为5s,共享实时性较强。(3)系统管理方式分层管理为主,信息能够逐层发送,最终传输至一级调度部门。(4)系统具有遥控以及遥调的功能,能够向RTU发送指令,并在全网范围内建立统一的时钟,进一步提高信息采集的效率及实时性水平。(5)系统具有遥测值归零处理的功能,应用的灵活性较强。 二、常见的调度自动化前置系统数据采集模式 数据采集功能,属于前置系统的基础功能。常见的调度自动化前置系统数据采集模式,主要包括主备终端服务器值班模式、按口值班模式、分组设计模式以及分层控制模式4种,具体如下: (一)主备终端服务器值班 主备终端服务器值班模式下,前置机以双机配置为主。主前置机功能在于采集并传输信息、备用前置机的功能则以监控为主。该模式下,主备终端服务器一般呈相互对应的关系。两者的硬件之间相互连接,软件及硬件的构成,均较为简单。该数据采集模式的优势在于便利性强,但通常也存在灵活性差的特点,两大服务器的功能无法相互置换。当某一终端服务器出现故障时,数据采集便无法实现。 (二)按口值班 前置机的按口值班模式,属于调度自动化前置系统的主要数据采集模式之一。传统的数据采集模式下,各个数据采集设备需单独发挥各自的作用,以确保数据的采集以及传输过程能够有效实现。按口值班模式的出现,有效克服了传统数据采集模式的缺陷,要求加强对设备的监控,使设备能够同时发挥作用,以提高数据的采集效率。传统的终端服务器值班模式,以分组值班为主,值班效率较低。按口值班模式下,终端服务器均被规划到了具体的端口下,控制的系统性以及集成性有效提升,控制效率极大提高。 与主备终端服务器模式相同,按口值班模式下调度自动化前置系统前置机配置方法,同样以双机配置为主,“双机”分别指主机及备用机。视数据采集需求,可将系统通道设置为单通道或双通道两种形式。单通道即单独开放主机或备用机,此时,数据的采集、传输等,均需通过同一通道来实现,监控也仅需针对同一通道而进行即可。双通道状态下,两台机器需同时开放,此时,前置机需同时承担不同的功能,即:控制一台机器传输数据,同时监控另一台机器的运行状况。上述数据采集模式,解决了主备终端服务器模式存在的服务器功能固定的缺陷。但需注意的是,该模式下,负责收集并传输数据的通道,必须具有与RTU交换信号的功能。如两个通道均无法与RTU交换信号,则意味着通道的硬件或畅通性出现了问题,系统运行的稳定性及可靠性,必定会受到影响。 (三)分组设计 分组设计模式,要求将同一数据采集系统,分为不同的子系统。每个子系统均配备各自的主机,均具有RTU数据交换的功能,但仅能够交换部分数据。各个子系统之间无联系,功能的实现相互独立。数据采集子系统在获得相应数据之后,需将数据传输给主机。主机与主机之间相互联系,共同构成整体的数据采集系统。 采用分组设计模式实现数据采集,各子系统之间的功能独立性较强。当一个子系统发生故障时,其他系统仍可正常运行,数据采集的连续性及可靠性较强。但随着电网数据量的增加,数据采集对子系统功能、数量以及采集速度的要求也会不断提升,必须设计一种与现代化电网特点相适应的数据采集模式,才能够达到进一步提高数据采集效率的目的。 较主备终端服务器值班模式以及按口值班模式相比,分组设计模式的数据采集效率更高。但该模式并未具有广泛的适用性。应用时,需充分考虑自身条件,以确保所选择的数据采集模式,能够与电力系统的数据采集需求相符合。分组设计模式的适用范围如下:(1)数据采集规模较大的主站系统,采用统一的采集模式采集数据,主机所面临的压力较大,发生故障的几率较高,对系统稳定性的提升不利。可采用分组设计模式采集数据,以便解决由统一采集数据对主机运行稳定性所带来的影响。(2)可以以电力数据的来源为依据,通过分组设计模式采集电力数据。电力领域可将处于同一地区的电力数据,共同归纳到某一子系统的管辖范围内,提高用电数据采集的明确性,为电网调度过程提供保证。(3)以提高管理的便利性为目的,将不同的电力数据分为不同的组别,分别由不同的子系统管理。(4)将RTU信号划分为普通信号以及GPRS信号两种类型,分别有不同的子系统负责采集数据。 (四)分层控制 分层控制的模式,属于调度自动化前置系统数据采集的新型模式之一。该模式下,每一集控站,均具有独立的前置系统以及数据库。将分层控制模式应用到电力用户数据采集过程中,能够使数据采集的层次性得以提升。采用分层控制模式采集用电数据,安全性以及冗余度较强,每一集控站的功能对其他集控站均无影响,数据采集的效率一般较高。该数据采集模式同样存在一定的缺陷,主要体现在运行及