EDA技术及其应用(1)

第14卷第5期(2009)Vol.14No.5(2009)

EDA 技术及其应用

谢华燕

(兰州职业技术学院信息工程系,甘肃兰州

730070)

摘要:随着大规模集成电路技术和计算机技术的不断发展,电子技术得到了飞速发展,电子设计自动化(E -DA)技术,加速了现代高科技发展的进程.从微电子技术、微电脑技术到信息技术等领域,EDA 技术的含量正以惊人的速度上升,在电子系统设计上产生了具有里程碑意义的飞跃,为大规模可编程逻辑器件的应用奠定了基础.

关键词:EDA 技术;HDL 硬件描述语言;自顶向下设计方法;PLD 可编程逻辑器件中图分类号:TP3

文献标识码:A

文章编号:1008-9020(2009)05-063-03

收稿日期:2009-06-25

作者简介:谢华燕(1973—),女,甘肃兰州人,讲师.研究方向:电子计算机

.

电子设计的必由之路是数字化,在数字化的道路上,电子技术经历了一系列重大的变革.从应用小规模集成电路构成电路系统,到广泛应用微控制器或单片机,EDA 技术也随之全方位溶入电子技术领域.EDA 技术使一些技术瓶颈得以轻松突破,从而使产品的开发周期大为缩短、性能价格比大幅提高.E-DA 技术已经成为电子设计领域中极其重要的组成部分.

1.EDA 技术

EDA 是电子设计自动化(Electronic Design Au-tomation )的缩写,由于涉及面广,内容丰富,理解各异,所以目前尚无一个确切的定义.但从EDA 技术的几个主要方面的内容来看,可以理解为:EDA 技术是以大规模可编程逻辑器件为设计载体,以硬件描述语言HDL (Hardware Description Language )为系统逻辑描述的主要表达方式,以计算机、大规模可编程逻辑器件开发软件及实验开发系统为设计工具,通过有关开发软件,自动完成用软件方式设计电子系统到硬件系统的一门新技术.

2.EDA 技术的特征

2.1EDA 打破了软件与硬件间的壁垒,是一门综合性学科

EDA 技术在硬件实现方面融合了大规模集成电路制造技术,专用集成电路ASIC 测试和封装技术、FPGA/CPLD 编程下载技术、自动测试等技术.在计算机辅助工程方面融合了计算机辅助设计(CAD )、计算机辅助制造(CAM )、计算机辅助测试

(CAT

)、计算机辅助工程(CAE )技术以及多种计算机语言的设计概念.而在现代电子学方面则容纳了更多的内容,如电子线路设计理论、数字信号处理技术、数字系统建模和优化技术等.因此,EAD 技术为现代电子理论和设计表达及实现提供了可能性,设计者的工作仅限于利用软件方式完成对系统硬件功能的描述.在EDA 工具帮助下应用相应的FP-GA/CPLD 器件,就可以得到最后设计结果.尽管目标系统是硬件,但整个设计和修改过程如同完成软件设计一样方便而高效.不难理解,EDA 技术已不是某一学科的分支,或某种新的技能技术,它应该是一门综合性学科.

2.2大规模可编程逻辑器件

EDA 所依托的PLD 器件(Programmable Logic Device ,可编程逻辑器件)是一种可编程专用集成电路,由用户开发并决定其功能.而传统设计所用到的通用型集成电路功能是确定的,不可更改的.FPGA 和CPLD 是实现这一途径的主流器件,它们分别是现场可编程门阵列和复杂可编程逻辑器件的简称,两者的功能基本相同,只是实现原理略有不同,所以我们有时可以忽略这两者的区别,统称为可编程逻辑器件或CPLD/FPGA.PLD 是电子设计领域中最具活力和发展前途的一项技术,能完成任何数字器件的功能.PLD 如同一张白纸或一堆积木,工程师可以通过传统的原理图输入法,或是硬件描述语言自由设计一个数字系统,通过软件仿真,我们可以事先验证设计的正确性.在PCB 完成以后,还可以利用

63

第14卷第5期(2009)Vol.14No.5(2009)

谢华燕:EDA技术及其应用

PLD的在线修改能力,随时修改设计而不必改动硬

件电路.使用PLD开发数字电路,可以大大缩短设

计时间,减少PCB面积,提高系统的可靠性.

2.3基于VHDL的自顶向下设计方法

在电子设计领域,自顶向下的设计方法只有在

EDA技术得到快速发展和成熟应用的今天才成为

可能.自顶向下的设计方法,就是使用VHDL模型在

所有综合级别上对硬件设计进行说明、建模和仿真测试.主系统及子系统最初的功能要求体现为可被VHDL仿真程序验证的可执行程序.由于综合工具可以将高级别的模型转化为门级模型,所以整个设计过程基本是由计算机自动完成的.在这些过程中,由于设计的下一步是基于当前的设计,发现问题或做新的修改,即使从头开始设计,也不妨碍整体的设计效率.自顶而下的设计方法使系统分解为各个模块的集合之后,可以对设计的每个独立模块指派不同的工作小组.这些小组可以工作在不同地点,甚至可以分属不同单位,最后将不同的模块集成为最终的系统模型,对其进行综合测试和评价.与其它硬件描述语言相比,VHDL具有较强的行为仿真与综合建模功能,这种远离具体硬件,基本行为描述的硬件描述语言满足典型的自顶向下设计方法,顺应EDA 技术发展,解决了现代电子设计中出现的诸多问题.

3EDA在电子技术教学中的应用

几乎所有理工科特别是电子信息类高校都开设了EDA课程.EDA的精髓在于向学生灌输新的设计思路和设计理念,而不是仅仅介绍一种新器件,学习一种新的软件应用而已.

以比较器和D/A器件实现A/D转换功能电路设计为例,分析EDA设计方法

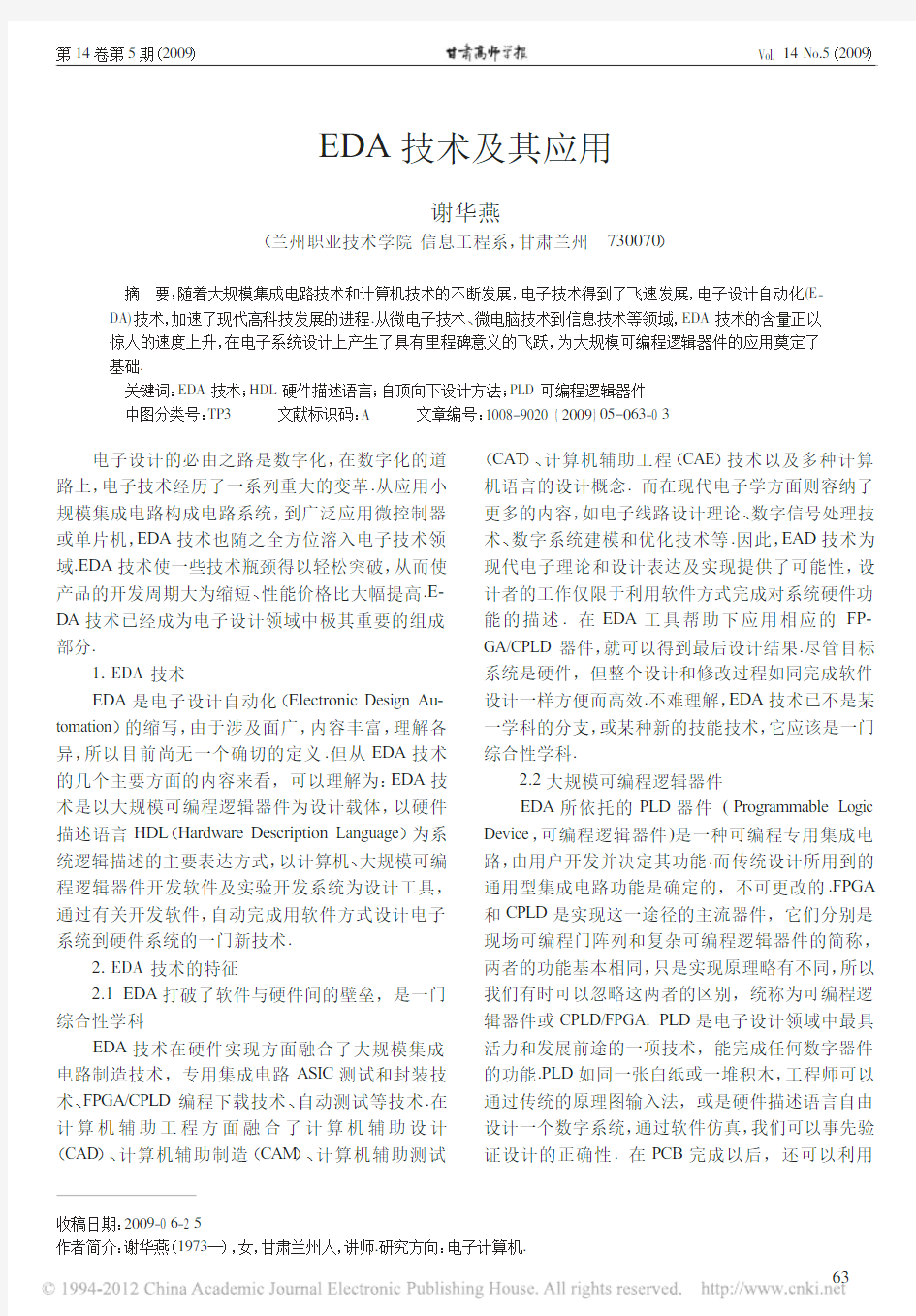

(1)画出电路框图,构造顶层设计模型.如图1所示是一个用比较器LM311和DAC0832构成的8位A/D转换器的电路框图.其工作原理是:当被测模拟信号电压vi接于LM311的“+”输入端时,由于FPGA产生自小到大的搜索数据加于DAC0832后,LM311的“-”端将得到一个比较电压vc.当vc

(2)结合模型结构,进行状态分析.首先锁定引脚,编译.实验电路中时钟CLK接clock();DD[7..0]分别接PIO31~PIO24;LM311比较信号接PIO37;显示数据DISPDATA[7..0]可以由数码8和7显示.向FPGA下载文件后,打开±12V电源;clock()接65536Hz.将FPGA的PIO37脚与LM311的输出端相接,0832的输出端与LM311的“3”脚相连,实验系统左下的输入口“AIN0”与LM311的“2”脚相连.因此被测信号可接于“AIN0”端,由于“AIN1”口与电位器相接,所以可以将“AIN1”接“AIN0”,“AIN0”就能获得电位器输出的作为被测信号的电压.

(3)根据设计要求,编制FPGA源程序代码.

LIBRARY LEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_USEIGNED.ALL;

ENTITY DAC IS

PORT(CLK:IN STD_LOGIC;

LM311:IN STD_LOGIC;

CLR:IN STD_LOGIC;

DD:OUTSTD_LOGIC_VECTOR(7DOWNTO0);

DISPDATA:OUTSTD_LOGIC_VECTOR(7DOWNTO0));

END

ARCHITECTURE DACC OF DAC IS

SIGNAL CQI:STD_LOGIC_VECTOR(7DOWNTO0);

BEGIN

DD<=CQI;

PROCESS(CLK,CLR,LM311)

BEGIN

IF CLR=’1’THEN CQI<=”00000000”;

ELSIF CLK’EVENT AND CLK=’1’THEN

IF LM311=’1’THEN CQI<=CQI+1;

ENDIF;

ENDIF;

END PROCESS;

DISPDATA<=CQI WHEN LM311=’0’ELSE“00000000”

END;

EDA平台的通用性与具体硬件结构无关,使得前期的设计容易应用于新的设计项目,强调将前一个VHDL模型重用的方法.如上述8位A/D转换器设计,通过修改源程序,可扩展为16位A/D、32位A/D转换器等,程序的编制根据用户自己的要求随8

被测模拟信号

VCC

2+

3-

1

LM311

CLR复位

PIO37

PIO31-PIO24

FPGA A/D转换

输出显示

比较信号

0832

图1比较器和D/A构成A/D电路框图

64

第14卷第5期(2009)Vol.14No.5(2009)

The technology of electronic design automation and its applications

XIE Hua-yan

(Department ofInformation Engineering,Lanzhou Vocation-TechnologyCollege,Lanzhou Gansu 730070)

Abstract:With the continuous progress of large scale integrated circuit technology and computer technology,the electronic technique develops rapidly.The technology of electronic design automation (EDA)accelerates the process of modern high-tech growing.The contents of EDA technology in domains such as microelectronics,microcomputer and information are increasing greatly,which ad -vance the design of electronic systems in a landmark way and lay the foundation for applications of the large scale programmable log -ic devices.This paper explains the meaning and characteristic of EDA technology and describes its applications.

Key words:technology of electronic design automation (EDA);hardware description language (HDL);top-down design approach;pro -grammable logic device (PLD)

责任编辑:

蒋德璋

时修改扩充,硬件电路和程序设计可同时进行,促进设计周期显著缩短.

将全新的设计思路和方法渗透到教学中,跟上电子科技发展步伐,密切结合实际需求,及时调整课程整体结构,进行全面深入改革,才能带给课程全新的面貌.从某种意义上来说,EDA 教学科研的情况,代表着一个学校电子类专业教学及科研水平的高低,而EDA 教学科研工作开展起来后,还会对微电子类、计算机类学科产生积极影响,从而带动高校相

应学科的同步发展.

参考文献:

[1]廖超平.EDA 技术VHDL 实用教程[M].北京:高等教育出版社,

2007.[2]路而红.电子设计自动化应用技术[M].北京:高等教育出版社,2006.

[3]潘松,黄继业.EDA 技术与VHDL (第2版)[M].北京:清华大学出版社,

2007.65

EDA技术实用教程-VHDL版课后答案

第一章 1-1 EDA技术与ASIC设计和FPGA开发有什么关系? P3~4 答:利用EDA技术进行电子系统设计的最后目标是完成专用集成电路ASIC的设计和实现;FPGA和CPLD是实现这一途径的主流器件。FPGA和CPLD通常也被称为可编程专用IC,或可编程ASIC。FPGA和CPLD的应用是EDA技术有机融合软硬件电子设计技术、SoC(片上系统)和ASIC设计,以及对自动设计与自动实现最典型的诠释。 1-2与软件描述语言相比,VHDL有什么特点? P6 答:编译器将软件程序翻译成基于某种特定CPU的机器代码,这种代码仅限于这种CPU而不能移植,并且机器代码不代表硬件结构,更不能改变CPU的硬件结构,只能被动地为其特定的硬件电路结构所利用。综合器将VHDL 程序转化的目标是底层的电路结构网表文件,这种满足VHDL设计程序功能描述的电路结构,不依赖于任何特定硬件环境;具有相对独立性。综合器在将VHDL(硬件描述语言)表达的电路功能转化成具体的电路结构网表过程中,具有明显的能动性和创造性,它不是机械的一一对应式的“翻译”,而是根据设计库、工艺库以及预先设置的各类约束条件,选择最优的方式完成电路结构的设计。 l-3什么是综合?有哪些类型?综合在电子设计自动化中的地位是什么? P5 什么是综合? 答:在电子设计领域中综合的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。 有哪些类型? 答:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合。(2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。(3)从RTL级表示转换到逻辑门(包括触发器)的表示,即逻辑综合。(4)从逻辑门表示转换到版图表示(ASIC设计),或转换到FPGA的配置网表文件,可称为版图综合或结构综合。 综合在电子设计自动化中的地位是什么? 答:是核心地位(见图1-3)。综合器具有更复杂的工作环境,综合器在接受VHDL程序并准备对其综合前,必须获得与最终实现设计电路硬件特征相关的工艺库信息,以及获得优化综合的诸多约束条件信息;根据工艺库和约束条件信息,将VHDL程序转化成电路实现的相关信息。 1-4在EDA技术中,自顶向下的设计方法的重要意义是什么? P7~10 答:在EDA技术应用中,自顶向下的设计方法,就是在整个设计流程中各设计环节逐步求精的过程。 1-5 IP在EDA技术的应用和发展中的意义是什么? P11~12 答:IP核具有规范的接口协议,良好的可移植与可测试性,为系统开发提供了可靠的保证。 第二章 2-1 叙述EDA的FPGA/CPLD设计流程。P13~16 答:1.设计输入(原理图/HDL文本编辑);2.综合;3.适配;4.时序仿真与功能仿真;5.编程下载;6.硬件测试。 2-2 IP是什么?IP与EDA技术的关系是什么? P24~26 IP是什么? 答:IP是知识产权核或知识产权模块,用于ASIC或FPGA/CPLD中的预先设计好的电路功能模块。 IP与EDA技术的关系是什么?答:IP在EDA技术开发中具有十分重要的地位;与EDA技术的关系分有软IP、固IP、硬IP:软IP是用VHDL等硬件描述语言描述的功能块,并不涉及用什么具体电路元件实现这些功能;软IP 通常是以硬件描述语言HDL源文件的形式出现。固IP是完成了综合的功能块,具有较大的设计深度,以网表文件的形式提交客户使用。硬IP提供设计的最终阶段产品:掩模。 2-3 叙述ASIC的设计方法。P18~19 答:ASIC设计方法,按版图结构及制造方法分有半定制(Semi-custom)和全定制(Full-custom)两种实现方法。 全定制方法是一种基于晶体管级的,手工设计版图的制造方法。 半定制法是一种约束性设计方式,约束的目的是简化设计,缩短设计周期,降低设计成本,提高设计正确率。半定制法按逻辑实现的方式不同,可再分为门阵列法、标准单元法和可编程逻辑器件法。 2-4 FPGA/CPLD在ASIC设计中有什么用途? P16,18 答:FPGA/CPLD在ASIC设计中,属于可编程ASIC的逻辑器件;使设计效率大为提高,上市的时间大为缩短。 2-5 简述在基于FPGA/CPLD的EDA设计流程中所涉及的EDA工具,及其在整个流程中的作用。 P19~23答:基于FPGA/CPLD的EDA设计流程中所涉及的EDA工具有:设计输入编辑器(作用:接受不同的设计输

《EDA技术及应用》全套教学教案

单元一教学设计 教学内容: 单元一EDA技术 学习任务1 EDA技术 一、认识课程 二、认识EDA技术 三、认识EDA技术的基本特征 学习任务2 可编程逻辑器件芯片 一、认识可编程逻辑器件 二、CPLD基本结构 三、FPGA基本结构 四、Altera公司的可编程逻辑器件汇报总结 评价与考核

教学设计与建议 教学设计:通过学习和查阅资料了解EDA技术,了解EDA技术的基本特征,并熟悉可编程逻辑器件的种类。了解CPLD和FPGA基本结构,熟悉 Altera公司的可编程逻辑器件。 教学建议:建议学生查找EDA技术发展与可编程逻辑器件应用相关资料,进行总结制作PPT,并进行汇报。 知识目标: 1.了解EDA技术 2.了解EDA技术的基本特征 3.了解可编程逻辑器件的种类 4.了解CPLD基本结构 5.了解FPGA基本结构 6.了解Altera公司的可编程逻辑器件 教学重点及难点: 教学重点:可编程逻辑器件种类 教学难点:熟悉Altera公司的可编程逻辑器件 教学载体与资源: 教学资源:教材、PPT、实训室、多媒体设备。 教学方法建议: 讲授与讨论相结合,查阅资料总结汇报。 教学过程: 1.下达任务和要求 2. 教师带领学生共同解析任务 3.学生展开讨论

4.学生查阅资料 5. 总结汇报 考核评价: 1.根据知识掌握情况评价 2.根据资料查找能力和小组汇报情况评价 教学板书: 任务1:EDA技术 认识课程 1.EDA技术是什么? 2.为什么学习EDA技术? 3.EDA技术学什么? 4.EDA技术怎么学? 相关知识 1.认识EDA技术 EDA(Electronic Design Automation,电子设计自动化)技术是帮助电子设计工程师在计算机上完成电路的功能设计、逻辑设计、性能分析、时序测试直至PCB(印制电路板)的自动设计等。 2.认识EDA技术的基本特征 (1)“自顶向下”设计方法 (2)硬件描述语言 (3)逻辑综合和优化 (4)开放性和标准化 (5)库的引入

eda技术的应用及发展

EDA技术的应用 摘要:随着科技的不断进步与发展,EDA (Electronic Design Automation)即电子设计自动化技术与我们的生活的交集越来越密切。随着微电子技术和计算机技术的不断发展,在涉及通信、国防、航天、工业自动化、仪器仪表等领域工作中,EDA技术的含量以惊人的速度上升,从而使它成为当今电子技术发展的前沿之一。本文简单的介绍EDA技术的发展应用及在未来的发展。 关键字:EDA,技术,应用, Abstract:With the advancement and development of technology,( Electronic Design Automation ) electronic design automation technology and our life is more and more close intersection. With microelectronic technology and the continuous development of computer technology, communication, national defense, involved in aerospace, industrial automation, instrumentation and other areas of work, EDA technical content is increasing at an alarming speed, so as to make it become the forefront of the development of electronic technology. This paper briefly introduced the development of EDA technology, application, and the future. Key world: EDA ,development , 一、前言 1·随着微电子技术和计算机技术的不断发展,在涉及通信、国防、航天、工业自动化、仪器仪表等领域工作中,EDA技术的含量以惊人的速度上升,从而使它成为当今电子技术发展的前沿之一。现代电子产品的性能提高、集成度和精密度不断的增加,电子产品更新换代的节奏越来越快。采用传统的电子设计方法设计电路越来越困难,EDA 技术提高了电路的设计效率和可靠性,减少了劳动强度,给电子系统设计带来了革命性的变化。 2·EDA:EDA是电子设计自动化(Electronic Design Automation)缩写,是90年代初从CAD(计算机辅助设计)、CAM(计算机辅助制造)、CAT(计算机辅助测试)和CAE(计算机辅助工程)的概念发展而来的。EDA技术是以计算机为工具,根据硬件描述语言HDL(Hardware Description language)完成的设计

EDA技术应用及发展前景介绍

EDA技术应用及发展前景介绍 EDA技术应用及发展前景介绍 电子设计技术的核心就是EDA技术,EDA是指以计算机为工作平台,融合应用电子技术、计算机技术、智能化技术最新成果而研制成的电子CAD通用软件包,主要能辅助进行三方面的设计工作,即IC设计、电子电路设计和PCB设计。EDA技术已有30年的发展历程,大致可分为三个阶段。70年代为计算机辅助设计(CAD)阶段,人们开始用计算机辅助进行IC版图编辑、PCB布局布线,取代了手工操作。80年代为计算机辅助工程(CAE)阶段。与CAD相比,CAE除了有纯粹的图形绘制功能外,又增加了电路功能设计和结构设计,并且通过电气连接网络表将两者结合在一起,实现了工程设计。CAE的主要功能是:原理图输入,逻辑仿真,电路分析,自动布局布线,PCB后分析。90年代为电子系统设计自动化(EDA)阶段。 一、EDA技术的基本特征 EDA代表了当今电子设计技术的最新发展方向,它的基本特征是:设计人员按照“自顶向下”的设计方法,对整个系统进行方案设计和功能划分,系统的关键电路用一片或几片专用集成电路(ASIC)实现,然后采用硬件描述语言(HDL)完成系统行为级设计,最后通过综合器和适配器生成最终的目标器件,这样的设计方法被称为高层次的电子设计方法。下面介绍与EDA基本特征有关的几个概念。 1.“自顶向下”的设计方法10年前,电子设计的基本思路还是选用标准集成电路“自底向上”地构造出一个新的系统,这样的设计方法就如同一砖一瓦建造金字塔,不仅效率低、成本高而且容易出错。 高层次设计是一种“自顶向下”的全新设计方法,这种设计方法首先从系统设计入手,在顶层进行功能方框图的划分和结构设计。在方框图一级进行仿真、纠错,并用硬件描述语言对高层次的系统行为进行描述,在系统一级进行验证。然后,用综合优化工具生成具体门电路的网络表,其对应的物理实现级可以是印刷电路板或专用集成电路。由于设计的主要仿真和调试过程是在高层次上完成的,这既有利于早期发现结构设计上的错误,避免设计工作的浪费,又减少了逻辑功能仿真的工作量,提高了设计的一次成功率。 2.ASIC设计现代电子产品的复杂度日益提高,一个电子系统可能由数万个中小规模集成电路构成,这就带来了体积大、功耗大、可靠性差的问题。解决这一问题的有效方法就是采用ASIC芯片进行设计。ASIC按照设计方法的不同可分为全定制ASIC、半定制ASIC和可编程ASIC(也称为可编程逻辑器件)。 设计全定制ASIC芯片时,设计师要定义芯片上所有晶体管的几何图形和工艺规则,最后将设计结果交由IC厂家去进行掩模制造,做出产品。这种设计方法的优点是芯片可以获得最优的性能,即面积利用率高、速度快、功耗低,而缺点是开发周期长,费用高,只适合

EDA技术及应用【朱正伟】第五章课后习题部分答案

1.试说明实体端口模式BUFFER和INOUT的不同之处? 答:BUFFER端口:缓冲模式,具有读功能的输出模式,即信号输出到实体外部,但同时也在内部反馈使用,不允许作为双向端口使用。而INOUT端口:双向模式,即信号的流通是双向的,既可以对此端口赋值,也可以通过此端口读入数据。 2.VHDL的数据对象有哪几种?它们之间有什么不同? 答:VHDL的数据对象有三种:信号、变量、常量。它们之间的的区别如下: 信号赋值至少有δ延时,而变量和常量没有;信号除当前值外,有许多相关信息,变量只有当前值,常量的值在设计实体中始终不变;进程对信号敏感而对变量及常量不敏感;信号可以是多个进程的全局信号,变量只在定义它们的顺序域可见,而常量的使用范围取决于它被定义的位置;信号是硬件连线的抽象描述信号赋值,赋值符号 <= 而变量和常量的赋值符号 :=。 3.说明下列各定义的意义: SIGNAL a , b , c : BIT : =’0’; CONSTANT TIME1 , TIME2 : TIME : 20ns ; VARIABLE x , y , z : STD_LOGIC :=’x’; 答:○1定义3个位数据类型的信号a、b、c,它们取值为0; ○2定义2个时间数据类型的常量TIME1、TIME2,它们值为20ns; ○3定义3个标准逻辑位 STD_LOGIC数据类型的变量x、y、z,它们的值是强未知的。 4.什么是重载函数?重载运算符有何用处?如何调用重载运算符函数? 答:为了方便各种不同数据类型间的运算,VHDL允许用户对原有的基本操作符重新定义,赋予新的含义和功能,从而建立一种新的操作符,这就是重载操作符,定义这种操作符的函数成为重载函数。重载运算符的作用是为了方便各种不同的数据类型间的运算。要调用重载运算符函数,先要在程序包中进行函数体的定义,调用的格式如下:

EDA技术及应用实训报告

桂林电子科技大学信息科技学院《EDA技术及应用》实训报告 学号1252100301 姓名 指导教师:覃琴 2014年4 月29 日

实训题目:数字日历电路 1 系统设计 1.1 设计要求 1.1.1 设计任务 (1)用Verilog HDL语言设计出能够在EDA实训仪的I/O设备和PLD芯片实现的数字日历。 (2)数字日历能够显示年、月、日、时、分和秒。 (3)用EDA实训仪上的8只八段数码管分两屏分别显示年、月、日和时、分、秒,即在一定时间段内显示年、月、日(如20140101),然后在另一时间段内显示时、分、秒(如010101099),两个时间段能自动倒换。 (4)数字日历具有复位和校准年、月、日、时、分、秒的按钮,但校年和校时同用一个按钮,即在显示年、月、日时用此按钮校年,在显示时、分、秒时则用此按钮校时。 (5)体现创新部分 1.1.2 性能指标要求 1)数字电路能够在一定的时间内显示切换的功能,并且能手动校准年月日和时分秒 2)具有复位和进位的功能 3)能起到提示的作用,如闹钟或亮彩灯等。 1.2 设计思路及设计框图 1.2.1设计思路 如图1.2.2所示 1) EDA实训箱上的功能有限,可以用到的有8支数码管和12个lED灯。年、月、日和时、分、秒可以通过数码管显示,年月日和时分秒的切换可以通过拨动开关控制,校正可以通过按键实现。 2)输入的秒脉冲由DEA实训仪上的20MHZ晶振经过分频得到,秒脉冲经过60分频后产生1分钟脉冲信号,在经过60分频后产生1小时的脉冲信号,最后进行24分频,得到1天的脉冲送24进制的 cout输出。在将两个60分频和一个24分频的输出送到送到数码管的译码器输入端,得到24小时的计时显示结果。由此得到数字日历的计时器模块。

《EDA技术与应用》A卷及答案

汕头大学成人教育学院二0一0年春季学期期末考试试卷 试卷编号:A卷闭卷课程名称:《EDA技术与应用》班级专业: 姓名:学号: 一、填空题(20分,每小题1分) 1.VHDL的中文名称是__超高速集成电路硬件描述语言_____________。 2.用EDA技术进行电子系统设计的目标是最终完成 asic________ 的设计与实现。 3.可编程器件分为 fpga__ 和 _cpld______ 。 4.标准逻辑位数据类型常用的数值有 _1__ 、 __0_ 、 _z__ 等。 5.在VHDL语言中可以使用的数据类型有: _位____ 、 __标准逻辑位__________、 ___布尔_____。 6.完整的条件语句将产生 _组合_______ 电路,不完整的条件语句将产生 __时序______ 电路。 7.信号的赋值符号为 <= ___ 变量的赋值符号为 =___ 。 8.随着EDA技术的不断完善与成熟, ___自顶向下______的设计方法更多的被应用于VHDL 设计当中。 9.EDA设计过程中的仿真有三种,它们是___行为_____ 仿真、 _逻辑______ 仿真和 __ 时序____ 仿真。 10.目前国际上较大的PLD器件制造公司有 __altera________ 和 ___xilinx______ 公 司。 二、简答题(20分,每小题4分) 1、与HDL文本输入法相比较,原理图输入法有何优点?

2、写出结构体的一般语言格式并说明其作用 3、信号和变量的区别? 4、写出PROCESS语句结构的一般表达格式。 5、写出五种以上的VHDL的预定义数据类型。 三、程序注解(20分,每空1分) library ieee; __________ use ieee.std_logic_1164.all; _____________ ENTITY aa1 is ________ __ port(a,b,s:in bit; _______________________________

EDA课后问题详解(适用于朱正伟《EDA技术及应用》)

1.1、设计集成计数器74161,设计要求如下: 4-BIT BINARY UP COUNTER WITH SYNCHRONOUS LOAD AND ASYNCHRONOUS CLEAR NOTE INPUTS: CLK LDN CLRN D C B A OUTPUTS:QD QC QB QA RCO *RCO = QD & QC & QB & QA LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY CNT4 IS PORT( CLK,LDN,CLRN : IN STD_LOGIC; D,C,B,A : IN STD_LOGIC; CARRY : OUT STD_LOGIC; QD,QC,QB,QA : OUT STD_LOGIC ); END; ARCHITECTURE A OF CNT4 IS SIGNAL DATA_IN: STD_LOGIC_VECTOR(3 DOWNTO 0); BEGIN DATA_IN<=D&C&B&A; PROCESS(DATA_IN,CLK,LDN,CLRN) V ARIABLE CNT:STD_LOGIC_VECTOR(3 DOWNTO 0); BEGIN IF CLRN='0' THEN CNT:=(OTHERS=>'0'); ELSIF CLK'EVENT AND CLK='1' THEN IF LDN='0' THEN CNT:=DATA_IN; ELSE CNT:=CNT+1; END IF; END IF; CASE CNT IS WHEN "1111"=> CARRY<='1'; WHEN OTHERS=> CARRY<='0'; END CASE; QA<=CNT(0); QB<=CNT(1); QC<=CNT(2); QD<=CNT(3); END PROCESS; END A; 1.2、设计一个通用双向数据缓冲器,要求缓冲器的输入和输出端口的位数可以由参数决定。 设计要求:N BIT数据输入端口A,B。工作使能端口EN=0时双

EDA技术的概念

EDA技术的概念 随着集成电路规模的扩大、半导体技术的发展,电子设计自动 化的重要性急剧增加。下面是的关于EDA技术的概念,欢迎大家参考! EDA技术的概念及范畴 EDA技术是在电子CAD技术基础上发展起来的计算机软件系统,是指以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动设计。 利用EDA工具,电子设计师可以从概念、算法、协议等开始设 计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC版图或PCB版图的整个过程在计算机 上自动处理完成。 现在对EDA的概念或范畴用得很宽。包括在机械、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域,都有EDA的应用。目前EDA技术已在各大公司、企事业单位和科研教学部门广泛使用。例如在飞机制造过程中,从设计、性能测试及特性分析直到飞行模拟,都可能涉及到EDA技术。本文所指的EDA技术,主要针对电子电路设计、PCB设计和IC设计。EDA设计可分为系统级、电路级和物理实现级。 EDA常用软件 EDA工具层出不穷,目前进入我国并具有广泛影响的EDA软件有:EWB、PSPICE、OrCAD、PCAD、Protel、Viewlogic、Mentor、Graphics、Synopsys、LSIlogic、Cadence、MicroSim等等。这些工具都有较强

的功能,一般可用于几个方面,例如很多软件都可以进行电路设计与仿真,同时以可以进行PCB自动布局布线,可输出多种网表文件与第三方软件接口。下面按主要功能或主要应用场合,分为电路设计与仿真工具、PCB设计软件、IC设计软件、PLD设计工具及其它EDA软件,进行简单介绍。 1、电子电路设计与仿真工具 电子电路设计与仿真工具包括 SPICE/PSPICE;EWB;Matlab;SystemView;MMICAD等。下面简单介绍前三个软件。 (1)SPICE(SimulationProgramwithIntegratedCircuit Emphasis)是由美国加州大学推出的电路分析仿真软件,是20世纪80年代世界上应用最广的电路设计软件,1998年被定为美国国家标准。1984年,美国MicroSim公司推出了基于SPICE的微机版PSPICE(Personal—SPICE)。现在用得较多的是PSPICE6.2,可以说在同类产品中,它是功能最为强大的模拟和数字电路混合仿真EDA软件,在国内普遍使用。最新推出了PSPICE9.1版本。它可以进行各种各样的电路仿真、激励建立、温度与噪声分析、模拟控制、波形输出、数据输出、并在同一窗口内同时显示模拟与数字的仿真结果。无论对哪种器件哪些电路进行仿真,都可以得到精确的仿真结果,并可以自行建立元器件及元器件库。 (2)EWB(ElectronicWorkbench)软件是InteractiveImageTechnologiesLtd在20世纪90年代初推出的电路

EDA技术实用教程课后习题答案

第一章 1-1 EDA 技术与 ASIC 设计和 FPGA 开发有什么关系? 答:利用 EDA 技术进行电子系统设计的最后目标是完成专用集成电路 ASIC 的设计和实现;FPGA 和 CPLD 是实现 这一途径的主流器件。FPGA 和 CPLD 通常也被称为可编程专用 IC,或可编程 ASIC。FPGA 和 CPLD 的应用是 EDA 技术 有机融合软硬件电子设计技术、SoC(片上系统)和 ASIC 设计,以及对自动设计与自动实现最典型的诠释。 1-2 与软件描述语言相比,VHDL 有什么特点? P6 答:编译器将软件程序翻译成基于某种特定 CPU 的机器代码,这种代码仅限于这种 CPU 而不能移植,并且机器 代码不代表硬件结构,更不能改变 CPU 的硬件结构,只能被动地为其特定的硬件电路结构所利用。综合器将 VHDL 程序转化的目标是底层的电路结构网表文件,这种满足 VHDL 设计程序功能描述的电路结构,不依赖于任何特定硬 件环境;具有相对独立性。综合器在将 VHDL(硬件描述语言)表达的电路功能转化成具体的电路结构网表过程中,具 有明显的能动性和创造性,它不是机械的一一对应式的“翻译”,而是根据设计库、工艺库以及预先设置的各类约 束条件,选择最优的方式完成电路结构的设计。 l-3 什么是综合?有哪些类型?综合在电子设计自动化中的地位是什么?什么是综合? 答:在电子设计领域中综合的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层 次的便于具体实现的模块组合装配的过程。 有哪些类型? 答:(1)从自然语言转换到 VHDL 语言算法表示,即自然语言综合。(2)从算法表示转换到寄存器 传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。(3)从 RTL 级表示转换到逻 辑门(包括触发器)的表示,即逻辑综合。(4)从逻辑门表示转换到版图表示(ASIC 设计),或转换到 FPGA 的配置网表 文件,可称为版图综合或结构综合。 综合在电子设计自动化中的地位是什么? 答:是核心地位(见图1-3)。综合器具有更复杂的工作环境,综合器 在接受 VHDL 程序并准备对其综合前,必须获得与最终实现设计电路硬件特征相关的工艺库信息,以及获得优化综 合的诸多约束条件信息;根据工艺库和约束条件信息,将 VHDL 程序转化成电路实现的相关信息。 1-4 在 EDA 技术中,自顶向下的设计方法的重要意义是什么? P7~10答:在 EDA 技术应用中,自顶向下的设计方法,就是在整个设计流程中各设计环节逐步求精的过程。 1-5 IP 在 EDA 技术的应用和发展中的意义是什么? P11~12 答:IP 核具有规范的接口协议,良好的可移植与可测试性,为系统开发提供了可靠的保证。 第二章 2-1 叙述 EDA 的 FPGA/CPLD 设计流程。 P13~16 答:1.设计输入(原理图/HDL 文本编辑);2.综合;3.适配;4.时序仿真与功能仿真;5.编程下载;6.硬件测试。 2-2 IP 是什么?IP 与 EDA 技术的关系是什么? P24~26 IP 是什么? 答:IP 是知识产权核或知识产权模块,用于 ASIC 或FPGA/CPLD 中的预先设计好的电路功能模块。 IP 与 EDA 技术的关系是什么? 答:IP 在 EDA 技术开发中具有十分重要的地位;与 EDA 技术的关系分有软 IP、 固 IP、硬 IP:软 IP 是用 VHDL 等硬件描述语言描述的功能块,并不涉及用什么具体电路元件实现这些功能;软 IP 通常是以硬件描述语言 HDL 源文件的形式出现。固 IP 是完成了综合的功能块,具有较大的设计深度,以网表文件 的形式提交客户使用。硬 IP 提供设计的最终阶段产品:掩模。 2-3 叙述 ASIC 的设计方法。 P18~19 答:ASIC 设计方法,按版图结构及制造方法分有半定制(Semi-custom)和全定制(Full-custom)两种实现方法。 全定制方法是一种基于晶体管级的,手工设计版图的制造方法。 半定制法是一种约束性设计方式,约束的目的是简化设计,缩短设计周期,降低设计成本,提高设计正确率。 半定制法按逻辑实现的方式不同,可再分为门阵列法、标准单元法和可编程逻辑器件法。 2-4 FPGA/CPLD 在 ASIC 设计中有什么用途? P16,18 答:FPGA/CPLD 在 ASIC 设计中,属于可编程 ASIC 的逻辑器件;使设计效率大为提高,上市的时间大为缩短。 2-5 简述在基于 FPGA/CPLD 的 EDA 设计流程中所涉及的 EDA 工具,及其在整个流程中的作用。 P19~23 答:基于 FPGA/CPLD 的 EDA 设计流程中所涉及的 EDA 工具有:设计输入编辑器(作用:接受不同的设计输 入表达方式,如原理图输入方式、状态图输入方式、波形输入方式以及HDL 的文本输入方式。);HDL 综合器(作用: HDL 综合器根据工艺库和约束条件信息,将设计输入编辑器提供的信息转化为目标器件硬件结构细节的信息,并在 数字电路设计技术、化简优化算法以及计算机软件等复杂结体进行优化处理);仿真器(作用:行为模型的表达、 电子系统的建模、逻辑电路的验证及门级系统的测试);适配器(作用:完成目标系统在器件上的布局和布线);下 载器(作用:把设计结果信息下载到对应的实际器件,实现硬件设计)。 第三章 3-1 OLMC(输出逻辑宏单元)有何功能?说明 GAL 是怎样实现可编程组合电路与时序电路的。 P34~36 OLMC 有何功能? 答:OLMC 单元设有多种组态,可配置成专用组合输出、专用输入、组合输出双向口、寄存器 输出、寄存器输出双向口等。 说明 GAL 是怎样实现可编程组合电路与时序电路的? 答:GAL(通用阵列逻辑器件)是通过对其中的 OLMC (输出逻辑宏单元)的编程和三种模式配置(寄存器模式、复合模式、简单模式),实现组合电路与时序电路设计 的。 3-2 什么是基于乘积项的可编程逻辑结构? P33~34,40 答:GAL、CPLD 之类都是基于乘积项的可编程结构;即包含有可编程与阵列和固定的或阵列的 PAL(可编程阵 列逻辑)器件构成。 3-3 什么是基于查找表的可编程逻辑结构? P40~41

《EDA技术及应用》朱正伟-三,四,五章部分课后题答案

第三章 3-5设计一个4选1多路选择器,当选择输入信号分别取“00”、“01”、“10”和“11”时,输出信号分别与一路输入信号相连。 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY MAX4_1 IS PORT(A,B,C,D,S1,S2 : IN STD_LOGIC; Y : OUT STD_LOGIC); END ENTITY MAX4_1; ARCHITECTURE HF1 OF MAX4_1 IS SIGNAL SS : STD_LOGIC_VECTOR (0 TO 1); BEGIN SS<=S2&S1; PROCESS(SS) BEGIN CASE SS IS WHEN "00" => Y<=A; WHEN "01" => Y<=B; WHEN "10" => Y<=C; WHEN "11" => Y<=D; WHEN OTHERS => NULL; END CASE; END PROCESS; END HF1; 3-6设计一个7人表决电路,参加表决者7人,同意为1,不同意为0,同意者过半则表决通过,绿指示灯亮;表决不通过则红指示灯亮。设计思路:根据7人表决电路设计要求,7人中至少有4个通过才可以表决通过,故可以在程序中设置一个变量TEMP,使其在表决电路中遇1则加1,遇0则加0(设计中1表示通过,0表示不通过)。当TEMP>=4时,表示表决通过,当TEMP<4时表决不通过。 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY VOTE7 IS PORT (MEN:IN STD_LOGIC_VECTOR(6 DOWNTO 0); OUTPUT: OUT BIT); END VOTE7; ARCHITECTURE BEHAVE OF VOTE7 IS BEGIN PROCESS(MEN) V ARIABLE TEMP: INTEGER RANGE 0 TO 7; BEGIN TEMP:=0; FOR I IN 0 TO 6 LOOP IF(MEN(I)='1')THEN TEMP:=TEMP+1;

EDA技术的发展与应用

目录 1 引言 (2) 1.1 对EDA的简述 (2) 1.2 对Multisim 10软件的简述 (2) 2 单管共射放大电路的静态工作点 (3) 2.1 静态工作点( Q 点)的设置 (3) 2.1.1 创建单管共射电路 (3) 2.1.2 对静态工作点的分析 (3) 2.2 温度对静态工作点( Q 点) 的影响 (5) 3 单管共射放大电路的动态指标 (5) 3.1 电压增益 (5) 3.1.1 计算电压增益 (5) 3.1.2 对电压增益的分析 (5) 3.2 输入电阻 (6) 3.3 输出电阻 (6) 4 体会 (8) 4.1 对本文的分析 (8) 4.2 对本文的体会 (9) 参考文献 (10)

Multisim 10 在单管共射放大电路中的应用 罗其会 (北京石油化工学院信息学院计算机科学与技术大兴区北京 102607)摘要利用Multisim 10 仿真软件对单管共射放大电路进行了计算机辅助教学。采用直流工作点分析了电路静态工作点的设置。利用温度扫描和参数扫描分析了温度对静态工作点以及电路参数对输出波形的影响。对电压增益、输入电阻和输出电阻的仿真测试结果和理论计算基本吻合。研究表明,利用Multisim 10 强大的分析功能对电子电路进行计算机仿,可以提高教学质量和教学效果。 关键字Multisim 10; 电路仿真; 静态工作点; 动态参数 Application of Multisim 10 in Single Transistor Amplifier Luoqihui (Beijing oil institute of chemical information institute of computer science and technology Daxing Beijing 102607) Abstract Multisim 10 simulation software was used for computer aided teaching. The quiescent operating point w as set by using DC operating point. The influence of temperature on quiescent operating point and circuit parameter on output voltage waveform were analyzed by using temperature scanning and parameter scanning. The simulation test of voltage gain, input resistance and output resistance coincide with theoretical calculation basically. The results show that using the powerful analysis capability of Multisim 10, the computer simulation of electronic circuits can enhance the teaching quality and teaching effect. Keywords Multisim 10; circuit simulation; quiescent operating point; dynamic par ammeters 1引言 1.1 对EDA的简述 在电子技术的发展历程中, 随着计算机辅助技术的应用和普及, 以及电子产品向数字化、集成化、微型化和低功耗方向的发展, EDA ( Elect ronic Design Automat ion) 技术逐渐产生并日趋完善。电子、电气、信息类专业的学生可以应用EDA 技术进行电子电路的设计和测试。EDA 具有效率高, 周期短, 应用范围广的优点,已成为当今电子设计的主流手段和技术潮流。 1.2 对Multisim 10软件的简述 在众多的电路仿真软件中, Multisim 以其界面友好, 功能强大和容易使用而倍受高校电类专业师生和工程技术人员的青睐。Multisim 10 是美国国家仪器公司N I( National Instruments) 最新推出的Multisim 版本, 集电路设计和功能测试于一件, 为设计者提供 了一个功能强大,仪器齐全的虚拟电子工作平台[ 1-3]。设计者可以利用大量的虚拟电子元器

eda技术及应用第三版课后答案谭会生.doc

eda 技术及应用第三版课后答案谭会生 【篇一:《eda 技术》课程大纲】 >一、课程概述 1.课程描述 《eda 技术》是通信工程专业的一门重要的集中实践课,是通信工程专业学生所必须具备的现代电子设计技术技能知识。eda 是电子技术的发展方向,也是电子技术教学中必不可少的内容。本课程主要 介绍可编程逻辑器件在电子电路设计及实现上的应用,介绍电路原 理图和pcb 图的设计技术。开设该课程,就是要让学生了解大规模 专用集成电路fpga 和cpld 的结构,熟悉一种以上的硬件描述语言, 掌握一种以上的开发工具的使用等,掌握电路原理图和pcb 图的现代设计技术与方法,从而提高学生应用计算机对电子电路和高速智 能化系统进行分析与设计的能力。 2.设计思路 本课程坚持“以学生为中心”的原则,以项目任务驱动的方式,采取 理论知识与案例相结合的方式授课,提高学生的学习主动性。通过 必要的理论知识讲授、大量的实践训练和案例分析,培养学生的动 手设计和实践能力,掌握eda 开发的整个流程和基本技巧。 课程采用演示讲授和实践相结合,边讲边练的方法,让学生切身体 会并掌握eda 开发产品的流程和方法。 本课程集中 2 周时间开设,注重实践性,边讲边练,让学生切身体 会并掌握eda 开发技术。 3.实践要求 (1)纪律和安全要求 ①不得将食物带入实验室,每次实训后请将使用后的废弃物带走。 违反者每次扣罚平时分 2 分。 ②实训期间不得做与实训无关的其他事情,不得大声喧哗或做其他 影响实训正常进行的事宜。违反者每次扣罚平时分 2 分。 ③实训期间,若学生有事不能正常参加实训,须提前以书面形式请 假,并按指导教师的安排补做实训。未经指导教师许可,学生不得 任意调换实训时间和实训地点。违反者每次扣罚平时分 4 分。 ④学生不得以任何理由替代他人进行实训,违者直接取消实训成绩。 ⑤学生除操作自己所分配的计算机外,不得操作实验室内其他任何 设备。违者每次扣罚平时分 2 分。(2)业务要求

EDA技术与应用

EDA技术与应用 一、EDA简介 1.1 EDA概念 EDA(Electronic Design Automation )即电子设计自动化,是以微电子技术为物理层面,现代电子设计为灵魂,计算机软件技术为手段,最终形成集成电子系统或专用集成电路芯片ASIC(Application Specific Integrated Circuit)为目的的一门新兴技术。 现代电子设计技术的核心是EDA技术。EDA技术就是依靠功能强大的电子计算机,在EDA工具软件平台上,对以硬件描述语言(如VHDL)为系统逻辑描述手段完成的设计文件,自动地完成逻辑编译、化简、分割、综合、优化和仿真,直至下载到可编程逻辑器件CPLD/FPGA 或专用集成电路ASIC芯片中,实现既定的电子电路设计功能。 EDA技术是以计算机为工作平台、以EDA软件工具为开发环境、以硬件描述语言为设计语言、以ASIC(专用集成电路)为实现载体的电子产品自动化设计过程。 1.2 EDA基本特征与优势 EDA工具主要进行三项辅助设计工作:集成电路(IC)设计、电子电路设计及印刷电路板(PCB)设计。 在EDA软件平台上,根据原理图或硬件描述语言HDL完成的设计文件,自动地完成逻辑编译、化简、分割、综合及优化、布局布线、仿真、目标芯片的适配编译、逻辑映射和编程下载等工作。 EDA技术的基本特征:采用高级语言描述;具有系统级仿真和综合能力;具有开放式设计环境;具有丰富的元器件模型库。 EDA技术的优势:(1)采用硬件描述语言,便于复杂系统设计(2)强大的系统建模和电路仿真功能(3)具有自主知识产权(4)开发技术的标准化和规范化(5)全方位地利用计算机的自动设计、仿真和测试技术(6)对设计者的硬件知识和硬件经验要求低。 EDA设计的实现目标:1、印刷电路板设计;2、集成电路(IC或ASIC)设计;3、可编程逻辑器件(FPGA/CPLD)设计;4、混合电路设计。 EDA设计整个综合过程就是将设计者在EDA平台上编辑输入的HDL文本、原理图或状态图形描述,依据给定的硬件结构组件和约束控制条件进行编译、优化、转换和综合,最终获得门级电路甚至更底层的电路描述网表文件。由此可见,综合器工作前,必须给定最后实现的硬件结构参数,它的功能就是将软件描述与给定的硬件结构用某种网表文件的方式对应起来,成为相应互的映射关系。 1.3 EDA工具 EDA工具在EDA技术应用中占据极其重要的位置,EDA的核心是利用计算机完成电子设计全过程自动化,因此,基于计算机环境的EDA软件的支持是必不可少的。EDA工具大致可以分为如下5个模块:设计输入编辑器;仿真器;HDL综合器;适配器(或布局布线器);下载器。当然这种分类不是绝对的,现在往往把各EDA工具集成在一起,如MAX+PLUS Ⅱ、Quartus Ⅱ等。 二、QuartusⅡ简介及设计流程 2.1 QuartusⅡ简介

EDA技术的基本概念

1 EDA技术的基本概念(什么是EDA技术,EDA做什么 EDA即电子设计自动化,是Electronic Design Automation 的英文缩写。 EDA技术是在电子CAD技术基础上发展起来的计算机软件系统,是指以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动设计。具体讲就是: 以大规模可编程逻辑器件为设计载体以硬件描述语言HDL(Hardware Description Language)为系统逻辑描述的主要表达方式以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具自动完成用软件的方式设计的电子系统到硬件系统的逻辑编译、逻辑化简、逻辑分割、逻辑综合、优化、逻辑布局布线、逻辑仿真直至完成对于特定目标芯片适配编译、逻辑映射、编程下载等工作最终形成集成电子系统或专用集成芯片。 2 EDA技术开发流程 设计输入硬件描述语言文本输入 这种方式与传统的计算机软件语言编辑输入基本一致,就是将使用了某种硬件描述语言(HDL)的电路设计文本,如VHDL或Verilog的源程序,进行编辑输入。 仿真让计算机根据一定的算法和一定的仿真库对EDA设计进行模拟,以验证设计排除错误。分为功能仿真和时序仿真两种不同级别的仿真测试 综合综合器不是机械的一对一翻译根据设计库、工艺库以及预先

设置的各类约束条件 选择最优的方式完成电路结构的形成。是选择一种能充分满足各项约束条件且最低成本的实现方案。 适配适配器也称结构综合器,功能是将综合产生的网表文件配置于指定的目标器件中,使之产生最终的下载文件,如JEDEC、Jam格式的文件。 下载和硬件测试把适配器生成的下载或配置文件,通过编程器或编程电缆向FPGA或CPLD进行下载,以便进行硬件调试和验证。 3 IP核基本概念介绍 就是知识产权核或知识产权模块的意思,即用于ASIC或FPGA/CPLD 中的预先设计好的电路模块,分为软IP、固IP和硬IP。 4名词解释:EDA CAD CAE SOC SOPC FPGA CPLD HDL VHDL IP ASIC 5条件赋值语句实现3-8译码器、三人表决器;学号末位奇偶校验位输出器设计 6 进程由信号的变化触发某电路的工作过程,就是进程。 这个信号对进程来说就是敏感信号。 7设计一个4位计数器 LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY counter4 IS PORT ( CLK : IN STD_LOGIC;