EDA技术与Verilog HDL技术实验报告

EDA技术与Verilog HDL技术实验报告

班级:09电信实验班姓名:虞鸿鸣组别:Q09610137

实验:交通灯控制

一、实验目的:

1、运用Verilog HDL综合编辑软件实现相应功能;

2、进一步使用EDA技术解决实际问题;

3、进一步使用EDA工具箱,提高对硬件电路的认识。

二、实验仪器

PC计算机、EDA实验工具箱

三、简要原理

1. 能显示十字路口东西、南北两个方向的红、黄、绿的指示状态

用两组红、黄、绿三色灯作为两个方向的红、黄、绿灯。变化规律为:东西绿灯,南北红灯→东西黄灯,南北红灯→东西红灯,南北绿灯→东西红灯,南北黄灯→东西绿灯,南北红灯……依次循环。

2. 能实现正常的倒计时功能

用两组数码管作为东西和南北方向的允许或通行时间的倒计时显示,显示时间为红灯45秒、绿灯40秒、黄灯5秒。

3. 能实现紧急状态处理的功能

(1) 出现紧急状态(例如消防车,警车执行特殊任务时要优先通行)时,两路上所有车禁止通行,红灯全亮;

(2) 显示到计时的两组数码管闪烁;

(3) 计数器停止计数并保持在原来的状态;

(4) 特殊状态解除后能返回原来状态继续运行。

4. 能实现系统复位功能

系统复位后,东西绿灯,南北红灯,东西计时器显示40秒,南北显示45秒。

5. 用VHDL语言设计符合上述功能要求的交通灯控制器,并用层次化设计方法设计该电路。

6. 控制器、置数器的功能用功能仿真的方法验证,可通过有关波形确认电

路设计是否正确。

7. 完成电路全部设计后,通过系统实验箱下载验证设计课题的正确性。

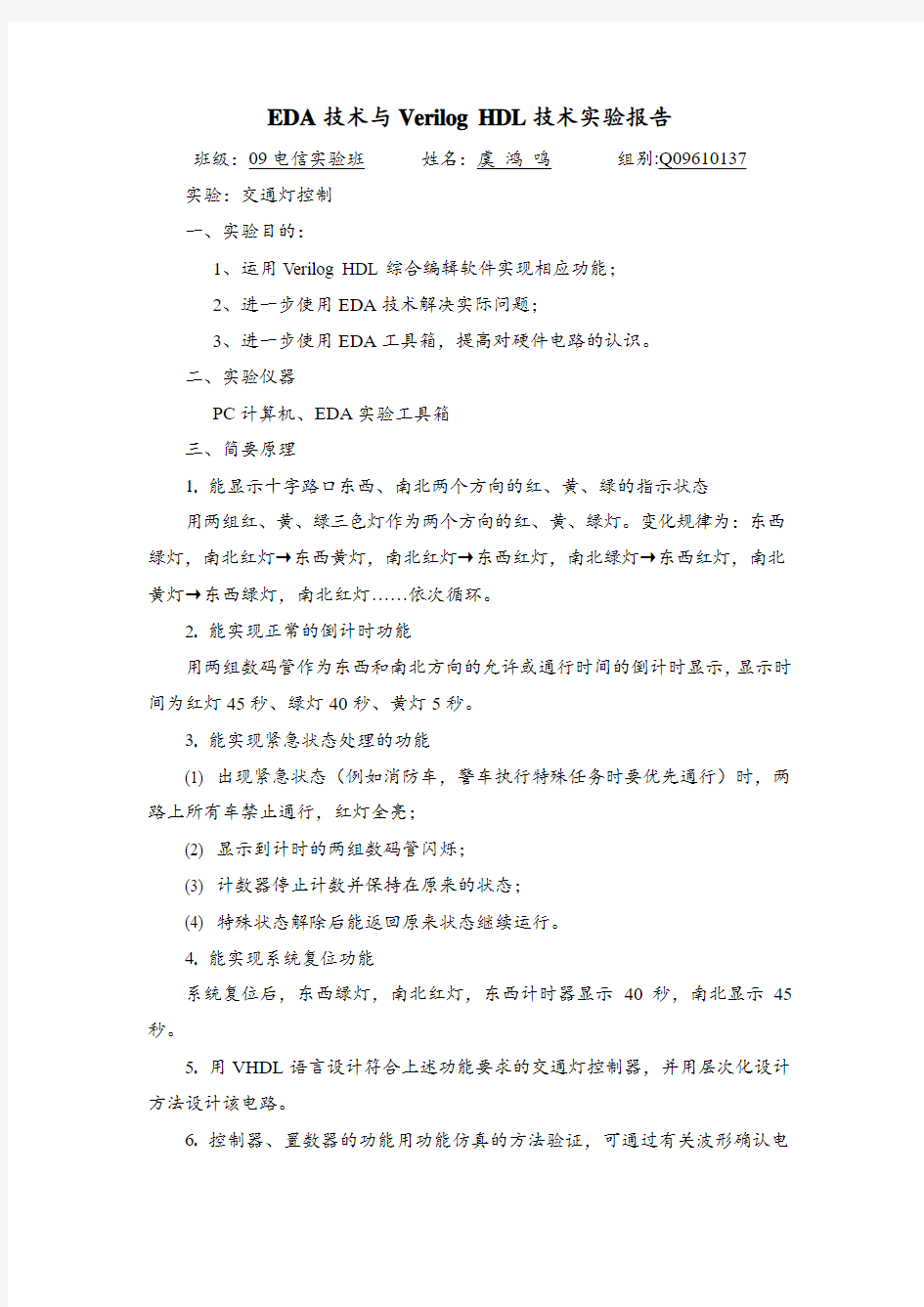

四、设计思路

EN、CLK、RST、URGEN分别为使能信号、时钟信号、复位信号和紧急情况信号;

num1,num2分别为东西方向的倒计时和南北方向的倒计时,两个八位数码管,硬件接有译码芯片;

light1,light2分别为东西方向的交通灯和南北方向的交通灯中红、黄、绿三色位置;

tim1,tim2分别为东西和南北方向的交通的灯控制信号,高电平时有效;

pb1,pb2分别为寄存紧急情况前交通灯状态变量的标志信号,高电平有效;

state1,state2分别为东西、南北方向的交通灯状态信号,每个方向有三种状态,即00、01、11;

五、源代码及注析

module TRAFFIC_LI(EN,CLK,RST,URGEN,num1,num2,light1,light2);

input EN,CLK,RST,URGEN;//EN、CLK、RST、URGEN分别为使能信号、时钟信号、复位信号和紧急情况信号

output[7:0] num1,num2;//num1,num2分别为东西方向的倒计时和南北方向的倒计时,两个八位数码管,硬件接有译码芯片

output[2:0] light1,light2;//light1,light2分别为东西方向的交通灯和南北方向的交通灯中红、黄、绿三色位置

reg tim1,tim2,pb1,pb2;//tim1,tim2分别为东西和南北方向的交通的灯控制信号,高电平时有效

//pb1,pb2分别为寄存紧急情况前交通灯状态变量的标志信号,高电平有效

reg[1:0]state1,state2;//state1,state2分别为东西、南北方向的交通灯状态信号,每个方向有三种状态,即00、01、11

reg[2:0]light1,light2,light3,light4;//light3,light4用以寄存紧急情况前交通灯

状态

reg[7:0] num1,num2;//现实时间寄存

reg[7:0] red1,red2,green1,green2,yellow1,yellow2;//东西南北方向三种颜色的交通灯亮的时间

always @(EN)

if(!EN)

begin //设置计数初值

green1<=8'b01000000;//绿灯40S

red1<=8'b01000000;//红灯40S

yellow1<=8'b00000101;//黄灯5S

green2<=8'b01000000;

red2<=8'b01000000;

yellow2<=8'b00000101;

end

always @(posedge CLK )

begin

if(!URGEN)

begin

light3<=light1;

end

if(RST)//东西方向复位控制

begin

light1<=3'b001; //亮绿灯

num1<=green1;//时间为40S

end

else if(URGEN) //东西方向紧急情况控制

begin

light1<=3'b100; //亮红灯

//计数暂停

pb1<=1;

end

else if(pb1)

begin

light1<=light3;

pb1<=0;

end

else if(EN)

begin //使能有效开始控制计数

if(!tim1) //开始控制

begin //东西方向交通灯点亮控制

tim1<=1;

case(state1)

2'b00:begin

num1<=green1;

light1<=3'b001;

state1<=2'b01;

end//绿灯亮40S,跳转至下一状态

2'b01:begin

num1<=yellow1-1;

light1<=3'b010;

state1<=2'b10;

end//黄灯亮5秒,跳转至下一状态

2'b10:begin

num1<=red1+5;

light1<=3'b100;

state1<=2'b00;

end//红灯亮45S,跳转至初状态

default:light1<=3'b100;//其他情况亮红灯

endcase

end

else

begin //倒数计时

if(num1>0)

if(num1[3:0]==0)

begin

num1[3:0]<=4'b1001;

num1[7:4]<=num1[7:4]-1;

end

else num1[3:0]<=num1[3:0]-1;

if(num1==1) tim1<=0;

end

end

else

begin

light1<=3'b010;

num1=2'b00;

tim1<=0;

end

end

always @(posedge CLK )

begin

if(!URGEN)

begin

light4<=light2;

end

if(RST) //南北方向复位控制

begin

light2<=3'b100;//亮红灯

num2<=red2+5;//时间为45S

end

else if(URGEN)//南北方向特殊情况控制

begin

light2<=3'b100;//亮红灯

//计数暂停

pb2<=1;

end

else if(pb2)

begin

light2<=light4;

pb2<=0;

end

else if(EN)

begin

if(!tim2)

begin //南北方向交通灯控制

tim2<=1;

case(state2)

2'b00:begin

num2<=red2+5;

light2<=3'b100;

state2<=2'b01;

end

2'b01:begin

num2<=green2;

light2<=3'b001;

state2<=2'b10;

end

2'b10:begin

num2<=yellow2-1;

light2<=3'b010;

state2<=2'b00;

end

default:light2<=3'b100;

endcase

end

else

begin //倒数计时

if(num2>0)

if(num2[3:0]==0)

begin

num2[3:0]<=4'b1001;

num2[7:4]<=num2[7:4]-1;

end

else num2[3:0]<=num2[3:0]-1;

if(num2==1) tim2<=0;

end

end

else

begin

tim2<=0;

state2<=2'b00;

light2<=3'b010;

end

end

endmodule

六、实验结果及分析

初始状态时,东西方向绿灯,计时40秒,南北方向红灯,计时45秒。当有RST高电平触发时,系统自动进入初始化状态,东西方向绿灯,南北方向红灯,计时分别为40秒和45秒。

RST后,程序自动重新开始计数,减1运行计时功能。

当URGEN高电平时,即出现紧急情况,东西和南北方向均亮起红灯,当紧急信号过去后再恢复原来的状态,计时继续进行。

紧急情况过去后,程序继续正常按照规定的时序进行运行。

当绿灯计时40秒后,就进入5秒种的黄灯阶段。在此期间,红灯仍继续工作5秒,直到5秒过后,两个方向的交通灯同时发生变化。

讨论:

1、在仿真阶段,由于CLK时钟频率设置不合理,一直没有得到想要的实验结果。通过改变CLK的参数设置和检查程序设计,实现了预期目的,波形达到了预期的效果。

2、在绿灯→黄灯阶段,在先前的设计中,始终不能保证两者的实时控制。经讨论研究,其问题出在黄灯的延时上面。因为绿灯和黄灯之间会有1秒的时间重合,这就导致了两者不能同时计时,实验结果自然不能达到预期效果。

实验心得:这是期末作业,同时也是对这一学期EDA学习的综合应用。在程序设计中,的的确确遇到了不少问题,但通过查阅资料,相互探讨得以解决。EDA的作用也不言而喻,因而在以后的学习中也应加强对其的学习。

数字系统设计与verilog HDL课程设计

数字系统设计与verilog HDL课程设计 设计题目:实用多功能数字钟 专业:电子信息科学与技术 班级:0313410 学号:031341025 姓名:杨存智 指导老师:黄双林

摘要 本课程设计利用QuartusII软件Verilog VHDL语言的基本运用设计一个多功能数字钟,经分析采用模块化设计方法,分别是顶层模块、alarm、alarm_time、counter_time、clk50mto1、led、switch、bitel、adder、sound_ddd、sound_ddd_du模块,再进行试验设计和软件仿真调试,分别实现时分秒计时、闹钟闹铃、时分秒手动校时、时分秒清零,时间保持和整点报时等多种基本功能。 单个模块调试达到预期目标,再将整体模块进行试验设计和软件仿真调试,已完全达到分块模式设计功能,并达到设计目标要求。 关键字:多功能数字钟、Verilog、模块、调试、仿真、功能

目录 1.课程设计的目的及任务............................................................. 错误!未定义书签。 1.1 课程设计的目的 (3) 1.2 课程设计的任务与要求 (4) 2.课程设计思路及其原理 (4) 3.QuartusII软件的应用 (5) 3.1工程建立及存盘 (5) 3.2工程项目的编译 (5) 3.3时序仿真 (6) 4.分模块设计、调试、仿真与结果分析 (7) 4.1 clk50mto1时钟分频模块 (7) 4.2 adder加法器模块 (7) 4.3 hexcounter16 进制计数器模块 (7) 4.4 counter_time 计时模块 (8) 4.5 alarm闹铃模块 (8) 4.6 sound_ddd嘀嘀嘀闹铃声模块 (9) 4.7 sound_ddd_du嘀嘀嘀—嘟声音模块 (9) 4.8 alarm_time闹钟时间设定模块 (10) 4.9 bitsel将输出解码成时分秒选择模块 (10) 4.10 switch去抖模块 (11) 4.11 led译码显示模块 (11) 4.12 clock顶层模块 (12) 5.实验总结 (13) 5.1调试中遇到的问题及解决的方法 (13) 5.2实验中积累的经验 (14) 5.3心得体会 (14) 6.参考文献 (14) 1.1 课程设计的目的 通过课程设计的锻炼,要求学生掌握V erilog HDL语言的一般设计方法,掌握VerilogHDL语言的基本运用,具备初步的独立设计能力,提高综合运用所学的理论知识独立分析和解决问题的能力,基于实践、源于实践,实践出真知,实践检验真理,培养学生的

中南大学EDA VerilogHDL试题 附答案

一、填空题(10分,每小题1分) 1.用EDA技术进行电子系统设计的目标是最终完成的设计与实现。 2.可编程器件分为和。 3.随着EDA技术的不断完善与成熟,的设计方法更多的被应用于 Verilog HDL设计当中。 4.目前国际上较大的PLD器件制造公司有和公司。 5.完整的条件语句将产生电路,不完整的条件语句将产生电路。 6.阻塞性赋值符号为,非阻塞性赋值符号为。 二、选择题(10分,每小题2分) 1.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述 中,正确的是。 A.FPGA全称为复杂可编程逻辑器件; B.FPGA是基于乘积项结构的可编程逻辑器件; C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置; D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。 2.基于EDA软件的FPGA / CPLD设计流程为:原理图/HDL文本输入→综合 →_____→→适配→编程下载→硬件测试。正确的是。 ①功能仿真②时序仿真③逻辑综合④配置⑤分配管脚 A.③①B.①⑤C.④⑤D.④② 3.子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行 速度(即速度优化);指出下列哪些方法是面积优化。 ①流水线设计②资源共享③逻辑优化④串行化⑤寄存器配平⑥关键路径法 A.①③⑤B.②③④C.②⑤⑥D.①④⑥ 4.下列标识符中,__________是不合法的标识符。 A.9moon B.State0 C.Not_Ack_0 D.signall 5.下列语句中,不属于并行语句的是:_______ A.过程语句B.assign语句C.元件例化语句D.case语句 三、EDA名词解释(10分)

《EDA技术与Verilog_HDL》清华第2版习题1

第章EDA技术概述

1-1 EDA技术与ASIC设计和FPGA开发有什么关系?FPGA在ASIC设计中有什么用途? 答:EDA技术进行电子系统设计的最后目标,是完成专用集成电路(ASIC)的设计和实现,FPGA是实现这一途径的主流器件,它们的特点是直接面向用户、具有极大的灵活性和通用性、使用方便、硬件测试和实现快捷、开发效率高、成本低、上市时间短、技术维护简单、工作可靠性好等。FPGA的应用是EDA技术有机融合软硬件电子设计技术、ASIC设计,以及对自动设计与自动实现最典型的诠释。 1-2 与软件描述语言相比,Verilog有什么特点? 答:Verilog语言的特点: (1)按照设计目的,Verilog程序可以划分为面向仿真和面向综合两类,而可综合的Verilog程序能分别面向FPGA和ASIC开发两个领域。 (2)能在多个层次上对所设计的系统加以描述,从开关级、门级、寄存器传输级(RTL)至行为级都可以加以描述。 (3)灵活多样的电路描述风格。

1-3 什么是综合?有哪些类型?综合在电子设计自动化中的地位是什么?答:综合(Synthesis),就其字面含义应该是:把抽象的实体结合成单个或统一的实体。 在电子设计领域,综合的概念可以表述为:将用行为和功能层次表达的电子系统转换为低层次的、便于具体实现的模块组合装配的过程。 (1)从自然语言转换到Verilog语言算法表述,即自然语言综合。 (2)从算法表述转换到寄存器传输级(Register Transport Level,RTL)表述,即从行为域到结构域的综合,也称行为综合。 (3)从RTL级表述转换到逻辑门(包括触发器)的表述,即逻辑综合。(4)从逻辑门表述转换到版图级表述(如ASIC设计),或转换到FPGA的配置网表文件,可称为版图综合或结构综合。 综合器就是能够将一种设计表述形式自动向另一种设计表述形式转换的计算机程序,或协助进行手工转换的程序。它可以将高层次的表述转化为低层次的表述,可以将行为域转化为结构域,可以将高一级抽象的电路描述(如算法级)转化为低一级的电路描述(如门级),并可以用某种特定的“技术”(如CMOS)实现。

EDA技术与Verilog HDL技术实验报告

EDA技术与Verilog HDL技术实验报告 班级:09电信实验班姓名:虞鸿鸣组别:Q09610137 实验:交通灯控制 一、实验目的: 1、运用Verilog HDL综合编辑软件实现相应功能; 2、进一步使用EDA技术解决实际问题; 3、进一步使用EDA工具箱,提高对硬件电路的认识。 二、实验仪器 PC计算机、EDA实验工具箱 三、简要原理 1. 能显示十字路口东西、南北两个方向的红、黄、绿的指示状态 用两组红、黄、绿三色灯作为两个方向的红、黄、绿灯。变化规律为:东西绿灯,南北红灯→东西黄灯,南北红灯→东西红灯,南北绿灯→东西红灯,南北黄灯→东西绿灯,南北红灯……依次循环。 2. 能实现正常的倒计时功能 用两组数码管作为东西和南北方向的允许或通行时间的倒计时显示,显示时间为红灯45秒、绿灯40秒、黄灯5秒。 3. 能实现紧急状态处理的功能 (1) 出现紧急状态(例如消防车,警车执行特殊任务时要优先通行)时,两路上所有车禁止通行,红灯全亮; (2) 显示到计时的两组数码管闪烁; (3) 计数器停止计数并保持在原来的状态; (4) 特殊状态解除后能返回原来状态继续运行。 4. 能实现系统复位功能 系统复位后,东西绿灯,南北红灯,东西计时器显示40秒,南北显示45秒。 5. 用VHDL语言设计符合上述功能要求的交通灯控制器,并用层次化设计方法设计该电路。 6. 控制器、置数器的功能用功能仿真的方法验证,可通过有关波形确认电

路设计是否正确。 7. 完成电路全部设计后,通过系统实验箱下载验证设计课题的正确性。 四、设计思路 EN、CLK、RST、URGEN分别为使能信号、时钟信号、复位信号和紧急情况信号; num1,num2分别为东西方向的倒计时和南北方向的倒计时,两个八位数码管,硬件接有译码芯片; light1,light2分别为东西方向的交通灯和南北方向的交通灯中红、黄、绿三色位置; tim1,tim2分别为东西和南北方向的交通的灯控制信号,高电平时有效; pb1,pb2分别为寄存紧急情况前交通灯状态变量的标志信号,高电平有效; state1,state2分别为东西、南北方向的交通灯状态信号,每个方向有三种状态,即00、01、11; 五、源代码及注析 module TRAFFIC_LI(EN,CLK,RST,URGEN,num1,num2,light1,light2); input EN,CLK,RST,URGEN;//EN、CLK、RST、URGEN分别为使能信号、时钟信号、复位信号和紧急情况信号 output[7:0] num1,num2;//num1,num2分别为东西方向的倒计时和南北方向的倒计时,两个八位数码管,硬件接有译码芯片 output[2:0] light1,light2;//light1,light2分别为东西方向的交通灯和南北方向的交通灯中红、黄、绿三色位置 reg tim1,tim2,pb1,pb2;//tim1,tim2分别为东西和南北方向的交通的灯控制信号,高电平时有效 //pb1,pb2分别为寄存紧急情况前交通灯状态变量的标志信号,高电平有效 reg[1:0]state1,state2;//state1,state2分别为东西、南北方向的交通灯状态信号,每个方向有三种状态,即00、01、11 reg[2:0]light1,light2,light3,light4;//light3,light4用以寄存紧急情况前交通灯

eda技术与veriloghdl实验报告

EDA技术与Verilog HDL 实验报告 学生姓名:樊奇峰 学生学号: 所在班级:10级电科(2)班 实验老师:陈亮亮 实验地点地点:理工楼

实验一 EDA实验箱使用 一.实验目的 1.GW48教学实验系统原理与使用介绍 2.熟悉QuartusII两种输入方式下编译、仿真简单的组合电路。 二.实验内容 首先了解GW48系统使用注意事项以及GW48系统主板结构与使用方法,接着对各实验电路结构图特点与适用范围简述。最后在QuartusII界面下,用文本输入和图形输入分别验证七选一多路选择器的功能。 三.程序清单 文本输入如下所示: module mux71(a,b,c,d,e,f,g,s,y); input a,b,c,d,e,f,g; output y; input [2:0] s; reg y ; always @(a,b,c,d,e,f,g,s) case (s) 0: y<=a; 1: y<=b; 2: y<=c; 3: y<=d; 4: y<=e; 5: y<=f; 6: y<=g; default: y<=a; endcase

endmodule 图形输入如下所示: 四、实验步骤 1、新建一个名称为MUX71a的工程,并在该文件夹中新建一个的文件。 2、编译代码,编译成功后进行第三步,若不成功则查改代码中的错误。 3、在工程文件夹中新建一个的波形文件,导入工程端口,设置输入波形,仿真得出输出端口波形。 4、验证输出端口波形是否达到七选一多路选择器的功能。 五、实验数据 仿真波形如下图所示。 六、实验小结 通过对EDA实验箱使用,了解了GW48教学实验系统原理与使用介绍;

EDA技术与verilog语言练习题

设计示范和上机习题 练习一.简单的组合逻辑设计 //(方法一): //---------------文件名compare.v ----------------- module compare(equal,a,b); input a,b; output equal; assign equal = (a==b)? 1 : 0; //a等于b时,equal输出为1;a不等于b时,equal输出为0。 endmodule //(方法二): module compare(equal,a,b); input a,b; output equal; reg equal; always @(a or b) if(a==b) //a等于b时,equal输出为1; equal =1; else //a不等于b时,equal输出为0。 equal = 0; //思考:如果不写else 部分会产生什么逻辑? endmodule //------------------------------------------------------------- //----------测试模块源代码(方法之一): `timescale 1ns/1ns // 定义时间单位。 `include "./compare.v"//包含模块文件。在有的仿真调试环境中并不需要此语句。 //而需要从调试环境的菜单中键入有关模块文件的路径和名称module t; reg a,b; wire equal; initial // initial常用于仿真时信号的给出。 begin a=0; b=0; #100 a=0; b=1; #100 a=1; b=1; #100 a=1; b=0; #100 a=0; b=0;

中南大学EDA技术与Verilog hdl实验指导书

实验1: QuartusII基本设计流程体验实验 实验步骤: 1. 启动QuartusII。 2. 创建工程。 (1)选择File->New Project Wizard命令 (2)输入工程库文件夹(注意:不要使用Quartus安装目录,不要使用路径中包含中文的目录,例如桌面等)。输入工程名:MUX41a (3)跳过“添加文件”步骤。 (4)选择目标芯片(EP3C55F484C8) (5)跳过“工具设置”步骤,点击“Finish”。 3. 输入设计文件。 (1)选择“File->New”命令,选择Verilog HDL File选项。 (2)在文本编辑器中输入4选一选择器的代码(使用Case语句)。 (3)选择File->Save As命令保存文件。 3. 进行全程编译。编译过程中注意Processing窗口的编译信息。 4. 查看编译报告。 扩展实验与思考: 1.将代码中Case语句修改为if-else语句,比较两者的编译结果(硬件资源使用 情况)。 2.将if-else语句改为不完整条件语句,再次编译后查看编译结果(1.查看综合 报告中的警告信息;2.利用Tools>Netlist Viewers>RTL Viewer查看结构图)。 实验2: ModelSim仿真实验1 实验步骤: (1)启动Modelsim; (2)选择File->New->Project建立新工程,工程目录指定为实验1所用目录,加入验证对象文件MUX41a.v; (3)在Project窗口中选中设计文件,单击鼠标右键,选择Compile->Compile All 编译源代码;如有编译错误,修改源代码; (4)选择Simulate->Start Simulation或点击Simulate按键,选Library窗口中 work->MUX41a,点击OK。 (5)在Object窗口中选择需要观察的信号,单击鼠标右键,选择Add->To Wave-> Selected Singals,添加待观察信号至波形窗口; (6)在Transcript窗口中使用force输入激励信号;例如:force A 0 (7)在Transcript窗口输入run命令或点击run按键执行仿真,查看结果. (8)改变激励信号,执行仿真并查看结果。

《EDA技术与Verilog HDL》

实用EDA技术研习培训相关资料 《EDA技术与Verilog HDL》 目录 第1章概述............................................................................................................................ 1.1 EDA技术及其发展.................................................................................................. 1.2EDA技术实现目标.................................................................................................. 1.3硬件描述语言Verilog HDL..................................................................................... 1.4 其他常用硬件描述语言........................................................................................... 1.5 HDL综合.................................................................................................................. 1.6 基于HDL的自顶向下设计方法............................................................................. 1.7 EDA技术的优势...................................................................................................... 1.8 EDA的发展趋势 思考题................................................................................................................................第2章 EDA设计流程及其工具........................................................................................... 2.1 设计流程................................................................................................................... 2.1.1 设计输入(原理图/HDL文本编辑).................................................................. 2.1.2 综合................................................................................................................... 2.1.3 适配................................................................................................................... 2.1.4 时序仿真与功能仿真........................................................................................... 2.1.5 编程下载............................................................................................................ 2.1.6 硬件测试............................................................................................................ 2.2ASIC及其设计流程................................................................................................. 2.2.1 ASIC设计方法简介............................................................................................. 2.2.2 一般ASIC设计的流程......................................................................................... 2.3 常用EDA工具......................................................................................................... 2.3.1 设计输入编辑器.................................................................................................. 2.3.2 HDL综合器........................................................................................................ 2.3.3 仿真器................................................................................................................ 2.3.4 适配器................................................................................................................ 2.3.5 下载器................................................................................................................ 2.4 Quartus II简介.......................................................................................................... 2.5 IP核简介...................................................................................................................

EDA VerilogHDL期末必考试题

一、填空题(10分,每小题1分)1.用EDA技术进行电子系统设计的目标 是最终完成 ASIC 的设 计与实现。 2.可编程器件分为FPGA 和 CPLD 。 3.随着EDA技术的不断完善与成熟,自顶向下的设计方法更多的被应用于Verilog HDL设计当中。 4.目前国际上较大的PLD器件制造公司有 Altera 和 Xilinx 公司。 5.完整的条件语句将产生组合电路,不完整的条件语句将产生时序 电路。 6.阻塞性赋值符号为=,非阻塞性赋值符号为 <= 。 二、选择题(10分,每小题2分) 1.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是 C 。 A.FPGA全称为复杂可编程逻辑器件; B.FPGA是基于乘积项结构的可编程逻辑器件; C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置; D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。 2.基于EDA软件的FPGA / CPLD设计流程为:原理图/HDL文本输入→综合 →___ __→→适配→编程下载→硬件测试。正确的是 B 。 ①功能仿真②时序仿真③逻辑综合④配置⑤分配管脚 A.③①B.①⑤C.④⑤D.④② 3.子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);指出下列哪些方法是面积优化 B 。 ①流水线设计②资源共享③逻辑优化④串行化⑤寄存器配平⑥关键路径法 D.①④⑥C.②⑤⑥A.①③⑤B.②③④ 4.下列标识符中,____A______是不合法的标识符。 A.9moon B.State0 C.Not_Ack_0 D.signall 5.下列语句中,不属于并行语句的是:___D____

中南大学EDA技术与Veriloghdl实验指导书

实验1:Q u a r t u s I I基本设计流程体验实验 实验步骤: 1.启动QuartusII。 2.创建工程。 (1)选择File->NewProjectWizard命令 (2)输入工程库文件夹(注意:不要使用Quartus安装目录,不要使用路径中包含中文的目录,例如桌面等)。输入工程名:MUX41a (3)跳过“添加文件”步骤。 (4)选择目标芯片(EP3C55F484C8) (5)跳过“工具设置”步骤,点击“Finish”。 3.输入设计文件。 (1)选择“File->New”命令,选择VerilogHDLFile选项。 (2)在文本编辑器中输入4选一选择器的代码(使用Case语句)。 (3)选择File->SaveAs命令保存文件。 3.进行全程编译。编译过程中注意Processing窗口的编译信息。 4.查看编译报告。 扩展实验与思考: 1.将代码中Case语句修改为if-else语句,比较两者的编译结果(硬件资源使 用情况)。 2.将if-else语句改为不完整条件语句,再次编译后查看编译结果(1.查看综 合报告中的警告信息;2.利用Tools>NetlistViewers>RTLViewer查看结构图)。 实验2:ModelSim仿真实验1 实验步骤: (1)启动Modelsim; (2)选择File->New->Project建立新工程,工程目录指定为实验1所用目录,加入验证对象文件MUX41a.v; (3)在Project窗口中选中设计文件,单击鼠标右键,选择Compile->CompileAll 编译源代码;如有编译错误,修改源代码; (4)选择Simulate->StartSimulation或点击Simulate按键,选Library窗口中work->MUX41a,点击OK。 (5)在Object窗口中选择需要观察的信号,单击鼠标右键,选择 Add->ToWave->SelectedSingals,添加待观察信号至波形窗口; (6)在Transcript窗口中使用force输入激励信号;例如:forceA0 (7)在Transcript窗口输入run命令或点击run按键执行仿真,查看结果. (8)改变激励信号,执行仿真并查看结果。

EDA技术与Verilog_HDL(潘松)第6章习题答案

6-1 在Verilog设计中,给时序电路清零(复位)有两种不同方法,它们是什么,如何实现? 答:同步清零、异步清零,在过程语句敏感信号表中的逻辑表述posedge CLK用于指明正向跳变,或negedge用于指明负向跳变实现 6-2 哪一种复位方法必须将复位信号放在敏感信号表中?给出这两种电路的Verilog 描述。 答:异步复位必须将复位信号放在敏感信号表中。 同步清零: always @(posedge CLK) //CLK上升沿启动 Q<=D; //当CLK有升沿时D被锁入Q 异步清零: always @(posedge CLK or negedge RST) begin //块开始 if(!RST)Q<=0; //如果RST=0条件成立,Q被清0 else if(EN) Q<=D;//在CLK上升沿处,EN=1,则执行赋值语句 end//块结束

6-3 用不同循环语句分别设计一个逻辑电路模块,用以统计一8位二进制数中含1的数量。 module Statistics8(sum,A); output[3:0]sum; input[7:0] A; reg[3:0] sum; integer i; always @(A) begin sum=0; for(i=0;i<=8;i=i+1) //for 语句if(A[i]) sum=sum+1; else sum=sum; end endmodule module Statistics8(sum,A); parameter S=4; output[3:0]sum; input[7:0] A; reg[3:0] sum; reg[2*S:1]TA; integer i; always @(A) begin TA=A; sum=0; repeat(2*S) begin if(TA[1])sum=sum+1; TA=TA>>1; end end endmodule repeat循环语句 for循环语句