时序控制器TCON的研究与设计

同步时序电路的设计步骤

同步时序电路的设计步骤 同步时序电路的设计步骤 同步时序电路的分析是根据给定的时序逻辑电路,求出能反映该电路功能的状态图。状态图清楚地表明了电路在不同的输入、输出原状态时,在时钟作用下次态状态的变化情况。同步时序电路的设计的设计是分析的反过程,其是根据给定的状态图或通过对设计要求的分析得到的状态图,设计出同步时序电路的过程。 这里主要讨论给定状态图的情况下的同步时序电路的设计,对于具体的要求得到状态图的过程一般是一个较复杂的问题,这是暂不讲。根据已知状态图设计同步时序电路的过程一般分为以下几步: 1.确定触发器的个数。首先根据状态的个数来确定所需要触发器的个数,如给定的状态个数为n,由应满足 n≤2K,K为实现这来状态所需要的触发器的个数。(实际使用时可能给定的状态中存在冗余项,这时一般还须对状态进行化简。) 2.列出状态转移真值表。根据状态列出状态转移真值表,也称状态表、状态转移表。 3.触发器选型。选择合适的触发器,通常可选的触发器有:JK-FF,D-FF,T-FF,一般使用较广的为JK-FF。根据状态图和给出的触发器的型号写出其输入方程,通常在写输入方程时须对其进行化简,以使电路更简单。 4.求出输出方程。根据状态表,求出输出逻辑函数Z的输出方程,还过有些电路没有独立的输出,这一步就省了。 5.画出逻辑图。根据输入方程、输出方程画出逻辑电路图。 6.讨论设计的电路能否自启动。在设计的电路中可能出现一些无关的状态,这些状态能否经过若干个时钟脉冲后进行有效的状态。 同步时序电路设计举例 例按下图状态图设计同步时序电路。 1.根据状态数确定触发器的数目:由状态图可以看出,其每个状态由两个状态,故可用两个触发器。其变量可 用Q 1,Q 表示; 2.根据状态图列出状态表:状态表的自变量为输入变量x和触发器当前状态Q 1 n,Q n,而应变量为触发器的次态 Q 1n+1Q n+1、及输出z,列表时将自变量的所有组合全部列出来,其中当Q 1 n Q n=01的状态为不出现,其输出可看作任意 项处理。

时序逻辑电路设计

引言 人类社会进步,各种仪器测试设备的以电子设备代替成为趋势,各类测试仪器都希望通过电子设备来实现。电子设备在实现相应参数的测量时,具有简单容易操作,而且数据便于计算机处理等优点。目前科技的飞速进展与集成电路的发展应用,有密不可分的关系。十九世纪工业革命主要以机器节省人力,二十世纪的工业的革命则主要以电脑为人脑分劳。而电脑的发展归于集成电路工业。 集成电路是将各种电路器件集成于半导体表面而形成的电路。近年来集成电路几乎成为所有电子产品的心脏。由于集成电路微小化的趋向,使电子产品得以“轻、薄、短、小”。故集成电路工业又称微电子工业。差不多在同时数字计算机的发展提供了应用晶体管的庞大潜在市场。 20世纪90年代以后,电子科学和技术取得了飞速的发展,其标志就是电子计算机的普及和大规模集成电路的广泛应用。在这种情况下,传统的关于数字电路的内容也随之起了很大的变化,在数字电路领域EDA工具已经相当成熟,无论是电路内容结构设计还是电路系统设计,以前的手工设计都被计算机辅助设计或自动设计所取代。 通过长期的学习微电子专业理论知识,我们应该多动手实践把理论知识与实践相结合,加强对理论知识的把握。本文是十进制同步计数器的设计,对十进制同步计数器的设计进行电路原理图设计以及仿真,版图设计,版图验证。 1 设计技术要求 (1)项目名称:十进制同步计数器的设计 (2)使用工艺:2.0um硅栅工艺(tanner)或者1.0um硅栅工艺(cadence) (3)供电电源:5V (4)输入要求:异步清除,CMOS电平 (5)进行原理图设计,并完成电路的仿真 (6)版图设计,完成LVS一致性检验,生成相应的GDSII文档 2 设计构思及理论 2.1 设计思路 十进制同步计数器的设计可以细化成下列步骤: ①建立最简原始状态图。 ②确定触发器级数,进行状态编码。 ③用状态装换卡诺图化简,求状态方程和输出方程。 ④查自启动特性。 ⑤确定触发类型,求驱动方程。 ⑥画逻辑图。

数字电路时序分析.pdf

数字电路时序分析 1数字电路时序分析 前面介绍了对器件之间的互连系统进行建模所需要的知识,包括对信号完整性的详细分析并估算了由于非理想因素引起的时序变化。但是要正确设计一个数字系统还需要使系统中器件之间可以互相通信,涉及到的内容主要是设计正确的时序,保证器件的时钟/锁存信号与数据信号之间保证正确的时序关系,满足接收端要求的最小建立和保持时间,使得数据可以被正确的锁存。 在本章中将会介绍共用时钟总线(common-clock)和源同步总线(source synchronous)的基本的时序方程。设计者可以利用时序方程来跟踪分析影响系统性能的有时序要求的器件,设置设计目标,计算最大的总线频率和时序裕量。 1.1. 共用时钟定时(common-clock timing) 在共用时钟总线中,总线上的驱动端和接收端共享同一个时钟。图8.1为一个共用时钟总线的例子,是处理器与外围芯片之间的总线接口,由处理器向外围芯片发送数据。图中还示出了位于每一个输入输出单元(I/O cell)的内部锁存器。完成一次数据传输需要两个时钟脉冲,一个用于将数据锁存到驱动端触发器,另一个用于将数据锁存到接收端触发器。整个数据传输过程分为以下几个步骤: 图8.1 共用时钟总线示意图 a.处理器内核产生驱动端触发器的有效输入D p。

b.系统时钟(clk in)的边沿1由时钟缓冲器输出并沿着传输线传播到处理器用于将驱动端触发器的输入(D p)锁存到输出(Q p)。 c.信号Q p沿着传输线传播到接收端触发器的输入(D c),并由第二个时钟边沿锁存。这样有效数据就在外围信号的内核产生了。 基于前面对数据传输过程的分析,可以得到一些基本的结论。首先,电路和传输线的延时必须小于时钟周期,这是因为信号每次从一个器件传播到另一个器件需要两个时钟周期:第一个周期——驱动端触发器将数据锁存到输出(Qp),第二个周期——接收端触发器将输入数据锁存到芯片内核。由电路和PCB走线引起的总延时必须小于一个时钟周期,这一结论限制了共用时钟总线的最高理论工作频率,因此设计一个共用时钟总线时必须考虑每部分的延时,满足接收端的建立和保持时间(建立和保持时间是为了保证能够正确地锁存数据,数据应该在时钟边沿来到之前和之后必须保持稳定的最小时间,这两个条件必须满足)。 1.1.1.共用时钟总线的时序方程 图8.2的时序图用于推导共用时钟总线的时序方程,每个箭头都表示系统中的一个延时,并在图8.1中已表示出来。实线表示的定时回路(timing loop)可用于推导建立时间时序裕量的计算公式,虚线表示的定时回路可用于推导保持时间时序裕量的计算公式。下面会介绍如何使用定时回路来得到时序方程。 图8.2 共用时钟总线的时序图 时延分为三个部分:T co、飞行时间(flight time)和时钟抖动。T co为时钟有效到数据输出有效的时间;飞行时间(T flt)是指PCB上传输线的延时;时钟抖动

时序电路的基本分析与设计方法

时序电路的基本分析与设计方法

时序逻辑电路 时序逻辑电路——电路任何一个时刻的输出状态不但取决于当时的输入信号,还与电路的原状态有关。时序电路中必须含有具有记忆能力的存储器件。 时序电路的逻辑功能可用逻辑表示式、状态表、卡诺图、状态图、时序图和逻辑图6种方式表示,这些表示方法在本质上是相同的,能够互相转换。 一、时序电路的基本分析和设计方法 (一)分析步骤 1.根据给定的时序电路图写出下列各逻辑方程式: (1)各触发器的时钟方程。(2)时序电路的输出方程。(3)各触发器的驱动方程。 2.将驱动方程代入相应触发器的特性方程,求得各触发器的次态方程,也就是时序逻辑电路的状态方程。 3.根据状态方程和输出方程,列出该时序电路的状态表,画出状态图或时序图。 4.根据电路的状态表或状态图说明给定时序逻辑电路的逻辑功能。【例1】分析时序电路

(1)时钟方程:CP CP CP CP ===012 输出方程:n n Q Q Y 21= 驱动方程:?? ? ??======n n n n n n Q K Q J Q K Q J Q K Q J 202001011212 (2)求状态方程 JK 触发器的特性方程:n n n Q K Q J Q +=+1 将各触发器的驱动方程代入,即得电路的状态方程: ?? ???=+=+==+=+==+=+=+++n n n n n n n n n n n n n n n n n n n n n n n n Q Q Q Q Q Q K Q J Q Q Q Q Q Q Q K Q J Q Q Q Q Q Q Q K Q J Q 202020000100101011111112121222212 (3)计算、列状态表 n n n n n n n n Q Q Y Q Q Q Q Q Q 2 12 100 1 1112=?????===+++ (4)画状态图及时序图

Moore型同步时序逻辑电路的设计与分析

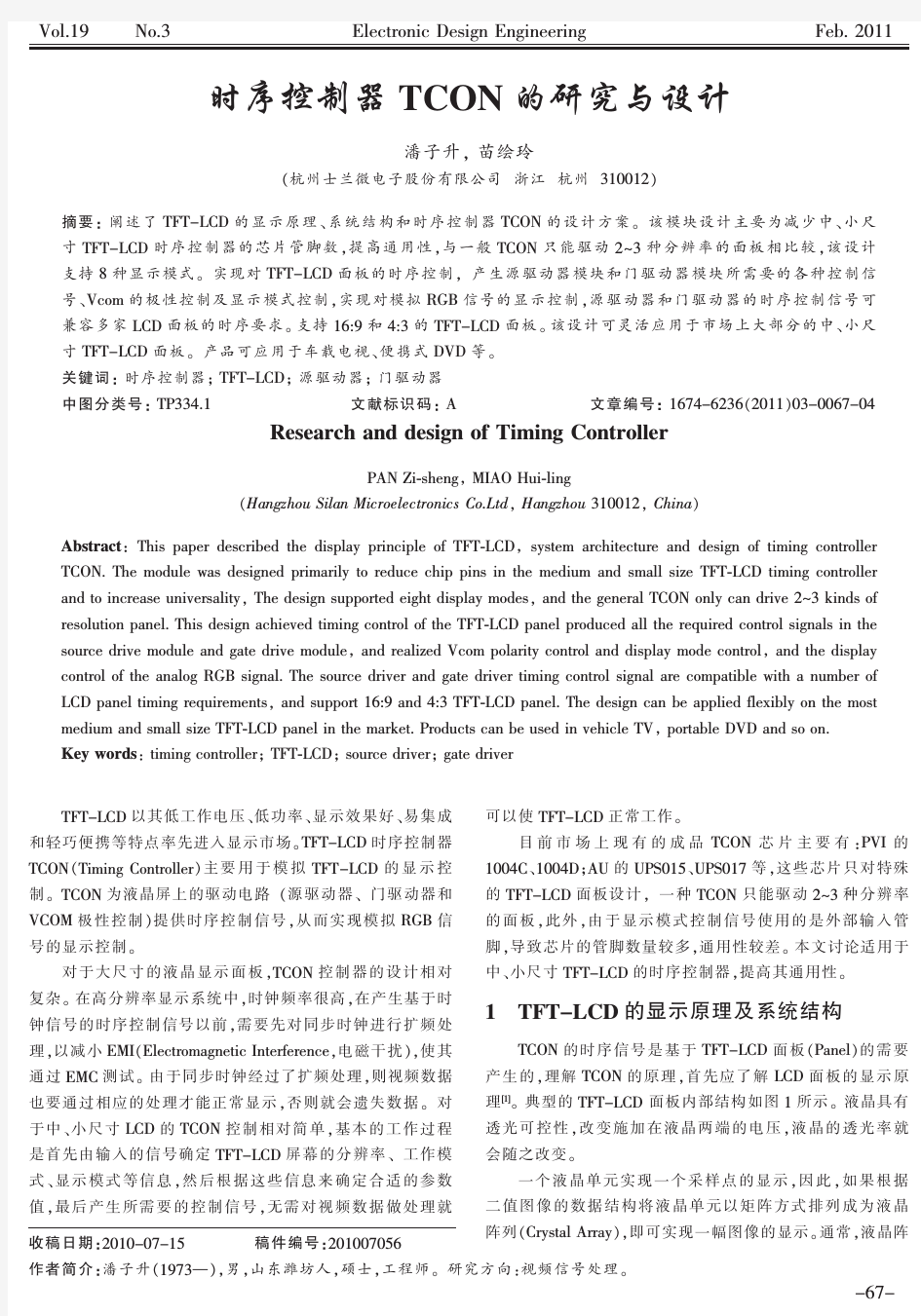

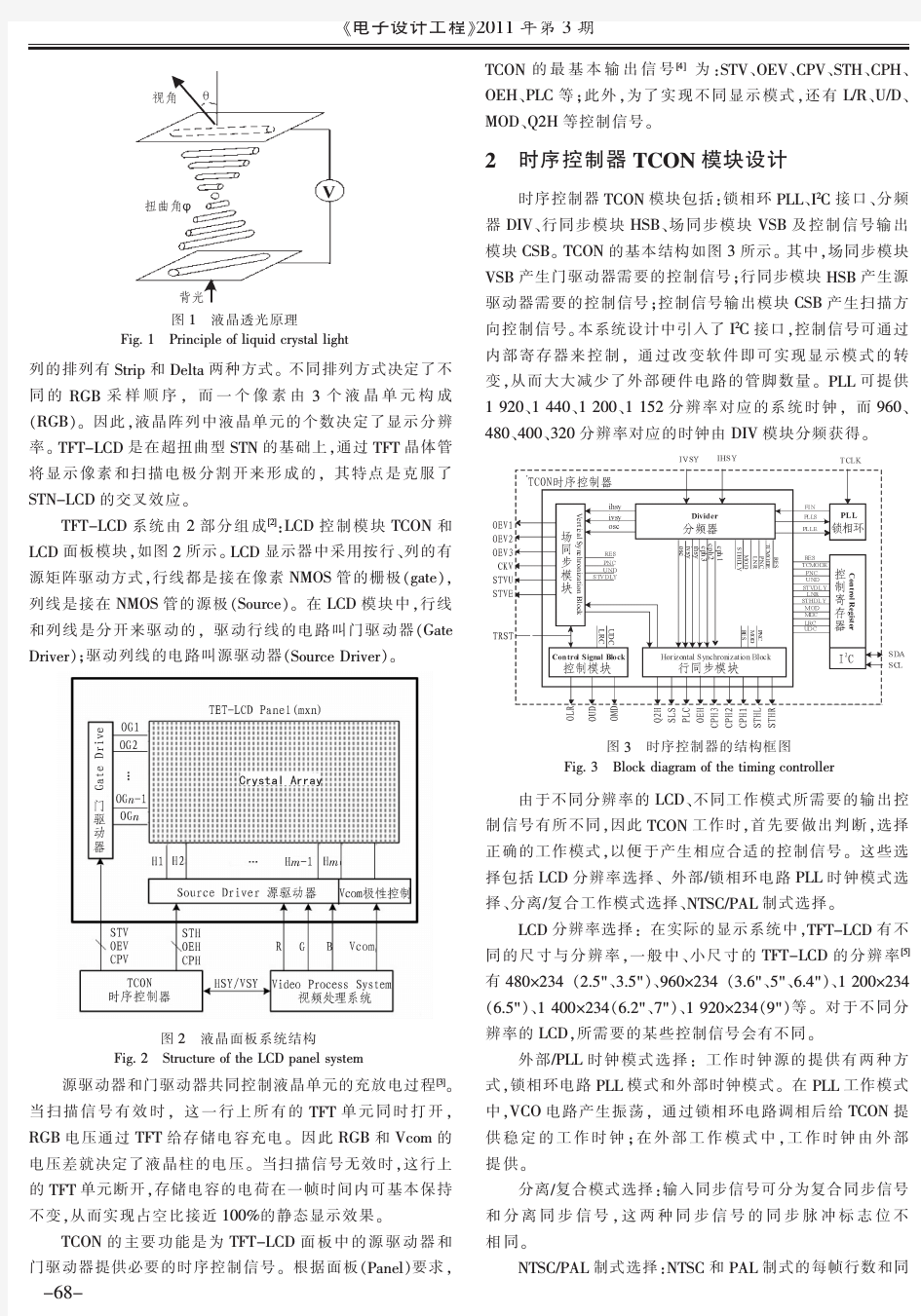

实验九Moore型同步时序逻辑电路的分析与设计 22920132203686 薛清文周2下午实验 一.实验目的: 1.同步时序逻辑电路的分析与设计方法 2.D,JK触发器的特性机器检测方法。 2.掌握时序逻辑电路的测试方法。 3.了解时序电路自启动设计方法。 4.了解同步时序电路状态编码对电路优化作用。 二.实验原理: 二、 1.Moore同步时序逻辑电路的分析方法: 时序逻辑电路的分析,按照电路图(逻辑图),选择芯片,根据芯片管脚,在逻辑图上标明管脚号;搭接电路后,根据电路要求输入时钟信号(单脉冲信号或连续脉冲信号),求出电路的状态转换图或时序图(工作波形),从中分析出电路的功能。 2.Moore同步时序逻辑电路的设计方法: (1)分析题意,求出状态转换图。 (2)状态分析化简:确定等价状态,电路中的等价状态可合并为一个状态。(3)重新确定电路状态数N,求出触发器数n,触发器数按下列公式求:2n-1 一、设计任务与要求 1. 彩灯电路,循环速度肉眼可辨。 2. 可实现2灯循环,3灯循环,…,8灯循环。最少6灯,可扩展成可逆循环。 3. 要求有功能扩展。 二、总体电路设计 1.原理框图 2. 整体设计电路图 3.电路整体分析 本电路大体可分为四部分:时钟信号部分、编译码部分、移位寄存器和彩灯显示部分。555芯片及74LS193产生移位所需时钟并通过分频控制彩灯移动速度,编译码部分控制循环彩灯的个数,移位寄存器74LS194控制彩灯的循环移动,最终通过彩灯显示。 功能实现说明: (1)通过电位器和频率选择开关J12、J13、J14控制彩灯循环移动速度 (2)J1、J2分别接高电平和与非门输出,并把J5与LED8连通,循环右移,拨码开关低(断开)有效,从D0到D7依次实现1-8灯循环, 并且多灯的优先级高于少灯优先级。 (3)J1、J2分别接通与非门输出和高电平,并把J5与LED0连通,循环左移,拨码开关低(断开)有效,从D7到D0依次实现1-8灯循环 并且少灯的优先级高于多灯优先级。 (4)J1、J2都接高电平时置位显示开关状态 (5)J1、J2都接反相器输出时状态保持,相当于暂停循环各部分电路具体的功能实现将在下面讲解。 4. 元件清单 拨码开关×1、拨动开关×6、按键开关×1 八位300Ω排阻×2 555芯片×1 8—3线优先编码器74LS148×1 3-8译码器74LS138×1 16进制计数器74LS193×1 反相器74LS04×1 LED彩灯×16 电阻100k×2、电位器100k×1 电容0.1uF 0.33uF 0.01uF各一 导线等若干 三、单元电路分析 1. 时钟信号部分 (1)555电路构成的多谐振荡器 时序控制器TCON的研究与设计 TFT-LCD以其低工作电压、低功率、显示效果好、易集成和轻巧便携等特点率先进入显示市场。TFT-LCD时序控制器TCON(Timing Contro-ller)主要用于模拟TFt-LCD的显示控制。TCON为液晶屏上的驱动电路(源驱动器、门驱动器和VCOM极性控制)提供时序控制信号,从而实现模拟RGB信号的显示控制。对于大尺寸的液晶显示面板,TCON控制器的设计相对复杂。在高分辨率显示系统中,时钟频率很高,在产生基于时钟信号的时序控制信号以前,需要先对同步时钟进行扩频处理,以减小EMI(Electromagnetic Interference,电磁干扰),使其通过EMC测试。由于同步时钟经过了扩频处理,则视频数据也要通过相应的处理才能正常显示,否则就会遗失数据。对于中、小尺寸LCD的TCON控制相对简单,基本的工作过程是首先由输入的信号确定TFT-LCD屏幕的分辨率、工作模式、显示模式等信息,然后根据这些信息来确定合适的参数值,最后产生所需要的控制信号,无需对视频数据做处理就可以使TFT-LCD正常工作。目前市场上现有的成品TCON芯片主要有:PVI的1004C、1004D;AU 的UPS015、UPS017等,这些芯片只对特殊的TFT-LCD面板设计,一种TCON只能驱动2~3种分辨率的面板,此外,由于显示模式控制信号使用的是外部输入管脚,导致芯片的管脚数量较多,通用性较差。本文讨论适用于中、小尺寸TFT-LCD的时序控制器,提高其通用性。1 TFT-LCD的显示原理及系统结构 TCON的时序信号是基于TFT-LCD面板(Panel)的需要产生的,理解TCON的原理,首先应了解LCD面板的显示原理。典型的TFT-LCD面板内部结构。液晶具有透光可控性,改变施加在液晶两端的电压,液晶的透光率就会随之改变。 一个液晶单元实现一个采样点的显示,因此,如果根据二值图像的数据结构将液晶单元以矩阵方式排列成为液晶阵列(Crystal Array),即可实现一幅图像的显示。通常,液晶阵列的排列有Strip和Delta两种方式。不同排列方式决定了不同的RGB采样顺序,而一个像素由3个液晶单元构成(RGB)。因此,液晶阵列中液晶单元的个数决定了显示分辨率。TFT-LCD 是在超扭曲型STN的基础上,通过TFT晶体管将显示像素和扫描电极分割开来形成的,其特点是克服了STN-LCD的交叉效应。 TFT-LCD系统由2部分组成:LCD控制模块TCON和LCD 面板模块,。LCD显示器中采用按行、列的有源矩阵驱动方式,行线都是接在像素NMOS管的栅极(gate),列线是接在NMOS管的源极(Source)。在LCD模块中,行线和列线是分开来驱动的,驱动行线的电路叫门驱动器(Gate Driver);驱动列线的电路叫源驱动器(Source Driver)。 源驱动器和门驱动器共同控制液晶单元的充放电过程。当扫描信号有效时,这一行上所有的TFT单元同时打开,RGB电压通过TFT给存储电容充电。因此RGB和Vcom的电压差就决定了液晶柱的电压。当扫描信号无效时,这行上的TFT单元断开,存储电容的电荷在一帧时间内可基本保持不变,从而实现占空比接近100%的静态显示效果。 TCON的主要功能是为TFT-LCD面板中的源驱动器和门驱动器提供必要的时序控制信号。根据面板(Panel)要求,TCON的最基本输出信号为:STV、OEV、CPV、STH、CPH、OEH、PLC等;此外,为了实现不同显示模式,还有L/R、U/D、MOD、Q2H等控制信号。2 时序控制器TCON模块设计时序控制器TCON模块包括:锁相环PLL、I2C接口、分频器DIV、行同步模块HSB、场同步模块VSB 及控制信号输出模块CSB。TCON的基本结构。其中,场同步模块VSB产生门驱动器需要的控制信号:行同步模块HSB产生源驱动器需要的控制信号;控制信号输出模块CSB产生扫描方向控制信号。本系统设计中引入了I2C接口,控制信号可通过内部寄存器来控制,通过改变软件即可实现显示模式的转变,从而大大减少了外部硬件电路的管脚数量。PLL可提供1 920、1 440、1 200、1 152分辨率对应的系统时钟,而960、480、400、320分辨率对应的时钟由DIV模块分频获得。 第五章 同步时序逻辑电路的习题 一、基本知识点 1、时序逻辑电路的一般结构 特点:a 、有存储电路(记忆元件);有组合电路(特殊时可没有) b 、包含反馈电路,电路功能与“时序”相关 c 、输出不仅与输入(X )有关,而且与存储状态(Y )有关 分类:(1)Mealy 型 Z =F (X ,Q ) 输出是电路的输入和现态的函数(注意输出与输入有直接关系) (2)Moore 型 Z =F (Q ) 输出仅仅是电路现态的函数(注意输出与输入没有直接关系) 同步时序逻辑电路:各触发器共用同一时钟信号,即电路中各触发器状态的转换时刻在统一时钟信号控制下同步发生。 异步时序逻辑电路:电路没有统一的时钟信号对状态变化进行同步控制,输入信号的变化将直接引起电路状态的变化。 //本课程将较少讨论异步时序逻辑电路 2、同步时序逻辑电路的描述 注意:任一个同步时序逻辑电路的结构和功能可用3组函数表达式完整地描述。 (1)激励函数表达式:存储电路输入Y 与电路输入X 和现态Q 之间的关系 Y =F (X ,Q ) //现态Q 就是上图存储电路原始的输出y k (2)次态函数表达式:电路的次态Q n+1与激励函数Y 和现态Q 之间关系 Q n+1=F (Y ,Q ) //次态Q n+1就是上图存储电路再次触发后的输出y k n+1 (3)输出函数表达式:电路的输出Z 和输入X 和当前现态Q 的关系 Mealy 型 Z =F (X ,Q ) Moore 型 Z =F (Q ) 输入信号 输出信号 X 1 X 2 X n Z 1 Z 2 Z m y s 过去输入 现态 现在输入 } 输出 输出 所有输入 现态 实验二 时序逻辑电路的设计 一、实验目的: 1、 掌握时序逻辑电路的分析方法。 2、 掌握VHDL 设计常用时序逻辑电路的方法。 3、 掌握时序逻辑电路的测试方法。 4、 掌握层次电路设计方法。 5、 理解时序逻辑电路的特点。 二、实验的硬件要求: 1、 EDA/SOPC 实验箱。 2、 计算机。 三、实验原理 1、时序逻辑电路的定义 数字逻辑电路可分为两类:组合逻辑电路和时序逻辑电路。组合逻辑电路中不包含记忆单元(触发器、锁存器等),主要由逻辑门电路构成,电路在任何时刻的输出只和当前时刻的输入有关,而与以前的输入无关。时序电路则是指包含了记忆单元的逻辑电路,其输出不仅跟当前电路的输入有关,还和输入信号作用前电路的状态有关。 2、同步时序逻辑电路的设计方法 同步时序逻辑电路的设计是分析的逆过程,其任务是根据实际逻辑问题的要求,设计出能实现给定逻辑功能的电路。同步时序电路的设计过程: (1)根据给定的逻辑功能建立原始状态图和原始状态表。 ①明确电路的输入条件和相应的输出要求,分别确定输入变量和输出变量的数目和符号; ②找出所有可能的状态和状态转换之间的关系; ③根据原始状态图建立原始状态表; (2)状态化简---求出最简状态图。 合并等价状态,消去多余状态的过程称为状态化简。 等价状态:在相同的输入下有相同的输出,并转换到同一个次态去的两个状态称为等价状态。 (3)状态编码(状态分配)。 给每个状态赋以二进制代码的过程。 根据状态数确定触发器的个数,n n M 221-≤∠(M 为状态数;n 为触发器的个数)。 (4)选择触发器的类型。 (5)求出电路的激励方程和输出方程。 (6)画出逻辑图并检查自启动能力。 3、时序逻辑电路的特点及设计时的注意事项 ①时序逻辑电路与组合逻辑电路相比,输出会延时一个时钟周期。 ②时序逻辑电路一般容易消除“毛刺”。 ③用VHDL 描述时序逻辑电路时,一般只需将时钟信号和异步控制(如异步复位)信号作为敏感信号。 5.2 时序逻辑电路的设计方法 本次重点内容: 1、同步时序逻辑电路的设计方法。 2、异步时序逻辑电路的设计方法。 教学过程 5.2.1 同步时序逻辑电路的设计 一、同步时序逻辑电路的设计方法 设计关键:根据设计要求→确定状态转换的规律→求出各触发器的驱动方程。 设计步骤:(先简单介绍,通过以下的举例后,再进行总结,特别再点出设计关键)1.根据设计要求,设定状态,确定触发器数目和类型。画出状态转换图。 2.状态化简 前提:保证满足逻辑功能要求。 方法:将等价状态(多余的重复状态)合并为一个状态。 3.状态分配,列出状态转换编码表 通常采用自然二进制数进行编码。N为电路的状态数。 每个触发器表示一位二进制数,因此,触发器的数目n可按下式确定 2n≥N>2n–1 4.画状态转换卡诺图,求出状态方程、输出方程 选择触发器的类型(一般可选JKF/F或DF/F,由于JK触发器使用比较灵活,因此,在设计中多选用JK触发器。)将状态方程和触发器的特性方程进行比较→驱动方程。 5.根据驱动方程和输出方程画逻辑图。 6.检查电路有无自启动能力。 如设计的电路存在无效状态时,应检查电路进入无效状态后,能否在时钟脉冲作用下自动返回有效状态工作。如能回到有效状态,则电路有自启动能力;如不能,则需修改设计,使电路具有自启动能力。 二、同步时序逻辑电路的设计举例 [例1] 试设计一个同步七进制加法计数器。 解:设计步骤 (1)根据设计要求,设定状态,画状态转换图。 七进制→7个状态→用S0,S1,…,S6表示 状态转换图如下所示: (2)状态化简。 本例中7个状态都是有效状态。 (3)状态分配,列状态转换编码表。 根据式2n≥N>2n–1,→ N=7,n=3,即采用三个触发器。 选用三位自然二进制加法计数编码→列出状态转换编码表。 (4)选择触发器的类型,求出状态方程,驱动方程和输出方程。根据状态转换编码表→得到各触发器次态和输出函数的卡诺图。得 输出方程为: Y= Q2n Q1n 控制器操作说明书 控制器有四个按键,分别是设定键、上升键、下降键、输入键。 显示数码管分为两行,上排为四位数码管,显示为参数和数值,下排为两位数码管,显示为当前的工作通道。 开始 1:按住设定键3秒以上,上排显示LU(通道设定,本控制器为自动检测输出路数,此参数可不必改动,如果改动,在下次上电即会被改回实际输出路数),按下输入键后,(以下的描述适用于其它的参数改动)上排显示通道设定值。此时可点按上升键或下岗键即可改变设定通道值。改动完后按下输入键,即可保存。如果不想保存可直接按下设定键。上排显示会显示下一参数的名称。 2:上排显示T-E(脉冲间隔时间的分钟参数),按下输入键后,操作同上。参数范围为0分到99分。 3:上排显示T-S(脉冲间隔时间的秒参数),按下输入键后,操作同上。参数范围为1秒到99秒。 4:上排显示S-H(停止时间的小时参数),按下输入键后,操作同上。参数范围为0小时到99小时。 5:上排显示S-E(停止时间的分钟参数),按下输入键后,操作同上。参数范围为0分钟到99分钟。 6:上排显示P-S(脉冲时间参数),按下输入键后,操作同上。参数范围为0.01秒到9.99秒。 7:上排显示SL(级联标志),按下输入键后,上排显示OFF或ON。按下上升键或下降键改变显示,改动完后按下输入键,即可保存。如果不想保存可直接按下设定键。上排显示会显示下一参数的名称。参数范围为OFF(关闭)和ON(打开)。 8:上排显示STAR(级联的主机标志),按下输入键后,上排显示OFF或ON。按下上升键或下降键改变显示,改动完后按下输入键,即可保存。如果不想保存可直接按下设定键。上排显示会显示下一参数的名称。参数范围为OFF(关闭)和ON(打开)。 9:上排显示RST(出厂值恢复标志),按下输入键后,上排显示OFF或ON。按下上升键或下降键改变显示,改动完后按下输入键,即可保存。如果不想保存可直接按下设定键。上排显示会显示下一参数的名称。参数范围为OFF(关闭)和ON(打开)。 10:上排显示LU01---LU12(通道使能标志),按下输入键后,上排显示OFF或ON。按下上升键或下降键改变显示,改动完后按下输入键,即可保存。如果不想保存可直接按下设定键。上排显示会显示下一参数的名称。参数范围为OFF(关闭)和ON(打开)。 11:退出参数设定状态。(如果在没有按动任何按键的12秒时,亦自动退出参数设定状态)。结束 控制器手动控制输出操作方法: 在控制器工作状态下,按住输入键不放,点按一下下降键,上排显示HAND,下排显示第几通道数值,此时按下上升键或下降键改动要测试输出的通道,点按输入键时即可输出电压。 实验十Moore型同步时序逻辑电路的分析与设计 一.实验目的: 1.同步时序逻辑电路的分析与设计方法 2.掌握时序逻辑电路的测试方法。 二.实验原理: 1.Moore同步时序逻辑电路的分析方法: 时序逻辑电路的分析,按照电路图(逻辑图),选择芯片,根据芯片管脚,在逻辑图上标明管脚号;搭接电路后,根据电路要求输入时钟信号(单脉冲信号或连续脉冲信号),求出电路的状态转换图或时序图(工作波形),从中分析出电路的功能。 2.Moore同步时序逻辑电路的设计方法: (1)分析题意,求出状态转换图。 (2)状态分析化简:确定等价状态,电路中的等价状态可合并为一个状态。(3)重新确定电路状态数N,求出触发器数n,触发器数按下列公式求:2n-1 (7)利用卡诺图如图2,求状态方程、驱动方程。 (8)自启动检验:将各无效状态代入状态方程,分析状态转换情况,画出完整的 状态转换图,如图3所示,检查是否能自启动。 时序逻辑电路的设计 一、实验目的 1. 熟悉集成计数器的逻辑功能和各控制端的作用。 2. 掌握计数器的使用方法。 3. 掌握任意进制计数器的设计方法。 4. 了解8421BCD和5421BCD的编码规则。 二、实验器材 集成计数器74LS90、四2输入与非门74LS00、双4输入与非门74LS20、四异或门74LS86、六非门74LS04、显示译码器7447/7448、七段数码管 三、实验任务及要求 1. 设计要求 (1)用1片74LS90和1片与非门设计一个5进制计数器。 (2)用2片74LS90和1片与非门设计一个四十以内(十以上)的任意进制计数器。 2.实验内容 (1)测试所用芯片74LS90的逻辑功能(置0、置9、8421BCD计数输出功能)。(2)组装所设计的时序逻辑电路,并验证其功能是否正确。 提示:计数器的状态输出端分别接在实验箱上的显示译码器的输入端,用七段数码管显示计数状态值。CP接实验箱上的可调连续脉冲。 四、实验原理 1. 74LS90的逻辑功能 74LS90是二-五-十进制异步计数器。 (1)R9(1)=R9(2)=“1”,Q3Q2Q1Q0=1001,置9; (2)R0(1)=R0(2)=“1”,R9(1)‖R9(2)=“0”,Q3Q2Q1Q0=0000,置0; (3)计数脉冲由CP0端输入,输出由Q0端引出,即得二进制计数器; (4)计数脉冲由CP1端输入,输出由Q3,Q2,Q1端引出,即得五进制计数器;(5)将Q0和CP1相连,计数脉冲由CP0端输入,输出由Q3,Q2,Q1,Q0端引出,即得8421BCD码十进制计数器; 2. 时序逻辑电路的基本设计方法 Step 1:明确设计电路功能,作出基于功能涉及到的所有编码排序的状态转换图;Step 2:判断电路是否有输入或输出变量,并根据状态转换图画出状态转换表; Step 3:根据状态转换表,分离出各触发器输出量Q 0~Q m (m=1、2、3…)、输出 变量Y的卡诺图并化简,得到各个触发器的状态方程; 时序控制器操作說明 一、 用途 顺序时间控制器是用于使用阀针式热流道系统时,用以控制模具热咀注塑时间先后的设备。 顺序时间控制器能使热流道系统的各个浇口得以控制,具有以下优势: ·使成形产品表面引发瑕疵的熔接痕消除,或重新设置产品表面熔接痕的位置,从而达到改善成形产品的质量; ·通过对每一个浇口的注射量的调节,达到改善品质,以防产品瑕疵出现或产品填充未到位等现象的发生; ·受时间控制器的控制,所有的浇口并不是同时开放,故注塑可在最小锁模力的情况下进行; ·通过浇口处注射率的提高,使产品流痕达到最佳状态。 二、电源配置 主电源输入单相交流电95-240VAC 50/60HZ 注射信号输入直流24VDC、交流110V/220V、开 关信号可选 电磁阀电压直流24VDC、交流110V/220V、 操作温度范围(-10 - +50度) PCB结构 1.PCB主板 2.显示PCB板时间控制器电源 注塑信号输入,注射信号输出。切换信号输入,状态显示。 三、面板操作說明 A —蜂鸣器 B —A模式指示灯 C —B模式指示灯 D —显示关闭时间 E —显示开启时间 F —关闭指示灯 G —打开指示灯 H —待机指示灯 J —设定值调节功能键(上) K —设定值调节功能键(下) I —手动键 L —参数设置键 M —电源开关键 N —模式信息对照表 二.时序控制器操作步骤。 1.按ON/OFF键打开时序控制卡电源, 2.功能参数设置, 1>A/B模式设置 按住MODE SET键1秒进入参数设置,上端显示器会显示A-B,下端显示器显示模式A或B,通过按上键或下键可调整为B模式或A模式;按按住MODE SET 键1秒可退出参数设置。 第1题: 设计一个串行数据检测器,对它的要求是:连续输入3个或3个以上的1时输出为1,其他输入情况下输出为0。 答案 输入数据作为输入变量,用X 表示;检测结果为输出变量,用Y 表示。 设电路没有输入1以前的状态为0S ,输入一个1状态为1S ,连续输入两个1后的状态为2S ,连续输入3个1以后的状态为3S 。状态转换图为: 求得触发器的输入方程为:X K XQ J ==101; 1;010==K Q X J 输出方程:1XQ Y = 画出逻辑图 第2题: 试用JK 触发器和门电路设计一个同步七进制计数器。 答案 因为七进制计数器需要有7个不同的状态,所以需要用三个触发器组成。根据题目要求画出状态转换图: 卡诺图为: 从卡诺图得到的状态方程为: 驱动方程为: 设计得到的逻辑电路图为: 第3题:设计一“011”序列检测器,每当输入011码时,对应最后一个1,电路输出为1。答案 画出原始状态图(或称转移图) 输入端X:输入一串行随机信号 输出端Z:当X出现011序列时,Z=1;否则Z=0 选用T 触发器 表达式为: T 触发器的驱动方程为: 第4题: 用JK 触发器设计时序逻辑电路,状态表如下所示: n n Q Q 01 Y Q Q n n /1 11++ A=0 A=1 00 01/0 11/0 01 10/0 00/0 10 11/0 01/0 11 00/1 10/1 答案 所要设计的电路由4个状态,需要用两个JK 触发器实现,求得JK 触发器的激励方程为:100==K J 011Q A K J ⊕== 输出方程:01Q Q Y = 由输出方程和激励方程画电路 A B C D 1/0 0/0 0/0 1/1 0/0 0/0 1/0 1/0 011XQ Q T +=000XQ Q X T +=0 1Q XQ Z =011XQ Q T +=0 00XQ Q X T +=0 1Q XQ Z = “电工学(二)数字逻辑电路”课程实验报告 实验/实训项目同步时序逻辑电路分析与设计 实验/实训地点 实验/实训小组 实验/实训时间 专业电器工程及其自动化 班级 姓名 学号 指导老师 过程、步骤、代一、实验原理 1. 集成计数器74LS290功能测试。 74LS290是二一五一十进制异步计数器,逻辑简图为图5.1所示。 74LS290具有下述功能: 直接置0(R 0(1),R 0(2)=1),直接置(S 0(1),S 0(2)=1) 二进制计数(CP 1输入Q A 输出) 五进制计数(CP 1输入Q A Q B Q C 输出) 十进制计数(两种接法如图5.2A 、B 所示) 按芯片引脚图分别测试上述功能,并填入表5.1、表5.2、表5.3中。 图5.1 74LS290逻辑图 图5.2 十进制计数器 2. 计数器级连 分别用2片74LS290计数器级连成二一五混合进制、十进制计数器。 (1)画出连线电路图。 (2)按图接线,并将输出端接到LED 数码显示器的相应输入端,用单脉冲作为输入脉冲验证设计是否正确。 (3)画出四位十进制计数器连接图并总结多级计数级连规律。 3. 任意进制计数器设计方法 采用脉冲反馈法(称复位法或置位法),可用74LS290组成任意(M )计数器,图5.3是用74LS290实现模7计数器的两种方案,图(A )采用复位法,即计到M 异步置0,图(B )采用置位法,即计数计到M-1异步置0。 表5.1 功能表 R 0(1) R 0(2) S 0(1) S 0(2) 输出 Q D Q G Q B Q A H H L X H H X L X X H H X L X L L X X L X L L X 表5.2 二一五混合时制 计数 输出 Q A Q D Q G Q B 0 1 2 3 4 5 6 7 8 9 实验二时序电路设计 一. 实验内容 使用Verilog语言完成一个时序电路模块的RTL设计,并为这个模块设计一个简单的testbench 文件,并用ncverilog完成仿真过程,用拷屏的方法,完成WORD格式的实验报告,记录仿真结果的波形输出。 二. 时序电路模块设计要求 (1)滤波器电路设计 使用一个乘法器和一个加法器,设计完成一个五阶数字滤波器的设计,输入为串行数据X,复位信号RST,时钟信号CLK,使能信号EN,输出为串行数据信号Y,数据输出有效信号OEN。数字滤波器公式为: y(i) = a0+ a1*x(i-1)+ a2*x(i-2)+ a3*x(i-3)+ a4*x(i-4)+ a5*x(i-5) 其中: a0=0.08 a1=0.13 a2=0.23 a3=0.14 a4=0.16 a5=0.26 用Verilog语言为这个滤波器设计一个testbench,要求输入激励X为随机数据输入。(2)接口设计 为上述设计一个外部接口,可以通过该接口对滤波器的系数a0~ a5进行改写,在上述testbench基础上,完成滤波器系数配置的配置验证,系数配置如下: a0=0.20 a1=0.04 a2=0.08 a3=0.20 a4=0.16 a5=0.32 三. 实验过程 (1)分析滤波器程序需要的模块: 1)根据滤波器的公式,得知该程序需要一个乘法器模块2)i时刻输出与前5个时刻的输入有关,因此需要6个寄存器用来保存x输入的值3)i时刻输出完成了5次乘法5次加法,因此需要一个变频器产生一个5倍频的时钟4)需要定义五个状态,每个状态实现相应的乘法和加法操作。 (2)在给定a的5个值时出现一个问题,小数如何用二进制表示: 将滤波器公式左右同时乘以2的八次方,即所有的二进制数值左移八位,此时系数均四舍五入保留整数位,转换成二进制形式即可。将最终的计算结果高八位赋值给y即为滤波器的 5.1.3 操作控制器与时序产生器 CPU中有多个寄存器,每一个完成一种特定的功能。然而信息怎样才能在各寄存器之间传送呢?又由何种部件控制信息数据的传送呢?本小节介绍这方面的问题。 寄存器之间传送信息的通路,称为数据通路。信息从什么地方开始,中间经过哪个寄存器或多路开关,最后传送到哪个寄存器,都要加以控制。在各寄存器之间建立数据通路的任务,是由称为操作控制器的部件来完成的。 所谓操作控制器,就是根据指令操作码和时序信号,产生各种操作控制信号,以便正确地建立数据通路,从而完成取指令和执行指令的控制的部件。 操作控制器根据设计方法不同可分为:硬布线控制器、微程序控制器和门阵列控制器等三种。硬布线控制器,它是采用组合逻辑技术来实现的操作控制器;微程序控制器,它是采用存储逻辑来实现的操作控制器;门阵列控制器是吸收前两种设计思想,即逻辑技术和存储逻辑技术相结合的操作控制器。本书重点介绍微程序控制器。操作控制器产生的控制信号必须定时,还必须有时序产生器。因为计算机高速地进行工作,每一个动作的时间是非常严格的,不能有任何差错。时序产生器的作用,就是对各种操作实施时间上的控制。 CPU 中除了上述组成部分外,还有中断系统、总线接口等其他功能部件,这些内容将在以后各章中陆续展开。 综上所述,CPU 是由控制器组成的,控制器控制计算机运行,而运算器完成对操作数据的加工处理,一个典型的CPU具有:多个通用寄存器,用来保存CPU运行时所需的各类数据信息或运行状态信息;算术逻辑运算单元(ALU),对寄存器中的数据进行加工处理;操作控制器,产生各种操作控制信号,以便在各寄存器之间建立数据通路;时序产生器,对各种操作控制信号进行定时,以便进行时间上的约束。 实验二时序电路的设计及显示 一、实验目的: 1.了解教学系统中8位八段数码管显示模块的工作原理,设计标准扫描驱动电路模块,以备后面实验调用。 2.会电路图输入方法和VHDL语言方法输入的混合使用。 二、硬件要求: 1.GW48EDA/SOPC+PK2实验系统。 三、实验内容及预习要求: 1.计数器(counter): 计数器(counter)是数字系统中常用的时序电路,因为计数是数字系统的基本操作之一。计数器在控制信号下计数,可以带复位和置位信号。因此,按照复位、置位与时钟信号是否同步可以将计数器分为同步计数器和异步计数器两种基本类型,每一种计数器又可以分为进行加计数和进行减计数两种。在VHDL描述中,加减计数用“+”和“-”表示即可。 (1)同步计数器: 同步计数器与其它同步时序电路一样,复位和置位信号都与时钟信号同步,在时钟沿跳变时进行复位和置位操作。例2-1为带时钟使能的同步4位二进制减法计数器的VHDL模型: count是一个带时钟使能的同步4位二进制减法计数器,计数范围F~0。每当时钟信号或者复位信号有跳变时激活进程。如果此时复位信号clr有效(高电平),计数器被复位,输出计数结果为0;如果复位信号无效(低电平),而时钟信号clk出现上升沿,并且计数器的计数使能控制信号en有效(高电平),则计数器count自动减1,实现减计数功能。图S2-1为带时钟使能的同步4位二进制减法计数器的仿真波形图: 图S2-1 带时钟使能的同步4位二进制减法计数器的仿真图形 引脚锁定: 工作模式:模式1 clk0:4HZ clk2: 8HZ clk0:4096HZ (2)异步计数器 同样的道理,异步计数器是指计数器的复位、置位与时钟不同步。例2-2为带时钟使能的异步4位二进制加法计数器的VHDL模型: counta是一个带时钟使能的异步4位二进制加法计数器,计数范围0~F。每当时钟信号或者复位信号有跳变时激活进程。如果此时复位信号clr有效(高电平),计数器被复位,输出计数结果为0;如果复位信号无效(低电平),而时钟信号clk出现上升沿,并且计数器的计数使能控制信号en有效(高电平),则计数器count自动加1,实现加计数功能。图S2-2为带时钟使能的异步4位二进制加法计数器的仿真波形图: Sequence Injection Controller Version 5.5 Sequence Injection Controller INSTRUCTION MANUAL TYPE ACT-D800 Thank you for using YUDO production 感谢贵公司使用 YUDO 产品 Contents 目录 1、Environments ……………………………………………………2使用环境 2、Composition of Control Module ……… …………………………2PCB 结构 3、Central Processing Unit ……………………………………………2主要控制装置 4、Input ………………………………………………………………2输入因素 5、Display ……………………………………………………………3显示因素 6、Output ………………………………………………………………3输出因素 7、Start to Run…………………………………………………………4使用说明 8、Menu Setting (5) 动态说明 9、Mode Specification ………………………………………………7模式规格 10、System Application ………………………………………………8系统应用程序 11、Wiring Specification (9) 外部线连接图 Before using the product ,please read this instruction manual carefully to avoid any damage due to improper usage. If you have any questions, please do not hesitate to contact our Head Office or YUDO Territory Sales Branch. 使用本产品前,敬请仔细阅读此手册,以免在操作过程中的失误。如有任何疑问,敬请与柳道公司总部联系或柳道所在地分公司联系。时序电路设计实验

时序控制器TCON的研究与设计

同步时序逻辑电路的习题 数字逻辑

实验二 时序逻辑电路的设计[1]

时序逻辑电路的设计方法

时序控制器操作说明书

实验十 Moore型同步时序逻辑电路的分析与设计

时序逻辑电路设计

时序控制器说明书

时序逻辑电路设计题

同步时序逻辑电路分析与设计

时序电路设计

操作控制器与时序产生器

时序电路的设计及显示

YUDO时序控制器说明书