Current-Sense Transformer Application Design Guidelines

Current-Sense Transformer Application Design Guidelines

By Ariel General

Applications Engineer, Datatronic Distribution Inc.

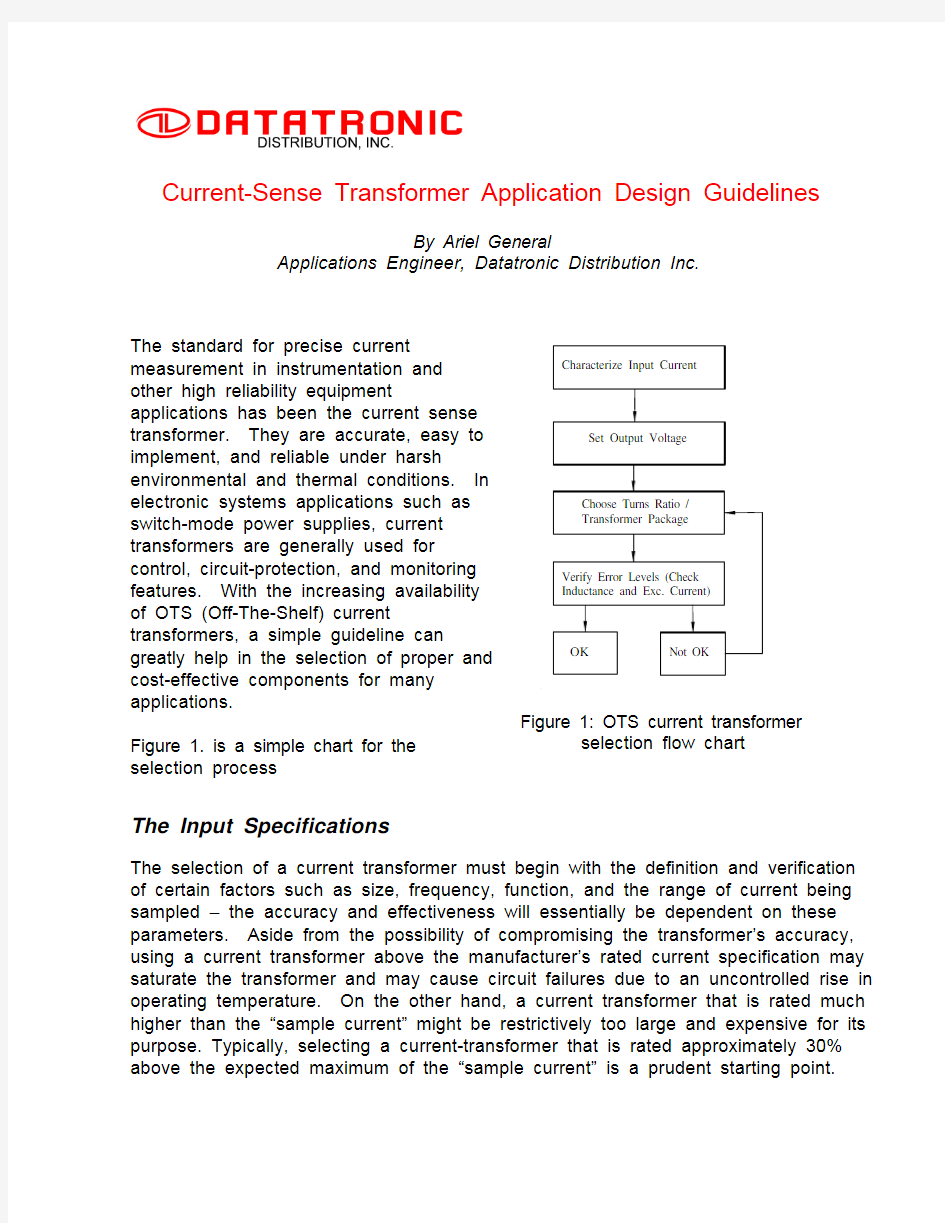

The standard for precise current measurement in instrumentation and other high reliability equipment applications has been the current sense transformer. They are accurate, easy to implement, and reliable under harsh environmental and thermal conditions. In electronic systems applications such as switch-mode power supplies, current transformers are generally used for control, circuit-protection, and monitoring features. With the increasing availability of OTS (Off-The-Shelf) current transformers, a simple guideline can greatly help in the selection of proper and cost-effective components for many applications.

Figure 1. is a simple chart for the selection process

Figure 1: OTS current transformer selection flow chart

The Input Specifications

The selection of a current transformer must begin with the definition and verification of certain factors such as size, frequency, function, and the range of current being sampled – the accuracy and effectiveness will essentially be dependent on these parameters. Aside from the possibility of compromising the transformer’s accuracy, using a current transformer above the manufacturer’s rated current specification may saturate the transformer and may cause circuit failures due to an uncontrolled rise in operating temperature. On the other hand, a current transformer that is rated much higher than the “sample current” might be restrictively too large and expensive for its purpose. Typically, selecting a current-transformer that is rated approximately 30% above the expected maximum of the “sample current” is a prudent starting point.

The Primary/Secondary Turns Ratio

Off the shelf current-transformers commonly have turns ratios ranging from 1:10 to 1:1000. The higher the turns ratio (r = N sec /N pri ), the higher the resolution of the current measurement. However, care must be taken as too high of a turns ratio will necessitate an increase in distributed capacitance and leakage inductance which may decrease the transformer’s accuracy and capability to operate at higher frequencies (due to self-resonance). However, if the number of turns is too low (lower inductance), the output signal may distort or “droop” (in positively sloped unipolar input signal) which may also cause instability in the control circuit and inaccuracies in measurements.

Inductance and Excitation Current

The current transformer’s secondary inductance will determine the fidelity of the output signal. The value of inductance is inversely proportional to the excitation current – which is then subtracted to the “sensed current.”

The excitation current should be several times less than the magnitude of the sample current (a maximum of 10% is ideal for most SMPS applications) – this will ensure the maximum error tolerance of the transformer. For instance, if a circuit has to maintain a maximum of 10% loss for a sample current of 1 A to 20 A at 100 kHz, the excitation current must be set to a maximum of 100 mA (10% of the minimum sample current value). A 1 A sample current will yield an error of 10% while a 20 A sample will yield an error of 0.5%.

In case the excitation current is not specified in the manufacturer’s data sheet, it can be calculated with the equation:

dt

dI L e ?=; L

e dt dI = Where e is the set output voltage (V), L is the inductance (H), and │dI/dt │ is the excitation current w/ respect to time (A/s).

The Output Voltage and “Burden Resistor”

The output voltage (Vo) should be set as low as practically possible to minimize the insertion loss. Assuming 0.5 V is the optimum secondary output voltage in a circuit and the output current is 20 A, a 1:100 ratio transformer will yield a secondary current of ? 200 mA. Per Figure 2, the burden resistor should be:

===5.0Vo Ro 2.5 ? Practical Example

Definition of Requirements:

Input Current: 100 kHz, 1A – 5A

Output Voltage: 0.1 V → 1 A

0.5 V → 5 A

@ 10% accuracy

Package: low-profile, surface-mount

Part Selection:

Using Datatronics’ standard OTS catalog on their website, the CT317-100 current transformer satisfies the input current and package requirements – only the accuracy level and burden resistance are left to be determined.

Error Level Approximation:

For 10% Error (neglecting coupling losses), the primary excitation current must be less than 10% of the minimum input current – a maximum of 100 mA in this case;

I exc (SEC) ? 1/f * e/L

? 1/100 kHz * 0.1/(2.5 mH)

? 0.4 mA

This yields an approximate current of 40 mA on the primary, 60 mA less than the 100 mA maximum.

Burden Resistor Calculation:

Ro = Vo/Isec = 0.1V / (1A/100) = 10?

For the given requirement, the Datatronics CT317-100 is an acceptable selection. Conclusion

OTS components are inexpensive and instantly available, but as discussed in this article, there are functional limitations on their usage. There are applications where specific recommendations or even full customization may be required. It is therefore advisable to procure these components from reputable manufacturers that have strong engineering, manufacturing, and customer service capabilities. References

Billings, Keith H., Switchmode Power Supply Handbook – 2nd ed., McGraw-Hill, New York, 1999.

McLyman, Colonel Wm. T., Transformer and Inductor Design Handbook, Marcel Dekker, New York, 1978.

解读高速数模转换器(DAC)的建立和保持时间

解读高速数/模转换器(DAC)的建立和保持时间Oct 10, 2007 摘要:本应用笔记定义了高速数/模转换器(DAC)的建立和保持时间,并给出了相应的图例。高速DAC的这两个参数通常定义为“正、负”值,了解它们与数据瞬态特性之间的关系是一个难点,为了解决这些难题,本文提供了一些图例。 介绍 为了达到高速数/模转换器(DAC)的最佳性能,需要严格满足数字信号的时序要求。随着时钟频率的提高,数字接口的建立和保持时间成为系统设计人员需要重点关注的参数。本应用笔记对建立和保持时间进行详尽说明,因为这些参数与Maxim的高性能数据转换方案密切相关。 定义建立和保持时间 建立时间(t S)是相对于DAC时钟跳变,数据必须达到有效的逻辑电平的时间。保持时间(t H)则定义了器件捕获/采样数据后允许数据发生变化的时间。图1给出了相对于时钟上升沿的建立和保持时间。特定器件的时钟信号有效边沿可能是上升/下降沿,或由用户选择,例如MAX5895 16位、500Msps、插值和调制双通道DAC,CMOS输入。 图1. 相对于时钟信号上升沿的建立和保持时间 采用CMOS技术设计的数字电路通常将电源摆幅的中间值作为切换点。因此,时间参考点定在信号边沿的中点。图1波形标明了器件在典型条件下的建立和保持时间。注意此时定义的这两个参数均为正值,但在建立或保持时间出现负值时将会令人迷惑不解。 MAX5891 600Msps、16位DAC为这一中间值状态提供了很好的学习实例。该器件的建立时间为-1.5ns,而保持时间为2.6ns。图2给出MAX5891的最小建立时间。注意,实际应用中,数据通常在采样时钟跳变后发生变化。图3给出了相同器件的最小保持时间。

用CMOS技术实现高速模数转换器

用CMOS技术实现高速模数转换器 通信用接收器的发展趋势是必需在信号刚一进入接收器信号通道时就进行取样,并配备有精确的测试仪,而要达到这个目标就要依赖超高速模拟数字转换器来实现。美国国家半导体首推的 ADC081000 芯片是一款模拟输入带宽高达 1.8 GHz 的 8 位 1GSPS 模拟数字转换器,它采用 0.18 微米 (mm) 的互补金属氧化半导体 (CMOS) 工艺技术制造。下文简述了结构及动作的原理,并较详细介绍了上文提到的在动作过程中起什么重要作用。 环顾目前的市场,大部分超高速模拟数字转换器都采用双极互补金属氧化半导体 (BiCMOS) 工艺技术制造,因此 ADC081000 芯片是市场上第一款完全采用 CMOS 技术制造的模拟数字转换器产品。由于双极晶体管的补偿电压比 CMOS 晶体管低,而增益则较高,因此工程师一向喜欢采用双极芯片设计模拟数字转换器前端,例如取样及保持放大器等信号调节电路。对于需要支持高频率操作的系统来说,双极芯片尤其受工程师欢迎。但双极芯片的缺点是需要较高的供电,其功耗远比采用 CMOS 技术的同类芯片大。ADC081000 芯片的实际功耗只有 1W 左右。相比之下,市场上功耗最低的 BiCMOS 模拟数字转换器则耗用超过 3W 的功率。要装设怎样的散热器才可将如此大量的热量全部散发?这却是一个令人极为头痛的问题。ADC081000 芯片不但性能卓越,而且符合通信系统及高性能测试仪表所需的动态规格,可提供 7 以上的有效位数 (ENOB),远超尼奎斯特(nyquist)的规定。 结构及运作原理 高速模拟数字转换器有多种结构可供选择,其中以快闪式、流水线式或折叠/内插式等三种最受欢迎。采用快闪式及折叠/内插式的结构可让数字 CMOS 工艺发挥更大的灵活性。折叠式模拟数字转换器的优点是速度快,而且所需的比较器比快闪式模拟数字转换器少。内插式模拟数字转换器则只需极少量输入放大器,而且所需的输入电容也较低。我们所知的折叠/内插式结构便是这两种技术的集成,其优点是管芯体积较小、功耗较低、而动态性能又很高,因此 ADC081000 芯片便采用这种结构,图 1 所示的就是这款芯片的结构框图。 1GSPS 的速度提供足够的计时时间: 以 ADC081000 这类高速、高性能的集成电路来说,它们所需的时钟信号绝对不能附随任何噪音,以确保外部时钟不会将不受欢迎的噪音带进系统,影响系统的整体动态性能。ADC081000 芯片所需的时钟必须属于低相位噪音 (低抖动) 时钟,而且必须能以千兆赫 (GHz) 以上的频率操作。传统的石英振荡器虽然可以提供低抖动的时钟信号,但市场上只有极少石英振荡器能提供振荡频率超过几百兆赫 (MHz) 的时钟信号。为了确保振荡频率及低相位噪音符合要求,我们可以采用高频率压控振荡器 (VCO)、锁相环路 (PLL) 及石英振荡器,并按图 2 所示的设计将之集成一体,这是目前最佳的方法。

高精度数模转换器

选择和使用高精度数模转换器 时间:2011-05-10 23:17:40 来源:作者:叶子 很多应用 (包括精密仪器、工业自动化、医疗设备和自动测试设备) 都需要高准确度数模转换。在 16 位分辨率时要求准确度好于约±15ppm 或±1LSB 的电路中,设计师传统上一直被迫使用大量校准,以在所有情况下保持准确度。新型高精度 DAC 使得能够采用一个单片式 DAC 来实现±4ppm 准确度或±1LSB (在 18 位分辨率条件下),而无需校准。在本文中我们将对高精度数模转换器的选择和使用过程中所涉及的问题进行研究。 DAC 的架构对于 DAC 的技术规格及其对电路板设计师的要求均有影响。为了实现最佳性能,需要谨慎地考虑 DAC 上的电源、基准和输出放大器所产生的影响。 过采样或增量累加 DAC 过采样或ΔΣ ADC 采用一个低分辨率 DAC (通常仅 1 位),在其前后分别布设一个噪声整形数字调制器和一个模拟低通滤波器。最准确的商用增量累加 DAC 实现±15ppm 的准确度,但是需要 15ms 才能稳定,并要承受相对较高的 1μV/√Hz 噪声密度。其它可购得的过采样 DAC 在 80us 内稳定,但是INL 较差,大约为 240 ppm。 合成 DAC 通过结合两个较低分辨率的单片 DAC,有可能构成一个高分辨率的合成 DAC。请注意,粗略 DAC 的分辨率和精细 DAC 的范围需要重叠,以确保所有想要的输出电压都可实现。粗略 DAC 的准确度和漂移一般将限制合成 DAC 的最终准确度,因此要提高准确度,就需要对合成 DAC 转移函数的特性和软件进行校正。也可能需要频率校准,以校正随温度、时间、湿度和机械压力产生的变化导致的漂移。 电阻串 DAC 电阻串 DAC 采用具有 2N 个分接点的一系列电阻分压器,以实现 N 位分辨率。采用电阻串架构的单片 16 位 DAC 一般含有一个较低分辨率的电阻串 DAC 和一个范围较小的 DAC,范围较小的 DAC 用于插入串器件之间,以实现 16 位分辨率。这种串+内插器方法的一个优点是,DAC 输出具有固有的单调性,无需微调或校准。 这类 DAC 的基准输入阻抗一般很高 (50KΩ~ 300kΩ),而且不受输入代码的影响,从而有可能使用一个非缓冲型基准。因为电阻串的输出阻抗随输入代码变化,所以大多数电阻串 DAC 含有集成的输出缓冲器放大器,以驱动电阻性负载。 尽管电阻串 DAC 的 DNL 本身非常好,但是 INL 由串联电阻器件的匹配决定,而且可能由于含有大量的独立器件而难以控制。直到最近,这类 DAC 的准确度一直限制在约±180ppm。最近的进步已经使得准确度提高到了±60ppm。例如,LTC2656 在 4mm x 5mm 封装中集成了 8 个 DAC 通道,在 16 位分辨率时具有±4LSB 的最大 INL。 阻性梯形或 R-2R 型 DAC 阻性梯形或 R-2R DAC 采用一种类似于图 2 所示的三端子结构,电阻器在 A 端和 B 端之间切换。请注意,A 端和 B 端上的阻抗与代码的相关性很高,而 C 端则具有一个固定阻抗。电阻器与开关的匹配情况将会影响这种结构的单调性和准确度。此类 DAC 一般经过修整或在出厂时经过校准,而且,具±1LSB INL 和 DNL 的单调 16 位阻性梯形电路 DAC 上市已有很长时间了。 电压输出 R-2R DAC 一种常见类型的 R-2R DAC 将C 端用作 DAC 输出电压,而 A 端连接到基准,B 端连接到地。输出阻抗相对于输入代码是恒定的,从而有可能以非缓冲方式驱动电阻负载。例如,LTC2641 16 位 DAC 能以非缓冲方式驱动 60kΩ负载,同时保持±1LSB 的 INL 和 DNL,并消耗不到 200μA 的电源电流。 这种方法的一个缺点是,基准阻抗随着输入代码大幅变化。由于 R-2R 梯形电路的本质,甚至DAC 输出电压中很小的变化也可能在基准电流中引起 1mA 或更大的阶跃变化。为此,必须由一个高性能放

Excel--手把手教你转换出中文大写金额

手把手教你转换出中文大写金额 大家在使用Excel的时候,是否会遇到要把一个或一些阿拉伯数字转换成中文大写金额的计算要求呢?如果只是偶尔需要对少数几个数字进行转换,干脆手工操作啦,但如果要进行转换的数字较多或经常要转换时,该怎么办呢?一向无往不胜的Excel能为你做些什么呢?其实,这个不难,最少有三种方法可以实现。 一、设置单元格格式: 用这个办法能直接将阿拉伯数字转换成中文大写金额,而且操作简单。右击需要转换的单元格,在弹出的快捷菜单中选择“单元格格式”,然后在“数字”选项卡中选择“自定义”,在“类型”中写入“[DBNum2]G/通用格式"元"”后按确定即可。瞧,321是不是已经变成了“叁佰贰拾壹元”了? 可惜的是,这个办法只能处理整数,而对带有小数的数字无能为力。当然也有过朋友通过对此法进行一定的扩展而可以处理部分带小数的数字,但效果不是很理想。 二、利用公式进行转换: 所谓“自力更生,丰衣足食”,这第三种方法就是自己编写公式进行转换。 为了照顾一些Excel初学者,我们先来了解一下什么是Excel里的公式与函数。Excel之所以计算功能异常强大,百分之八十的功劳就在于用户可以创建公式进行计算。所谓公式,实际上就是一个计算

表达式(通常是包含函数与单元格引用的计算表达式)。在Excel里,以“=”作为公式的标志,在任何一个非文本值类型的单元格内,只要以“=”开头,就必定是Excel公式,举一最简单的例子:如果A1、B1单元格的值为别为1和2,那么如果在C3单元格内输入“=A1+B1”,则Excel会自动将A1和B1的值相加,得到数值3,再返回给C3单元格。 再来说函数,函数其实就是包装好的公式,它能根据你提供的参数自动进行复杂的计算,从而最大限度地减轻你的工作量。Excel内置了大量具备各种功能的函数,而且Excel还允许用户自己添加函数,这样一来,在Excel里几乎没有计算不出来的东西了。拿Excel中较常用到的SUM函数来说,如果要计算从A1到A100单元格的数值总和,写公式时是用不着写成“=A1+A2+A3+……A100”的,而只是简单地写成“=SUM(A1:A10)”就可以了。 Excel中有上百种函数,今天我们只讲我们将要用到的几个。其实所有这些函数的功能及详细用法在Excel帮助文件里都有介绍,当你遇到具体计算要求时,只要你点击常用工具栏中“粘贴函数”按钮,Excel会将所有的函数一一展示在你眼前,结合相应的帮助文件,你可以迅速挑选到一个适合你的函数。 1、IF函数 这是Excel里最常用到的函数之一,它的功能是执行真假值判断,根据逻辑测试的真假值返回不同的结果。其语法为IF(判断表达式,当条件值为真时返回的值,当条件值为假时返回的值)。通俗地说,

高精度数模转换器AD420及其与MSP430的接口技术

高精度数模转换器AD420及其与MSP430的接口技术 1 概述 AD420是ADI公司生产的高精度、低功耗全数字电流环输出转换器。AD420的输出信号可以是电流信号,也可以是电压信号。其中电流信号的输出范围为4mA~20mA,0mA~20mA或0mA~24mA,具体可通过引脚RANGE SELECTl,RANGE SELECT2进行配置。当需要输出电压信号时,它也能从一个隔离引脚提供电压输出,这时需外接一个缓冲放大器,可输出0V~5V,0V~10V,±5V或±10V电压。 AD420具有灵活的串行数字接口(最大速率可达3.3 Mb/s),使用方便、性价比高、抑制干扰能力强,非常适合用于高精度远程控制系统。AD420与单片机的接口方式有2种:3线制和异步制。单片机系统通过AD420可实现连续的模拟量输出。其主要特点如下: ?宽泛的电源电压范围为12 V~32 V,输出电压范围为0V~-2.5 V; ?带有3线模式的SPI或Microwire接口,可采集连续的模拟输入信号,采用异步模式时仅需少量的信号线; ?数据输出引脚可将多个AD420器件连接成菊链型; ?上电初始化时,其输出最小值为0 mA,4 mA或O V; ?具有异步清零引脚,可将输出复位至最小值(0mA、4 mA或0V); ?BOOST引脚可连接一个外部晶体管来吸收回路电流,降低功耗; ?只需外接少量的外部器件,就能达到较高的精度。 AD420采用24引脚SOIC和PDIP封装,表1是其引脚功能说明。

2 工作原理 在AD420中,二阶调节器用于保持最小死区。从调节器发出的单字节流控制开关电流源,两个连续的电阻电容装置进行过滤。电容为电流输出额外增加的器件。输出电流则简单显示为4 mA~20 mA,OmA~20mA或0mA~24mA。AD420采用BiCMOS工艺,能够适合高性能的低电压数字逻辑和高电压模拟电路。

AD(模数转换器)选型

AD(模数转换器)选型: TI/BB公司ADC产品: 【ADS7812】1通道,12位,串行接口,低功耗,SOIC封装; 【AMC7820】8通道,12位,串行接口,100kHz 采样速率,TQFP封装; 【TLC2558】8通道,12位,串行接口,400KSPS,5V供电,0-Ref输入,SOIC封装; 【TLV2543】11通道,12位,串行接口,低功耗,DIP封装; 【TLC2543】11通道,12位,串行接口,DIP封装; 【ADS7869】12通道,12位,串行/并行接口,TQFP封装; 【TLC3548】8通道,14位,串行接口,200KSPS,5V供电,0-Ref输入,SOIC封装; 【ADS8320】1通道,16位,串行接口,高速,2.7V-5.5V,MSOP封装;【ADS8321】1通道,16位,串行接口,高速,MSOP封装; 【ADS8505】1通道,16位,并行接口,250-KSPS,SSOP封装; 【ADS8509】1通道,16位,串行接口,250Ksps,SSOP封装; 【ADS7809】1通道,16位,串行接口,100Ksps,5V供电,SOIC封装; 【ADS8342】4通道,16位,并行接口,250Ksps,输入范围-2.5-2.5,TQF P封装; 【ADS8345】8通道,16位,串行接口,串行,SSOP封装; 【ADS1241】4通道,24位,串行接口,SSOP封装; 【ADS7835】1通道,24位,串行接口,高速,低功耗AD转换器,MSOP封装; 详细内容,请访问:https://www.360docs.net/doc/7212297769.html,查看

AD公司ADC产品: 【AD7864】4通道,12位,并行接口,高速同时采样,单电源,TQFP封装; 【AD7865】4通道,14位,并行接口,高速同时采样,单电源,TQFP封装; 【AD677 】1通道,16位,串行接口,100KSPS,DIP封装; 【AD7612】1通道,16位,并行/串行,750KSPS,单级/双级输入,DIP封装; 【AD7715】1通道,16位,串行接口,3V供电,DIP封装; 【AD974 】4通道,16位,串行接口,单电源,200KSPS,DIP封装; 【AD976 】4通道,16位,串行接口,单电源,200KSPS,±10V输入,DIP 封装; 【AD7710】2通道,24位,串行接口,输入可编程增益,SOIC封装; 详细内容,请访问:https://www.360docs.net/doc/7212297769.html,查看。 MAXIM公司ADC产品: 【MAX156】4通道,8位,并行接口,高速,电压基准,DIP封装; 【MAX158】8通道,8位,并行接口,高速,电压基准,DIP封装; 【MAX160】1通道,8位,并行接口,+5V,±5、10 输入范围,4μs,DIP 封装; 【MAX176】1通道,12位,串行接口,250ksps,电压基准,DIP封装; 【MAX187】1通道,12位,串行接口,+5V,低功耗,DIP封装; 【MAX163】1通道,12位,并行接口,5V输入,采样率100k,电压基准,D IP封装; 【MAX167】1通道,12位,并行接口,±2.5V输入,采样率100k,电压基准,DIP封装; 【MAX144】2通道,12位,串行接口,+3V/5V,低功耗,108ksps,DIP封装;

多通道高精度模数转换器AD7718 原理与应用

多通道高精度模数转换器AD7718原理与应用 解放军信息工程大学信息工程学院六系(450002)陈铖武安河 摘要:本文从外部引脚和内部可编程寄存器两方面讲解了多通道高精度模数转换器AD7718,并通过一个24bits分辨率的数据采集电路介绍了AD7718的应用。 关键词:模数转换器 AD7718 数据采集 The Principle And Application Of 10-Channel 24-Bit Resolution Σ-Δ ADCs AD7718 Institute of Information Engineering, Information Engineering University of PLA, Zhengzhou 450002,China Chen Cheng, Wu AnHe Abstract: The AD7718 is a 10-channel 24-bit resolution Σ-ΔAnalog To Digital Converter. This paper presents firstly its pin and consist, and then designs a data acquisition scheme. Key Words: ADC, AD7718, Data Acquisition 1 概述 在低频测量应用中,AD7718是一个单电源供电(+3V或+5V)的完整前端。其内部结构如图1所示。从图中可以看出片内有一个带PGA(Programmable Gain Amplifier,可编程增益放大器)的Σ-Δ型ADC(Analog to Digital Converter,模数转换器)。ADC的分辨率为24 bits ,PGA的范围为20~27,8档可编程。所以,AD7718能直接转换范围在20mV~2.56V之间的输入信号而无须信号调理电路。AD7718片内还有一个多路开关MUX,可以将模拟输入配置成4或5通道差分输入,也可以配置成8或10通道伪差分输入。AD7718需要外接32KHZ晶体,片内PLL通过它产生所需要的工作时钟。 图1 AD7718的内部功能框图

高速多通道同步采样ADC MAX1312及其应用

高速多通道同步采样ADC MAX1312及其应用 【摘要】阐述了MAX1312的特性和工作原理,介绍了MAX1312与通用8位微处理器AT89C52的硬件接口设计以及软件编程方法,最后简述了该模数转换器在多相电机控制中的应用。 【关键词】模数转换器;多通道;同步采样;MAX1312 Abstract:The principle,features and application of multi-channel synchronized sample ADC MAX1312 are introduced,including its hardware interface design and software programming method between MAX1312 and Micro-processor.AT89C52.At last,it describes the application of MAX1312 in controlling the polyphase electric engine. Keywords:A/D converter;multi-channel;synchronized sample;MAX1312 1.引言 在电子测量技术中,必须把模拟信号转换为数字信号,才能够用计算机系统进行处理,模/数转换的速度和精度一直是测量的关键。但是高速和高精确度的转换器仍然难以满足某些特殊场合的要求,例如:在多相电机控制、多相电源监控等场合,要求对多路数据进行精确同步的采集,一般的单通道A/D和多通道轮流采集A/D都不满足这种场合的要求。MAX1312是美国美信公司(MAXIM)新推出的一种高速同步采样模数转换器,它具有12位的精度,8路模拟信号输入,单电源+5V供电,完成8个通道的转换时间仅需要1.96us,对外提供了一个12位20MHZ并行数字接口,可以很方便与各种微处理器相连接,使用十分方便[1]。 2.MAX1312简介 MAX1312是美国美信公司(MAXIM)新推出的多通道同步采样、并行输出模数转换器。采用TQFP48封装,引脚形式如图1所示。 其中: CH0-CH7为八路模拟信号的输入端; D0-D7为八位双向数据总线,用来写入控制字或读出低8位转换结果; D8-D11为高四位数据输出口,当RD=1或CS=1时为高阻状态; CS为片选引脚低电平有效,低电平将激活数字接口,保持高电平时,数字总线为高阻状态;

高速模数转换器(ADC)的INL DNL测量

高速模数转换器(ADC)的INL/DNL测量 摘要:尽管积分非线性和微分非线性不是高速、高动态性能数据转换器最重要的参数,但在高分辨率成像应用中却具有重要意义。本文简要回顾了这两个参数的定义,并给出了两种不同但常用的测量高速模数转换器(ADC)的INL/DNL的方法。 近期,许多厂商推出了具有出色的静态和动态特性的高性能模数转换器(ADC)。你或许会问,“他们是如何测量这些性能的,采用什么设备?”。下面的讨论将聚焦于有关ADC两个重要的精度参数的测量技术:积分非线性(INL)和微分非线性(DNL)。 尽管INL和DNL对于应用在通信和高速数据采集系统的高性能数据转换器来讲不算是最重要的电气特性参数,但它们在高分辨率成像应用中却具有重要意义。除非经常接触ADC,否则你会 很容易忘记这些参数的确切定义和重要性。因此,下一节给出了这些定义的简要回顾。 INL和DNL的定义 DNL误差定义为实际量化台阶与对应于1LSB的理想值之间的差异(见图1a)。对于一个理想ADC,其微分非线性为DNL = 0LSB,也就是说每个模拟量化台阶等于1LSB (1LSB = V FSR/2N,其中 V FSR为满量程电压,N是ADC的分辨率),跳变值之间的间隔为精确的1LSB。若DNL误差指 标≤ 1LSB,就意味着传输函数具有保证的单调性,没有丢码。当一个ADC的数字量输出随着模拟输入信号的增加而增加时(或保持不变),就称其具有单调性,相应传输函数曲线的斜率没有变号。DNL指标是在消除了静态增益误差的影响后得到的。具体定义如下: DNL = |[(V D+1- V D)/V LSB-IDEAL - 1] |,其中0 < D < 2N - 2 V D是对应于数字输出代码D的输入模拟量,N是ADC分辨率,V LSB-IDEAL是两个相邻代码的理 想间隔。较高数值的DNL增加了量化结果中的噪声和寄生成分,限制了ADC的性能,表现为 有限的信号-噪声比指标(SNR)和无杂散动态范围指标(SFDR)。

高速数模转换器的设计思路

高速数模转换器的设计思路及应用考虑(上) 北京市英赛尔器件集团(100044)高工 中国科学院长春物理研究所(130021)徐健 摘要:在分析影响高速数模转换器的主要问题(毛刺和无杂散动态范围)基础上,总结出四种基本电路结构的设计思路及应用考虑。 关键词:毛刺无杂散动态范围全译码式DAC 分段式DAC 插值式DAC 1 概述 随着通信事业、多媒体技术和数字化设备的飞速发展,促进了高速(一般指更新速率大于1MS PS)数模转换器(DAC)有了长足进步,牵动着DAC制造商研制出许多新结构、新工艺及各种特殊用途的高速DAC。譬如用于通信系统信号发送信道的TxDAC,用于CRT光栅扫描系统的Video DAC,用于CD唱机再现音频信号的Audio DAC。有些Video DAC内部含有调色板存储器并且 具备图形显示系统常用功能的DAC又称作RAMDAC。高速DAC的应用领域主要有三个方面:(1)数字化仪器,包括波形重建和任意波形发生器;(2)直接数合成(DDS),包括接收器本机振荡器、跳频无线电设备、通信系统、正交调制(QAM)系统和雷达系统;(3)图形显示系统,包括失量扫描和光栅扫描。为了满足高速DAC 上述应用领域的要求,提高DAC的动态技术指标,美国模拟器件公司(ADI)在DAC电路结构上做了一系列改进,研制出带SHA式DAC、全译码式DAC,分段式DAC以及插值式DAC。本文通过对高速DAC的设计思路及应用考虑做简单综述,希望能对读者应用高速DAC有所裨益。 2 影响高速DAC的主要问题 2 1 主要动态技术指标 高速DAC的主要动态(或交流)技术指标: 建立时间(settling time),通常指DAC从数字输入变迁(通常从半满度即50%点,例如从011…11到100…00)开始到达并保持在规定终值附近的误差带(一般为±1/2LSB)所需要的时间。 输出更新速率(output update rate),指从数据寄存器精确地向DAC传输数据的速率,但并不意味着这个速率能达到规定位数的精度。无杂散动态范围(SFDR),指在规定带宽范围内,DAC输出信号幅度的有效值与峰值杂散信号的有效值之差,通常用分贝(dB)表示。 总谐波失真(THD),指DAC输出前6次谐波总有效值与输入信号(基波)有效值之比,可用百分比表示,也可用分贝(dB)表示。毛刺脉冲(glitch impulse),指由于DAC的开关时间不对称引起的讨厌的瞬变,它是影响高速DAC的关键指标。 2 2 毛刺的产生机理、性质及其表示方法 近年来DAC制造商一直围绕如何消除或减小毛刺脉冲的影响研制出不同结构的高速DAC,所以有必要清楚地了解毛刺脉冲的成因、性质及其表示方法。当DAC的输入发生变迁(即从一个数码跳变到另一个数码)时,理想情况下DAC的输出波形应该是单调地变化,如图1a所示,实际上会出现类似正脉冲、负脉冲或两者都出现(见图1b,c)。

高精度模数转换器(ADC)

Σ-Δ转换器的特点是将绝大多数的噪声从动态转移到阻态,因而Σ-Δ转换器通常被用于对成本与精度有要求的低频场合。CS1232是芯海科技公司自主设计的一款高精度模数转换器(ADC),采用先进的3阶Σ-Δ 转换技术,可用于低电平、高精度测量,尤其适用于衡器领域,软件和硬件上不需要做任何修改,即可完全兼容于TI公司的ads1232。 CS1232的有效精度达到23.5位,可以在3.3V-5.5V的电压范围内正常工作,工作电压范围宽,并且内置4.9152M晶振,无需外部提供时钟信号,如果同时运行多个芯片,还可以使用外部时钟。通过控制PDWN引脚为低电平,可以使芯片进入掉电工作模式,功耗电流仅1μA。片内有两路差分通道,可用于多通道测量。片上内置低噪声的仪用放大器,最高128倍,可以直接测量幅度较小的微小信号。输出速度可以选择10Hz或80Hz,采用10Hz的数据速率时,可拟制50Hz和60Hz的干扰信号。CS1232的增益温漂约2pp/℃,并内置温度传感器,可以监测环境温度。 关键特性及结构 CS1232包括一个高性能Σ-ΔADC、低噪声放大器(PGA)、多路复用器、时钟、校准寄存器和串行外围接口,图1为CS1232的内部结构图。 CS1232内置一路Σ-Δ ADC,ADC采用三阶Σ-Δ调制器,通过低噪声仪用放大器结构实现PGA放大,PGA=1时,有效分辨率23.5位;PGA=128时,有效分辨率可达21位,内部放大器具有低噪声、低温漂等优点。CS1232的参数配置都通过外部引脚控制,无需寄存器编程。 图1: CS1232的内部结构图。 典型应用设计 传统的精密数据转换器解决方案不能兼备低噪声和低功耗的特性,而CS1232因为具有功耗低、噪声小、温漂系数小等特点,特别适合于衡器仪表、电子天平、数字传感器等小信号测量领域。图2给出了CS1232的仪表方案典型应用电路。 图2:采用CS1232的仪表方案典型应用电路。 图2中的传感器是电阻应变式传感器。根据电阻应变式传感器的原理,四片应变片构成全桥桥路,在电桥供电端施加恒定的直流电压,则电桥输出端的电压将与其上所承受的压力成正比,由此可根据输

基于FPGA的高精度多通道采集系统及其性能分析

收稿日期:2011-05-23 作者简介: 涵妤(1979-),女,江苏南京人,实验师,工程硕士,研究方向为嵌入式系统。 0 引言 随着信息技术的飞速发展和数据采集系统的广泛应用,数据采集系统的性能要求也越来越高。在图像处理与音频信号处理等高速、高精度和实时性强的处理中,高性能的数据采集系统尤为重要。 数据采集系统实时性与同步性的要求既限制了低速单片机数据采集系统的使用,也限制了基于DSP 频繁中断的数据采集系统的采纳。如采用可编程逻辑器件设计数据采集系统具有开发周期短、集成度高、设计费用低、工作频率高、功耗低、编程配置灵活等优点。本文介绍一种基于FPGA 的高精度多通道的数据采集系统,并对这个系统的高精度、多通道和高速度等性能进行了分析。 1 系统概述 基于FPGA 的高精度多通道采集系统(如图1所示)由多路复用选择器、模数转换器、高速精密放大器、数模转化器和FPGA 组成。多路模拟信号由多路复用选择器引入,经选择后通过高速精密放大器进行滤波处理,然后再进入高速精密模数转换器进行数据转换,在此过程中,模拟输入信号选择的控制和模数转换器的控制均由FPGA 实现,而转换后的数字信号通过FPGA 传输给处理模块。数字控制电机转动过程中,数字控制信号通过数模转换模块转换成为模拟信号。数模转换模块主要是和模数转换模块进行联调来证明整个采集系统具有高精度性能。 图1 数据系统采集框图 2 系统硬件结构 2.1 多路复用选择器 多路复用选择器采用的是ADI 公司生产的ADG1406,包括16个单端通道。它可以将其中一个输入切换到公共输出,具体由4位二进制地址线决定(A0、A1、A2和A3)。这款器件EN 引脚高低电平可以用来使能或禁用器件,禁用时所有通道都被关断;启用时每个通道都执行双向操作,输入信号范围可扩展至电源电压。这些开关具有超低的导通电阻以及导通电阻平坦度,是低失真度至关重要的数据采集与增益开关应用的理想解决方案,iCMOS ?架构具有超低功耗性能[1]。 采集系统做了正负10V-0V 的标定输入和10个单端模拟输入通道,其中IN1-IN9为模拟输入。正负15V 电源供电,每个电源引脚上要接一个0.1uF 的去耦电容,EN 引脚接在高电平上。FPGA 的I/O 脚与A0、A1、A2和A3相连,通道选择的控制是通过写逻辑来完成的,D 引脚是输出引脚。2.2 高速精密放大器 OPA827是一款JFET 输入运算放大器,其具 基于FPGA的高精度多通道采集系统及其性能分析 Research on performance of data acquisition system based on FPGA 洑涵妤 FU Han-yu (江苏技术师范学院 计算机工程学院,常州 213001) 摘 要: 本文先将多路复用选择器作为模拟信号的输入端口来实现多路模拟信号的采集,再通过信号 滤波处理来确保最有效的模拟信号进入模数转换器,转换后输出的数字量暂存在FPGA的缓存区中。整个过程均由FPGA来控制的。最后,采用DAC-ADC间联调,通过比较可以看出ADC 的最终结果在14位。 关键词: 数据采集系统;高精度;数据转换;FPGA 中图分类号:TP391 文献标识码:A 文章编号:1009-0134(2011)9(下)-0065-04Doi: 10.3969/j.issn.1009-0134.2011.9(下).21

高速模数转换器ADC的INLDNL测量

Maxim > App Notes > A/D and D/A CONVERSION/SAMPLING CIRCUITS HIGH-SPEED SIGNAL PROCESSING Sep 01, 2000 Keywords: integral nonlinearity, INL, differential nonlinearity, DNL, analogue-to-digital, analog-to-digital, high- speed, high performance, data converters, ADCs, digital-to-analog, digital-to-analogue, converter, DACs APPLICATION NOTE 283 INL/DNL Measurements for High-Speed Analog-to-Digital Converters (ADCs) Abstract: Although integral and differential nonlinearity may not be the most important parameters for high-speed, high dynamic performance data converters, they gain significance when it comes to high-resolution imaging applications. The following application note serves as a refresher course for their definitions and details two different, yet commonly used techniques to measure INL and DNL in high-speed analog-to-digital converters (ADCs). Manufacturers have recently introduced high-performance analog-to-digital converters (ADCs) that feature outstanding static and dynamic performance. You might ask, "How do they measure this performance, and what equipment is used?" The following discussion should shed some light on techniques for testing two of the accuracy parameters important for ADCs: integral nonlinearity (INL) and differential nonlinearity (DNL). Although INL and DNL are not among the most important electrical characteristics that specify the high-performance data converters used in communications and fast data-acquisition applications, they gain significance in the higher-resolution imaging applications. However, unless you work with ADCs on a regular basis, you can easily forget the exact definitions and importance of these parameters. The next section therefore serves as a brief refresher course. INL and DNL Definitions DNL error is defined as the difference between an actual step width and the ideal value of 1LSB (see Figure 1a). For an ideal ADC, in which the differential nonlinearity coincides with DNL = 0LSB, each analog step equals 1LSB (1LSB = V FSR/2N, where V FSR is the full-scale range and N is the resolution of the ADC) and the transition values are spaced exactly 1LSB apart. A DNL error specification of less than or equal to 1LSB guarantees a monotonic transfer function with no missing codes. An ADC's monotonicity is guaranteed when its digital output increases (or remains constant) with an increasing input signal, thereby avoiding sign changes in the slope of the transfer curve. DNL is specified after the static gain error has been removed. It is defined as follows: DNL = |[(V D+1- V D)/V LSB-IDEAL - 1] | , where 0 < D < 2N - 2. V D is the physical value corresponding to the digital output code D, N is the ADC resolution, and V LSB-IDEAL is the ideal spacing for two adjacent digital codes. By adding noise and spurious components beyond the effects of quantization, higher values of DNL usually limit the ADC's performance in terms of signal-to-noise ratio (SNR) and spurious-free dynamic range (SFDR).

Excel货币大写转换

Excel中如何将货币数值由数字金额自动转为中文大写金额 使用Excel时有时会用数据的转换,尤其是做财务工作,如工资表等时就需要用中文大写金额。如果手动输入,就会麻烦一些,多的时候也会增加了工作量。我们可以使用Excel 中的函数来实现将货币数值由数字金额自动转换成中文大写金额。 本文以一份表格为例讲解如何将数字金额转换为中文大写金额。 先在Excel表格中算出合计金额,如下图。 利用公式把小写的货币转换为中文大写,并写在合并的单元格中。公式如下: =IF((I41-INT(I41))=0,TEXT(I41,"[DBNUM2]")&"元整 ",IF(INT(I41*10)-I41*10=0,TEXT(INT(I41),"[DBNUM2]")&"元 "&TEXT(INT(I41*10)-INT(I41)*10,"[DBNUM2]")&"角整",TEXT(INT(I41),"[DBNUM2]")&"元 "&IF(INT(I41*10)-INT(I41)*10,"零",TEXT(INT(I41*10)-INT(I41)*10,"[DBNUM2]")&"角 ")&TEXT(RIGHT(I41,1),"[DBNUM2]")&"分"))。 把公式输入合计右边的合并单元格中,如下图。

输入后的显示结果如下图。

公式中一共用到了4函数,文本连接符“&”及相应的汉字。下面对这4种函数做个讲解:IF函数:是一个条件判断函数,该函数的基本格式是:IF(a,b,c),其中“a”是一个条件,“b”和“c”是两种判断结果,可以表述为:如果条件a成立,那么结果是b,否则结果就是c。以上公式是一个多层嵌套判断函数,根据货币金额的不同情况生成不同格式的中文大写。 INT函数:是一个取整函数,取参数数字的整数部分。如:INT(I41)是取I41这个单元格数字的整数部分,(I41-INT(I41))=0表示一个整数,INT(I41*10)-INT(I41)*10表示I41单元小数点后第一位数,INT(I41*10)-INT(I41)*10=0表示I41单元格中有一位小数。 TEXT函数:可以将阿拉伯格式数字转换为中文大写格式,如公式中 TEXT(I41,"[DBNUM2] ")就是把I41单元格中的数字转换成中文大写格式,其中"[DBNUM2] "是把数字转换为中文大写形式,照搬即可。 RIGHT函数:可以提取字符串右边的若干个字符。如公式中的“RIGHT(I41,1)” 表示从I41单元格数字右起提取一个字符。 公式使用了多层嵌套,看起来比较复杂一些。 可以将整个条件函数公式表述为: 如果单元格A7中数字为整数(假如为35566),那么人民币大写就是“叁万伍仟伍佰陆拾陆元整”,否则:

多通道高速数据采集板的设计

多通道高速数据采集板的设计 高丽珍 王敦庆 张晓明 (中北大学信息与通信工程学院,山西太原030051) 摘 要:根据虚拟仪器的设计思想,详细介绍了高速数据采集板软硬件设计的基本原则、方法及工作流程,设计了基于PXI总线的多通道高速数据采集板。采用DSP到PXI总线的跨总线DMA技术解决了高速数据传输的瓶颈问题,实现了多通道高速数据采集。 关键词:虚拟仪器;数据采集;PXI总线;DSP 中图分类号:TP274 文献标识码:A 0 引言 随着计算机技术和微电子技术的高速发展,高速测试系统有两方面发展趋势。一方面并行测试系统在近年来得到了发展,并行系统中为每个测试通道单独配置通道放大器和A/D转换器,具有很高的通道采集速率和精度,特别适合对动态信号的采集和分析。另一方面,信号的高速测试要求测试仪器拥有较高的数据传输带宽,以传输采集的大量数据[1]。 根据对高速数据采集板提出的要求,笔者设计了基于PXI总线的数据采集原型板。该采集板具备以下功能:多通道同时采集数据;单通道数据采集率达到10MSPS以上,A/ D分辨率达12位;板上具有一定的数据存储能力;实时对大量的采集数据进行主机存储;系统静态精度:±0.1%FS;具有一定的实时预处理功能。 1 方案设计 1.1 数据总线的选择[2] 近些年出现的串行标准USB2.0和Fire wire虽然在传输带宽方面有了很大的提升,但是由于缺少多模板间的同步机制,所以在设计并行高速数据采集系统时也不能被采纳。现阶段应用于测试仪器领域的主流并行测试系统主要有基于VXI总线和基于PXI总线两种构架。而VXI总线目前最大传输速率可达80MB/s,远远低于PCI/PXI总线传输速率,并且未能成为通用计算机总线。PXI总线就是在PCI总线的基础上,面向仪器应用扩展了触发总线等。PCI总线传输速率高达264MB/s,使PCI/PXI接口卡和主机之间可以实现高效可靠的数据传输。PXI继承了PCI和Compact PCI 的全部优点,并新增了许多电气特性以满足高性能仪器和测试领域的需要。因此该方案选择了PXI总线作为高速数据传输总线。 根据接口实现简单可靠的技术要求,本设计采用专用总线接口芯片进行本地总线与PCI总线的连接。考虑到PL X 公司的PCI9054能够提供多种数据传输方式,尤其是2个独立的DMA通道具有PCI总线主控能力,可以大大提高由本地到主机的数据传输带宽,因此选定PCI9054作为PCI总线到本地的桥接芯片。 1.2 采集板上处理器的选择 对于高速测试系统而言,处理器主要是实现对信号的采集控制、采集数据的实时预处理以及处理后数据的高速传输和存储等功能。DSP芯片具有运算速度快、编程方便、稳定性好、精度高、便于集成等优点,已广泛用于复杂的数字信号处理等领域。为了更有效地完成数据采集任务,测试系统中的DSP芯片应该具有以下几个特点:高速的数据处理及片内、片外数据传输能力;总线主控能力;可根据通道扫描表设置多种触发方式、采集率、存储模式等采集参数;并行操作; OEM优势[3]。 结合设计要求,提出对DSP的选择标准:浮点32位DSP、指令速度900MFLOPS、片内存储器空间至少64K B、片外存储空间至少128MB、软硬件开发工具齐全。考虑到产品系列覆盖面和成熟度,以德州仪器公司的TMS320系列DSP作为首选。选用性价比较高的TMS320C6711作为板上核心DSP部件。 1.3 组合电路和时序电路 在数据采集板设计时,不仅要协调DSP和外围电路的接口,而且还须考虑PXI集成接口芯片与DSP总线及主机PCI总线的接口电路。所以数据采集板上存在较多功能复杂的时序逻辑电路。我们选择具有更高集成度、设计更加灵活且功耗较小的FPG A来实现模板的控制核心。Altera公司的FL EX10KE芯片内部含有多条32位总线。它基于可重新配置的COMS SRAM单元技术,具有高集成度、快速、高可靠性等特点,适合于复杂的组合电路和时序电路的设计。 1.4 系统硬件总体框图 由以上分析,可以将高速数据采集板分为三个模块: DSP模块、PCI9054模块和FPG A模块,如图1所示。DSP 模块是数据采集、预处理、传输、存储的控制中心;PCI9054模块主要用于本地总线与PCI总线的连接以实现模板与上位机的通讯;FPG A模块负责各部分间的控制逻辑电路与时 山西电子技术 2007年第6期 应用实践 收稿日期:2007-04-07 第一作者 高丽珍 女 30岁 助教