JTAG接口定义

JTAG接口定义

2009-12-14 17:32

什么是jtag接口

JTAG(Joint Test Action Group ,联合测试行动小组 ) 是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试, JTAG 技术是一种嵌入式调试技术,它在芯片内部封装了专门的测试电路 T AP ( Test Access Port ,测试访问口),通过专用的 JTAG 测试工具对内部节点进行测试。

目前大多数比较复杂的器件都支持 JTAG 协议,如 ARM 、 DSP 、 FPGA 器件等。标准的 JTAG 接口是 4 线: TMS 、 TCK 、 TDI 、 TDO ,分别为测试模式选择、测试时钟、测试数据输入和测试数据输出。JTAG 测试允许多个器件通过 JTAG 接口串联在一起,形成一个 JTAG 链,能实现对各个器件分别测试。JTAG 接口还常用于实现 ISP ( In-System Programmable 在系统编程)功能,如对 FLASH器件进行编程等。

通过 JTAG 接口,可对芯片内部的所有部件进行访问,因而是开发调试嵌入式系统的一种简洁高效的手段。目前 JTAG 接口的连接有两种标准,即 14 针接口和 20 针接口,其定义分别如下所示。

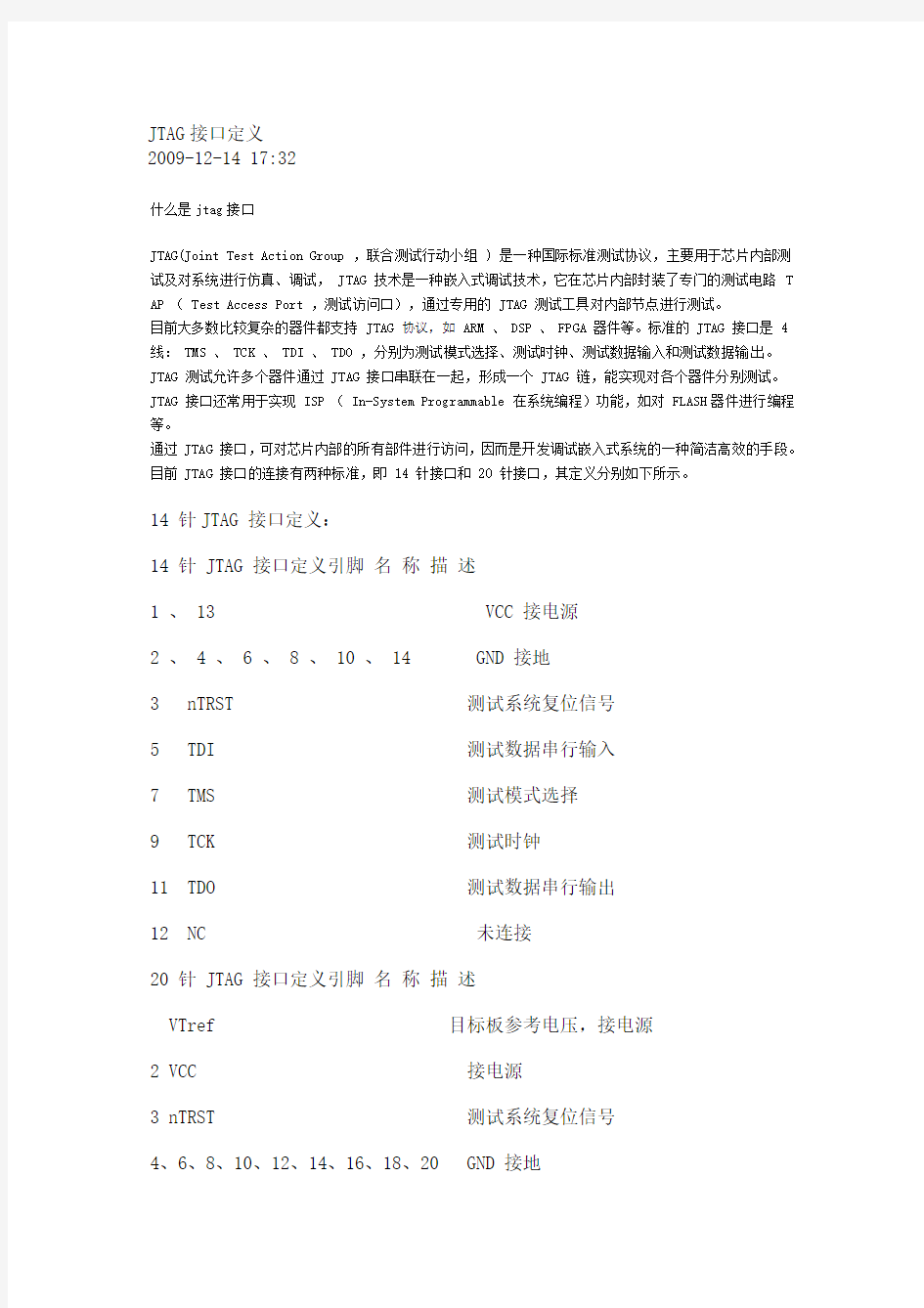

14 针JTAG 接口定义:

14 针 JTAG 接口定义引脚名称描述

1 、 13 VCC 接电源

2 、 4 、 6 、 8 、 10 、 14 GND 接地

3 nTRST 测试系统复位信号

5 TDI 测试数据串行输入

7 TMS 测试模式选择

9 TCK 测试时钟

11 TDO 测试数据串行输出

12 NC 未连接

20 针 JTAG 接口定义引脚名称描述

VTref 目标板参考电压,接电源

2 VCC 接电源

3 nTRST 测试系统复位信号

4、6、8、10、12、14、16、18、20 GND 接地

5 TDI 测试数据串行输入

7 TMS 测试模式选择

9 TCK 测试时钟

11 RTCK 测试时钟返回信号

13 TDO 测试数据串行输出

15 nRESET 目标系统复位信号

17 、 19 NC 未连接

下面以S3C4510B开发板为例说明JTAG接口:

在保证电源电路、晶振电路和复位电路正常工作的前提下,可通过JTAG 接口调试S3C4510B,在系统上电前,首先应检测JTAG 接口的 TMS 、 TCK 、 TDI 、TDO 信号是否已与 S3C4510B 的对应引脚相连,其次应检测 S3C4510B 的 nEWA IT 引脚( Pin71 )是否已上拉, ExtMREQ 引脚( Pin108 )是否已下拉,对这两只引脚的处理应注意,作者遇到多起S3C4510B 不能正常工作或无法与JTA G 接口通信,均与没有正确处理这两只引脚有关。

给系统上电后,可通过示波器查看 S3C4510B 对应引脚的输出波形,判断是否已正常工作,若S3C4510B 已正常工作,在使能片内 PLL 电路的情况下, SDCLK/ MCLKO 引脚( Pin77 )应输出频率为 50MHz 的波形,同时, MDC 引脚( Pin 50 )和其他一些引脚也应有波形输出。

在保证 S3C4510B 已正常工作的情况下,可使用 ADS 或 SDT 通过 JTAG 接口对片内的部件进行访问和控制。

在此,首先通过对片内控制通用 I/O 口的特殊功能寄存器的操作,来点亮连接在 P3 ~ P0 口上的4 只 LED ,用以验证 ADS 或 SDT 调试环境是否已正确设置,以及与 JTAG 接口的连接是否正常。

ADS 和 SDT 均为 ARM 公司为方便用户在 ARM 芯片上进行应用开发而推出的一整套集成开发工具,其中, ADS 为 SDT 的升级版本。该系统的调试以 ADS 为例,同时也适合于 SDT 开发环境。

连接好硬件后,打开 AXD Debugger ,建立与目标板(待调试的系统板)的连接, AXDDebugger 有软件仿真方式和带目标系统的调试方式,此时应工作在带目标系统的调试方式。

选择菜单 System Views → Command Line Interface 功能,该选项为 AXD De bugger 的一个命令行窗口,可在该窗口内输入各种调试命令,使用非常方便。

在命令行窗口输入:

> setmem 0x3FF5000, 0xFFFF, 32

> setmem 0x3FF5008, 0xFFFF, 32

setmem 命令用于对特定的地址设置特定的值,待设定的值可以是 8 位、 16 位或 32 位,在此,对通用 I/O 口的模式寄存器和数据寄存器设置相应的值,点亮 LED 。

S3C4510B 在复位后,特殊功能寄存器的基地址为 0x3FF0000, 由表 5 -2-3 可知,I/O 口的模式寄存器偏移地址为0x5000,因此, I/O 口的模式寄存器的物理地址为 0x3FF5000 ,设定该寄存器的值为 0xFFFF ,将 I/O 口置为输出方式。 I/O 口的数据寄存器的物理地址为 0x3FF5008 ,设定该寄存器的值为 0xFFFF ,将 I/O 口的输出置为高电平。

在执行完以上两条命令后,连接在通用 I/O 口的 4 只 LED 应被点亮,表示调试系统的软、硬件连接完好,可进行下一步的调试工作,否则,应重新检查调试系统。

用户若使用 SDT 作为调试工具,操作方法类似。连接好硬件后,打开 ARM De bugger for Windows ,建立与目标板(待调试的系统板)的连接,选择菜单View → Command 功能,即可显示命令行窗口,在命令行窗口输入:

Debug:let 0x3FF5000 = 0xFFFF

Debug:let 0x3FF5008 = 0xFFFF

执行完以上两条命令后,连接在通用 I/O 口的 4 只 LED 应被点亮。

关于通用 I/O 口更具体的工作原理和使用方法,可参考S3C4510B 用户手册。

用户系统若能正常完成上述操作并成功点亮连接在P3~P0 口上的LED 显示器,则表明S3C4510B已在正常工作,且调试环境也已正确建立,以后的调试工作就相对简单。笔者曾遇到多个用户系统因为不能完成这步工作,使开发者失去信心而最终放弃。

液晶显示屏V-by-One与LVDS接口信号驱动原理

V-by-One接口信号驱动原理(3840*2160) 一、时钟与像素点关系 一场:60Hz-16.667ms,2250行(2160行有效) ——刷新像素点:3840*2160个/Vertical 一行:135KHz-7.407us,(=60Hz*2250),4400=550*8点(3840点=480*8点有效)——刷新像素点:3840个/ Horizontal Clock:74.25MHz-13.468ns,(=135KHz*550) ——刷新像素点:8个/Clock 以上,可参考《附录A:屏规格书信号时序特性》。 二、V-by-One信号传输规则 每个Clock(DCLK),V-by-O接口有8对差分对(lane0~lane7)同时传输,每对差分对负责一个Pixel;共8个Pixels一起传输数据。 以上,可参考《附录B:屏规格书每场画面时序》与《附录C:屏规格书单区与双区的驱动方式(每一行)》。 每对差分对同时串行传输4Bytes字节(共32bits,V-by-One传输协议有40bits);(每bit周期0.3367ns=13.468ns/40,2,97G带宽) 或按照公式计算:4(byte)×8×(10/8)×(594MHz/8lines)=2,97G 以上,可参考《附录D:屏规格书数据传输格式》与《附录E:V-by-O协议文件截图》。 信号最小单位为bit,1bit的数据长度合成眼图(1UI=0.3367ns=336.7ps),可通过眼图测试得具体信号特性; 以上,可参考《附录F:V-by-O接口输入端眼图》。

附录C:屏规格书单区与双区的驱动方式(每一行)

JTAG接口的定义及常见问题

JTAG接口的定义及常见问题 ARM系统的JTAG接口的设计不当往往使硬件系统无法调试,所以在设计ARM 系统前要先熟悉ARM系统的JTAG接口的定义和常见问题。 1.ARM系统的JTAG接口是如何定义的?每个PIN又是如何连接的? 下图是JTAG接口的信号排列示意: 接口是一个20脚的IDC插座。下表给出了具体的信号说明: 表 1 JTAG引脚说明 序号信号名方向说明 1 Vref Input 接口电平参考电压,通常可直接接电源 2 Vsupply Input 电源 (设备提供) 3 nTRST Output (可选项) JTAG复位。在目标端应加适当的上拉电阻以防止误触发。 4 GND -- 接地 5 TDI Output Test Data In from Dragon-ICE to target. 6 GND -- 接地 7 TMS Output Test Mode Select 8 GND -- 接地 9 TCK Output Test Clock output from Dragon-ICE to the target 10 GND -- 接地 11 RTCK Input (可选项) Return Test Clock。由目标端反馈给Dragon-ICE的时钟信号,用来同步TCK信号的产生。不使用时可以直接接地。12 GND -- 接地

13 TDO Input Test Data Out from target to Dragon-ICE. 14 GND -- 接地 15 nSRST Input/Output (可选项) System Reset,与目标板上的系统复位信号相连。可以直接对目标系统复位,同时可以检测目标系统的复位情况。为了防止误触发,应在目标端加上适当的上拉电阻。 16 GND -- 接地 17 NC -- 保留 18 GND -- 接地 19 NC -- 保留 20 GND -- 接地 2.目标系统如何设计? 目标板使用与Dragon-ICE一样的20脚针座,信号排列见表1。RTCK和 nTRST 这两个信号根据目标ASIC有否提供对应的引脚来选用。nSRST则根据目标系统的设计考虑来选择使用。下面是一个典型的连接关系图: 复位电路中可以根据不同的需要包含上电复位、手动复位等等功能。如果用户希望系统复位信号nSRST能同时触发JTAG口的复位信号nTRST,则可以使用一些简单的组合逻辑电路来达到要求。后面给出了一种电路方案的效果图。

LVDS屏线及屏接口定义

LVDS屏线及屏接口定义 现在碰到液晶屏大多是LVDS屏线,经常碰到什么单6,双6 单8双8.如何区分呢? 方法数带“+-”的这种信号 线一共有几对,有10对的减2对就是双8,有8对的减2对就是双6。有5对的 减掉1对是单8,有4对的减掉1对是单6,数+/-线一共有多少对。说通俗点就 4对——单6 5对——单8 8对——双6 10对——双8 方法2 拧开螺丝看看主板里面的电路,一般每对数据线之间都有一个100欧姆的电阻 ,看到4个的话就是单6位的屏,看到8个的话就是双六位,5个的话一般是单8位,有10个一般就是双8位,当然有资料的话就不用这么麻烦,也有TMDS 也用这种20PIN的连接头的,比如LG的LP141X1,不过基本上很少lvds的接口的定义20PIN单6定义: 1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:地 8:R1- 9:R1+ 10:地 11:R2- 12:R2+ 13:地 14:CLK- 15:CLK+ 16空 17空 18空 19 空 20空每组信号线之间电阻为(数字表120欧左右) 20PIN双6定义 1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:R1- 8:R1+ 9:R2- 10:R2+ 11:CLK- 12:CLK+ 13:RO1- 14:RO1+ 15:RO2- 16:RO2+ 17:RO3- 18:RO3+;19:CLK1- 20:CLK1+每组信号线之间电阻为(数字表120欧左右) X20PIN单8定义: 1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:地 8:R1- 9:R1+ 10:地 11:R2- 12:R2+ 13:地 14:CLK- 15:CLK+ 16:R3- 17:R3+ 每组信号线之间电阻为(数字表120欧左右) 30PIN单6定义: 1:空2:电源3:电源 4:空 5:空 6:空 7:空 8:R0- 9:R0+ 10:地 11:R1- 12:R1+ 13:地 14:R2- 15:R2+ 16:地 17:CLK- 18:CLK+ 19:地 20:空- 21:空 22:空 23:空 24:空 25:空 26:空 27:空 28空 29空 30空每组信号线之间电阻为(数字表120欧左右)' 30PIN单8定义: 1:空2:电源3:电源 4:空 5:空 6:空 7:空 8:R0- 9:R0+ 10:地 11:R1- 12:R1+ 13:地 14:R2- 15:R2+ 16:地 17:CLK- 18:CLK+ 19:地 20:

Jtag的各种引脚定义

Jtag的各种引脚定义 使用过ARM芯片的人肯定都听过一个仿真器————JLINK,为什么ARM芯片现在能够这么流行?其中恐怕就有一个原因就是很多的ARM芯片都支持使用Jlink进行调试和仿真。所以你只要有一个Jlink,不管是ARM7、ARM9、ARM11还是最新的ARM Cortex 系统都能下载和调试了。 以前的嵌入式开发者,可能使用什么公司的芯片就得买一个对应芯片的下载和仿真器,这样如果你只使用一种芯片,可能还好,不过恐怕没有那种芯片能够一直引领市场。 Jlink使用的是一种叫做JTAG的协议,JTAG原本是用于芯片内部测试的,现在大多用于芯片的程序下载和调试仿真。由于现在Jlink用的比较多,所以有些人可能把Jlink就等同于JTAG了,实际上,JTAG是一种协议,只要满足这种协议的就可以叫做JTAG,比如H—JTAG、OpenJTAG、OSJTAG等等。正版的Jlink是卖的很贵的。大概是1000到2000RMB吧。不过,中国的山寨能力是很强的,而且你硬件卖给别人了,你也没办法控制别人说你不许拆开我的东西看里面的电路是怎么样的。所以Jlink就被破解了,破解之后的Jlink很便宜,网上五六十块钱就能买到一个能用的Jlink。 除了商业版的Jlink和H—JTAG,网上还有一些电子爱好者,他们参照开源软件的模式,设计了开源硬件,比如arduino。还有人制作了开源版本的JTAG仿真器——OpenJTAG。而一些芯片的开发商不像那些软件厂商,会给软件做很多的限制,他们对于开源硬件还是比较开明的,所以他们也支持了一些开源硬件。比如TI公司的MSP430 LaunchPad、ST公司的STM Discovery 等等板子。还有飞思卡尔公司的USBDM和OSJTAG。他们把这些硬件的原理图、PCB还有固件都放在了网络上供人自由下载和制作,你也可以根据他的资料进行改进。这样能使大家对于他们家的芯片有更多的了解,所以,他们也乐于开源一些评估板。 今天我要说的是几种JTAG仿真器的引脚定义,首先我看看比较常见的JTAG 20-Pin的引脚接口如下:

JTAG各类接口针脚定义及含义

JTAG各类接口针脚定义及含义 JTAG有10pin的、14pin的和20pin的,尽管引脚数和引脚的排列顺序不同,但是其中有一些引脚是一样的,各个引脚的定义如下。 一、引脚定义 Test Clock Input (TCK) -----强制要求1 TCK在IEEE1149.1标准里是强制要求的。TCK为TAP的操作提供了一个独立的、基本的时钟信号,TAP的所有操作都是通过这个时钟信号来驱动的。 Test Mode Selection Input (TMS) -----强制要求2 TMS信号在TCK的上升沿有效。TMS在IEEE1149.1标准里是强制要求的。TMS信号用来控制TAP状态机的转换。通过TMS信号,可以控制TAP在不同的状态间相互转换。 Test Data Input (TDI) -----强制要求3 TDI在IEEE1149.1标准里是强制要求的。TDI是数据输入的接口。所有要输入到特定寄存器的数据都是通过TDI接口一位一位串行输入的(由TCK驱动)。 Test Data Output (TDO) -----强制要求4 TDO在IEEE1149.1标准里是强制要求的。TDO是数据输出的接口。所有要从特定的寄存器中输出的数据都是通过TDO接口一位一位串行输出的(由TCK驱动)。 Test Reset Input (TRST) ----可选项1 这个信号接口在IEEE 1149.1标准里是可选的,并不是强制要求的。TRST可以用来对TAPController进行复位(初始化)。因为通过TMS也可以对TAP Controll进行复位(初始化)。所以有四线JTAG与五线JTAG之分。 (VTREF) -----强制要求5 接口信号电平参考电压一般直接连接Vsupply。这个可以用来确定ARM的JTAG接口使用的逻辑电平(比如3.3V还是5.0V?) Return Test Clock ( RTCK) ----可选项2 可选项,由目标端反馈给仿真器的时钟信号,用来同步TCK信号的产生,不使用时直接接地。System Reset ( nSRST)----可选项3 可选项,与目标板上的系统复位信号相连,可以直接对目标系统复位。同时可以检测目标系统的复位情况,为了防止误触发应在目标端加上适当的上拉电阻。 USER IN 用户自定义输入。可以接到一个IO上,用来接受上位机的控制。 USER OUT 用户自定义输出。可以接到一个IO上,用来向上位机的反馈一个状态 由于JTAG经常使用排线连接,为了增强抗干扰能力,在每条信号线间加上地线就出现了这种20针的接口。但事实上,RTCK、USER IN、USER OUT一般都不使用,于是还有一种14针的接口。对于实际开发应用来说,由于实验室电源稳定,电磁环境较好,干扰不大。

lvds接口定义及原理知识

lvds接口定义及原理知识 LVDS接口定义 作者:bechade 更新时间:2007-9-22 7:31:10 文章录入:chfygl -------------------------------------------------------------------------------- 20PIN单6定义: 1:电源2:电源3:地4:地5:R0- 6:R0+ 7:地8:R1- 9:R1+ 10:地11:R2- 12:R2+ 13:地14:CLK- 15:CLK+ 16空17空18空19 空20空 每组信号线之间电阻为(数字表120欧左右) 20PIN双6定义: 1:电源2:电源3:地4:地5:R0- 6:R0+ 7:R1- 8:R1+ 9:R2- 10:R2+ 11:CLK- 12:CLK+ 13:RO1- 14:RO1+ 15:RO2- 16:RO2+ 17:RO3- 18:RO3+ 19:CLK1- 20:CLK1+ 每组信号线之间电阻为(数字表120欧左右) 20PIN单8定义:

1:电源2:电源3:地4:地5:R0- 6:R0+ 7:地8:R1- 9:R1+ 10:地11:R2- 12:R2+ 13:地14:CLK- 15:CLK+ 16:R3- 17:R3+ 每组信号线之间电阻为(数字表120欧左右) 30PIN单6定义: 1:空2:电源3:电源4:空5:空6:空7:空8:R0- 9:R0+ 10:地11:R1- 12:R1+ 13:地14:R2- 15:R2+ 16:地17:CLK- 18:CLK+ 19:地20:空- 21:空22:空23:空24:空25:空26:空27:空28空29空30空 每组信号线之间电阻为(数字表120欧左右) 30PIN单8定义: 1:空2:电源3:电源4:空5:空6:空7:空8:R0- 9:R0+ 10:地11:R1- 12:R1+ 13:地14:R2- 15:R2+ 16:地17:CLK- 18:CLK+ 19:地20:R3- 21:R3+ 22:地23:空24:空25:空26:空27:空28空29空30空 每组信号线之间电阻为(数字表120欧左右) 30PIN双6定义: 1:电源2:电源3:地4:地5:R0- 6:R0+ 7:地8:R1- 9:R1+ 10:地11:R2- 12:R2+ 13:地14:CLK- 15:CLK+ 16:

JTAG接口电路

JTAG接口电路 1 JTAG(Joint Test Action Group;联合测试行动小组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。 JTAG最初是用来对芯片进行测试的,JTAG的基本原理是在器件内部定义一个TAP(Test Access Port;测试访问口)通过专用的JTAG测试工具对进行内部节点进行测试。JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。现在,JTAG接口还常用于实现ISP(In-System Programmable�在线编程),对FLASH等器件进行编程。 JTAG编程方式是在线编程,传统生产流程中先对芯片进行预编程现再装到板上因此而改变,简化的流程为先固定器件到电路板上,再用JTAG编程,从而大大加快工程进度。JTAG接口可对PSD芯片内部的所有部件进行编程 具有JTAG口的芯片都有如下JTAG引脚定义: TCK——测试时钟输入; TDI——测试数据输入,数据通过TDI输入JTAG口; TDO——测试数据输出,数据通过TDO从JTAG口输出; TMS——测试模式选择,TMS用来设臵JTAG口处于某种特定的测试模式。 可选引脚TRST——测试复位,输入引脚,低电平有效。 含有JTAG口的芯片种类较多,如CPU、DSP、CPLD等。 JTAG内部有一个状态机,称为TAP控制器。TAP控制器的状态机通过TCK和TMS进行状态的改变,实现数据和指令的输入。图1为TAP控制器的状态机框图。 2 JTAG芯片的边界扫描寄存器 JTAG标准定义了一个串行的移位寄存器。寄存器的每一个单元分配给IC芯片的相应引脚,每一个独立的单元称为BSC(Boundary-Scan Cell)边界扫描单元。这个串联的BSC在IC内部构成JTAG回路,所有的BSR (Boundary-Scan Register)边界扫描寄存器通过JTAG测试激活,平时这些引脚保持正常的IC功能。图2为具有JTAG口的IC内部BSR单元与引脚的关系。 3 JTAG在线写Flash的硬件电路设计和与PC的连接方式 以含JTAG接口的StrongARM SA1110为例,Flash为Intel 28F128J32 16MB容量。SA1110的JTAG的TCK、TDI、TMS、TDO分别接PC并口的2、3、4、11线上,通过程序将对JTAG口的控制指令和目标代码从PC的并口写入JTAG的BSR中。在设计PCB时,必须将SA1110的数据线和地址线及控制线与Flash的地线线、数据线和控制线相连。因SA1110的数据线、地址线及

LVDS接口定义

LVDS接口又称RS-644总线接口,是20世纪90年代才出现的一种数据传输和接口技术。LVDS即低电压差分信号,这种技术的核心是采用极低的电压摆幅高速差动传输数据,可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点,其传输介质可以是铜质的PCB连线,也可以是平衡电缆。LVDS在对信号完整性、低抖动及共模特性要求较高的系统中得到了越来越广泛的应用。目前,流行的LVDS技术规范有两个标准:一个是TIA/EIA(电讯工业联盟/电子工业联盟)的ANSI/TIA/EIA-644标准,另一个是IEEE 1596.3标准。 如上图,就是一块单六位LVDS 30针接口的液晶屏,其中1脚GND就是地,2脚、3脚VCC就是电压,4、6、7脚为存储IC(一般为24C之类的芯片)的读写信号脚,就是我们常换DELL机器的屏所说的码片,这里面存储了屏的一些信息,如型号、生产日期等,DELL 之类的少类的机器就往屏上这个IC里写入了自家的识别信号。8脚R0-、9脚R0+为第一组LVDS信号,依次类推,每往下一组信号中间都空一脚,共三组R-及R+信号,一直到接口的17脚CLKIN-、18脚CLKIN+,这两脚很重要,断开一根线,屏就无法显示,R-+的信号,少了一根两根还可以点亮屏,当然会显示不正常!这四对信号用数字表量阻值表现为100欧--120欧(不同屏)。

像我以前装液晶显示器的时候,这个单六位LVDS,只要对应单六位,再对应屏的分辨率(分辨率很重要)写个程序,屏线只用十根线,几乎就可以点亮这类的屏!这类屏我们常称为单六,当然液晶显示器的屏还有单八,单八的就多了对R3-和R3+,别小看这多出的一对信号,液晶屏的色彩就会多很多~单八位的己经过时了,以前15寸的液晶显示器的屏很多都是单八位的。当然,还有双八的~现在的市面上的液晶显示器都是双八位的接口啦~ 这里,我可以大胆的说:笔记本上用的都是单六,和双六的~现在液晶显示器上用的都是双八位了,早期的还有TTL、TMDS、TCON接口的,这类接口的我们修本的完全不必了解。扯远了。。。当然,你别和我说:我狗年马日拆的一台液晶显示器里怎么就是单六的……这个就是中国的山寨文化了,你们都懂的……. 真正用于笔记本上的屏全部都是单六的,高档机有双六的,双六接口的就是我们所说的高分屏了。 以前如果超过了1280X800的分辨率的屏就一定是双六或双八的,当然现在出的LED的屏也是这样的,只不过单六的分辨率到了1366X768,略高一点点而己!LED的屏,屏信号也是LVDS的,说的LED只不过是背光源是LED发光的而己~ 双六接口的高分辨率的屏,多了四对信号: RS0-、RS0+,RS1-、RS1+,RS2-、RS2+,CLK2-、CLK2+。(有的屏的PDF档里为RB0-、RB0+之类的,其实都一样): 如果我们接双六屏线的时候,这四对信号不能接到R0-至CLK1+上面去,否则……你们懂的~ 早期的20针的笔记本屏的定义如下,懒得找图了,直接在百度找个定义说明,略加修改,你们自己研究下吧: 20PIN单6定义: 1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:地 8:R1- 9:R1+ 10:地 11:R2- 12:R2+ 13:地 14:CLK- 15:CLK+ 16空17空18空19 空20空; 每组信号线之间电阻为(数字表100~120欧左右) 20PIN双6定义: 1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:R1- 8:R1+ 9:R2- 10:R2+ 11:CLK- 12:CLK+ 13:RO1- 14:RO1+ 15:RO2- 16:RO2+ 17:RO3- 18:RO3+ 19:CLK1- 20:CLK1+6;

LVDS接口与MIPI接口

LVDS接口与MIPI接口 MIPI?(Mobile Industry Processor Interface) 是2003年由ARM, Nokia, ST ,TI等公司成立的一个联盟,目的是把手机内部的接口如摄像头、显示屏接口、射频/基带接口等标准化,从而减少手机设计的复杂程度和增加设计灵活性。 MIPI联盟下面有不同的WorkGroup,分别定义了一系列的手机内部接口标准,比如摄像头接口CSI、显示接口DSI、射频接口DigRF、麦克风 /喇叭接口SLIMbus等。统一接口标准的好处是手机厂商根据需要可以从市面上灵活选择不同的芯片和模组,更改设计和功能时更加快捷方便。下图是按照 MIPI的规划下一代智能手机的内部架构。 MIPI是一个比较新的标准,其规范也在不断修改和改进,目前比较成熟的接口应用有DSI(显示接口)和CSI(摄像头接口)。CSI/DSI分别是指其承载的是针对Camera或Display应用,都有复杂的协议结构。以DSI为例,其协议层结构如下:

CSI/DSI的物理层(Phy Layer)由专门的WorkGroup负责制定,其目前的标准是D-PHY。D-PHY 采用1对源同步的差分时钟和1~4对差分数据线来进行数据传输。数据传输采用DDR方式,即在时钟的上下边沿都有数据传输。 D- PHY的物理层支持HS(High Speed)和LP(Low Power)两种工作模式。HS模式下采用低压差分信号,功耗较大,但是可以传输很高的数据速率(数据速率为80M~1Gbps); LP模式下采用单端信号,数据速率很低(<10Mbps),但是相应的功耗也很低。两种模式的结合保证了MIPI总线在需要传输大量数据(如图像)时可以高速传输,而在不需要大数据量传输时又能够减少功耗。下图是用示波器捕获的MIPI信号,可以清楚地看到HS和LP信号。

常见LVDS接口液晶屏定义

常见LVDS 接口液晶屏定义 20PIN 单 6 定义: 1:电源 2:电源 3:地 4:地 5:R0- 6:R0+ 7:地 8:R1- 9:R1+ 10:地 11 :R2- 12:R2+ 13:地14 :CLK- 15 :CLK+ 16空 17 空 18 空 19 空 20 空 每组信号线之间电阻为(数字表 120 欧左右) 20PIN 双 6 定义: 1:电源 2:电源 3:地 4:地 5:R0- 6:R0+ 7:R1- 8 :R1+ 9:R2- 10 :R2+ 11 : CLK- 12:CLK+ 13: RO1- 14 :RO1+ 15: RO2- 16 :RO2+ 17: RO3- 18 : RO3+ 19: CLK1- 20 : CLK1+ 每组信号线之间电阻为(数字表 120 欧左右) 20PIN 单 8 定义: 1:电源 2:电源 3:地 4:地 5:R0- 6:R0+ 7:地 8:R1- 9:R1+ 10:地 11 :R2- 12:R2+ 13:地14 :CLK- 15 :CLK+ 16 : R3- 17 :R3+ 每组信号线之间电阻为(数字表 120 欧左右) 30PIN 单 6 定义: 1:空 2:电源 3:电源 4:空 5:空 6:空 7:空 8:R0- 9:R0+ 10:地 11 :R1- 12: R1+ 13:地14 :R2- 15 :R2+ 16:地17 :CLK- 18 :CLK+ 19:地20:空- 21 :空22:空23:空24:空25 :空 26 :空 27 :空 28 空 29 空 30 空 每组信号线之间电阻为(数字表 120 欧左右) 30PIN 单 8 定义: 1:空 2:电源 3:电源 4:空 5:空 6:空 7:空 8:R0- 9:R0+ 10:地 11 :R1- 12: R1+ 13:地14 :R2- 15 :R2+ 16:地 17 : CLK- 18 :CLK+ 19:地 20 :R3- 21 :R3+ 22:地 23:空 24:空

JTAG接口总结

并口与连接 1.并行口基地址: 0x0378 新系统通用,通常是LPT1,也可以是LPT2,通常使用中断IRQ7 0x0278 通常是LPT2,也可以是LPT1,LPT3(只能用此基地址),通常使用中断IRQ5 2.寄存器定义 3.状态寄存器(379)和控制寄存器(37A)的定义:

5.连接方式 a)hybus255与并口的连接是通过74CH541与并口连接 LPT D0 Pin 2 and TCK J10 Pin 4 LPT D1 Pin 3 and TDI J10 Pin 11 LPT D2 Pin 4 and TMS J10 Pin 9 LPT Busy Pin 11 and TDO J10 Pin 13 b)2410以及44b0连接图 TCK---------------->DATA0 TDI---------------->DATA1 TMS---------------->DATA2 TDO---------------->STATUS7

6.寄存器的读写 a)先对控制寄存器(Control)初始化 如果禁止中断用out(37A,0x80),如果使用中断用out(37A,0x90) b)写一个寄存器的两条基本指令: out(37B,addr);// 将addr写入用户设备地址寄存器 写:out(37C,data);// 将数据data写入addr指向的用户设备空间单元 读:in(37C);// 从addr指向的用户设备空间单元中读取数据 JTAG接口信息 1.TCK:输入移位时钟TMS和TDI的数据在TCK的上升沿被采样数据在时钟的下降沿输出到TDO 2.TMS:输入方式选择TMS用于控制TAP状态机 3.TDI:输入。输入到指令寄存器IR或数据寄存器DR的数据出现在TDI输入端在TCK的上升沿被采样 4.TDO:TDO输出来自指令寄存器或数据寄存器的数据在时钟的下降沿被移出到TDO

教你区分LVDS屏线及屏接口定义(精)

教你区分 LVDS 屏线及屏接口定义 现在碰到液晶屏大多是 LVDS 屏线 , 经常碰到什么单 6, 双 6 单 8双 8. 如何区分呢 ? 我以前也不知道 , 后在网上收集学习后才弄明白 方法 1 数带“ +-”的这种信号线一共有几对,有 10对的减 2对就是双 8, 有 8对的减 2对就是双 6。有 5对的减掉 1对是单 8, 有 4对的减掉 1对是单 6,数 +/-线一共有多少对。说通俗点就是 4对————单 6 5对————单 8 8对————双 6 10对————双 8 方法 2 拧开螺丝看看主板里面的电路,一般每对数据线之间都有一个 100欧姆的电阻,看到 4个的话就是单 6位的屏,看到 8个的话就是双六位, 5个的话一般是单 8位, 有10个一般就是双 8位,当然有资料的话就不用这么麻烦, 也有 TMDS 也用这种 20PIN 的连接头的,比如 LG 的 LP141X1,不过基本上很少 lvds 的接口的定义 20PIN 单 6定义: 1:电源 2:电源 3:地 4:地 5:R0- 6:R0+ 7:地 8:R1- 9:R1+ 10:地 11:R2- 12:R2+ 13:地14:CLK- 15:CLK+ 16空 17空 18空 19 空 20空

每组信号线之间电阻为(数字表 120欧左右 ,20PIN 双 6定义 1:电源 2:电源 3:地 4:地 5:R0- 6:R0+ 7:R1- 8:R1+ 9:R2- 10:R2+ 11:CLK- 12:CLK+ 13:RO1- 14:RO1+ 15: RO2- 16:RO2+ 17:RO3- 18:RO3+; 19:CLK1- 20:CLK1+ 每组信号线之间电阻为(数字表 120欧左右 20PIN 单 8定义: 1:电源 2:电源 3:地 4:地 5:R0- 6:R0+ 7:地 8:R1- 9:R1+ 10:地 11:R2- 12:R2+ 13:地14:CLK- 15:CLK+ 16:R3- 17:R3+ 每组信号线之间电阻为(数字表 120欧左右 30PIN 单 6定义: 1:空 2:电源 3:电源 4:空 5:空 6:空 7:空 8:R0- 9: R0+ 10:地 11:R1- 12:R1+ 13:地14:R2- 15:R2+ 16:地 17:CLK- 18:CLK+ 19:地 20:空 - 21:空 22:空 23:空 24:空 25:空26:空 27:空 28空 29空 30空 每组信号线之间电阻为(数字表 120欧左右 30PIN 单 8定义: 1:空 2:电源 3:电源 4:空 5:空 6:空 7:空 8:R0- 9: R0+ 10:地 11:R1- 12:R1+ 13:地14:R2- 15:R2+ 16:地 17:CLK- 18:CLK+ 19:地 20:R3- 21:R3+ 22:地 23:空 24:空 25:空26:空 27:空 28空 29空 30空 每组信号线之间电阻为(数字表 120欧左右

Jtag的各种引脚定义

使用过ARM芯片的人肯定都听过一个仿真器————JLINK,为什么ARM芯片现在能够这么流行?其中恐怕就有一个原因就是很多的ARM芯片都支持使用Jlink进行调试和仿真。所以你只要有一个Jlink,不管是ARM7、ARM9、ARM11还是最新的ARM Cortex 系统都能下载和调试了。 以前的嵌入式开发者,可能使用什么公司的芯片就得买一个对应芯片的下载和仿真器,这样如果你只使用一种芯片,可能还好,不过恐怕没有那种芯片能够一直引领市场。 Jlink使用的是一种叫做JTAG的协议,JTAG原本是用于芯片内部测试的,现在大多用于芯片的程序下载和调试仿真。由于现在Jlink用的比较多,所以有些人可能把Jlink就等同于JTAG了,实际上,JTAG是一种协议,只要满足这种协议的就可以叫做JTAG,比如H—JTAG、OpenJTAG、OSJTAG等等。正版的Jlink是卖的很贵的。大概是1000到2000RMB吧。不过,中国的山寨能力是很强的,而且你硬件卖给别人了,你也没办法控制别人说你不许拆开我的东西看里面的电路是怎么样的。所以Jlink就被破解了,破解之后的Jlink很便宜,网上五六十块钱就能买到一个能用的Jlink。 除了商业版的Jlink和H—JTAG,网上还有一些电子爱好者,他们参照开源软件的模式,设计了开源硬件,比如arduino。还有人制作了开源版本的JTAG仿真器——OpenJTAG。而一些芯片的开发商不像那些软件厂商,会给软件做很多的限制,他们对于开源硬件还是比较开明的,所以他们也支持了一些开源硬件。比如TI公司的MSP430 LaunchPad、ST公司的STM Discovery 等等板子。还有飞思卡尔公司的USBDM和OSJTAG。他们把这些硬件的原理图、PCB还有固件都放在了网络上供人自由下载和制作,你也可以根据他的资料进行改进。这样能使大家对于他们家的芯片有更多的了解,所以,他们也乐于开源一些评估板。 今天我要说的是几种JTAG仿真器的引脚定义,首先我看看比较常见的JTAG 20-Pin的引脚接口如下:

常见LVDS屏接口定义

2 常见屏的接口 LVDS接口: 比较常见的接口,有14针插接口,20P针插、30针插和片插等多为LVDS接口LVDS常用的驱动板: 2023(支持17寸以下含17寸的所有LVDS屏VGA烧录模式) 2025(支持19寸以下含19寸以下的所有LVDS屏VGA烧录模式) NTA91B(支持22寸或1680*1050以下的所有LVDS屏VGA烧录模式) 2621免程序驱动板(直接跳线就可支持14-19等LVDS屏免烧录) TTL接口:(与LVDS的屏线区别TTL的屏线相对较多) TTL屏要求驱动板输入单或双6位/8位的三基色的TTL电平,所以连接线用得比较多,一般有31扣41扣30软排线+40软排线60扣70扣80扣等,特点线比较多 驱动板: RTMC7B(新款TTL驱动板支持所有TTL接口协议还可支持TMDS TCON接口屏代替2013 2533 2033等驱动板) 鼎科2033V免程序驱动板 RSDS接口: 单50软排线、双40软排线(50+30)软排线一般为RSDS接口。 驱动板: MA4B:支持双40 30+50 单50软排线RSDS专用驱动板 TCON接口:Timing Controller(不常用) 现在很多的型号的液晶屏接受的是LVDS信号,而Driver IC收到的是RSDS信号,这中间就是由TCON实现的转换,不少屏是RSDS接口的,是PANEL厂家为了减少PANEL成本,省掉了TCON芯片,因为目前的很多驱动板IC都可以直接处理RSDS 信号了。 TMDS接口(不常用) 是一种类似于LVDS的接口。该接口在液晶发展中属于昙花一现。典型的有三星公司出的 LT181E2-131、LT170E2-131、日立的TX38D21V、LG的LP141X1等。 最新到货!!超小体积四灯小口高压板特价销售,联想方正系列超小体积电源高压一体板疯狂特价销 ? 上面我们知道了屏的型号和接口了,但是我们还不知道这个是多少位的屏和多少 的供电,为了让大家轻松搞会这一步,我们拿一个单6位LVDS的屏来解析一下,

JTAG接口连接方法

我的JLINK终于用上了,哈哈,好开心,终于不用考虑是不是要借用别人的PC 机了,昨天到城隍庙电子市场忙活了一下午,终于算是满载而归,呵呵,好了,下面说一下接法,其实根本不需要什么转接板什么的,直接把相应的几根线对接就可以用了,所以要参考电路图,上面为TQ2440开发板的JTAG电路图,下面为JLINK的20针电路图,下面的JLINKV7电路图是标准接口,网上到处都能找到 10针JTAG针序20针JTAG针序信号 1,21VTref -2NC 33nTRST -4GND 55TDI -6GND 77TMS 88GND 99TCK 1010GND -11RTCK -12GND 613TDO -14GND 415RESET -16GND -17DBGRQ -18GND

-195V-Supply -20GND 实际上只需要接4跟线,4号是自连回路,不需要接,1,2接的都是1管脚,而8,10接的是GND,也可以不接 ARM系统的JTAG接口的设计不当往往使硬件系统无法调试,所以在设计ARM系统前要先熟悉ARM系统的JTAG接口的定义和常见问题。 1.ARM系统的JTAG接口是如何定义的?每个PIN又是如何连接的? 下图是JTAG接口的信号排列示意: 接口是一个20脚的IDC插座。下表给出了具体的信号说明: 表 1 JTAG引脚说明 序号信号名方向说明 1 Vref Input 接口电平参考电压,通常可直接接电源 2 Vsupply Input 电源 3 nTRST Output (可选项) JTAG复位。在目标端应加适当的上拉电阻以防止误触发。 4 GND -- 接地 5 TDI Output Test Data In from Dragon-ICE to target. 6 GND -- 接地 7 TMS Output Test Mode Select 8 GND -- 接地 9 TCK Output Test Clock output from Dragon-ICE to the target

LVDS接口与MIPI接口

LVDS接口与MIPI接口 MIPI (Mobile Industry Processor Interface) 是2003年由ARM, Nokia, ST ,TI等公司成立的一个联盟,目的是把手机内部的接口如摄像头、显示屏接 口、射频/基带接口等标准化,从而减少手机设计的复杂程度和增加设计灵活性。MIPI联盟下面有不同的WorkGroup,分别定义了一系列的手机内部接口标准,比如摄像头接口CSI、显示接口DSI、射频接口DigRF、麦克风 /喇叭接口SLIMbus 等。统一接口标准的好处是手机厂商根据需要可以从市面上灵活选择不同的芯片和模组,更改设计和功能时更加快捷方便。下图是按照 MIPI的规划下一代智能手机的内部架构。 MIPI是一个比较新的标准,其规范也在不断修改和改进,目前比较成熟的接口应用有DSI(显示接口)和CSI(摄像头接口)。CSI/DSI分别是指其承载的是针对Camera或Display应用,都有复杂的协议结构。以DSI为例,其协议层结构如下:

CSI/DSI的物理层(Phy Layer)由专门的WorkGroup负责制定,其目前的标准是D-PHY。D-PHY采用1对源同步的差分时钟和1,4对差分数据线来进行数据传输。数据传输采用DDR方式,即在时钟的上下边沿都有数据传输。 D- PHY的物理层支持HS(High Speed)和LP(Low Power)两种工作模式。HS模式下采用低压差分信号,功耗较大,但是可以传输很高的数据速率(数据速率为80M,1Gbps); LP模式下采用单端信号,数据速率很低(<10Mbps),但是相应的功耗也很低。两种模式的结合保

JTAG接口介绍

JTAG(Joint Test Action Group,联合测试行动小组)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试,JTAG技术是一种嵌入式调试技术,它在芯片内部封装了专门的测试电路TAP(Test Access Port,测试访问口),通过专用的JTAG测试工具对内部节点进行测试。 目前大多数比较复杂的器件都支持JTAG协议,如ARM、DSP、FPGA器件等。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为测试模式选择、测试时钟、测试数据输入和测试数据输出。 JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。JTAG接口还常用于实现ISP(In-System Programmable在系统编程)功能,如对FLASH器件进行编程等。 通过JTAG接口,可对芯片内部的所有部件进行访问,因而是开发调试嵌入式系统的一种简洁高效的手段。目前JTAG接口的连接有两种标准,即14针接口和20针接口,其定义分别如下所示。 14针JTAG接口定义: 14针JTAG接口定义引脚名称描述 1、13VCC接电源 2、4、6、8、10、14GND接地 3nTRST测试系统复位信号 5TDI测试数据串行输入 7TMS测试模式选择 9TCK测试时钟

11TDO测试数据串行输出 12NC未连接 20针JTAG接口定义引脚名称描述 1VTref目标板参考电压,接电源 2VCC接电源 3nTRST测试系统复位信号 4、6、8、10、12、14、16、18、20GND接地 5TDI测试数据串行输入 7TMS测试模式选择 9TCK测试时钟 11RTCK测试时钟返回信号 13TDO测试数据串行输出 15nRESET目标系统复位信号 17、19NC未连接 下面以S3C4510B开发板为例说明JTAG接口: 在保证电源电路、晶振电路和复位电路正常工作的前提下,可通过JTAG接口调试S3C4510B,在系统上电前,首先应检测JTAG接口的TMS、TCK、TDI、TDO信号是否已与S3C4510B 的对应引脚相连,其次应检测S3C4510B的nEWAIT引脚(Pin71)是否已上拉,ExtMREQ 引脚(Pin108)是否已下拉,对这两只引脚的处理应注意,作者遇到多起S3C4510B不能正常工作或无法与JTAG接口通信,均与没有正确处理这两只引脚有关。 给系统上电后,可通过示波器查看S3C4510B对应引脚的输出波形,判断是否已正常工作,若S3C4510B已正常工作,在使能片内PLL电路的情况下,SDCLK/MCLKO引脚(Pin77)应输出频率为50MHz的波形,同时,MDC引脚(Pin50)和其他一些引脚也应有波形输出。

LVDS接口定义及标准

LVD LVD 低電對多線,廣泛盟)199公佈範,現,纜。高傳LVD 成,很高mV 在有的M 理很輸入1) S 接口定義DS 接口又稱電壓差分信多點的連接,也可以是平泛的應用。)的ANSI/T 95年11月佈了IEEE ,對於生產工,其供電電。標準推薦傳輸速率可DS 接口的原一個簡單,如圖1所高,驅動器電V 。通過驅有些最新生MAX9121/9在LVDS 很簡單,因為入端產生的來傳送信號表1是LV 表2 是接義及標準 稱RS-644信號,這種技接,具有低功平衡電纜。目前,流行TIA/EIA -6,以美國國1596.3標準工藝、傳輸電壓可以從+薦的最高數據可達1.923G 原理及電特單的LVDS 傳所示。驅動器電流大部分驅動器的開關生產的LVDS 9122等。 系統中,採為一對差分效果是相互號,從而可VDS 驅動器 接收器的主要4總線接口技術的核心是功耗、低誤。LVDS 在對行的LVDS 技644標準,國家半導體準。這兩個輸介質和供電+5V 到+3.3據傳輸速率Gbps 。 特性 傳輸系統由器的電流源分直接流過關,改變直S 接收器中採用差分方分線對上的電互抵消的,可以大大提高器的主要電 要電特性參,是20世紀是採用極低誤碼率、低串對信號完整技術規範有另一個是 體公司為主推個標準注重於電電壓等則3V ,甚至更率是655Mbp 一個驅動器源(通常為3100?的終直接流過電阻中,100?左方式傳送數據電流方向是因而對信號高數據傳輸電特性參數 參數。 紀90年代低的電壓擺幅串擾和低輻整性、低抖動有兩個標準IEEE 159推出了ANS 於對LVDS 則沒有明確更低;其傳輸ps ,而理論器和一個接3.5mA )來終端電阻,從阻的電流的左右的電阻直據,有著比是相反的,當號的影響很 輸速率和降低才出現的一幅高速差動輻射等特點動及共模特:一個是T 96.3標準。SI/TIA/EIA S 接口的電。LVDS 可輸介質可以論上,在一收器通過一來驅動差分線從而在接收的有無,從而直接集成在比單端傳輸方當共模方式很小。這樣,低功耗。 一種數據傳動傳輸數據,其傳輸介特性要求較高TIA/EIA (電 -644標準電特性、互連可採用CMO 以是PCB 連個無衰耗的一段差分阻線對,由於收器輸入端產而產生「1」在片內輸入端方式更強的式的噪聲耦合就可以採用 傳輸和接口技,可以實現介質可以是銅高的系統中電訊工業聯準。1996連與線路端OS 、GaAs 連線,也可的傳輸線上阻抗為100於接收器的直產生的信號」和「0」的端上了,如的共模噪聲抑合到線對上用很低的電技術。LVDS 現點對點或一銅質的PCB 中得到了越來盟/電子工業年3月,IE 端接等方面的s 或其他技術以是特製的上,LVDS 的?的導體連接直流輸入阻號幅度大約的邏輯狀態如MAXIM 公抑制能力。上時,在接收電壓擺幅(見S 即一點B 連來越業聯EE 的規術實的電的最接而阻抗350態。公司道收器見表