89C51管脚图

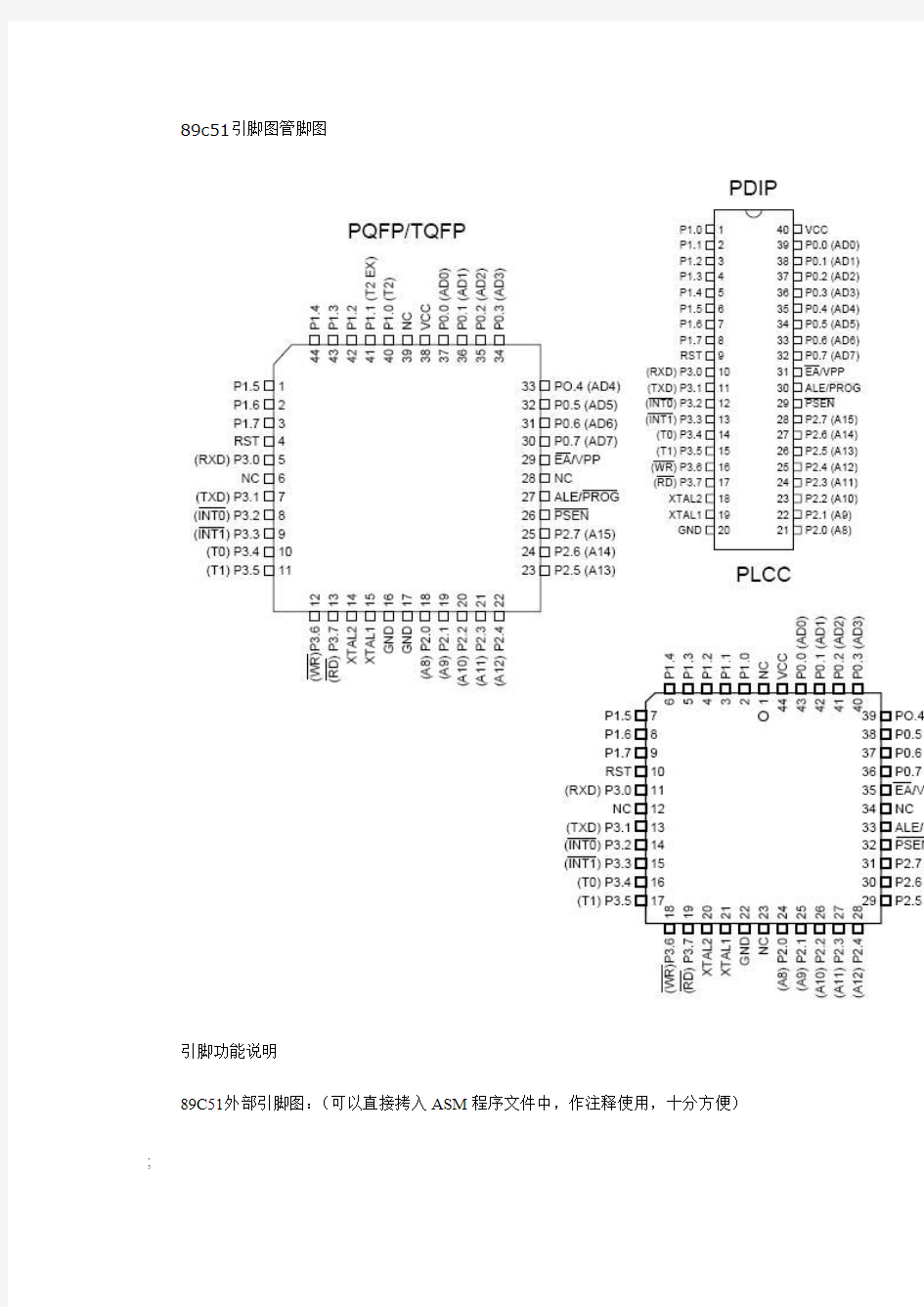

89c51引脚图管脚图

引脚功能说明

89C51外部引脚图:(可以直接拷入ASM程序文件中,作注释使用,十分方便);

┏━┓┏━┓

; P1.0 ┫1 ┗┛40┣Vcc

; P1.1 ┫2 39┣P0.0

; P1.2 ┫3 38┣P0.1

; P1.3 ┫4 37┣P0.2

; P1.4 ┫5 36┣P0.3

; P1.5 ┫6 35┣P0.4

; P1.6 ┫7 34┣P0.5

; P1.7 ┫8 33┣P0.6

; RST/Vpd ┫9 32┣P0.7

; RXD P3.0 ┫10 31┣-EA/Vpp(内1/外0 程序地址选择); TXD P3.1 ┫11 30┣ALE/-P (地址锁存输出)

; -INT0 P3.2 ┫12 29┣-PSEN (外部程序读选通输出); -INT1 P3.3 ┫13 28┣P2.7

; T0 P3.4 ┫14 27┣P2.6

; T1 P3.5 ┫15 26┣P2.5

; -WR P3.6 ┫16 25┣P2.4

; -RD P3.7 ┫17 24┣P2.3

; X2 ┫18 23┣P2.2

; X1 ┫19 22┣P2.1

; GND ┫20 21┣P2.0

; ┗━━━━┛

引脚说明:

①电源引脚

Vcc(40脚):典型值+5V。

Vss(20脚):接低电平。

②外部晶振

X1、X2分别与晶体两端相连接。当采用外部时钟信号时,X2接振荡信号,X1接地

。

③输入输出口引脚:

P0口:I/O双向口。作输入口时,应先软件置“ 1”。

P1口:I/O双向口。作输入口时,应先软件置“ 1”。

P2口:I/O双向口。作输入口时,应先软件置“ 1”。

P3口:I/O双向口。作输入口时,应先软件置“ 1”。

④控制引脚:

RST/Vpd、ALE/-PROG、-PSEN、-EA/Vpp组成了MSC-51的控制总线。

RST/Vpd(9脚):复位信号输入端(高电平有效)。

第二功能:加+5V备用电源,可以实现掉电保护RAM信息不丢失。

ALE/-PROG(30脚):地址锁存信号输出端。

第二功能:编程脉冲输入。

-PSEN(29脚):外部程序存储器读选通信号。

-EA/Vpp(31脚):外部程序存储器使能端。

第二功能:编程电压输入端(+21V)。

常用芯片引脚图

.v .. .. 常用芯片引脚 74LS00数据手册 74LS01数据手册 74LS02数据手册 74LS03数据手册 74LS04数据手册 74LS05数据手册 74LS06数据手册 74LS07数据手册 74LS08数据手册 74LS09数据手册 74LS10数据手册 74LS11数据手册

第2页 共8页 74LS12数据手册 74LS13数据手册 74LS14数据手册 74LS15数据手册 74LS16数据手册 74LS17数据手册 74LS19数据手册 74LS20数据手册 74LS21数据手册 74LS22数据手册 74LS23数据手册 74LS26数据手册 74LS27数据手册 74LS28数据手册

.v .. .. 74LS30数据手册 74LS32数据手册 74LS33数据手册 74LS37数据手册 74LS38数据手册 74LS40数据手册 74LS42数据手册 [1].要求0—15时,灭灯输入(BI )必须开路或保持高电平,如果不要灭十进制数零,则动态灭灯输入(RBI )必须开路或为高电平。 [2].将一低电平直接输入BI 端,则不管其他输入为何电平,所有的输出端均输出为低电平。 [3].当动态灭灯输入(RBI )和A,B,C,D 输入为低电平而试灯输入为高电平时,所有输出端都为低电平并且动态灭灯输入(RBO )处于第电平(响应条件)。 [4].]当灭灯输入/动态灭灯输出(BI/RBO )开朗路或保持高电平而试 灯输入为低电平时,所有各段输出均为高电平。 表中1=高电平,0=低电平。BI/RBO 是线与逻辑,作灭灯输入(BI )或动态灭灯(RBO )之用,或者兼为二者之用。

优先编码器74LS148

优先编码器74LS148 有些单片机控制系统和数字电路中,无法对几个按钮的同时响应做出反映,如电梯控制系统在这种情况下就出出现错误,这是绝对不允许的于是就出现了74ls148优先编码器,先说一下他的基本原理.他允许同时输入两个以上编码信号。不过在设计优先编码器时已经将所有的输入信号按优先顺序排了队,当几个输入信号同时出现时,只对其中优先权最高的一个进行编码。 〈74ls148管脚功能〉〈74ls148引脚图〉 74ls148优先编码器管脚功能介绍:为16脚的集成芯片,电源是VCC(16) GND(8),I0—I7为输入信号,A2,A1,A0为三位二进制编码输出信号,IE是使能输入端,OE是使能输出端,GS 为片优先编码输出端。 〈74ls148逻辑图〉〈74ls148逻辑表达式〉 使能端OE(芯片是否启用)的逻辑方程: OE =I0·I1·I2·I3·I4·I5·67·IE 当OE输入IE=1时,禁止编码、输出(反码):A2,A1,A0为全1。 当OE输入IE=0时,允许编码,在I0~I7输入中,输入I7优先级最高,其余依次为:

I6,I5,I4,I3,I2,I0,I0等级排列。 输入输出 EI I0I1I2I3I4I5I6I7A2A1A0GS EO 1 x x x x x x x x 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 0 0 x x x x x x x 0 0 0 0 0 1 0 x x x x x x 0 1 0 0 1 1 0 0 x x x x x 0 1 1 0 1 0 1 0 0 x x x x 0 1 1 1 0 1 1 1 0 0 x x x 0 1 1 1 1 1 0 0 1 0 0 x x 0 1 1 1 1 1 1 0 1 1 0 0 x 0 1 1 1 1 1 1 1 1 0 1 0 0 0 1 1 1 1 1 1 1 1 1 1 1 0 <优先编码器74ls148功能表> 从以上的的功能表中可以得出,74ls148输入端优先级别的次序依次为I7,I6,…,I0 。当某一输入端有低电平输入,且比它优先级别高的输入端没有低电平输入时,输出端才输出相应该输入端的代码。例如:I5=0且I6=I7=1(I6、I7优先级别高于I5) 则此时输出代码010 (为(5)10=(101)2的反码)这就是优先编码器的工作原理。

芯片引脚图及引脚描述

555芯片引脚图及引脚描述 555的8脚是集成电路工作电压输入端,电压为5~18V,以UCC表示;从分压器上看出,上比较器A1的5脚接在R1和R2之间,所以5脚的电压固定在2UCC/3上;下比较器A2接在R2与R3之间,A2的同相输入端电位被固定在UCC/3上。 1脚为地。2脚为触发输入端;3脚为输出端,输出的电平状态受触发器控制,而触发器受上比较器6脚和下比较器2脚的控制。 当触发器接受上比较器A1从R脚输入的高电平时,触发器被置于复位状态,3脚输出低电平; 2脚和6脚是互补的,2脚只对低电平起作用,高电平对它不起作用,即电压小于1Ucc/3,此时3脚输出高电平。6脚为阈值端,只对高电平起作用,低电平对它不起作用,即输入电压大于2 Ucc/3,称高触发端,3脚输出低电平,但有一个先决条件,即2脚电位必须大于1Ucc/3时才有效。3脚在高电位接近电源电压Ucc,输出电流最大可打200mA。 4脚是复位端,当4脚电位小于0.4V时,不管2、6脚状态如何,输出端3脚都输出低电平。 5脚是控制端。 7脚称放电端,与3脚输出同步,输出电平一致,但7脚并不输出电流,所以3脚称为实高(或低)、7脚称为虚高。 555集成电路管脚,工作原理,特点及典型应用电路介绍. 1 555集成电路的框图及工作原理 555集成电路开始是作定时器应用的,所以叫做555定时器或555时基电路。但后来经过开发,它除了作定时延时控制外,还可用于调光、调温、调压、调速等多种控制及计量检测。此外,还可以组成脉冲振荡、单稳、双稳和脉冲调制电路,用于交流信号源、电源变换、频率变换、脉冲调制等。由于它工作可靠、使用方便、价格低廉,目前被广泛用于各种电子产品中,555集成电路内部有几十个元器件,有分压器、比较器、基本R-S触发器、放电管以及缓冲器等,电路比较复杂,是模拟电路和数字电路的混合体,如图1所示。 2. 555芯片管脚介绍 555集成电路是8脚封装,双列直插型,如图2(A)所示,按输入输出的排列可看成如图2(B)所示。其中6脚称阈值端(TH),是上比较器的输入;2脚称触发端(TR),是下比较器的输入;3脚是输出端(Vo),它有O和1两种状态,由输入端所加的电平决定;7脚是放电端(DIS),它是内部放电管的输出,有悬空和接地两种状态,也是由输入端的状态决定;4脚是复位端(MR),加上低电平时可使输出为低电平;5脚是控制电压端(Vc),可用它改变上下触发电平值;8脚是电源端,1脚是地端。 图2 555集成电路封装图 我们也可以把555电路等效成一个带放电开关的R-S触发器,如图3(A)所示,这个特殊的触发器有两个输入端:阈值端(TH)可看成是置零端R,要求高电平,触发端(TR)可看成是置位端S,要求低电平,有一个输出端Vo,Vo可等效成触发器的Q端,放电端(DIS)可看成是由内部放电开关控制的一个接点,由触发器的Q端控制:Q=1时DIS端接地,Q=0时DIS 端悬空。另外还有复位端MR,控制电压端Vc,电源端VDD和 地端GND。这个特殊的触发器有两个特点: (1)两个输入端的触发电平要求一高一低,置零端R即阈值端(TH)要求高电平,而置位端s 即触发端(TR)则要求低电乎; (2)两个输入端的触发电平使输出发生翻转的阈值电压值也不同,当V c端不接控制电压时,对TH(R)端来讲,>2/3VDD是高电平1,<2/3VDD是低电平0:而对TR(S)端来讲,>1/3VDD是

常用运放芯片实物和引脚功能图_TL081-082-084运放引脚功能及贴片封装形式

常用运放芯片实物和引脚功能图_TL081/082/084运放引 脚功能及贴片封装形式 (1)运放芯片的3种型号序列(部分器件有此序列) 如TL081、TL082、TL084,分别为8引脚单运放;8引脚双运放;14引脚四运放集成器件。封装型式一般为塑封双列直插和贴片双列,环列封装形式比较少见。 图1 TL081/082/084运放引脚功能及贴片封装形式 而常见常用,仅为下述两种器件。 世界上有几个人?有两个人,男人和女人,不失为一个智慧的回答。常用运放芯片有几片,只有两片,8脚和14脚的双运放和四运放集成器件(8脚封装单运放器件和环列式封装器件应用较少),把此两种芯片引脚功能记住,检修中就不需要随时去查资料了。

图2 常用运放芯片实物和引脚功能图 如上图。其封装一般为塑封双列直插DIP8/DIP14和塑封贴片工艺封装SO8/SO14两种形式,随着电子线路板小型化精密化要求的提高,贴片元件的应用占据主流,直插式器件逐渐淡出人们的视野。但无论何种封装模式,其引脚功能、次序都是一样的,所以仅需记准8脚(双运放)和14脚(四运放)两种运放的引脚功能就够了。 (2)运放芯片的3种温度序列 任何一种集成IC器件,按应用温度范围不同,都可细分为3种器件,如LM358,实际上有LM158、LM258、LM358三种型号的产品,其引脚功能、内部结构、工作原理、供电电压等等都无差别,仅仅是应用温度范围差异甚大。 LM158 适应工作温度-50℃~125℃,军工用品(1类); LM258 适应工作温度-25℃~85℃,工业用品(2类); LM358 适应工作温度0℃~70℃,农用品(3类)。 单看参数,似乎LM258适用于山东地区,若用于东北地区,其参数有些不足。而LM358仅能适用于江南地区。而事实上并非如此,如低于2类品规格参数被淘汰到3类品的器件,可能是-24℃~84℃温度范围

51单片机常用芯片引脚图

常用芯片引脚图 一、 单片机类 1、MCS-51 芯片介绍:MCS-51系列单片机是美国Intel 公司开发的8位单片机,又可以分为多个子系列。 MCS-51系列单片机共有40条引脚,包括32 条I/O 接口引脚、4条控制引脚、2条电源引 脚、2条时钟引脚。 引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时 的地址/数据复用口。 P1.0~P1.7:P1口8位口线,通用I/O 接口无第二功能。 P2.0~P2.7:P2口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时传送高8位地址。 P3.0~P3.7:P3口8位口线,第一功能作为 通用I/O 接口,第二功能作为为单片机的控 制信号。 ALE/ PROG :地址锁存允许/编程脉冲输入信号线(输出信号) PSEN :片外程序存储器开发信号引脚(输出信号) EA/Vpp :片外程序存储器使用信号引脚/编程电源输入引脚 RST/VPD :复位/备用电源引脚 2、MCS-96 芯片介绍:MCS-96系列单片机是美国Intel 公司继MCS-51系列单片机之后推出的16位单 片机系列。它含有比较丰富的软、硬件 资源,适用于要求较高的实时控制场合。 它分为48引脚和68引脚两种,以48引 脚居多。 引脚说明: RXD/P2.1 TXD/P2.0:串行数据传出分发 送和接受引脚,同时也作为P2口的两条 口线 HS1.0~HS1.3:高速输入器的输入端 HS0.0~HS0.5:高速输出器的输出端(有 两个和HS1共用) Vcc :主电源引脚(+5V ) Vss :数字电路地引脚(0V ) Vpd :部RAM 备用电源引脚(+5V ) V REF :A/D 转换器基准电源引脚(+5V ) AGND :A/D 转换器参考地引脚 12345678910111213141516171819204039383736353433323130292827262524232221P1.0P1.1P1.2P1.3P1.4P1.5P1.6P1.7RST RXD/P3.0TXD/P3.1INT0/P3.2INT1/P3.3T0/P3.4T1/P3.5WR/P3.6RD/P3.7XTAL2XTAL1V SS V CC P0.0/AD 0P0.1/AD 1 P0.2/AD 2P0.3/AD 3P0.4/AD 4P0.5/AD 5P0.6/AD 6P0.7/AD 7 EA/V PP ALE/PROG PSEN P2.7/A 15P2.6/A 14P2.5/A 13 P2.4/A 12P2.3/A 11P2.2/A 10P2.1/A 9P2.0/A 8803180518751

常用芯片引脚图[1]

您的数字ID 是:463099 您的密码是:1.8667 附录三 常用芯片引脚图 一、单片机类 1、MCS-51 芯片介绍:MCS-51系列单片机是美国Intel 公司开发的8位单片机,又可以分为多个子系列。 MCS-51系列单片机共有40条引脚,包括32 条I/O 接口引脚、4条控制引脚、2条电源引脚、2条时钟引脚。引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时的地址/数据复用口。P1.0~P1.7:P1口8位口线,通用I/O 接口无第二功能。P2.0~P2.7:P2口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时传送高8位地址。 P3.0~P3.7:P3口8位口线,第一功能作为通用I/O 接口,第二功能作为为单片机的控制信号。 ALE/PROG :地址锁存允许/编程脉冲输入信号线(输出信号) PSEN :片外程序存储器开发信号引脚(输出信号) EA/Vpp :片外程序存储器使用信号引脚/编程电源输入引脚 RST/VPD :复位/备用电源引脚 2、MCS-96 芯片介绍:MCS-96系列单片机是美国Intel 公司继MCS-51系列单片机之后推出的16位单 片机系列。它含有比较丰富的软、硬件 资源,适用于要求较高的实时控制场合。 它分为48引脚和68引脚两种,以48引 脚居多。 引脚说明: RXD/P2.1TXD/P2.0:串行数据传出分发 送和接受引脚,同时也作为P2口的两条 口线 HS1.0~HS1.3:高速输入器的输入端 HS0.0~HS0.5:高速输出器的输出端(有 两个和HS1共用) Vcc :主电源引脚(+5V ) Vss :数字电路地引脚(0V ) Vpd :内部RAM 备用电源引脚(+5V ) V REF :A/D 转换器基准电源引脚(+5V ) AGND :A/D 转换器参考地引脚 XTAL1、XTAL2:内部振荡器反相器输 P1.0P1.1P1.2P1.3P1.4P1.5P1.6P1.7RST RXD/P3.0TXD/P3.1INT0/P3.2INT1/P3.3T0/P3.4T1/P3.5WR/P3.6RD/P3.7XTAL2XTAL1V SS

及其他系列芯片引脚图大全

一:分类 74ls00 2输入四与非门 74ls01 2输入四与非门 (oc) 74ls02 2输入四或非门 74ls03 2输入四与非门 (oc) 74ls04 六倒相器 74ls05 六倒相器(oc) 74ls06 六高压输出反相缓冲器/驱动器(oc,30v) 74ls07 六高压输出缓冲器/驱动器(oc,30v) 74ls08 2输入四与门 74ls09 2输入四与门(oc) 74ls10 3输入三与非门 74ls11 3输入三与门 74ls12 3输入三与非门 (oc) 74ls13 4输入双与非门 (斯密特触发) 74ls14 六倒相器(斯密特触发) 74ls15 3输入三与门 (oc) 74ls16 六高压输出反相缓冲器/驱动器(oc,15v) 74ls17 六高压输出缓冲器/驱动器(oc,15v) 74ls18 4输入双与非门 (斯密特触发) 74ls19 六倒相器(斯密特触发) 74ls20 4输入双与非门 74ls21 4输入双与门 74ls22 4输入双与非门(oc) 74ls23 双可扩展的输入或非门 74ls24 2输入四与非门(斯密特触发)

74ls25 4输入双或非门(有选通) 74ls26 2输入四高电平接口与非缓冲器(oc,15v) 74ls27 3输入三或非门 74ls28 2输入四或非缓冲器 74ls30 8输入与非门 74ls31 延迟电路 74ls32 2输入四或门 74ls33 2输入四或非缓冲器(集电极开路输出) 74ls34 六缓冲器 74ls35 六缓冲器(oc) 74ls36 2输入四或非门(有选通) 74ls37 2输入四与非缓冲器 74ls38 2输入四或非缓冲器(集电极开路输出74ls39 2输入四或非缓 冲器(集电极开路输出) 7 4ls40 4输入双与非缓冲器 7 4ls41 bcd-十进制计数器 7 4ls42 4线-10线译码器(bcd输入) 7 4ls43 4线-10线译码器(余3码输 入) 7 4ls44 4线-10线译码器(余3葛莱 码输入) 7 4ls45 bcd-十进制译码器/驱动器 7 4ls46 bcd-七段译码器/驱动器

常用芯片引脚图

. . 常用芯片引脚 74LS00数据手册 74LS01数据手册 74LS02数据手册 74LS03数据手册 74LS04数据手册 74LS05数据手册 74LS06数据手册 74LS07数据手册 74LS08数据手册 74LS09数据手册 74LS10数据手册 74LS11数据手册

第2页 共8页 74LS12数据手册 74LS13数据手册 74LS14数据手册 74LS15数据手册 74LS16数据手册 74LS17数据手册 74LS19数据手册 74LS20数据手册 74LS21数据手册 74LS22数据手册 74LS23数据手册 74LS26数据手册 74LS27数据手册 74LS28数据手册

. . 74LS30 数据手册 74LS32数据手册 74LS33 数据手册 74LS37 数据手册 74LS38数据手册 74LS40 数据手册 74LS42数据手册 [1].要求0—15时,灭灯输入(BI )必须开路或保持高电平,如果不要灭十进制数零,则动态灭灯输入(RBI )必须开路或为高电平。 [2].将一低电平直接输入BI 端,则不管其他输入为何电平,所有的输出端均输出为低电平。 [3].当动态灭灯输入(RBI )和A,B,C,D 输入为低电平而试灯输入为高电平时,所有输出端都为低电平并且动态灭灯输入(RBO )处于第电平(响应条件)。 [4].]当灭灯输入/动态灭灯输出(BI/RBO )开朗路或保持高电平而试灯 输入为低电平时,所有各段输出均为高电平。 表中1=高电平,0=低电平。BI/RBO 是线与逻辑,作灭灯输入(BI )或动态灭灯(RBO )之用,或者兼为二者之用。

常用单片机及其它芯片引脚图

一、 单片机类 1、MCS‐51 芯片介绍:MCS‐51系列单片机是美国Intel公司开发的8位单片机,又可以分为多个子系列。 MCS‐51系列单片机共有40条引脚,包括32 条I/O接口引脚、4条控制引脚、2条电源引脚、2条时钟引脚。 引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为 通用I/O接口,第二功能作为存储器扩展时的地址/数据复用口。 P1.0~P1.7:P1口8位口线,通用I/O接口无第二功能。 P2.0~P2.7:P2口8位口线,第一功能作为通用I/O接口,第二功能作为存储器扩展时传送高8位地址。 P3.0~P3.7:P3口8位口线,第一功能作为通用I/O接口,第二功能作为为单片机的控制信号。 ALE/ PROG:地址锁存允许/编程脉冲输入信号线(输出信号) PSEN:片外程序存储器开发信号引脚(输出信号) EA/Vpp:片外程序存储器使用信号引脚/编程电源输入引脚 RST/VPD:复位/备用电源引脚 2、MCS‐96 芯片介绍:MCS‐96系列单片机是美国Intel公司继MCS‐51系列单片机之后推出的16位单 片机系列。它含有比较丰富的软、硬件资源,适用于要求较高的实时控制场合。它分为48引脚和68引脚两种,以48引脚居多。 引脚说明: RXD/P2.1 TXD/P2.0:串行数据传出分发 送和接受引脚,同时也作为P2口的两条口线 HS1.0~HS1.3:高速输入器的输入端 HS0.0~HS0.5:高速输出器的输出端(有 两个和HS1共用) Vcc:主电源引脚(+5V) Vss:数字电路地引脚(0V) Vpd:内部RAM备用电源引脚(+5V) VREF:A/D转换器基准电源引脚(+5V) AGND:A/D转换器参考地引脚

74ls147引脚图管脚图和功能真值表

74ls147引脚图管脚图和功能真值表 优先编码器是当多个输入端同时有信号时,电路只对其中优先级别最高的输入信号进行编码。常用的集成优先编码器IC有10线-4线、8线-3线两种。10线-4线优先编码器常见的型号为54/74147、54/74LS147,8线-3线优先编码器常见的型号为54/74148、54/74LS148。 下面我们以TTL中规模集成电路74LS147为例介绍8421→BCD码优先编码器的功能。 10线-4线8421 BCD码优先编码器74LS147的真值表见表3.5。74LS147的引脚图如图3.5所示,其中第9脚NC为空。74LS147优先编码器有9个输入端和4个输出端。某个输入端为0,代表输入某一个十进制数。当9个输入端全为1时,代表输入的是十进制数0。4个输出端反映输入十进制数的BCD 码编码输出。 74LS147优先编码器的输入端和输出端都是低电平有效,即当某一个输入端低电平0时,4个输出端就以低电平0的输出其对应的8421 BCD编码。当9个输入全为1时,4个输入出也全为1,代表输入十进制数0的8421 BCD编码输出。 表3.5 74LS147的真值表

数字电路CD4511的原理(引脚及功能) CD4511是一个用于驱动共阴极 LED (数码管)显示器的 BCD 码—七段码译码器,特点:具有BCD转换、消隐和锁存控制、七段译码及驱动功能的CMOS电路能提供较大的拉电流。可直接驱动LED显示器。 CD4511 是一片 CMOS BCD—锁存/7 段译码/驱动器,引脚排列如图 2 所示。其中a b c d 为 BCD 码输入,a为最低位。LT为灯测试端,加高电平时,显示器正常显示,加低电平时,显示器一直显示数码“8”,各笔段都被点亮,以检查显示器是否有故障。BI为消隐功能端,低电平时使所有笔段均消隐,正常显示时, B1端应加高电平。另外 CD4511有拒绝伪码的特点,当输入数据越过十进制数9(1001)时,显示字形也自行消隐。LE是锁存控制端,高电平时锁存,低电平时传输数据。a~g是 7 段输出,可驱动共阴LED数码管。另外,CD4511显示数“6”时,a段消隐;显示数“9”时,d段消隐,所以显示6、9这两个数时,字形不太美观图3是 CD4511和CD4518配合而成一位计数显示电路,若要多位计数,只需将计数器级联,每级输出接一只 CD4511 和 LED 数码管即可。所谓共阴 LED 数码管是指 7 段 LED 的阴极是连在一起的,在应用中应接地。限流电阻要根据电源电压来选取,电源电压5V时可使用300Ω的限流电阻。 用CD4511实现LED与单片机的并行接口方法如下图:

常用芯片引脚图

附录三 常用芯片引脚图 一、 单片机类 1、MCS-51 芯片介绍:MCS-51系列单片机是美国Intel 公司开发的8位单片机,又可以分为多个子系列。 MCS-51系列单片机共有40条引脚,包括32 条I/O 接口引脚、4条控制引脚、2条电源引 脚、2条时钟引脚。 引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时 的地址/数据复用口。 P1.0~P1.7:P1口8位口线,通用I/O 接口无第二功能。 P2.0~P2.7:P2口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时传送高8位地址。 P3.0~P3.7:P3口8位口线,第一功能作为 通用I/O 接口,第二功能作为为单片机的控 制信号。 ALE/ PROG :地址锁存允许/编程脉冲输入信号线(输出信号) PSEN :片外程序存储器开发信号引脚(输出信号) EA/Vpp :片外程序存储器使用信号引脚/编程电源输入引脚 RST/VPD :复位/备用电源引脚 2、MCS-96 芯片介绍:MCS-96系列单片机是美国Intel 公司继MCS-51系列单片机之后推出的16位单 片机系列。它含有比较丰富的软、硬件 资源,适用于要求较高的实时控制场合。 它分为48引脚和68引脚两种,以48引 脚居多。 引脚说明: RXD/P2.1 TXD/P2.0:串行数据传出分发 送和接受引脚,同时也作为P2口的两条 口线 HS1.0~HS1.3:高速输入器的输入端 HS0.0~HS0.5:高速输出器的输出端(有 两个和HS1共用) Vcc :主电源引脚(+5V ) Vss :数字电路地引脚(0V ) Vpd :内部RAM 备用电源引脚(+5V ) V REF :A/D 转换器基准电源引脚(+5V ) AGND :A/D 转换器参考地引脚 12345678910111213141516171819204039383736353433323130292827262524232221P1.0P1.1P1.2P1.3P1.4P1.5P1.6P1.7RST RXD/P3.0TXD/P3.1INT0/P3.2INT1/P3.3T0/P3.4T1/P3.5WR/P3.6RD/P3.7XTAL2XTAL1V SS V CC P0.0/AD 0P0.1/AD 1 P0.2/AD 2P0.3/AD 3P0.4/AD 4P0.5/AD 5P0.6/AD 6P0.7/AD 7 EA/V PP ALE/PROG PSEN P2.7/A 15P2.6/A 14P2.5/A 13 P2.4/A 12P2.3/A 11P2.2/A 10P2.1/A 9P2.0/A 8803180518751

常用芯片引脚图

. . .. .v .. .. 常用芯片引脚 74LS00数据手册 74LS01数据手册 74LS02数据手册 74LS03数据手册 74LS04数据手册 74LS05数据手册 74LS06数据手册 74LS07数据手册 74LS08数据手册 74LS09数据手册 74LS10数据手册 74LS11数据手册

第2页 共8页 74LS12数据手册 74LS13数据手册 74LS14数据手册 74LS15数据手册 74LS16数据手册 74LS17数据手册 74LS19数据手册 74LS20数据手册 74LS21数据手册 74LS22数据手册 74LS23数据手册 74LS26数据手册 74LS27数据手册 74LS28数据手册

. . .. .v .. .. 74LS30数据手册 74LS32数据手册 74LS33数据手册 74LS37数据手册 74LS38数据手册 74LS40数据手册 74LS42数据手册 [1].要求0—15时,灭灯输入(BI)必须开路或保持高电平,如果不 要灭十进制数零,则动态灭灯输入(RBI)必须开路或为高电平。 [2].将一低电平直接输入BI端,则不管其他输入为何电平,所有的输 出端均输出为低电平。 [3].当动态灭灯输入(RBI)和A,B,C,D输入为低电平而试灯输入为高 电平时,所有输出端都为低电平并且动态灭灯输入(RBO)处于第电 平(响应条件)。 [4].]当灭灯输入/动态灭灯输出(BI/RBO)开朗路或保持高电平而试 灯输入为低电平时,所有各段输出均为高电平。 表中1=高电平,0=低电平。BI/RBO是线与逻辑,作灭灯输入(BI)或 动态灭灯(RBO)之用,或者兼为二者之用。

LS系列芯片引脚图 大全

74系列芯片引脚图资料大全 反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373 反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8 │六非门(OC高压输出) 74LS06 Y = A ││ │ 1 2 3 4 5 6 7 │ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND

Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│ Y =A+C )│四总线三态门74LS125 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND Vcc -G B1 B2 B3 B4 B8 B6 B7 B8 ┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位总线驱动器74LS245 │20 19 18 17 16 15 14 13 12 11│ )│ DIR=1 A=>B │ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A └┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘ DIR A1 A2 A3 A4 A5 A6 A7 A8 GND 页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑与门,与非门: Vcc 4B 4A 4Y 3B 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = AB )│ 2输入四正与门74LS08 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1B 1Y 2A 2B 2Y GND

74LS148四路抢答器设计报告

潍坊学院 专业课综合课程设计说明书 设计题目:四路抢答器设计 系部:信息与控制工程学院 专业:电气自动化技术 班级:一班 学生姓名: 2013年6月10日

目录 1.设计任务和要求 (3) 2.设计方案 (3) 2.1设计思路 (3) 2.2设计原理 (4) 2.3实现功能 (4) 3.硬件设计 (5) 3.1各功能电路连线图 (5) 3.2框图和说明 (6) 4.软件设计 (7) 5.小结 (8) 6.参考文献 (9)

1设计任务与要求 1.1 可同时供四名选手参赛,其编号分别是1-4,各用一个抢答按钮,按钮的编号和选手的编号相对应,给节目主持人设置一控制开关,用于控制系统的清零(编号显示数码管灭灯)抢答的开始。 1.2 抢答器具有数据锁存和显示的功能,抢答开始后,若有选手按抢答按钮,其编号立即所存,并在数码管上显示该选手的编号,同时封锁输入电路,禁止其他选手抢答。优先抢答选手的编号一直保持到主持人主持人将系统清零为止。 2 设计方案 2.1 设计思路 2.1.1 在给定5V直流电源电压的条件下设计一个可以容纳四组参赛者的抢答器,每组设定一个抢答按钮供参赛者使用。 2.1.2 设置一个系统清零和抢答控制开关K(该开关由主持人控制),当开关K被按下时,抢答开始(允许抢答),打开后抢答电路清零。 2.1.3 抢答器具有一个抢答信号的鉴别、锁存及显示功能。即有抢答信号输入(参赛者的开关中任意一个开关被按下)时,锁存相应的编号,并在LED数码管上显示出来,同时扬声器发生声响。此时再按其他任何一个抢答器开关均无效,优先抢答选手的编号一直保持不变,直到主持人将系统清除为止。 2.1.4 开关K按下后,抢答开始,开始10S倒计时。 2.2 设计原理 2.2.1原理图

常用芯片引脚图

常用芯片引脚 74LS00数据手册74LS01数据手册74LS02数据手册 74LS03数据手册74LS04数据手册74LS05数据手册 74LS06数据手册74LS07数据手册74LS08数据手册 74LS09数据手册74LS10数据手册74LS11数据手册

74LS12数据手册 74LS13数据手册 74LS14数据手册 74LS15数据手册 74LS16数据手册 74LS17数据手册 74LS19数据手册 74LS20数据手册 74LS21数据手册 74LS22数据手册 74LS23数据手册

74LS26数据手册74LS27数据手册74LS28数据手册 74LS30数据手册74LS32数据手册74LS33数据手册 74LS37数据手册74LS38数据手册74LS40数据手册 74LS42数据手册

[1].要求0—15时,灭灯输入(BI )必须开路或保持高电平,如果不要灭十进制数零,则动态灭灯输入(RBI )必须开路或为高电平。 [2].将一低电平直接输入BI 端,则不管其他输入为何电平,所有的输出端均输出为低电平。 [3].当动态灭灯输入(RBI )和A,B,C,D 输入为低电平而试灯输入为高电平时,所有输出端都为低电平并且动态灭灯输入(RBO )处于第电平(响应条件)。 [4].]当灭灯输入/动态灭灯输出(BI/RBO )开朗路或保持高电 平而试灯输入为低电平时,所有各段输出均为高电平。 表中1=高电平,0=低电平。BI/RBO 是线与逻辑,作灭灯输入(BI )或动态灭灯(RBO )之用,或者兼为二者之用。 74LS49数据手册 ·74XX49简介: [1].要求0—15时,灭灯输入(BI )必须开路或保持高电平。 [2].将一低电平直接输入BI 端,则不管其他输入为何电平,所有的输出端均输出为低电平。 [1].要求0—15时,灭灯输入(BI )必须开路或保持高电平,如果不要灭十进制数零,则动态灭灯输入(RBI )必须开路或为高电平。 [2].将一低电平直接输入BI 端,则不管其他输入为何电平,所有的输出端均输出为低电平。 [3].当动态灭灯输入(RBI )和A,B,C,D 输入为低电平而试灯输入为高电平时,所有各段灯输出(RBO )为低电平(响应条件)。[4].当灭灯输入/动态灭灯输出(BI/RBO )开 而试灯输入为低电平,则所有输出端都为1。

常见芯片管脚说明

触发器常用芯片: 7470与输入J-K正沿触发器(带置位和清除端) 7472、74H72、74L72与输入J-K主从触发器(带预置和清除端) 7472、74H72、74L72与输入J-K主从触发器(带预置和清除端) 7473、74H73、74L73、74LS73、74HC73、74C73双J-K主从触发器(带清除端) 7476、74 H76、74LS76、74HC76、74C76 双J-K主从触发器(带预置和清除端) 74LS78A、74HC78双J-K负沿触发器(带预置、公共清除和公共时钟端) 74H101与或输入J-K负沿触发器(带预置端) 74H102与输入J-K负沿触发器(带预置和清除端) 74H103双J-K负沿触发器(带清除端) 74H106双J-K负沿触发器(带预置和清除端) 74107、74LS107A、74HC107、74C107双J-K触发器(带清除端) 74109、74LS109A、74F109、74ALS109、74HC109双J-K正沿触发器(带预置和清除端)74110、74F110与输入J-K主从触发器(带数据锁定) 74111、74F111双J-K触发器(带数据锁定) 74LS112A、74F112、74ALS112、74S112、74HC112双J-K负沿触发器(带预置和清除端)功能表 74LS113A、74S113、74F113、74ALS113、74HC113双J-K负沿触发器(带预置) 功能表 74LS114A、74F114、74ALS114、74F114、74HC114双J-K负沿触发器(带预置、公共清除和公共时钟端) 功能表与74LS112A相同。 74276四J-K触发器 74376四J-K非触发器 D触发器的芯片介绍(74系列): 74HC74 74LS90双D触发器74LS74 74LS364八D触发器(三态) 7474、74 H74、74F74、74ALS74、74L74、74LS74A、74S74、74HC73、74C74双D型正沿触发器(带预置和清除端) 74174、74LS174、74F174、74ALS174、74S174、74HC174、74C174六D型触发器(带清除端)

常用芯片引脚图

常用芯片引脚 74LS00数据手册 74LS01数据手册 74LS02数据手册 74LS03数据手册 74LS04数据手册 74LS05数据手册 74LS06数据手册 74LS07数据手册 74LS08数据手册 74LS09数据手册 74LS10数据手册 74LS11数据手册

74LS12数据手册 74LS13数据手册 74LS14数据手册 74LS15数据手册 74LS16数据手册 74LS17数据手册 74LS19数据手册 74LS20数据手册 74LS21数据手册 74LS22数据手册 74LS23数据手册 74LS26数据手册 74LS27数据手册 74LS28数据手册

74LS30数据手册 74LS32数据手册 74LS33数据手册 74LS37数据手册 74LS38数据手册 74LS40数据手册 74LS42数据手册 [1].要求0—15时,灭灯输入(BI )必须开路或保持高电平,如果不要灭十进制数零,则动态灭灯输入(RBI )必须开路或为高电平。 [2].将一低电平直接输入BI 端,则不管其他输入为何电平,所有的输出端均输出为低电平。 [3].当动态灭灯输入(RBI )和A,B,C,D 输入为低电平而试灯输入为高电平时,所有输出端都为低电平并且动态灭灯输入(RBO )处于第电平(响应条件)。 [4].]当灭灯输入/动态灭灯输出(BI/RBO )开朗路或保持高电平而试灯 输入为低电平时,所有各段输出均为高电平。 表中1=高电平,0=低电平。BI/RBO 是线与逻辑,作灭灯输入(BI )或动态灭灯(RBO )之用,或者兼为二者之用。

常用芯片引脚图(1)

附录三 常用芯片引脚图 一、单片机类 1、MCS-51 芯片介绍:MCS-51系列单片机是美国Intel公司开发的8位单片机,又可以分为多个子系列。 MCS-51系列单片机共有40条引脚,包括32 条I/O接口引脚、4条控制引脚、2条电源引 脚、2条时钟引脚。 引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为 通用I/O接口,第二功能作为存储器扩展时 的地址/数据复用口。 P1.0~P1.7:P1口8位口线,通用I/O接口 无第二功能。 P2.0~P2.7:P2口8位口线,第一功能作为 通用I/O接口,第二功能作为存储器扩展时 传送高8位地址。 P3.0~P3.7:P3口8位口线,第一功能作为 通用I/O接口,第二功能作为为单片机的控 制信号。 ALE/ PROG:地址锁存允许/编程脉冲输入信号线(输出信号) PSEN:片外程序存储器开发信号引脚(输出信号) EA/Vpp:片外程序存储器使用信号引脚/编程电源输入引脚 RST/VPD:复位/备用电源引脚 2、MCS-96 芯片介绍:MCS-96系列单片机是美国Intel公司继MCS-51系列单片机之后推出的16位单 片机系列。它含有比较丰富的软、硬件 资源,适用于要求较高的实时控制场合。 它分为48引脚和68引脚两种,以48引 脚居多。 引脚说明: RXD/P2.1 TXD/P2.0:串行数据传出分发 送和接受引脚,同时也作为P2口的两条 口线 HS1.0~HS1.3:高速输入器的输入端 HS0.0~HS0.5:高速输出器的输出端(有 两个和HS1共用) Vcc:主电源引脚(+5V) Vss:数字电路地引脚(0V) Vpd:内部RAM备用电源引脚(+5V) V REF:A/D转换器基准电源引脚(+5V)P1.0 P1.1 P1.2 P1.3 P1.4 P1.5 P1.6 P1.7 RST INT0/P3.2 INT1/P3.3 WR/P3.6 RD/P3.7 XTAL2 XTAL1 V SS

74ls148优先编码器

实验六编码、译码显示电路 一、实验目的 1.熟悉七段发光二极管显示器的结构及工作原理。 2.掌握分段式显示译码电路的设计方法及调试方法。 3.掌握编码器的逻辑功能及其应用。 4.掌握中规模显示译码器74LS48和优先编码器74LS148的功能和使用方法。 二、手动实验预习要求及思考题 1.复习8/3线优先编码器74LS148的工作原理及逻辑功能。 2.复习中规模译码器74LS48的工作原理及逻辑功能。 3.用发光二极管组成的七段显示器按结构分为共阴极和共阳极两种,中规模译码器74LS48应采用哪种结构形式?为什么? 4.译码电路输出与笔画段之间是否要加限流电阻器。 5.设计一个能显示0、一、二、三,四个字形的译码逻辑电路,输入两变量A、B。 三、仿真实验要求 采用EWB或者PSpice软件仿真电路,以便将仿真结果与实验结果进行比较。 四、实验仪器及器件 1.TTL集成芯片若干 2.万用表一块 3.电子学综合实验装置一台 五、实验内容与步骤 1.七段显示译码器的设计和调试 选用共阴极数码管、与非门74LS00、反相器74LS04和510?限流电阻,根据预习中设计出的能显示0、一、二、三,四个字形的译码逻辑电路连好,调试电路,到数码管能显示0、一、二、三,四个字形为止。要求写出设计过程,列出真值表,写出逻辑表达式,画出逻辑图。 选做:设计一个译码器,输入为两个变量,输出能显示出数字0~9和字母AbCdEFHP 中任四个字形。 2.测试74LS48译码逻辑功能 74LS48的各管脚的功能为: (1)试灯输入:当将LT置成低电平时,不论A、B、C、D输入状态如何,记录显示器状态。 (2)灭灯输入:当将BI置成低电平时,不论A、B、C、D输入状态如何,记录显示器状态。 (3)灭零输入:在A、B、C、D均为低电平时,把_____ RBI端分别接高电平、低电平,观 察数码管显示情况。

74ls148管脚图引脚功能表真值表

74ls148管脚图引脚功能表真值表逻 有些单片机控制系统和数字电路中,无法对几个按钮的同时响应做出反映,如电梯控制系统在这种情况下就出出现错误,这是绝对不允许的。于是就出现了74ls148优先编码器,先说一下他的基本原理.他允许同时输入两个以上编码信号。不过在设计优先编码器时已经将所有的输入信号按优先顺序排了队,当几个输入信号同时出现时,只对其中优先权最高的一个进行编码。 〈74ls148管脚功能〉〈74ls148引脚图〉 74ls148优先编码器管脚功能介绍:为16脚的集成芯片,电源是VCC(16) GND(8), I0—I7为输入信号,A2,A1,A0为三位二进制编码输出信号,IE是使能输入端,OE是使能输出端,GS为片优先编码输出端。 〈74ls148逻辑图〉〈74ls148逻辑表达式〉 使能端OE(芯片是否启用)的逻辑方程:

OE =I0·I1·I2·I3·I4·I5·I6·I7·IE 当OE输入IE=1时,禁止编码、输出(反码):A2,A1,A0为全1。 当OE输入IE=0时,允许编码,在I0~I7输入中,输入I7优先级最高,其余依次为:I6,I5,I4,I3,I2,I0,I0等级排列。 输入输出 EI I 0I 1 I 2 I 3 I 4 I 5 I 6 I 7 A 2 A 1 A GS EO 1x x x x x x x x11111 01111111111110 0x x x x x x x000001 0x x x x x x0100110 0x x x x x01101010 0x x x x011101110 0x x x0111110010 0x x01111110110 0x011111111010 00111111111110 <优先编码器74ls148功能表> 从以上的的功能表中可以得出,74ls148输入端优先级别的次序依次为I7,I 6,…,I0 。当某一输入端有低电平输入,且比它优先级别高的输入端没有低电平输入时,输出端才输出相应该输入端的代码。例如:I5=0且I6=I7=1(I6、I7优先级别高于I5) 则此时输出代码010 (为(5)10=(101)2的反码)这就是优先编码器的工作原理。