hspice si仿真:package model的那些事儿

package model的那些事儿(全文完)

来源:https://www.360docs.net/doc/aa6889951.html,/bbs/thread-3185-1-1.html

写在前面的废话:

最近一直在捣鼓着IBIS5.0的spec,希望能在里面挖点金子出来,这不,一下子瞅见了眼生的[package model],于是乎,对它产生了很大的兴趣。以前在仿真中关于package一般只调用模型的[package]参数,或者[PIN]里面的参数,但是从来没用过[package model]这个东东,更何况在大多数IBIS模型里难觅它的踪影。为了一睹它的芳容,我们就来讲述下它的故事。

首先感谢下Triton版主的大力帮忙,Triton版主是个新好男人,耐心细致,哈哈。另外本文仅仅为个人学习总结,水平有限,文中难免会有错误之处,还请各位童鞋们和大侠们不吝赐教,多谢关注。

最后声明本文由作者亲作,如有雷同,实属荣幸,请需要转的童鞋务必注明来自https://www.360docs.net/doc/aa6889951.html,论坛。

好了,废话结束,也不知道大家对这个话题有没有热情,要是大家都感兴趣的话就准备开掰。

——阿笨2012.1.6

先给个概要:

1. [package] [pin] [package model]的“爱恨情仇”

2. [package model]的自述

3. 用hspice调用package参数的区别

1. [package] [pin] [package model]的“爱恨情仇”

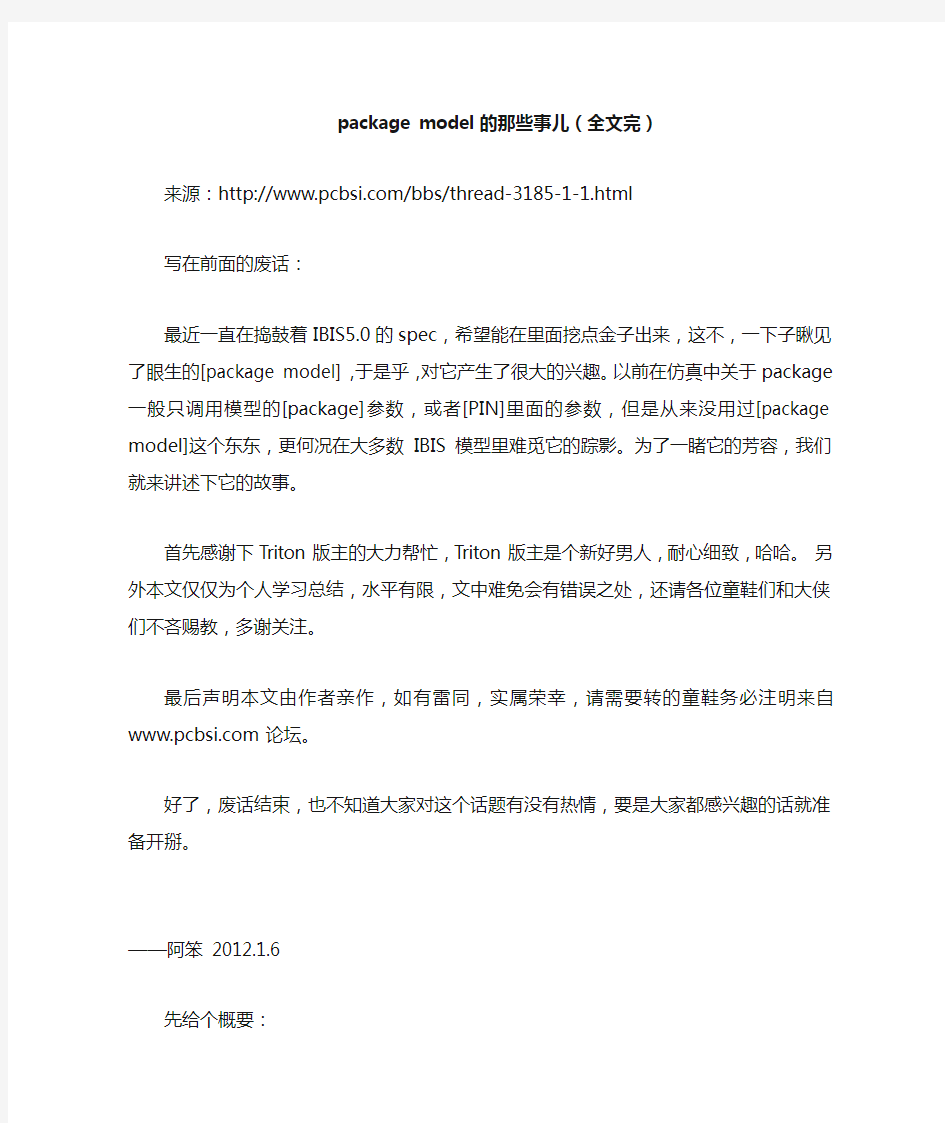

那我们就从[package]说起吧,首先来一段[package]的示例,图1

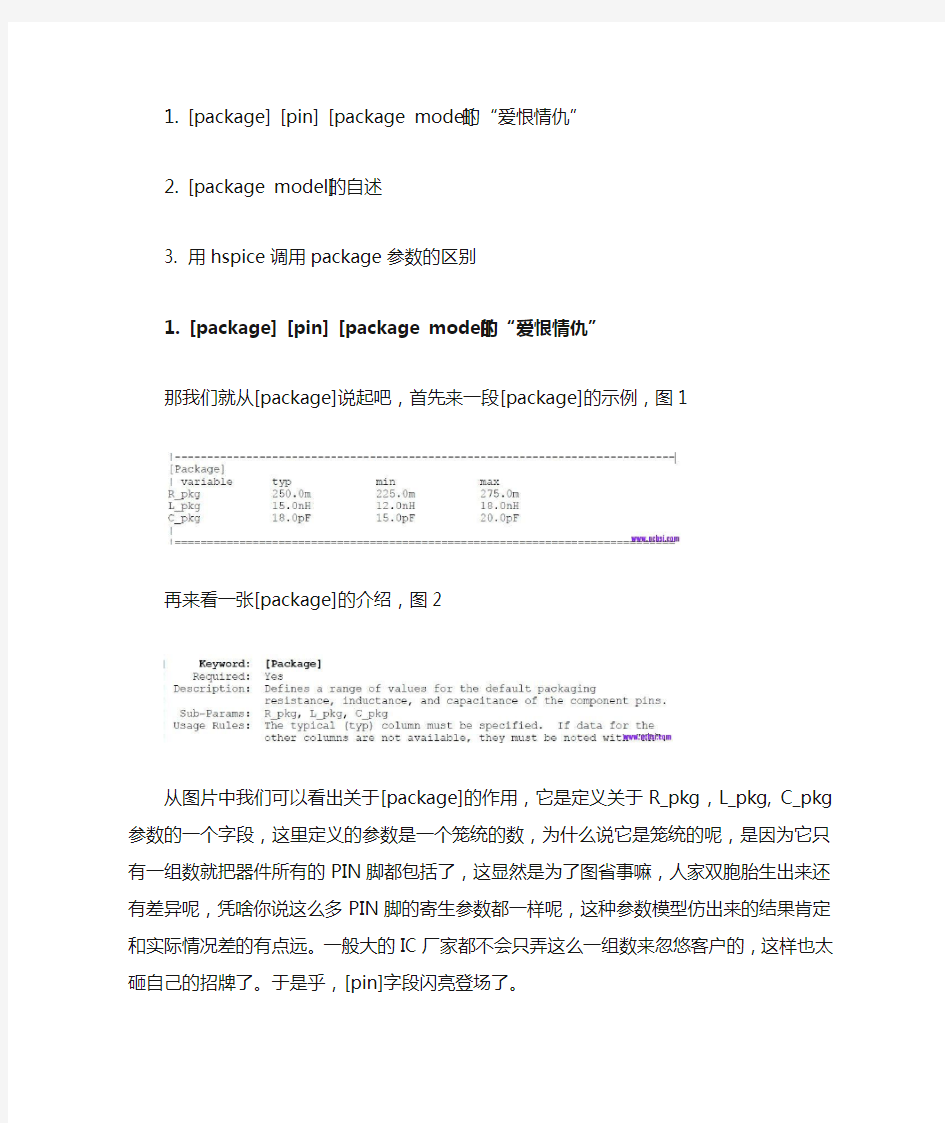

再来看一张[package]的介绍,图2

从图片中我们可以看出关于[package]的作用,它是定义关于R_pkg,L_pkg, C_pkg参数的一个字段,这里定义的参数是一个笼统的数,为什么说它是笼统的呢,是因为它只有一组数就把器件所有的PIN脚都包括了,这显然是为了图省事嘛,人家双胞胎生出来还有差异呢,凭啥你说这么多PIN脚的寄生参数都一样呢,这种参数模型仿出来的结果肯定和实际情况差的有点远。一般大的IC厂家都不会只弄这么一组数来忽悠客户的,这样也太砸自己的招牌了。于是乎,[pin]字段闪亮登场了。

按照惯例,先来看一张[pin]字段的例子,图3

接着看一下[pin]字段的introduction,图4

上图的描述里我们可以看出[pin]字段不仅仅描述了每个PIN脚的package参数,同时也描述了管脚的编号,管脚的信号名称,管脚的模型名称,包含的内容还是蛮多的。由于[PIN]字段里的package信号具体到了每个管脚,不像[package]一组数据打天下,所以用它仿真出来的结果还算勉勉强强接近实际,所以大家看到的ibis模型里既有[package]字段数据,又有[pin]字段数据的比较多。刚才说到为什么[pin]字段仿真出来的结果是勉勉强强接近实际呢,这是因为[pin]字段和[package]字段一样,仅仅用一阶的RLC电路来描述整个package的特性,可能在频率不太高的情况下可以做个参考,但是到了高频后这显然是不够的,PIN与PIN之间的耦合信息,IC内部的bondwire信息等等全部没有。有人会说用3D全波电磁场建模可以解决问题,当然能这么做是最好了,可惜往往事与愿违,package的3D模型不是每个厂家都能提供的。而让手头仅有的资源发挥出最大的作用是我们可以做的事情,同时ibis模型也祭出了绝招,那就是[package model]!!!

这次我们不给示例,先看下[package model]在IBIS5.0的spec里的说明,图5

大家看到这个说明几句话就结束了,都没看明白写的啥意思是吧,咱们暂时先不急,关于[package model]的内容我们第2章在来详细说明,接下来我们该说说[package] [pin] [package model]的“爱恨情仇”了。

看下面一段话,图6

这段话是来自[package]字段里的,它的意思是当[PIN]字段里要是定义了每个pin的package 参数,那么以[PIN]字段里的信息为优先考虑,要是[package model]字段也被定义了,那么同样[package model]字段里的信息也优先于[package]字段的信息。

也就是说[package model]>[package]

[PIN]>[package]

文中我没找到[package model]与[PIN]的优先级顺序,要是哪位童鞋找到的话可以告知一下,在我自己的理解里当然是[package model]>[PIN],可惜现在找不到证据。不过不打紧,软件调用的时候可以自己定义的,你愿意用哪个就用哪个。

上面说了这么多,我们明显看出来[package model]在3个字段当中的优势,"这是为什么呢"(咳咳~,必须是小沈阳腔调)。[package model]究竟是何方神圣,它又有怎样的独门绝技。。

2. [package model]的自述

OK,广告回来了,[package model]也该登场了,先看一段示例,因为太长我只截了一小部分,图7

首先看一下[package model]的介绍,图8

这段话的意思是在IBIS里定义了[package model]后,[package model]字段内容可以出现在.ibs文件里,也可以出现在一个单独的以.PKG为后缀名的文件里。

我们再看下[package model]的整体结构,见图9

这里的第一行[Define Package Model]是什么意思呢,上面我们刚说了[package model]

字段内容可以出现在两种地方,当出现在.PKG为后缀名的文件里时它靠什么来和.ibs文件来联系呢,对,就是这个[Define Package Model],这里的keyword一定要和.ibs里定义的[package model]名称是一致的,这样仿真软件才能根据这个名称找到正确的.PKG文件.

接下来3个字段[Manufacturer],[OEM],[Description]属于描述性质的,大家完全可以忽略,对仿真没有什么影响。

底下就是[Number Of Sections]了,看下图片说明,图10

[Number Of Sections]是描述了组成寄生参数桩线的最大分段数目,这个桩线是什么意思呢,它是连接硅圆焊盘和引脚之间的线,包含了bondwire,bondwir与pin之间的连线以及pin本身,它一般是由几段线组成,每段线的参数是不一样的,可能有的童鞋对这段IC内部的引线没有什么概念,下面给大家展示一张IC内部的3D的图形,应该就能明白不少了,图11

这个3D结构模型很清楚,黄色的是硅圆焊盘,淡青色的是PIN脚,PIN脚通过封装由IC内部伸出IC的外部为我们所用。而里面的那些蓝色的线就是我们说的package stub

(寄生参数桩线),可以很明显的看出它是有弯曲的,不是一条直线下来的。

接下来是[Number Of Pins],这个看字面意思应该也能理解了,就是器件的引脚个数,不再多说.

底下是[Pin Numbers],这个看起来和刚才的[Number Of Pins]是不是很像呀,但是它们的意思就差的远了,来看下它的介绍,图12

从介绍里可以看出,当前面的[Number Of Sections]要是有定义的话,那么这里就是给[Number Of Sections]做的一个详细信心,包括每段的长度啊,电感值,电容值,电阻值,分支信息等等,这里的东西还是蛮多的,我就不再展开多说,有兴趣的童鞋可以自己查阅下IBIS的spec。说实话我自己从来都没看到过有哪家厂家会给出[Number Of Sections]和[Pin Numbers]信息,可能这段会涉及到什么保密信息?不太清楚,不过还是贴上一段示例给大家看下,spec上的,图13

上面那个例子包含了bondwire,第1段线的信息,第2段线的信息,还有分支的信息。

OK,终于到了[Model Data]了,这个是块大头,我们慢慢往下看,这个[Model Data]里包含了[Resistance Matrix],[Inductance Matrix],[Capacitance Matrix],翻译过来就是电阻矩阵,电感矩阵和电容矩阵。先给个示例,图14

眼尖的童鞋可能发现了在[Resistance Matrix],[Inductance Matrix],[Capacitance Matrix]后面有Banded_matrix,Sparse_matrix和Full_matrix,这三个关键字的意思是解释了电容,电阻,电感矩阵的特点,分别表示为一维矩阵,多维矩阵和全矩阵(暂且我先这么翻译吧)。这个是什么意思呢,底下解释。

首先得弄清楚电容,电阻,电感矩阵里到底有什么信息,首先看电组的,大家都知道电组是没有耦合效果的,所以它的矩阵里面只是能一维的(Banded_matrix),也就是说一个脚对应一个数,给个示范,图15

图里面的[row]应该是器件的管脚编号,另外还有个[Bandwidth]的关键字,说实话我也不太清楚是干嘛的,说明里面只是说只有[Resistance Matrix]时才有效,是表示矩阵的带宽,哪位童鞋知道的也请告之一声。

接着我们看电感和电容的,电感和电容是有自感(自容)和互感(互容),所以说它们的矩阵只能是Sparse_matrix或者是Full_matrix,Sparse_matrix是多维矩阵,以我的理解来看,它是指定某个管脚和其他指定管脚的相互关系(要是理解不对大家可以提出来),给段示例,图16

以[row]为1时我们看,1和1之间的关系就是1脚的自容值,底下分别是1和2脚的互容值,底下类似.

再看Full_matrix,顾名思义嘛,就是有每一个管脚的自容(自感)信息和这个管脚对其他管脚的互容(互感)信息。所以它只需要指定每个[row]的值。这里打个比方,比如一个器件有10个脚,我们首先指定[ROW]为1脚,则这个[row]的数据肯定有10个,1_1,1_2,1_3...1_10,等[ROW]为2脚时,那么[row]的数据只有9个了2_2,2_3...2_10,因为2_1和1_2是同一个意思,前面已经定义过了,如此类推,到最后一个脚时那只有一个数据了。给个例子,图17

这个例子里定义的电感矩阵为Full_matrix,一共器件有8个脚,所以[row]为1时有8个数据。。。等[row]为8时则为1个数据了.

至此,[package model]的内容基本都说完了,是不是觉得里面的东西比[package]和[pin]多的多呢,由于[package model]内东西太多,所以不截图了,随后给大家一个例子下载。现在总结下[package model]的主要内容。

1. [Number Of Sections]和[Pin Numbers]里定义了package stub的信息,但是这两个字段平时在[package model]很难见到,一般厂家都不去定义。

2. [Model Data]这里主要是电阻,电容和电感的矩阵,包含了电阻信息,自容自感和互容互感信息,当然仿真的精度肯定是Banded_matrix 最后还有一个地方自己仍比较模糊,就是[Bandwidth]仍不清楚它所表达的意思,哪位知道的童鞋可以指点一下,多谢。 俗话说,学以致用,说完了[package model],[package]和[pin],底下就是如何在仿真中调用它们了。 要知后事如何,请听下回分解。。。 3. 用hspice调用package参数的区别 上面啰啰嗦嗦了一大堆关于[package model],[package]和[pin]的相关知识,底下咱们就得学以致用了。对于用来说当然是仿真软件如何调用了,首先我们先来看下[package]和[pin]字段参数调用,因为[package]和[pin]字段参数都为一阶的RLC参数,所以放在一起说。 其实在hspice里对这种管脚对应好的RLC电路描述相信大家看到的比较多了,一般先用B-element来调用需要仿真的那个管脚对应的buffer,然后再用节点描述RLC电路,图18 或者将RLC电路定义成一个子电路来调用,图19 但是我们遇到了[package model]怎么办,[package model]里不仅有管脚的自容自感信息,也有互容互感信息,要是还用上一种方法显然不太管用,要是能有一个方法,让软件在仿真中自动去取PIN脚的封装信息就好了,既可以不用自己去写语句描述,也不用担心粗心出错,一举两得啊,到底有没有这样的方法呢,答案是肯定的,有!!! 可能对hspice比较熟悉的童鞋已经猜到了,这个方法就是.IBIS Component Command,我们先看下这个语法的组成结构吧,见图20 第一行的'ibis_name'指的是这个示例的名字,简单的说就是起个名字吧,没什么好说的。 第二行的file指的是指定一个.ibs文件,这个也没啥说的。 第三行的component指的是.ibs文件中你要仿真的器件名称,因为.ibs文件里可能包含好几个器件,需要你手动选择下。 第四行的mod_sel和上面意思类似,因为一个管脚可能对应不同的buffer模型,你需要指定一个你想用的模型。 第五行的package我们需要着重说下,这个地方是重点,先来张截图,图21 截图是hspice的文档对这里package的说明,意思是这里的package有4个值可选,0指的是不调用任何package参数,1指的是用[package]字段里的RLC参数,2指的是用[pin]字段里的RLC参数。3的话是最有意思了,我们分个小段开看下 3的后面有个(default)字样,因为package这项是可选项,你要是不对它进行定义的话,那么package的值就为3,那3究竟是说明什么意思呢:上面说了,要是[Package Model]被定义了的话,那么3指的是用[Package Model]字段里的RLC参数,要是[Package Model]没有定义,那么3指的就是[pin]字段里的RLC参数。要是[pin]里也没有RLC参数的话,那么3指的就是[package]字段里的RLC参数。 这里我们也可以印证第一节得出来的结果,那就是这三个字段的调用优先级为[package model]>[pin]>[package]。 第六行的typ其实就是对应了.ibs里的typ max min三组数,不再多说。 我们大致的把.IBIS Component Command的结构描述了一遍,看到这里有的童鞋可能会迷糊了,你这个.IBIS仅仅调用的是一个整的器件信息,没有涉及到单个管脚的内容,我到底怎么样才能对单个管脚进行操作,或者说软件是怎样把单个管脚和它对应的package 参数联系起来的。这个大家先不要着急,咱们来看一个示例,图22 看了这个示例大家可能就有点明白了,我上面的红框圈起来的就是器件的实际管脚编号。其实只要我们知道了单个管脚buffer的节点就可以对单个管脚进行操作了,用.IBIS调用的buffer节点和B-element是几乎一样的,但是有点微小的差别,那就是节点是由ibisname_PIN_nd组成,假设我要对ibis_name为'pcomp'的第U1管脚的“使能”节点进行操作,那这个节点名称就为pcomp_U1_en,其他节点都类似,给大家截图节点说明图,图23 其实常用的节点是ibis_name_PIN_i,ibis_name_PIN_o,ibis_name_PIN_en,ibis_name_PIN(pin脚的最终输出或者输入),要是还有哪个童鞋仍然看不懂的话,就需要恶补下buffer节点知识了。 OK,理论的说完了,咱们应该亲自实践下看这个方法好不好使,实践出真知嘛,底下我们来进行一个示例来验证下这种方法是否能够正常调用[package model],由于带[package model]的.ibs模型不是很好找,附件会为大家奉献一个。(此.ibs模型由本论坛坛友fengjie19871128提供,在此表示感谢。) 首先编写网表,图24 文件中[package]的RLC参数都改为0或者NA,图25 容数据从4.755e-13改成4.755e-12,图26 大家是不是仿真的时候很长,呵呵,确实是,跑出来的结果我们就可以看出来为什 么要跑这么久,图27 图上可以看到软件把那些没有用到的管脚都跑了一遍,一共有105个脚,工作量当然大了,这里我没也发现啥好方法能有优化的,只能手动改.ibs文件了。所以电脑不太好的朋友就得注意了,很可能会跑卡住的。 接下来在对比下package=3和package=0的波形,图28 图上面是package=3也就是调用[package model]的RLC参数的波形,下图是不调用任何波形,能够明显看出来[package model]的RLC参数确实在仿真结果中起到了作用,说明我们的调用方法是可行的。 本文到此基本上就结束了,在1楼附上示例网表和相关的.ibs文件供大家参考。 参考文档: (I/O Buffer Information Specification)IBIS ver5.0 spec.pdf doc_help of Hspcie:hspice_si.pdf,hspice_cmdref.pdf 写在最后的话: 第一次写这么多字的文章,也花了不少心思,只是想提供一种方法供大家参考,使用仿真软件并不难,主要是在仿真过程中所涉及到的背景知识自己是否真正的明白和掌握。这几天里总觉得帖子人气不够,可能大家对这个话题不感兴趣,或者是自己水平有限,写的比较烂。不管怎么说,还是感谢大家的关注,要是这篇拙作真的能够给大家带来一些帮助的话那就实现了它的价值了。 本来还想和大家聊聊关于频域仿真时PORT的理解和使用心得,无奈年底较忙,计划 只能暂时搁浅,待以后有时间再续。 §电路级和行为级仿真 §直流特性分析、灵敏度分析 §交流特性分析 §瞬态分析 §电路优化(优化元件参数) §温度特性分析 §噪声分析 例(Hspicenetlist for the RC network circuit): .title A SIMPLE AC RUN .OPTIONS LIST NODE POST .OP .AC DEC 10 1K 1MEG .PRINT AC V(1) V(2) I(R2) I(C1) V1 1 0 10 AC 1 R1 1 2 1K R2 2 0 1K C1 2 0 .001U .END 输出文件:一系列文本文件 ?*.ic:initial conditions for the circuit ?*.lis:text simulation output listing ?*.mt0,*.mt1…:post-processor output for MEASURE statements ?*.pa0 :subcircuit path table ?*.st0 :run-time statistics ?*.tr0 ,*.tr1…:post-processor output for transient analysis ?*.ac0,*.ac1…: post-processor output for AC analysis .TITLE 语句 .TITLE IC课程设计报告 题目TSPC锁存器的设计与HSPICE仿真学院 专业 班级 学生姓名 日期 指导教师(签字) HSPICE简介 SPICE(Simulator Program with Integrated Circuit Emphasis,以集成电路为重点的模拟程序)模拟器最初于20世纪70年代在berkeley开发完成,能够求解描述晶体管、电阻、电容以及电压源等分量的非线性微分方程。SPICE 模拟器提供了许多对电路进行分析的方法,但是数字VLSI电路设计者的主要兴趣却只集中在直流分析(DC analysis)和瞬态分析(transient analysis)两种方法上,这两种分析方法能够在输入固定或实时变化的情况下对节点的电压进行预测。SPICE程序最初是使用FORTRAN语言编写的,所以SPICE就有其自身的一些相关特点,尤其是在文件格式方面与FORTRAN有很多相似之处。现在,大多数平台都可以得到免费的SPICE版本,但是,往往只有商业版本的SPICE 才就有更强的数值收敛性。尤其是HSPICE,其在工业领域的应用非常广泛,就是因为其具有很好的收敛性,能够支持最新的器件以及互连模型,同事还提供了大量的增强功能来评估和优化电路。PSPICE也是一个商业版本,但是其有面向学生的限制性免费版本。本章所有实例使用的都是HSPICE,这些实例在平台版本的SPICE中可能不能正常运行。 虽然各种SPICE模拟器的细节随着版本和操作平台的不同而各不相同,但是所有版本的SPICE都是这样工作的:读入一个输入文件,生产一个包括模拟结果、警告信息和错误信息的列表文件。因为以前输入文件经常是以打孔卡片盒的方式提供给主机的,所以人们常常称输入文件为SPICE“卡片盒(deck)”,输入文件中的每一行都是一张“卡片”。输入文件包含一个由各种组件和节点组成的网表。当然输入文件也包含了一些模拟选项、分析指令以及器件模型。网吧可以通过手工的方式输入,也可以从电路图或者CAD工具的版图(layout)中提取。 一个好的SPICE“卡片盒”就好像是一段好的软件代码,必须具有良好的可读性、可维护性以及可重用性。适当地插入一些注释和空白间隔有助于提高“卡片盒”的可读性。一般情况下,书写SPICE“卡片盒”的最好方法就是:先找一个功能完备、正确的“卡片盒”范例,然后在此基础上对其进行修改。 Hspice简明手册 Hspice简明手册 Hspice是一个模拟电路仿真软件,在给定电路结构和元器件参数的条件下,它可以模拟和 计算电路的各种性能。用Hspice分析一个电路,首先要做到以下三点: (1)给定电路的结构(也就是电路连接关系)和元器件参数(指定元器件的参数库); (2)确定分析电路特性所需的分析内容和分析类型(也就是加入激励源和设置分析类 型); (3)定义电路的输出信息和变量。 Hspice规定了一系列输入,输出语句,用这些语句对电路仿真的标题,电路连接方式,组 成电路元器件的名称,参数,模型,以及分析类型,以及输出变量等进行描述。 一Hspice输入文件的语句和格式 Hspice输入文件包括电路标题语句,电路描述语句,分析类型描述语句,输出描述语句, 注释语句,结束语句等六部分构成,以下逐一介绍: 1 电路的标题语句 电路的标题语句是输入文件的第一行,也成为标题行,必须设置。它是由任意字母和字 符串组成的说明语句,它在Hspice的title框中显示。 2 电路描述语句 电路描述语句由定义电路拓扑结构和元器件参数的元器件描述语句,模型描述语句和电 源语句等组成,其位置可以在标题语句和结束语句之间的任何地方。(1)电路元器件 Hspice要求电路元器件名称必须以规定的字母开头,其后可以是任意数字或字母。除 了名称之外,还应指定该元器件所接节点编号和元件值。 电阻,电容,电感等无源元件描述方式如下: R1 1 2 10k (表示节点1 与2 间有电阻R1,阻值为10k 欧) C1 1 2 1pf (表示节点1 与2 间有电容C1,电容值为1pf) L1 1 2 1mh (表示节点1 与2 间有电感L1,电感值为1mh) 半导体器件包括二极管,双极性晶体管,结形场效应晶体管,MOS 场效应晶体管等, 这些半导体器件的特性方程通常是非线性的,故也成为非线性有源元件。在电路CAD工具 进行电路仿真时,需要用等效的数学模型来描述这些器件。 (a)二极管描述语句如下: 时序计算和Cadence仿真结果的运用 中兴通讯康讯研究所EDA设计部余昌盛刘忠亮 摘要:本文通过对源同步时序公式的推导,结合对SPECCTRAQuest时序仿真方法的分析,推导出了使用SPECCTRAQuest进行时序仿真时的计算公式,并对公式的使用进行了说明。 关键词:时序仿真源同步时序电路时序公式 一.前言 通常我们在时序仿真中,首先通过时序计算公式得到数据信号与时钟信号的理论关系,在Cadence仿真中,我们也获得了一系列的仿真结果,怎样把仿真结果正确的运用到公式中,仿真结果的具体含义是什么,是我们正确使用Cadence仿真工具的关键。下面对时序计算公式和仿真结果进行详细分析。 二.时序关系的计算 电路设计中的时序计算,就是根据信号驱动器件的输出信号与时钟的关系(Tco——时钟到数据输出有效时间)和信号与时钟在PCB上的传输时间(Tflytime)同时考虑信号驱动的负载效应、时钟的抖动(Tjitter)、共同时钟的相位偏移(Tskew)等,从而在接收端满足接收器件的建立时间(Tsetup)和保持时间(Thold)要求。通过这些参数,我们可以推导出满足建立时间和保持时间的计算公式。 时序电路根据时钟的同步方式的不同,通常分为源同步时序电路(Source-synchronous timing)和共同时钟同步电路(common-clock timing)。这两者在时序分析方法上是类似的,下面以源同步电路来说明。 源同步时序电路也就是同步时钟由发送数据或接收数据的芯片提供。图1中,时钟信号是由CPU驱动到SDRAM方向的单向时钟,数据线Data是双向的。 图1 图2是信号由CPU 向SDRAM 驱动时的时序图,也就是数据与时钟的传输方向相同时 的情况。 Tsetup ’ Thold ’ CPU CLK OUT SDRAM CLK IN CPU Signals OUT SDRAM Signals IN Tco_min Tco_max T ft_clk T ft_data T cycle SDRAM ’S inputs Setup time SDRAM ’S inputs Hold time 图2 图中参数解释如下: ■ Tft_clk :时钟信号在PCB 板上的传输时间; ■ Tft_data :数据信号在PCB 板上的传输时间; ■ Tcycle :时钟周期 ■ Tsetup’:数据到达接收缓冲器端口时实际的建立时间; ■ Thold’:数据到达接收缓冲器端口时实际的保持时间; ■ Tco_max/Tco_min :时钟到数据的输出有效时间。 由图2的时序图,我们可以推导出,为了满足接收芯片的Tsetup 和Thold 时序要求,即 Tsetup’>Tsetup 和Thold’>Thold ,所以Tft_clk 和Tft_data 应满足如下等式: Tft_data_min > Thold – Tco_min + Tft_clk (公式1) Tft_data_max < Tcycle - Tsetup – Tco_max + Tft_clk (公式2) 当信号与时钟传输方向相反时,也就是图1中数据由SDRAM 向CPU 芯片驱动时,可 以推导出类似的公式: Tft_data_min > Thold – Tco_min - Tft_clk (公式3) Tft_data_max < Tcycle - Tsetup – Tco_max - Tft_clk (公式4) 如果我们把时钟的传输延时Tft_clk 看成是一个带符号的数,当时钟的驱动方向与数据 驱动方向相同时,定义Tft_clk 为正数,当时钟驱动方向与数据驱动方向相反时,定义Tft_clk 为负数,则公式3和公式4可以统一到公式1和公式2中。 三.Cadence 的时序仿真 在上面推导出了时序的计算公式,在公式中用到了器件手册中的Tco 参数,器件手册中 Tco 参数的获得,实际上是在某一种测试条件下的测量值,而在实际使用上,驱动器的实际 负载并不是手册上给出的负载条件,因此,我们有必要使用一种工具仿真在实际负载条件下 的信号延时。Cadence 提供了这种工具,它通过仿真提供了实际负载条件下和测试负载条件 下的延时相对值。 我们先来回顾一下CADENCE 的仿真报告形式。仿真报告中涉及到三个参数:FTSmode 、 电路模拟实验专题 实验文档 一、简介 本实验专题基于SPICE(Simulation Program With Integrated Circuit)仿真模拟,讲授电路模拟的方法和spice仿真工具的使用。 SPICE仿真器有很多版本,比如商用的PSPICE、HSPICE、SPECTRE、ELDO,免费版本的WinSPICE,Spice OPUS等等,其中HSPICE和SPECTRE功能更为强大,在集成电路设计中使用得更为广泛。因此本实验专题以HSPICE和SPECTRE作为主要的仿真工具,进行电路模拟方法和技巧的训练。 参加本实验专题的人员应具备集成电路设计基础、器件模型等相关知识。 二、Spice基本知识(2) 无论哪种spice仿真器,使用的spice语法或语句是一致的或相似的,差别只是在于形式上的不同而已,基本的原理和框架是一致的。因此这里简单介绍一下spice的基本框架,详细的spice语法可参照相关的spice教材或相应仿真器的说明文档。 首先看一个简单的例子,采用spice模拟MOS管的输出特性,对一个NMOS管进行输入输出特性直流扫描。V GS从1V变化到3V,步长为0.5V;V DS从0V变化到5V,步长为0.2V;输出以V GS为参量、I D与V DS之间关系波形图。 *Output Characteristics for NMOS M1 2 1 0 0 MNMOS w=5u l=1.0u VGS 1 0 1.0 VDS 2 0 5 .op .dc vds 0 5 .2 Vgs 1 3 0.5 .plot dc -I(vds) .probe *model .MODEL MNMOS NMOS VTO=0.7 KP=110U +LAMBDA=0.04 GAMMA=0.4 PHI=0.7 .end 描述的仿真电路如下图, CADENCE工具VIRTUSO/DRACULA入门介绍 (2) 1.使用V IRTUSO/D IV A/D RACULA之前的准备 (2) 1.1.找一台装有IC工具的服务器 (2) 1.2.连接到这台计算机上 (2) 2.IC工具的软件环境配置 (3) 2.1.创建IC工具的启动目录,即工作目录。 (3) 2.2.将配置文件拷贝到IC工具的启动目录 (3) 2.3.将工艺文件和显示文件拷贝至工作目录 (3) 2.4.启动IC工具,命令为icfb& (3) 3.IC工具的使用 (4) 3.1.新建一个设计库 (4) 3.2.Compile一个工艺文件 (5) 3.3.创建新设计 (5) 3.4.编辑电路图 (5) 3.5.编辑版图 (6) 3.6.根据习惯改变版图层次的显示特性 (7) 3.7.完成版图编辑之后保存,退出 (8) 4.版图的DRC检查 (8) 4.1.基于Diva的方式(不推荐) (8) 4.2.基于Dracula的方式(推荐) (8) 5.LVS (10) 5.1.准备版图的GDS文件 (10) 5.2.准备电路网表 (10) 5.3.用LOGLVS转换电路网表成LVS要求格式 (11) 5.4.修改lvs的命令文件 (12) 5.5.运行PDRACULA来生成lvs任务的可执行文件 (12) 5.6.在控制台下,运行https://www.360docs.net/doc/aa6889951.html,文件 (12) 5.7.查看错误 (12) 5.8.修正版图或网表错误 (13) 6.一些小经验 (13) 7.附件清单 (14) Cadence工具Virtuso/Dracula入门介绍 (以上华0.6um DPDM工艺设计库为例) Cadence 是一套功能强大的EDA软件,包含有诸如IC、SE等常用芯片设计工具。其中IC是针对全定制芯片设计应用的,IC本身仍是一套工具集。本手册主要讨论其中的全定制版图设计工具Virtuso和验证工具Diva/Dracula之使用方法。其中Diva是基于Xwindow 的方式,而Dracula是基于命令行的方式;Virtuso中提供这两者的相关接口。 采用Virtuso/ Diva/Dracula进行芯片的设计和验证大致有如下几步:准备schmematic(电路)、画layout(版图)、作版图设计规则检查(DRC)、做电路与版图的一致性检查(LVS)、导出最终版图的gds文件。 缩写术语: ERC: Electrical Rule Check DRC: Design Rule Check LVS: Layout Versus Schematic LPE: Layout Parameter Extraction PRE: Parasitic Resistor Extraction 1.使用Virtuso/Diva/Dracula之前的准备 1.1.找一台装有IC工具的服务器 Virtuso不能单独安装,所以只有在安装了IC工具的计算机上才能使用。 [例]机房的10台服务器(IP:219.223.169.111到219.223.169.120)都能使用Virtuso/Diva/Dracula. 1.2.连接到这台计算机上 除非是在自己的计算机上安装有IC工具,否则您必须保证能够从您的计算机远程登录到装有IC的服务器上。 [例]以登录服务器IC来说明远程登录方法: a.向管理员申请用户(每个人都已经有了一个用户) b.下载远程登录软件Exceed, 在本地计算机上安装; 安装完毕之后进行远程登录配置: 在开始菜单→程序→Hummingbird.Exceed.v7.1.Multilanguage→Exceed→Client Wizard设定xterm,Host:219.223.169.111,Host type: Linux(下拉菜单选择),其余next即可。c.完成登录。 采用其它方式比如vnc、xWin、SSH Secure Shell Client等远程终端方法登录。 『注意』使用不同的远程登陆软件连接服务器;不同的服务器所需的软件设置均有所不同,配置细节请咨询曾经使用过该登陆软件的师兄师姐或同学。 第一章在Allegro 中准备好进行SI 仿真的PCB 板图 1)在Cadence 中进行SI 分析可以通过几种方式得到结果: * Allegro 的PCB 画板界面,通过处理可以直接得到结果,或者直接以*.brd 存盘。 * 使用SpecctreQuest 打开*.brd,进行必要设置,通过处理直接得到结果。这实际与上述方式类似,只不过是两个独立的模块,真正的仿真软件是下面的SigXplore 程序。 * 直接打开SigXplore 建立拓扑进行仿真。 2)从PowerPCB 转换到Allegro 格式 在PowerPCb 中对已经完成的PCB 板,作如下操作: 在文件菜单,选择Export 操作,出现File Export 窗口,选择ASCII 格式*.asc 文件格式,并指定文件名称和路径(图1.1)。 图1.1 在PowerPCB 中输出通用ASC 格式文件 图1.2 PowerPCB 导出格式设置窗口 点击图1.1 的保存按钮后出现图1.2 ASCII 输出定制窗口,在该窗口中,点击“Select All”项、在Expand Attributes 中选中Parts 和Nets 两项,尤其注意在Format 窗口只能选择PowerPCB V3.0 以下版本格式,否则Allegro 不能正确导入。 3)在Allegro 中导入*.ascPCB 板图 在文件菜单,选择Import 操作,出现一个下拉菜单,在下拉菜单中选择PADS 项,出现PADS IN 设置窗口(图1.3),在该窗口中需要设置3 个必要参数: 图1.3 转换阿三次文件参数设置窗口 i. 在的一栏那填入源asc 文件的目录 第一章概 论 §1.1 HSPICE简介 随着微电子技术的迅速发展以及集成电路规模不断提高,对电路性能的设计要求越来越严格,这势必对用于大规模集成电路设计的EDA工具提出越来越高的要求。自1972年美国加利福尼亚大学柏克莱分校电机工程和计算机科学系开发的用于集成电路性能分析的电路模拟程序SPICE (Simulation Program with ICEmphasis)诞生以来,为适应现代微电子工业的发展,各种用于集成电路设计的电路模拟分析工具不断涌现。HSPICE是MetaSoftware公司为集成电路设计中的稳态分析,瞬态分析和频域分析等电路性能的模拟分析而开发的一个商业化通用电路模拟程序,它在柏克莱的SPICE(1972年推出),MicroSim公司的PSPICE(1984年推出)以及其它电路分析软件的基础上,又加入了一些新的功能,经过不断的改进,目前已被许多公司、大学和研究开发机构广泛应用。HSPICE可与许多主要的EDA设计工具,诸如Candence,Workview等兼容,能提供许多重要的针对集成电路性能的电路仿真和设计结果。采用HSPICE软件可以在直流到高于100MHz的微波频率范围内对电路作精确的仿真、分析和优化。在实际应用中,HSPICE能提供关键性的电路模拟和设计方案,并且应用HSPICE进行电路模拟时,其电路规模仅取决于用户计算机的实际存储器容量。 §1.2 HSPICE的特点与结构 HSPICE除了具备绝大多数SPICE特性外,还具有许多新的特点,主要有: 优越的收敛性 精确的模型参数,包括许多Foundry模型参数 层次式节点命名和参考 基于模型和库单元的电路优化,逐项或同时进行AC,DC和瞬态分析中的优化 具备蒙特卡罗(Monte Carlo)和最坏情况(worst-case)分析 对于参数化单元的输入、出和行为代数化 具备较高级逻辑模拟标准库的单元特性描述工具 对于PCB、多芯片系统、封装以及IC技术中连线间的几何损耗加以模拟 在HSPICE中电路的分析类型及其内部建模情况如图1.2.1和图1.2.2所示: IC课程设计报告 题目 TSPC锁存器的设计与HSPICE仿真学院 专业 班级 学生姓名 日期 指导教师(签字) HSPICE简介 SPICE(Simulator Program with Integrated Circuit Emphasis,以集成电路为重点的模拟程序)模拟器最初于20世纪70年代在berkeley开发完成,能够求解描述晶体管、电阻、电容以及电压源等分量的非线性微分方程。SPICE 模拟器提供了许多对电路进行分析的方法,但是数字VLSI电路设计者的主要兴趣却只集中在直流分析(DC analysis)和瞬态分析(transient analysis)两种方法上,这两种分析方法能够在输入固定或实时变化的情况下对节点的电压进行预测。SPICE程序最初是使用FORTRAN语言编写的,所以SPICE就有其自身的一些相关特点,尤其是在文件格式方面与FORTRAN有很多相似之处。现在,大多数平台都可以得到免费的SPICE版本,但是,往往只有商业版本的SPICE 才就有更强的数值收敛性。尤其是HSPICE,其在工业领域的应用非常广泛,就是因为其具有很好的收敛性,能够支持最新的器件以及互连模型,同事还提供了大量的增强功能来评估和优化电路。PSPICE也是一个商业版本,但是其有面向学生的限制性免费版本。本章所有实例使用的都是HSPICE,这些实例在平台版本的SPICE中可能不能正常运行。 虽然各种SPICE模拟器的细节随着版本和操作平台的不同而各不相同,但是所有版本的SPICE都是这样工作的:读入一个输入文件,生产一个包括模拟结果、警告信息和错误信息的列表文件。因为以前输入文件经常是以打孔卡片盒的方式提供给主机的,所以人们常常称输入文件为SPICE“卡片盒(deck)”,输入文件中的每一行都是一张“卡片”。输入文件包含一个由各种组件和节点组成的网表。当然输入文件也包含了一些模拟选项、分析指令以及器件模型。网吧可以通过手工的方式输入,也可以从电路图或者CAD工具的版图(layout)中提取。 一个好的SPICE“卡片盒”就好像是一段好的软件代码,必须具有良好的可读性、可维护性以及可重用性。适当地插入一些注释和空白间隔有助于提高“卡片盒”的可读性。一般情况下,书写SPICE“卡片盒”的最好方法就是:先找一个功能完备、正确的“卡片盒”范例,然后在此基础上对其进行修改。 二、要与要求 在两相时钟技术中,必须十分小心的对两个时钟信号进行布线以保证它们的 标签:cadence工具介绍 cadence工具介绍 主要是cadence的常用工具: (一)System & Logic Design & Verification 1、SPW:系统仿真工具,与matlab相似,但是比其专业,用于系统建模,常用于通信系统2、Incisive: 就是大家最常用的nc_verilog, nc_sim, nc_lauch,以及ABV,TBV的集合,仿真和验证功能很强大 (二)Synthesis & Place & Route 1、BuildGates:与DC同期推出的综合工具,但是在国内基本上没有什么市场,偶尔有几家公司用2、RTL Complil er:继BuildGates之后的一个综合工具,号称时序,面积和功耗都优于DC,但是仍然无法取代人们耳熟能详的DC 3、Silicon Ensemble & PKS: 硅谷早期做物理设计的工程师,几乎都用它。是第一个布局布线工具4、First Encount er & SoC Encounter: 继SE以后的很好的P&R工具,但是盗版太少,所以也只有大公司能用且都用,但是目前astro在国内有赶超之意5、Cetlic :噪声分析工具,权威6、Fire&Ice: 分布参数提取工具,国内很多人用synopsys的StarRC 7、VoltageStrom:静态功耗和动态功耗分析的很不错的工具,与s 的Power Complier相同。8、SingnalStrom:时序分析工具,唯一一个能建库的工具9、nanoroute : 很强大的布线器喔,但是不是一般人能用的到的。我也是在cadence实习的时候爽过的,比astro快十倍不止。 (三)custom IC Design 1、Virtoso:版图编辑工具,没有人不知道吧,太常用了,现在还有一个公司的laker 2、diva, dracula, assura: 物理验证工具,用的比较普遍,但是calibre是标准,很多公司都是用其中的一个和calibre同时验证,我好可怜,现在只能用herculus (四)数模混合信号设计这部分太多了,但是一个ADE的环境基本上都能包括,不细说了,打字都打累了(五)PCB A llego最为典型了,很多大公司都用的。 系统分类: 软件开发 | 用户分类: IC设计 | 来源: 原创 | 【推荐给朋 友】 | 【添加到收藏夹】 Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面有着绝对的优势。Cadence 包含的工具较多几乎包括了EDA 设计的方方面面。下面主要介绍其产品线的范围。 1、板级电路设计系统。 包括原理图输入、生成、模拟数字/混合电路仿真,fpga设计,pcb编辑和自动布局布线mcm电路设计、高速pcb版图的设计仿真等等。包括: A、Concept HDL原理图设计输入工具, 有for NT和for Unix的产品。 Hspice语法手册 天津大学电信学院 陈力颖 Preface 最初写作本文的目的是希望提供一份中文版的Hspice手册从而方便初学者的使用,本文的缘起是几位曾经一起工作过的同事分别进入不同的新公司,而公司主要是使用Hspice,对于已经熟悉了Cadence的GUI界面的使用者转而面对Hspice的文本格式,其难度是不言而喻的,而Hspice冗长的manual(长达2000页以上)更让人在短时间内理不出头绪。鉴于我曾经使用过相当一段时间的Hspice,于是我向他们提供了一份简单而明了的handbook来帮助他们学习,本来是准备借助一个具体运放的设计例子,逐步完善成为一份case by case的教程,但由于工作比较浩大,加之时间的关系,一直难以完成,愈拖愈久,在几个朋友的劝说下,与其等其日臻完善后再发布,不如先行发布在逐步完善,以便可以让更多的朋友及早使用收益。本文虽通过网络发表,但作者保留全部的著作权,转载时务请通知本人。由于水平的有限,讨论范围的局限及错误不可避免,恳请读者指正。联系方式为e-mail: nkchenliy@https://www.360docs.net/doc/aa6889951.html,。 目录 一、HSPICE基础知识 (2) 二、有源器件和分析类型 (3) 三、输出格式和子电路 (4) 四、控制语句和OPTION语句 (6) 五、仿真控制和收敛 (7) 六、输入语句 (8) 七、统计分析仿真 (9) 天津大学电信学院 陈力颖 2006年2月 一、HSPICE基础知识 Avant! Start-Hspice(现在属于Synopsys公司)是IC设计中最常使用的电路仿真工 具,是目前业界使用最为广泛的IC设计工具,甚至可以说是事实上的标准。目前,一 般书籍都采用Level 2的MOS Model进行计算和估算,与Foundry经常提供的Level 49 和Mos 9、EKV等Library不同,而以上Model要比Level 2的Model复杂的多,因此 Designer除利用Level 2的Model进行电路的估算以外,还一定要使用电路仿真软件 Hspice、Spectre等进行仿真,以便得到精确的结果。 本文将从最基本的设计和使用开始,逐步带领读者熟悉Hspice的使用,以便建立 IC设计的基本概念。文章还将对Hspice的收敛性做深入细致的讨论。 Hspice输入网表文件为.sp文件,模型和库文件为.inc和.lib,Hspice输出文件有运 行状态文件.st0、输出列表文件.lis、瞬态分析文件.tr#、直流分析文件.sw#、交流分析 文件.ac#、测量输出文件.m*#等。其中,所有的分析数据文件均可作为AvanWaves的 输入文件用来显示波形。 表1 Hspice所使用的单位 单位缩写含义 F(f) 1e-15 P(p) 1e-12 N(n) 1e-10 U(u) 1e-06 M(m) 1e-03 K(k) 1e+03 Meg(meg) 1e+06 G(g) 1e+09 T(t) 1e+12 DB(db) 20log10 注:Hspice单位不区分大小写 独立电压和电流源包括: 1. 直流源(DC): 电路原理图设计及Hspice仿真 实验报告 学生姓名: 学号: 指导老师: 实验内容: 用EDP原理图设计软件设计出两级运算放大器的电路图 用Hspice软件完成此两级运算放大器的仿真 实验地点:***实验室 实验时间:2009年9月——2009年12月 实验任务: 根据运算放大器的设计要求(单位增益带宽、相位裕量、输入等效噪声、功耗等),选择电路结构,详细分析了CMOS 运算放大器的所有性能参数,使用Level one 模型进行手工计算,设计出器件的几何尺寸,最后通过Hspice 仿真软件给出了性能指标的仿真结果。 实验思路: 两级运放可以同时实现较高增益和较大输出摆幅,其设计思路是将增益和摆幅要求分别处理,而不是在同一级中兼顾增益与摆幅。即运用第一级放大器得到高增益,可以牺牲摆幅,第二级放大器主要实现大输出摆幅,以补偿第一级牺牲的摆幅,并进一步提升增益,从而克服了单级运放增益与摆幅之间的矛盾,同时实现高增益和大摆幅。 实验指标: 开环增益≥80DB; 共模抑制比≥60DB; 相位裕度≥60°; 实验步骤: 一、用EDP原理图设计软件设计两级运算放大器的电路图,电路图如图一所示: 图一:CMOS两级运算放大器电路图 1、电路工作原理: 信号由差分对管两端输入,差模电压被转化为差模电流,差模电流作用在电流镜负载上又转化成差模电压,信号电压被第一次放大后被转化为单端输出,随即进入共源级再一次被放大后从漏端输出。电路特点是通过两级结构可以同时满足增益和输出摆幅的要求,即第一级提供高增益,可以牺牲摆幅,第二级弥补摆幅,同时进一步增大增益。 2、电路主体结构 由两个两个单级放大器构成,分别是:差分输入级和共源增益级。辅助电路为偏置电路和频率补偿电路。差分输入级采用PMOS 输入对管,NMOS 电流镜负载;共源级采用NMOS 放大管,PMOS 负载管;由六个MOS 管和一个电阻构成的电流源为两级放大电路提供偏置,另外还为频率补偿MOS 管提供偏压;一个NMOS 管和一个电容构成频率补偿电路,连接在共源级的输入输出之间作为密勒补偿。图一中分别命名为M1到M13。 HSPICE介绍 1、为什么要使用Hspice进行电路仿真 Avant! Star_Hspice(Synopsys公司)是IC设计中最长用的仿真工具,是目前业界使用最为广泛的IC设计工具,甚至可以说是事实上的标准。目前,一般的书籍中都采用比较简单的MODEL对MOS 电路进行计算和估算。而工艺厂商提供的MODEL往往要高级的多、复杂的多。因此设计者除了利用书本上的公式对电路进行估算外,还需要使用更高级的MODEL对电路进行精确的仿真,这就有赖于仿真工具的使用,如Hspice,Spectre。 2、Hspice仿真的流程 3、Hspice所使用的单位(不区分大小写) 4、输入文件格式(.net /.sp) 5、电路元器件在Hspice文件中的表示方法 在器件名字前面加上前缀字符,即可被Hspice程序识别,如:MOS器件前缀为:M BJT器件前缀为:Q Diode器件前缀为:D 子电路的前缀为:X 电阻、电容、电感的前缀分别为R、C、L 下面表示一个器件名为M1的MOS管 MM1 ND NG NS NB MNAME L=VAL W=VAL M=VAL 下面表示一个器件名为C1的电容 CC1 net1 net2 1pf 定义子电路的语句如下: .SUBCKT SUBNAM(子电路的名字) 1 2 3 4(子电路外部节点)例子: .SUBCKT 2NAND 1 2 3 (描述电路结构) .ENDS 2NAND 调用子电路时,使用X前缀加实例名,将SUBCKT实例化,如: .XOPAMP1 4 5 6 OPAMP 6、信号源描述(激励描述): 电压源-V,电流源-I Vxxx/Ixxx n+ n- < 电路模拟实验专题 实验文档 一、简介 Simulation Program With Integrated Circuit)仿真模拟,SPICE(本实验专题基于讲授电路模拟的方法和spice仿真工具的使用。 SPICE仿真器有很多版本,比如商用的PSPICE、HSPICE、SPECTRE、ELDO,免费版本的WinSPICE,Spice OPUS等等,其中HSPICE和SPECTRE功能更为强大,在集成电路设计中使用得更为广泛。因此本实验专题以HSPICE和SPECTRE作为主要的仿真工具,进行电路模拟方法和技巧的训练。 参加本实验专题的人员应具备集成电路设计基础、器件模型等相关知识。 二、Spice基本知识(2) 无论哪种spice仿真器,使用的spice语法或语句是一致的或相似的,差别只是在于形式上的不同而已,基本的原理和框架是一致的。因此这里简单介绍一下spice的基本框架,详细的spice 语法可参照相关的spice教材或相应仿真器的说明文档。 首先看一个简单的例子,采用spice模拟MOS管的输出特性,对一个NMOS管进行输入输出特性直流扫描。V从1V变化到3V,步长为0.5V;V从0V变化到5V,步长为DSGS0.2V;输出以V为参量、I与V之间关系波形图。DSGSD *Output Characteristics for NMOS M1 2 1 0 0 MNMOS w=5u l=1.0u VGS 1 0 1.0 VDS 2 0 5 .op .dc vds 0 5 .2 Vgs 1 3 0.5 .plot dc -I(vds) .probe *model .MODEL MNMOS NMOS VTO=0.7 KP=110U +LAMBDA=0.04 GAMMA=0.4 PHI=0.7 .end 描述的仿真电路如下图, 图2-1 MOS管输入输入特性仿真电路图 得到的仿真波形图如下图。 程序中可以知道spice电路描述的主要组成部分。从这个简单的spice 标题和电路结束语句(1)在输入的电路描述语句中输入的第一条语句必须是标题语句,最后一条必须是结束语句。在本例中, ←标题*Output Characteristics for NMOS ……. ……结束语句←.end 2电路描述语句)(器件模型等描述,另激励源、电路描述语句描述电路的组成和连接关系,包括元器件、外,如果电路是层次化的,即包含子电路,电路描述部分还包括子电路描述(。).subckt元器采用不同的关键字作为元件名的第一个字母,要根据类型,在描述元器件时,NMOS件关键字见下表。如本例中,管的描述为:M1 2 1 0 0 MNMOS w=5u l=1.0u 表示的意思为: 元器件关键字x D G S B 模型名宽=xx 长=xx 其中D:漏结点;G:栅结点;S:源结点;B:衬底结点。 Candence使用手册_仿真分册 前言PCB仿真 Cadence软件是我们公司统一使用的原理图设计、PCB设计、高速仿真的EDA工具。进行仿真工作需要有很多方面的知识,须对高速设计的理论有较全面的认识,并对具体的单板原理有一定的了解,还需具备仿真库的相关知识等。 在这个分册中仅对仿真软件的使用进行较详细的阐述,还介绍高速设计的一些相关理论,仿真过程是基于Allegro SPB 15.7的PCB SI模块进行的。 其他知识,如仿真库的知识、约束管理器等请参阅专门的使用手册。 在此非常感谢网络南研 EDA和本部 EDA对此手册的支持。 第一章高速设计与PCB仿真流程本章介绍高速PCB仿真设计的基础知识和重要意义,并介绍基于Cadence 的Allegro SPB15.7的PCB仿真流程。 1.1高速信号与高速设计 随着通信系统中逻辑及系统时钟频率的迅速提高和信号边沿不断变陡,PCB的走线和板层特性对系统电气性能的影响也越发显著。对于低频设计,走线和板层的影响要求不高甚至可以完全忽略不计。当频率超过 50MHz时,PCB走线则必须以传输线考虑,而在评定系统性能时也必须考虑 PCB 板材的电参数影响。当系统时钟频率达到120MHz及更高时,就只能使用高速电路设计方法,否则基于传统方法设计的PCB将无法工作。因此,高速电路设计技术已经成为电子系统设计师必须采取的设计手段,只有通过使用高速电路设计师的设计技术,才能实现设计过程的可控性。高速系统的设计必须面对互连延迟引起的时序问题以及串扰、传输线效应等信号完整性问题。 通常认为如果数字逻辑电路的频率达到或者超过45MHZ~50MHZ,而且工作在这个频率之上的电路占整个电子系统的一定份量(比如说1/3),就称为高速电路。 实际上,信号边沿的谐波频率比信号本身的频率高,是信号快速变化的上升沿与下降沿(或称信号的跳变)引发了信号传输的非预期结果。因此,通常约定如果线传播延时大于1/2数字信号驱动端的上升时间,则认为此类信号是高速信号并产生传输线效应,见图1-1所示。 信号的传递发生在信号状态改变的瞬间,如上升或下降时间。信号从驱动端到接收端经过一段固定的延迟时间,如果传输延迟时间小于1/2的上升或下降时间,那么来自接收端的反射信号将在信号改变状态之前到达驱动端。反之,反射信号将在信号改变状态之后到达驱动端,如果反射信号很强,叠加的波形就有可能会改变逻辑状态。 1.Allegro PCB Design CIS Allegro PCB Design CIS Allegro Designer Entry CIS集成强大的原理图设计功能,其特点主要是具有快捷的元件信息管理系统(CIS),并具有通用PCB设计入口。扩展的CIS功能可以方便地访问本地元件优选数据库和元件信息。通过减少重新搜索元件信息或重复建库,手动输入元件信息,维护元件数据的时间,从而可以提高生产率。无论是设计全新的模拟,数字,或混合信号电路,还是修改现有电路板的电路原理图,或进行层次结构电路图设计,Allegro Designer Entry CIS 提供电路设计从构思到生产所需的一切。 Allegro Designer Entry CIS是全球应用最多且经过生产验证的原理图输入工具和强大的元件信息管理系统。 优点 1、提供快捷,直观的,具备完备功能的原理图编辑工具 2、通过层次式和变体(基于同一原理图,不同机型导出)设计提高复杂原理图的设计效率 3、具备强大功能的CIS,帮助加速设计进程,降低项目成本 4、原理图提供的自动缩放/搜索/导航功能,结合Allegro PCB Editor之间的交互探测和交互摆放,和集成的 AMS-Simulatuor帮助提供设计的可生产性 5、减少重复搜寻元件信息的时间,接收来自MRP,ERP和PLM的数据和支持关系型数据库使智能选择元件成为可能 6、通过直接访问ActiveParts和ActiveParts门户网站,提供给选择原理图设计所需要的元件和直接获取器件供应商元件数据更大的便利,ActiveParts提供了超过200万份的元器件数据 7、通过FPGA输出/输入双向数据流程自动整合可编程门阵列(FPGA)和可编程逻辑器件(PLD),从而缩短设计时间 功能特色 全功能原理图编辑器 Allegro Designer Entry CIS,带有拼接式和层次式的原理图页面编辑器,它具有快捷、直观的原理图编辑的特点。原理图页面编辑器整合了标准的Windows用户界面,这些功能和特性是为工程师完成设计任务和发布设计设计数据而特别定制的。 1、在一个会话窗中可以查看和编辑多个项目 2、通过互联网访问最新元器件 3、对“What-if”场景使用状态标签 4、在设计中引入了高效率的电子表格式的属性编辑或者是在原理图编辑器中编辑属性和打印定义好的属性 ASIC课程设计MOS 输出级电路设计与Hspice仿真 目录 一.背景介绍................................... 错误!未定义书签。二.设计要求与任务................................ 错误!未定义书签。三.电路原理及设计方法............................ 错误!未定义书签。1.电阻负载共源级放大器电路原理分析..............错误!未定义书签。2.有源负载共源放大器设计方法....................错误!未定义书签。四.HSpice软件环境概述............................ 错误!未定义书签。1.简介 .........................................错误!未定义书签。2.特点 .........................................错误!未定义书签。3.界面预览 .....................................错误!未定义书签。五.设计过程...................................... 错误!未定义书签。六.结果和讨论.................................... 错误!未定义书签。七.设计心得...................................... 错误!未定义书签。八.库文件程序附录................................ 错误!未定义书签。hspice仿真整理

TSPC锁存器的设计与HSPICE仿真

Hspice 简明手册

Cadence仿真简介

(完整版)HSPICE与CADENCE仿真规范与实例..

CADENCE工具VIRTUSO-DRACULA入门介绍

cadence仿真流程

Hspice(中文实用版)

TSPC锁存器的设计与HSPICE仿真设计

cadence工具介绍

hspice语法手册

电路原理图设计及Hspice仿真

CMOS实验课1HSPICE介绍

完整版HSPICE与CADENCE仿真规范与实例

candence使用手册仿真分册实用手册

cadence软件介绍

ASIC课程设计MOS输出级电路设计与Hspice仿真