AMBA_AXI总线详解

AXI总线协议资料整理

第一部分:

1、AXI简介:AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。它的地址/控制和数据相位是分离的,支持不对齐的数据传输,同时在突发传输中,只需要首地址,同时分离的读写数据通道、并支持显著传输访问和乱序访问,并更加容易就行时序收敛。AXI 是AMBA 中一个新的高性能协议。AXI 技术丰富了现有的AMBA 标准内容,满足超高性能和复杂的片上系统(SoC)设计的需求。

2、AXI 特点:单向通道体系结构。信息流只以单方向传输,简化时钟域间的桥接,减少门数量。当信号经过复杂的片上系统时,减少延时。

支持多项数据交换。通过并行执行猝发操作,极大地提高了数据吞吐能力,可在更短的时间内完成任务,在满足高性能要求的同时,又减少了功耗。

独立的地址和数据通道。地址和数据通道分开,能对每一个通道进行单独优化,可以根据需要控制时序通道,将时钟频率提到最高,并将延时降到最低。第二部分:

本部分对AXI1.0协议的各章进行整理。

第一章

本章主要介绍AXI协议和AXI协议定义的基础事务。

1、AXI总线共有5个通道分别是read address channel

、write address channel 、read data channel 、write data channel、write response channel。每一个AXI传输通道都是单方向的。

2、每一个事务都有地址和控制信息在地址通道(address channel)中,用来描述被传输数据的性质。

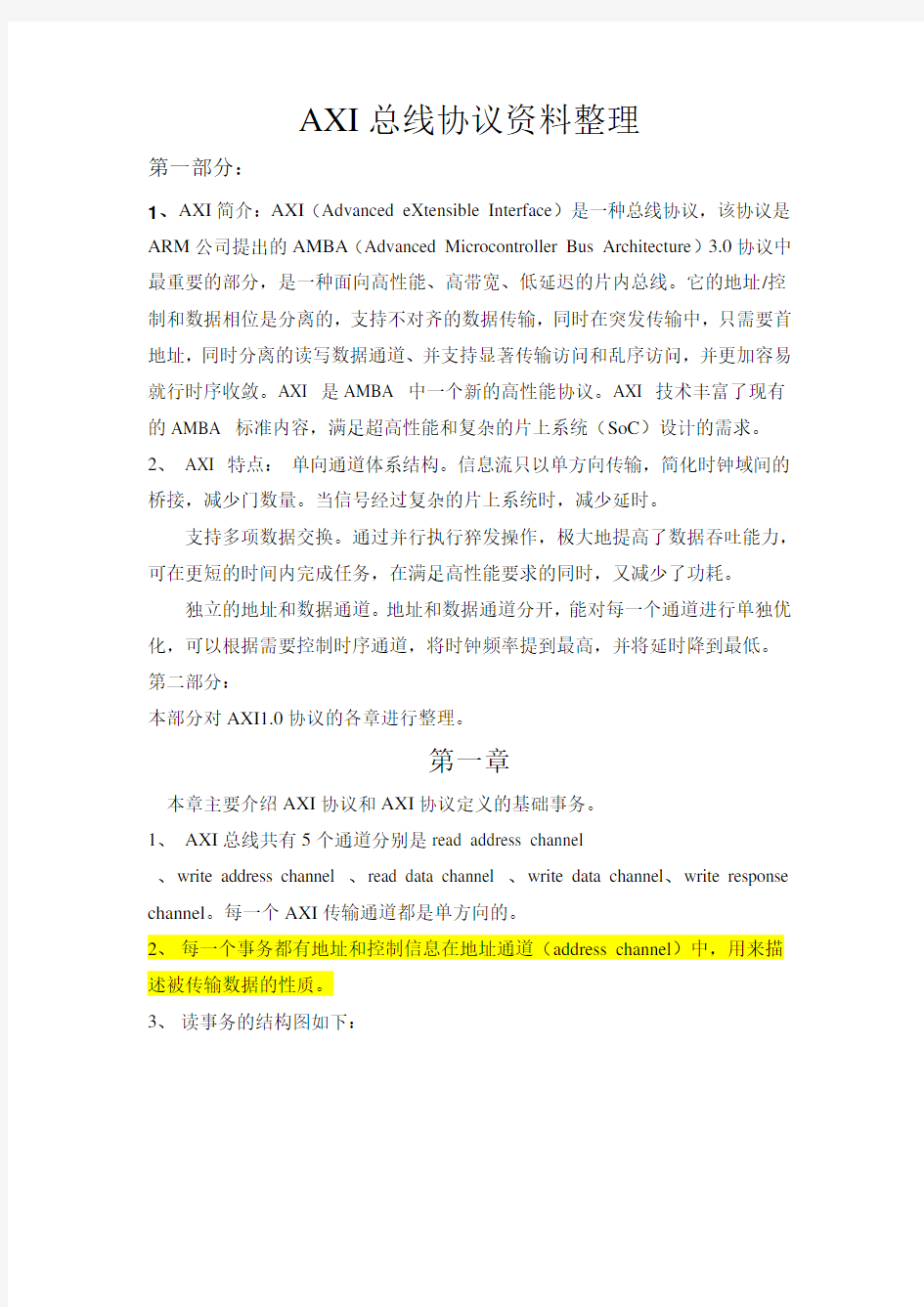

3、读事务的结构图如下:

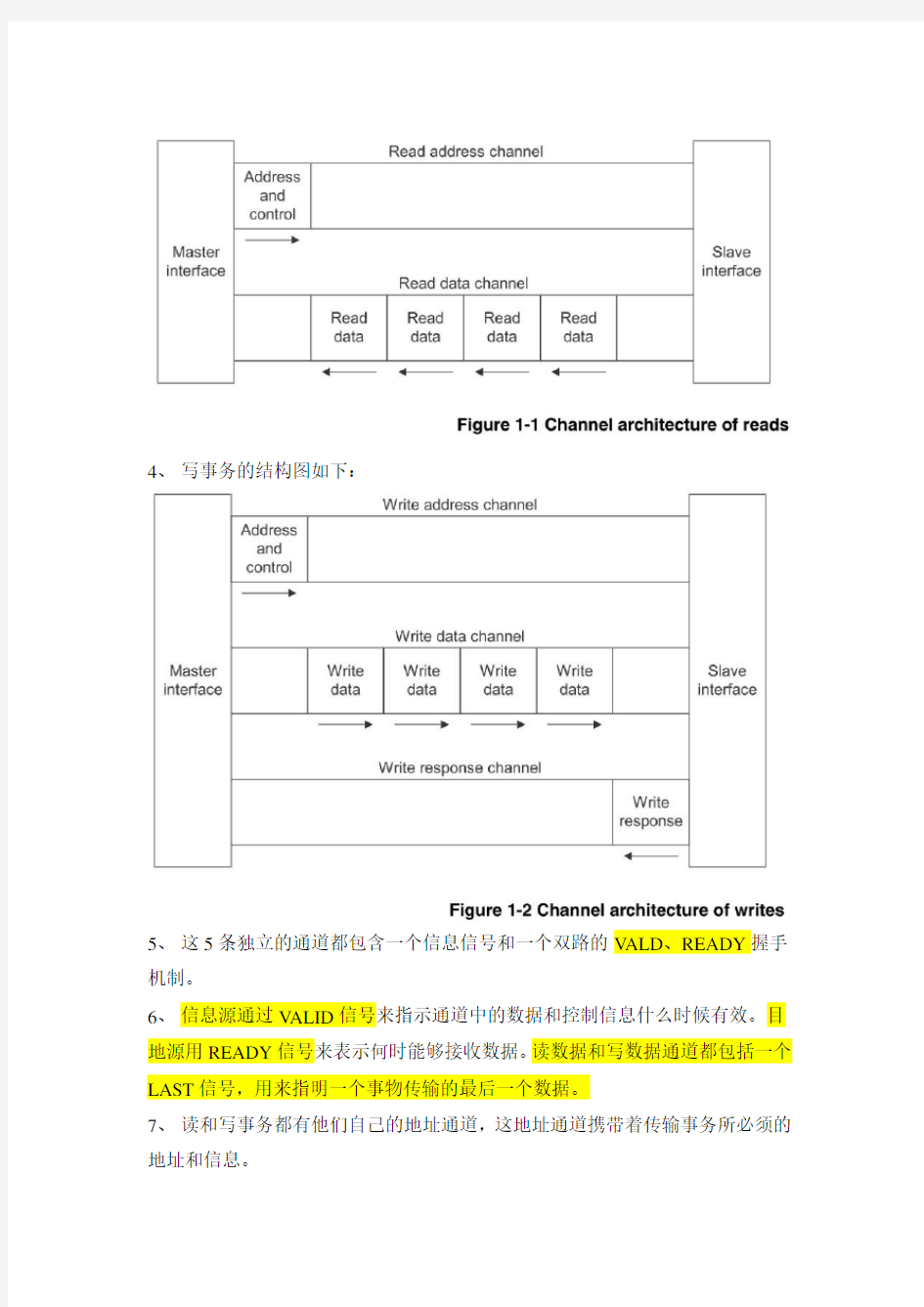

4、写事务的结构图如下:

5、这5条独立的通道都包含一个信息信号和一个双路的V ALD、READY握手机制。

6、信息源通过V ALID信号来指示通道中的数据和控制信息什么时候有效。目地源用READY信号来表示何时能够接收数据。读数据和写数据通道都包括一个LAST信号,用来指明一个事物传输的最后一个数据。

7、读和写事务都有他们自己的地址通道,这地址通道携带着传输事务所必须的地址和信息。

8、读数据通道传送着从设备到主机的读数据和读响应信息。读响应信息指明读事务的完成状态。

9、写数据通路传送着主机向设备的写数据。每八个数据都会有一个byte lane ,用来指明数据总线上面的哪些byte有效。写响应通道提供了设备响应写事务的一种方式。这完成信号每一次突发式读写会产生一个。

10、主机和设备的接口和互联图如下:

11、传输地址信息和数据都是在V ALID和READY同时为高时有效。

12、突发式读的时序图如下:

当地址出现在地址总线后,传输的数据将出现在读数据通道上。设备保持V ALID 为低直到读数据有效。为了表明一次突发式读写的完成,设备用RLAST信号来表示最后一个被传输的数据。

13、重叠突发式读时序图如下:

设备会在第一次突发式读完成后处理第二次突发式读数据。也就意味着,主机一开始传送了两个地址给设备。设备在完全处理完第一个地址的数据之后才开始处理第二个地址的数据。

14、突发式写时序图如下:

这一过程的开始时,主机发送地址和控制信息到写地址通道中,然后主机发送每一个写数据到写数据通道中。当主机发送最后一个数据时,WLAST信号就变为高。当设备接收完所有数据之后他将一个写响应发送回主机来表明写事务完成。

15、AXI协议支持乱序传输。他给每一个通过接口的事务一个IDtag。协议要求相同ID tag的事务必须有序完成,而不同ID tag可以乱序完成。

第二章

本章主要介绍一些信号描述,其中包括全局信号、写地址通道信号、写数据通道信号、写响应通道信号、读地址通道信号、读数据通道信号、低功耗接口信号。本章的所有表都是以32位的数据总线、4位的写数据闸门、4位的ID段。

1、全局信号

信号源描述

ACLK Clock source 全局时钟信号

ARESETn Reset source 全局复位信号,低电平有效

2、写地址通道信号

信号源描述

AWID[3:0] 主机写地址ID,这个信号是写地址信号组的ID tag。AWADDR[31:0] 主机写地址。

AWLEN[3:0] 主机突发式写的长度。此长度决定突发式写所传输的数据的

个数。

AWSIZE[2:0] 主机突发式写的大小。

AWBURST[1:0] 主机突发式写的类型。

AWLOCK[1:0] 主机锁类型。

AWCACHE[3:0] 主机Cache类型。这信号指明事务的bufferable、cacheable、

write-through、write-back、allocate attributes信息。AWPROT[2:0] 主机保护类型。

AWV ALID 主机写地址有效。

1 = 地址和控制信息有效

0 = 地址和控制信息无效

这个信号会一直保持,直到AWREADY变为高。AWREADY 设备写地址准备好。这个信号用来指明设备已经准备好接受

地址和控制信息了。

1 = 设备准备好

0 = 设备没准备好

3、写数据通道信号

信号源描述

WID[3:0] 主机写ID tag,WID的值必须与AWID的值匹配

WDATA[31:0] 主机写的数据。

WSTRB[3:0] 主机写阀门。WSTRB[n]标示的区间为WDATA[(8*n)+7:(8*n)]

WLAST 主机写的最后一个数据。

WV ALID 主机写有效

1 = 写数据和阀门有效

0 = 写数据和阀门无效

WREADY 设备写就绪。指明设备已经准备好接受数据了

1 = 设备就绪

0 = 设备未就绪

4、写响应通道信号

信号源描述

BID[3:0] 设备响应ID ,这个数值必须与AWID的数值匹配。BRESP[1:0] 设备写响应。这个信号指明写事务的状态。可能有的响应:

OKAY、EXOKAY、SLVERR、DECERR。

BV ALID 设备写响应有效。

1 = 写响应有效

0 = 写响应无效

BREADY 主机接受响应就绪。该信号表示主机已经能够接受响应信息。

1 = 主机就绪

0 = 主机未就绪

5、读地址通道信号

信号源描述

ARID[3:0] 主机读地址ID。

ARADDR[31:0] 主机读地址。

ARLEN[3:0] 主机突发式读长度。

ARSIZE[2:0] 主机突发式读大小。

ARBURST[1:0] 主机突发式读类型。

ARLOCK[1:0] 主机锁类型。

ARCACHE[3:0] 主机Cache类型。

ARPROT[2:0] 主机保护类型。

ARV ALID 主机读地址有效。信号一直保持,直到ARREADY为高。

1 = 地址和控制信息有效

0 = 地址和控制信息无效

ARREADY 设备读地址就绪。指明设备已经准备好接受数据了。

1 = 设备就绪

0 = 设备未就绪

6、读数据通道信号

信号源描述

RID[3:0] 设备读ID tag。RID的数值必须与ARID的数值匹配。RDATA[31:0] 设备读数据。

RRESP[1:0] 设备读响应。这个信号指明读传输的状态:OKAY、

EXOKAY、SLVERR、DECERR。

RLAST 设备读事务传送的最后一个数据。

RV ALID 设备读数据有效。

1 = 读数据有效。

0 = 读数据无效。

RREADY 主机读数据就绪。

1 = 主机就绪

0 = 主机未就绪

7、低功耗接口信号

信号源描述

CSYSREQ CLOCK controller 系统低功耗请求。此信号来自系统时钟控制

器,使外围设备进入低功耗状态。CSYSACK 外围设备低功耗请求应答。

CACTIVE 外围设备Clock active

1 = 外围设备时钟请求

0 = 外围设备时钟无请求

第三章

本章介绍主机/设备之间的握手过程以及READY和V ALD握手信号的关系以及默认值。

1、全部5个通道使用相同的V ALID/READY握手机制传输数据及控制信息。传输源产生VLAID信号来指明何时数据或控制信息有效。而目地源产生READY 信号来指明已经准备好接受数据或控制信息。传输发生在V ALID和READY信号同时为高的时候。V ALID和READY信号的出现有三种关系。

(1)V ALID先变高READY后变高。时序图如下:

在箭头处信息传输发生。

(2)READY先变高V ALID后变高。时序图如下:

同样在箭头处信息传输发生。

(3)V ALID和READY信号同时变高。时序图如下:

在这种情况下,信息传输立马发生,如图箭头处指明信息传输发生。

2、通道之间的关系

地址、读、写和写响应通道之间的关系是灵活的。

例如,写数据可以出现在接口上早于与其相关联的写地址。也有可能写数据与写地址在一个周期中出现。

两种关系必须被保持:

(1)读数据必须总是跟在与其数据相关联的地址之后。

(2)写响应必须总是跟在与其相关联的写事务的最后出现。

3、通道握手信号之间的依赖性

读事务握手依赖关系如图:

(1)设备可以在ARV ALID出现的时候在给出ARREADY信号,也可以先给出ARREADY信号,再等待ARV ALID信号。

(2)但是设备必须等待ARV ALID和ARREADY信号都有效才能给出RV ALID 信号,开始数据传输。

写事务握手依赖关系如图:

(1)主机必须不能够等待设备先给出AWREADY或WREADY信号信号后再给出信号AWV ALID或WVLAID。

(2)设备可以等待信号AWV ALID或WV ALID信号有效或者两个都有效之后再给出AWREADY信号。

(3)设备可以等待AWV ALID或WV ALID信号有效或者两个信号都有效之后再给出WREADY信号。

第四章

本章主要介绍AXI突发式读写的类型和在一次突发式读写事务内如何计算地址和byte lanes。

1、突发式读写的地址必须以4KB对齐。

2、信号AWLEN或信号ARLEN指定每一次突发式读写所传输的数据的个数。具体信息如下图:

3、ARSIZE信号或AWSIZE信号指定每一个时钟节拍所传输的数据的最大位数。

具体信息如下图:

需要注意的是任何传输的SIZE都不能超过数据总线的宽度。

4、AXI协议定义了三种突发式读写的类型:固定式的突发读写、增值式突发读写、包装式突发读写。用信号ARBURST或AWBURST来选择突发式读写的类

型。具体信息如下图:

(1)固定式突发读写是指地址是固定的,每一次传输的地址都不变。这样的突发式读写是重复的对一个相同的位置进行存取。例如FIFO。

(2)增值式突发读写是指每一次读写的地址都比上一次的地址增加一个固定的

值。

(3)包装式突发读写跟增值式突发读写类似。包装式突发读写的地址是包数据

的低地址当到达一个包边界。

包装式突发读写有两个限制:

◇1起始地址必须以传输的size对齐。

◇2突发式读写的长度必须是2、4、8或者16。

5、关于一些地址的计算公式。

Start_Address 主机发送的起始地址

Number_Bytes 每一次数据传输所能传输的数据byte的最大数量

Data_Bus_Bytes 数据总线上面byte lanes的数量

Aligned_Address 对齐版本的起始地址

Burst_Length 一次突发式读写所传输的数据的个数

Address_N 每一次突发式读写所传输的地址数量,范围是2-16

Wrap_Boundary 包装式突发读写的最低地址

Lower_Byte_Lane 传输的最低地址的byte lane

Upper_Byte_Lane 传输的最高地址的byte lane

INT(x) 对x进行向下取整

下面是计算公式:

Start_Address = ADDR

Number_Bytes = 2SIZE

Burst_Length = LEN + 1

Aligned_Address = (INT(Start_Address / Number_Bytes) ) x Number_Bytes Address_1 = Start_Address

Address_N = Aligned_Address + (N –1) x Number_Bytes

Wrap_Boundary = (INT(Start_Address / (Number_Bytes x Burst_Length)))

x (Number_Bytes x Burst_Length)

如果有Address_N = Wrap_Boundary + (Number_Bytes x Burst_Length),则后面的公式成立Address_N = Wrap_Boundary。

第一次突发式读写:

Lower_Byte_Lane = Start_Address - (INT(Start_Address / Data_Bus_Bytes))

x Data_Bus_Bytes

Upper_Byte_Lane = Aligned_Address + (Number_Bytes - 1) -

(INT(Start_Address / Data_Bus_Bytes)) x Data_Bus_Bytes

除了第一次读写之后的读写:

Lower_Byte_Lane = Address_N –(INT(Address_N / Data_Bus_Bytes))

x Data_Bus_Bytes

Upper_Byte_Lane = Lower_Byte_Lane + Number_Bytes –1

DATA[(8 x Upper_Byte_Lane) + 7 : (8 x Lower_Byte_Lane)]。

第五章

本章描述了AXI协议支持的系统级的Cache和保护单元。

1、ARCACHE[3:0]和AWCACHE[3:0]的编码如下图:

在一些情况下,信号AWACAHE可以用来确定哪个部件来提供写响应。如果写事务被指定为bufferable ,那么他接受来自桥或者系统级的cache提供的写响

应。如果事务被指定为non-bufferable,那么写响应必须有最终目的源提供。2、AWPROT或者ARPROT信号提供三种级别的存取保护:

(1)正常存取或者特权存取,ARPROT[0] 和AWPROT[0]

(2)安全性存取或者没有安全性存取,ARPROT[1] 和AWPROT[1]

(3)指令存取或者数据存取ARPROT[2] 和AWPROT[2]

信号ARPROT[2:0] 和信号AWPROT[2:0]的编码如下图:

第六章

本章描述了AXI协议工具的独占式存取和锁存取机制。

1、当对自动存取时能之后,可以通过信号ARLOCK[1:0]或信号AWLOCK[1:0]来配置独占式存取和锁存取。编码如下图:

我们通过信号ARLOCK[1:0]或AWLOCK[1:0]来选择独占式存取,用信号RRESP[1:0]或BRESP[1:0]来指明独占式存取的成功与否。

2、主机在请求独占式存取时,设备会返回两个响应分别是EXOKAY和OKAY。EXOKAY是指设备支持独占式存取,而OKAY是指设备不支持独占式存取。、

3、如果一个设备不支持独占式存取,可以忽略信号ARLOCK[1:0]和

AWLOCK[1:0]。他必须提供OKAY响应对正常式存取和独占式存取。如果一个设备要支持独占式存取则必须有硬件监视器。

4、通过信号ARLOCK[1:0]或信号AWLOCK[1:0]对事务加锁,需要确定只允许主机存取设备区域直到一个未加锁的事务从同一个主机完成。此处推荐锁存取只用来支持legacy devices。

5、推荐遵循下面两条建议,但是不强制:

(1)保持所有锁事务序列都在相同的4KB地址区域内。

(2)限制用琐事务序列对两个事务加锁。

第七章

本章描述了AXI读写事务的四个设备响应。

1、AXI协议对读事务和写事务都有响应。对于读事务,读响应与读数据一起发送给主机,而写事务将写响应通过写响应通道传送。AXI协议的响应类型有OKAY、EXOKAY、SLVERR、DECERR。

2、通过信号RRESP[1:0]和BRESP[1:0]来编码响应信号,具体如下图:

协议规定请求的需要传输的数据数量必须被执行,即使有错误报告。在一次突发式读写的剩余数据不会被取消传输,即使有单个错误报告。

3、AXI协议的四种响应类型:正常存取成功、独占式存取、设备错误、译码错误。AXI协议要求,在一个传输事务中的所有数据必须传输完成,即使有错误状态发生。

第八章

本章描述AXI协议用事务ID tags来处理多地址和乱序传输。

1、下面介绍5中事务IDs:

(1)AWID 这个ID tag是写地址群组信号。

(2)WID 这个是写ID tag在写事务中,与写数据在一起,主机传送一个WID去匹配与地址相一致的AWID。

(3)BID 这个ID tag是写响应事务中。设备会传送BID去匹配与AWID 和WID相一致的事务。

(4)ARID 这个ID tag是读地址群组信号。

(5)RID 这个ID tag是在读事务中。设备传送RID去匹配与ARID相一致的事务。

2、主机可以使用一个事务的ARID或者AWID段提供的附加信息排序主机的需要。事务序列规则如下:

(1)从不同主机传输的事务没有先后顺序限制。他们可以以任意顺序完成。(2)从同一个主机传输的不同ID事务,也没有先后顺序限制。他们可以以任

意顺序完成。

(3)相同数值的AWID写事务数据序列必须按照顺序依次写入主机发送的地

址内。

(4)相同数值的ARID读事务数据序列必须遵循下面的顺序:

◇1当从相同设备读相同的ARID时,设备必须确保读数据按照相同的地址顺序接受。

◇2当从不同的设备读相同的ARID时,接口处必须确保读数据按照主机发送的相同的地址顺序。

(5)在相同的AWID和ARID的读事务和写事务之间没有先后顺序限制。如果主机要求有顺序限制,那么必须确保第一次事务完全完成后才开始执行第二个事务。

3、当一个主机接口与interconnect相连时,interconnect会在信号ARID、AWID、WID段添加一位,每一个主机端口都是独一无二的。

这样做有两个影响:

(1)主机不需要去知道其他主机的ID数值,因为interconnect是ID值是唯一的,当将主机number添加到段中。

(2)在设备接口处的ID段的宽度要比主机接口处的ID段宽。

对于读数据,interconnect附加一位到RID段中,用来判断哪个主机端口读取数据。Interconnect会移除RID段中的这一位在将RID的值送往正确的主机端口之前。

第九章

本章描述了AXI读写数据总线传输的不同大小和接口如何用字节不变endian去握手混合endian传输。

1、Narrow传输,当主机产生的数据宽度小于数据总线宽度时,地址和控制信息决定哪一个byte lanes为有效的数据。下面是两个应用byte lanes的例子:

Example 1:

Example 2:

2、下面是一个数据不变性存取需求的数据结构的例子。他包含头信息,例如source、destination identifiers这些信息是采用little-endian格式,但是payload是big-endian 字节流,具体情况如下图:

can总线协议完全解析

CAN总线协议解析 李玉丽 (吉林建筑工程学院电气与电子信息工程学院,吉林长春,130021 ) 摘要:现场总线的发展与应用引起了传统控制系统结构的改变。控制局域网(C AN)总线因其自身的特点被广泛应用于 自动控制领域。本文对C AN总线协议作了详尽解析。 关键词:C AN总线;隐性位;显性位;节点 中图分类号:T U 85 文献标识码:A CAN(Cont roll e r A rea N et work)是分布式实时控 制系统的串行通信局域网,称谓CAN总线。在数据 实时传输中,设计独特、低成本,具有高可靠性,得到 广泛应用。 本文着重解析C AN 技术规范2.0B 版的CAN 的分层结构规范和CAN 报文结构规范。重点在于 充分理解CAN总线协议精髓,有助于CAN总线的 局网设计、软件编程、局网维护。 一、C AN的分层结构 CAN 遵从O SI ( Ope n Syste m I nte rc onnec ti on Re fe re nce Mode l ) 模型,其分层结构由高到低如图1 所示。 图1 C AN的分层结构 对应OSI 模型为两层,实际为三层,即LLC、 MA C、PL S。由此而知,对应于CAN总线系统每个 节点都是三层结构。数据发送节点数据流为LLC→ MA C→P LS ,然后将数据发送到总线上;而对于挂在 总线上的所有节点(包括发送节点)的接收的数据流 为PL S→MA C→LLC。 这种分层结构的规范保证了CAN 总线的多主 方式工作模式,即不分主从,非破坏性的仲裁工作模 式。而LLC 层的报文滤波功能可实现点到点、一点 对多点、全局广播、多点对一点,多点对多点等数据 传递方式。 各分层主要功能如下: LLC 层:接收滤波、超载通知、恢复管理; MAC 层:控制帧结构、执行仲裁、错误检测、出 错标定、故障界定。该层是CAN的核心; PL S 层:位编码/ 解码、位定时。 二、CAN总线的报文规范 CAN报文的传送有4 种不同类型的帧结构,数 据帧、远程帧、出错帧、超载帧。CA B2.0B 有4 种帧 格式。 (一)数据帧

AMBAAXI总线详解

AXI 总线协议资料整理 第一部分: 1、AXI 简介:AXI (Adva need eXte nsible In terface 是一种总线协议,该协议是ARM 公司提出的AMBA( Advanced Microcontroller Bus Architecture)3.0 协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。它的地址/控 制和数据相位是分离的,支持不对齐的数据传输,同时在突发传输中,只需要首 地址,同时分离的读写数据通道、并支持显著传输访问和乱序访问,并更加容易就行时序收敛。AXI 是AMBA 中一个新的高性能协议。AXI 技术丰富了现有的AMBA标准内容,满足超高性能和复杂的片上系统(SoC)设计的需求。 2、AXI 特点:单向通道体系结构。信息流只以单方向传输,简化时钟域间的桥接,减少门数量。当信号经过复杂的片上系统时,减少延时。 支持多项数据交换。通过并行执行猝发操作,极大地提高了数据吞吐能力,可在更短的时间内完成任务,在满足高性能要求的同时,又减少了功耗。 独立的地址和数据通道。地址和数据通道分开,能对每一个通道进行单独优化,可以根据需要控制时序通道,将时钟频率提到最高,并将延时降到最低。第二部分: 本部分对AXI1.0 协议的各章进行整理。 第一章 本章主要介绍AXI 协议和AXI 协议定义的基础事务。 1 、AXI 总线共有5 个通道分别是read address channel 、write address channel 、read data channel、write data channe、l write response ehanne。每一个AXI传输通道都是单方向的。 2、每一个事务都有地址和控制信息在地址通道( address channel 中,用来描述被传输数据的性质。 3、读事务的结构图如下:

AI总线中文详解

AXI总线协议资料整理 第一部分: 1、AXI简介:AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。它的地址/控制和数据相位是分离的,支持不对齐的数据传输,同时在突发传输中,只需要首地址,同时分离的读写数据通道、并支持显著传输访问和乱序访问,并更加容易就行时序收敛。AXI 是AMBA 中一个新的高性能协议。AXI 技术丰富了现有的AMBA 标准内容,满足超高性能和复杂的片上系统(SoC)设计的需求。 2、 AXI 特点:单向通道体系结构。信息流只以单方向传输,简化时钟域间的桥接,减少门数量。当信号经过复杂的片上系统时,减少延时。 支持多项数据交换。通过并行执行猝发操作,极大地提高了数据吞吐能力,可在更短的时间内完成任务,在满足高性能要求的同时,又减少了功耗。 独立的地址和数据通道。地址和数据通道分开,能对每一个通道进行单独优化,可以根据需要控制时序通道,将时钟频率提到最高,并将延时降到最低。 第二部分: 本部分对AXI1.0协议的各章进行整理。 第一章 本章主要介绍AXI协议和AXI协议定义的基础事务。 1、 AXI总线共有5个通道分别是read address channel 、 write address channel 、 read data channel 、 write data channel、 write response channel。每一个AXI传输通道都是单方向的。2、每一个事务都有地址和控制信息在地址通道(address channel)中,用来描述被传输数据的性质。 3、读事务的结构图如下:

单片机常用总线讲解

第8章单片机常用总线讲解 8.1 C总线接口 80C51单片机本身不具有总线接口,但是通过软件进行模拟,可以挂接具有C接口的芯片。 8.1.1 C总线的介绍 串行扩展总线在单片机系统中的应用是目前单片机技术发展的一种趋势。在目前比较流行的几种串行扩展总线中,总线以其严格的规范和众多带接口的外围器件而获得广泛应用。总线是PHILIPS公司推出的芯片间串行传输总线,它由两根线组成,一根是串行时钟线(SCL),一根是串行数据线(SDA)。主控器利用串行时钟线发出时钟信号,利用串行数据线发送或接收数据。总线由主控器电路引出,凡具有接口的电路(受控器)都可以挂接在总线上,主控器通过总线对受控器进行控制。 随着总线研究的深入,总线已经广泛应用于视/音频领域、IC卡行业和一些家电产品中,在智能仪器、仪表和工业测控领域也越来越多地得到应用。 8.1.2 总线的特点 总线的广泛应用是同它卓越的性能和简便的操作方法分不开的。总线的特点主要表现在以下几个方面: 硬件结构上具有相同的硬件接口界面。总线系统中,任何一个总线接口的外围器件,不论其功能差别有多大,都是通过串行数据线(SDA)和串行时钟线(SCL)连接到总线上。这一特点给用户在设计用用系统中带来了极大的便利性。用户不必理解每个总线接口器件的功能如何,只需将器件的SDA和SCL引脚连到总线上,然后对该器件模块进行独立的电路设计,从而简化了系统设计的复杂性,提高了系统抗干扰的能力。 线接口器件地址具有根大的独立性。每个接口芯片具有唯一的器件地址,由于不能发出串行时钟信号而只能作为从器件使用。各器件之间互不干扰,相互之间不能进行通信,各个器件可以单独供电。单片机与器件之间的通信是通过独一无二的器件地址来实现的。 软件操作的一致性。由于任何器件通过总线与单片机进行数据传送的方式是基本一样的, .v .. ..

各类总线解析

查漏补缺-总线 以前在找工作的时候,每次笔试总会遇到各种总线协议什么的题目,每次都头大,不是没听到过,而是基本上都是了解但是不清晰的状态,需要查资料、翻书才能搞得清楚的。也没太在意,但是到了实际工作的时候,慢慢地发现它就变成一个疑难杂症了(因为他总是不能被记住,每到要的时候到处找资料),我觉得做技术的东西就是要把是事情做牢靠,把产品做稳定。那些个所谓的高科技、高技术含量的的东西,如果不稳定那就跟垃圾无异。 根据以前碰到的问题,经过查阅资料和一些自己的理解汇总如下,今天特地把他整理出来,大家如果觉得有必要的可以瞅瞅,不过高手就可以飘过了。 微机中总线一般有内部总线、系统总线和外部总线。内部总线是微机内部各外围芯片与处理器之间的总线,用于芯片一级的互连;而系统总线是微机中各插件板与系统板之间的总线,用于插件板一级的互连;外部总线则是微机和外部设备之间的总线,微机作为一种设备,通过该总线和其他设备进行信息与数据交换,它用于设备一级的互连。内部总线有以下几种类型。 1.1IIC总线 I2C串行总线一般有两根信号线,一根是双向的数据线SDA,另一根是时钟线SCL。所有接到I2C总线设备上的串行数据SDA都接到总线的SDA上,各设备的时钟线SCL接到总线的SCL上。 为了避免总线信号的混乱,要求各设备连接到总线的输出端时必须是漏极开路(OD)输出或集电极开路(OC)输出。设备上的串行数据线SDA接口电路应该是双向的,输出电路用于向总线上发送数据,输入电路用于接收总线上的数据。而串行时钟线也应是双向的,作为控制总线数据传送的主机,一方面要通过SCL输出电路发送时钟信号,另一方面还要检测总线上的SCL电平,以决定什么时候发送下一个时钟脉冲电平;作为接受主机命令的从机,要按总线上的SCL 信号发出或接收SDA上的信号,也可以向SCL线发出低电平信号以延长总线时钟信号周期。总线空闲时,因各设备都是开漏输出,上拉电阻Rp使SDA和SCL 线都保持高电平。任一设备输出的低电平都将使相应的总线信号线变低,也就是说:各设备的SDA是“与”关系,SCL也是“与”关系。

I2C总线时序详解

I2C 总线时序详解 I2C总线位传输 由于连接到I2C总线的器件有不同种类的工艺(CMOSNMOS双极性),逻辑0 (低)和逻辑1 (高)的电平不是固定的,它由电源VCC的相关电平决定,每传输一个数据位就产生一个时钟脉冲。 数据的有效性 SDA线上的数据必须在时钟的高电平周期保持稳定。数据线的高或低电平状态只有在SCL线的时钟信号是低电平时才能改变。 I2C位传输数据有效性 起始和停止条件 SCL线是高电平时,SDA线从高电平向低电平切换,这个情况表示起始条件; SCL线是高电平时,SDA线由低电平向高电平切换,这个情况表示停止条件。 起始和停止条件一般由主机产生,总线在起始条件后被认为处于忙的状态 SDA

起始和停止条件 ,在停止条件的某段时间后总线被认为再次处于空闲状态。如果产生重复起始条件而不产生停止条件,总线会一直处于忙的状态,此时的起始条件(S)和重复起始条件(Sr)在功能上是一样的。 I2C总线数据传输 字节格式 发送到SDA线上的每个字节必须为8位,每次传输可以发送的字节数量不受限制。每个字节后必须跟一个响应位。首先传输的是数据的最高位 (MSB,如果从机要完成一些其他功能后(例如一个内部中断服务程序)才能接收或发送下一个完整的数据字节,可以使时钟线SCL保持低电平, 迫使主机进入等待状态,当从机准备好接收下一个数据字节并释放时钟线SCL后数据传输继续。应答响应 数据传输必须带响应,相关的响应时钟脉冲由主机产生。在响应的时钟脉冲期间发送器释放SDA线(高)。 在响应的时钟脉冲期间,接收器必须将SDA线拉低,使它在这个时钟 脉冲的高电平期间保持稳定的低电平。 通常被寻址的接收器在接收到的每个字节后,除了用CBUS地址开头的 数。

CAN总线解析

一、概述 CAN(Controller Area Network)即控制器局域网,是一种能够实现分布式实时控制的串行通信网络。 想到CAN就要想到德国的Bosch公司,因为CAN就是这个公司开发的(和Intel)CAN 有很多优秀的特点,使得它能够被广泛的应用。比如:传输速度最高到1Mbps,通信距离最远到10KM,无损位仲裁机制,多主结构。 近些年来,CAN控制器价格越来越低,很多MCU也集成了CAN控制器。现在每一辆汽车上都装有CAN总线。 一个典型的CAN应用场景: 二、CAN总线标准 CAN总线标准只规定了物理层和数据链路层,需要用户来自定义应用层。不同的CAN标准仅物理层不同。

CAN收发器负责逻辑电平和物理信号之间的转换,将逻辑信号转换成物理信号(差分电平)或者将物理信号转换成逻辑电平。 CAN标准有两个,即IOS11898和IOS11519,两者差分电平特性不同。(有信号时,CANH 3.5V,CANL 1.5V,即显性;没有信号时,CANH 2.5V,CANL 2.5V,即隐性) IOS11898高速CAN电平中,高低电平的幅度低,对应的传输速度快。 双绞线共模消除干扰,是因为电平同时变化,电压差不变。 2.1物理层 CAN有三种接口器件

多个节点连接,只要有一个为低电平,总线就为低电平,只有所有的节点都输出高电平时,才为高电平。所谓“线与”。 CAN总线有5个连续性相同的位后,就会插入一个相反位,产生跳变沿,用于同步。从而消除累计误差。 和485、232一样,CAN的传输速度与距离成反比。 CAN总线终端电阻的接法:

特点:低速CAN在CANH和CANL上串入2.2kΩ的电阻;高速CAN在CANH和CANL 之间并入120Ω电阻。为什么是120Ω,因为电缆的特性阻抗为120Ω,为了模拟无限远的传输线。(因为大多数双绞线电缆特性阻抗大约在100~120Ω。) 120欧姆只是为了保证阻抗完整性,消除回波反射,提升通信可靠性的,因此,其只需要在总线最远的两端接上120欧姆电阻即可,而中间节点并不需要接(接了反而有可能会引起问题)。因此各位在使用CAN Omega做CAN总线侦听的时候,大多数情况下是不需要这个120欧姆电阻的,当然,即使当前网络中并没有终端匹配电阻,只要传输线长度不长(比如SysCan360比赛环境中,传输线只有1-2米)CAN节点数量不多的情况下,不要这个120欧姆电阻也完全可以工作,甚至,你接任意电阻都是不会有影响的。因为此时传输线长度和波长还相差甚远,节点不多的情况下,反射波的叠加信号强度也不会很强,因此传输线效应完全可以忽略。 而哪些情况需要呢,主要就是,当使用2个CAN Omega对发或者当前网络中仅有2个CAN设备的时候,此时两个端点最好都加上终端匹配电阻,当然,前面也说过了,传输线长度不长的时候,也可以不需要2端120欧姆电阻,但为了信号完整性考虑,加上这两个电阻才是严谨的。 2个120欧姆电阻的意义在于,使用USB CAN调试某些不带终端电阻的中间节点设备时,有时候CAN总线上没有2个120欧姆电阻通信可能会异常,此时可以接入2个120欧姆电阻作为2个终端电阻来作阻抗匹配,这时候其他端点不应接入任何终端电阻!并且,这2个120欧姆电阻不可用1个60欧姆电阻代替!

常见九大现场总线全解析

常见九大现场总线全解析 内容来源网络,由“深圳机械展(11万㎡,1100多家展商,超10万观众)”收集整理!更多cnc加工中心、车铣磨钻床、线切割、数控刀具工具、工业机器人、非标自动化、数字化无人工厂、精密测量、3D打印、激光切割、钣金冲压折弯、精密零件加工等展示,就在深圳机械展. 目前国际上有40多种现场总线,但没有任何一种现场总线能覆盖所有的应用面,按其传输数据的大小可分为3类:传感器总线(sensorbus),属于位传输;设备总线(devicebus),属于字节传输;现场总线,属于数据流传输。 什么是现场总线? 现场总线(Fieldbus)是20世纪80年代末、90年代初国际上发展形成的,用于现场总线技术过程自动化、制造自动化、楼宇自动化等领域的现场智能设备互连通讯网络。它作为工厂数字通信网络的基础,沟通了生产过程现场及控制设备之间及其与更高控制管理层次之间的联系。它不仅是一个基层网络,而且还是一种开放式、新型全分布控制系统。这项以智能传感、控制、计算机、数字通讯等技术为主要内容的综合技术,已经受到世界范围的关注,成为自动化技术发展的热点,并将导致自动化系统结构与设备的深刻变革。现场总线设备的工作环境处于过程设备的底层,作为工厂设备级基础通讯网络,要求具有协议简单、容错能力强、安全性好、成本低的特点:具有一定的时间确定性和较高的实时性要求,还具有网络负载稳定,多数为短帧传送、信息交换频繁等特点。由于上述特点,现场总线系统从网络结构到通讯技术,都具有不同上层高速数据通信网的特色。

目前国际上有40多种现场总线,但没有任何一种现场总线能覆盖所有的应用面,按其传输数据的大小可分为3类:传感器总线(sensorbus),属于位传输;设备总线(devicebus),属于字节传输;现场总线,属于数据流传输。下面让我一起去认识主要的几种总线。 一、FF现场总线 FF现场总线基金会是由WORLDFIPNA(北美部分,不包括欧洲)和ISPFoundation于1994年6月联合成立的,它是一个国际性的组织,其目标是建立单一的、开放的、可互操作的现场总线国际标准。这个组织给予了IEC现场总线标准起草工作组以强大的支持。这个组织目前有l00多成员单位,包括了全世界主要的过程控制产品及系统的生产公司。1997年4月这个组织在中国成立了中国仪协现场总线专业委员会(CFC)。致力于这项技术在中国的推广应用。FF成立的时间比较晚,在推出自己的产品和把这项技术完整地应用到工程上相对于PROFIBUS和WORLDFIP要晚。但是正由于FF是1992年9月成立的,是以

CNA总线详解

详解车载网络CAN总线系统 息,并将此信息发送至相对应的控制单元内。 『车身上各种控制单元的分布图』 通过上图我们可以看到车身上的各种控制单元,车越高级,车身上的控制单元也就越多,每个控制单元都可看做一台独立的电脑,它可以接受信息,同时能对各种信息进行处理、分析,然后发出一个指令。比如发动机控制单元会接受来自进气压力传感器、发动机温度传感器、油门踏板位置传感器、发动机转速传感器等等的信息,在经过分析和处理后会发送相应的指令来控制喷油嘴的喷油量、点火提前角等等,其它控制单元的工作原理也都类似。在这里可以给大家做一个比喻,车上的各种控制单元就好比一家公司各个部门的经理,每个部门的经理接受来自自己部门员工的工作汇报,经过分析作出决策,并命令该部门的员工去执行。

『控制单元』 车身上的这些控制单元并不是独立工作的,它们作为一个整体,需要信息的共享,那么这就存在一个信息传递的问题。比如发动机控制单元内的发动机转速与油门踏板位置这两个信号也需要传递给自动变速器的控制单元,然后自动变速器控制单元会据此来发出升档和降档的操作指令,那么两个控制单元之间又是如何进行通信的呢? 『每项信息都通过各自独立的数据线进行交换』 目前在车辆上应用的信息传递形式有两种。第一种是每项信息都通过各自独立的数据线进行交换。比如两个控制单元间有5种信息需要传递,那么则需要5根独立的数据线。也就是说信息的种类越多,数据线的数量和控制单元的针脚数也会相应增加。这些复杂繁多的线束无疑会增加车身重量,也为整车的布线带来一定困难。

『所有信息都通过两根数据线进行交换』 第二种方式是控制单元之间的所有信息都通过两根数据线进行交换,这种数据线也叫CAN 数据总线。通过该种方式,所有的信息,不管信息容量的大小,都可以通过这两条数据线进行传递,这种方式充分的提高了整个系统的运行效率。我们常见的电脑键盘有104个按键,却可以发出数百种不同的指令,但键盘与电脑主机之间的数据连接线只有7根,键盘正是依靠这7根数据连接线上不同的编码信号来传递信息的。CAN数据总线的原理也正是如此。这种一线一用的专线制改为一线多用制,可以大大减少汽车上电线的数量,同时也简化了整车的布线。 在了解到两个控制单元是通过两根数据线来进行信息交换的基础上,我们可以将其推而广之,多个控制单元之间的通信其实就是将每个控制单元都连接到这两条CAN总线上,从而实现多个控制单元间的信息共享。 『多个控制单元间的信息传递』 目前汽车上的CAN总线连接方式主要有两种,一种是用于驱动系统的高速CAN总线,速率可达到500kb/s,另一种是用于车身系统的低速CAN总线,速率为100kb/s。当然对于中高级轿车还有一些如娱乐系统或智能通讯系统的总线,它们的传输速率更高,可以超过1Mb/s。高速CAN总线主要连接发动机控制单元、ABS控制单元、安全气囊控制单元、组合仪表等这