s12dg128寄存器介绍及例程

PWM模块介绍

时间:2009-11-25 22:51来源:电子设计吧作者:dzsj8 点击: 662次该教程以MC9S12XS128单片机为核心进行讲解,全面阐释该16位单片机资源。本文为第一讲,开始介绍该MCU的PWM模块。

PWM 调制波有8个输出通道,每一个输出通道都可以独立的进行输出。每一个输出通道都有一个精确的计数器(计算脉冲的个数),一个周期控制寄存器和两个可供选择的时钟源。每一个P WM 输出通道都能调制出占空比从0—100% 变化的波形。

PWM 的主要特点有:

1、它有8个独立的输出通道,并且通过编程可控制其输出波形的周期。

2、每一个输出通道都有一个精确的计数器。

3、每一个通道的P WM 输出使能都可以由编程来控制。

4、PWM 输出波形的翻转控制可以通过编程来实现。

5、周期和脉宽可以被双缓冲。当通道关闭或PWM 计数器为0 时,改变周期和脉宽才起作用。

6、8 字节或16 字节的通道协议。

7、有4个时钟源可供选择(A、SA、B、SB),他们提供了一个宽范围的时钟频率。

8、通过编程可以实现希望的时钟周期。

9、具有遇到紧急情况关闭程序的功能。

10、每一个通道都可以通过编程实现左对齐输出还是居中对齐输出。

PWM寄存器说明1——PWME、PWMCLK

时间:2009-11-25 22:56来源:电子设计吧作者:dzsj8 点击: 493次

1、PWM启动寄存器PWME

PWME 寄存器每一位如图1所示:

复位默认值:0000 0000B

图1 PWME 寄存器

每一个PWM 的输出通道都有一个使能位P WMEx 。它相当于一个开关,用来启动和关闭相应通道的PWM 波形输出。当任意的P WMEx 位

置1,则相关的P WM 输出通道就立刻可用。

用法:PWME7=1 --- 通道7 可对外输出波形

PWME7=0 --- 通道7 不能对外输出波形

注意:在通道使能后所输出的第一个波形可能是不规则的。当输出通道

工作在串联模式时(PWMCTL 寄存器中的CONxx置1),那么)使能相应

的16位PWM 输出通道是由PWMEx 的高位控制的,例如:设置PWMCTL_CON01 = 1,通道0、1级联,形成一个16位PWM 通道,由通道 1 的使

能位控制PWM 的输出。

2、PWM时钟选择寄存器PWMCLK

PWMCLK 寄存器每一位如图3所示:

复位默认值:0000 0000B

图2 PWMCLK 寄存器

S12的PWM 共有四个时钟源,每一个P WM 输出通道都有两个时钟可供选

。其中0、1、4、5 通道可选用择(Clock A、Clock SA 或Clock B、Clock SB))

Clock A和ClockSA,2、3、6、7 通道可选用ClockB、ClockSB 通道。该寄存器用来实现几个通道时钟源的选择。

用法:PCLK0 =1 --- 通道0(PTP0)的时钟源设为ClockSA

PCLK2 =0 --- 通道2(PTP2)的时钟源设为ClockB

PWM寄存器说明2——PWMPRCLK、PWMSCLA/B

时间:2009-11-25 22:58来源:电子设计吧作者:dzsj8 点击: 435次

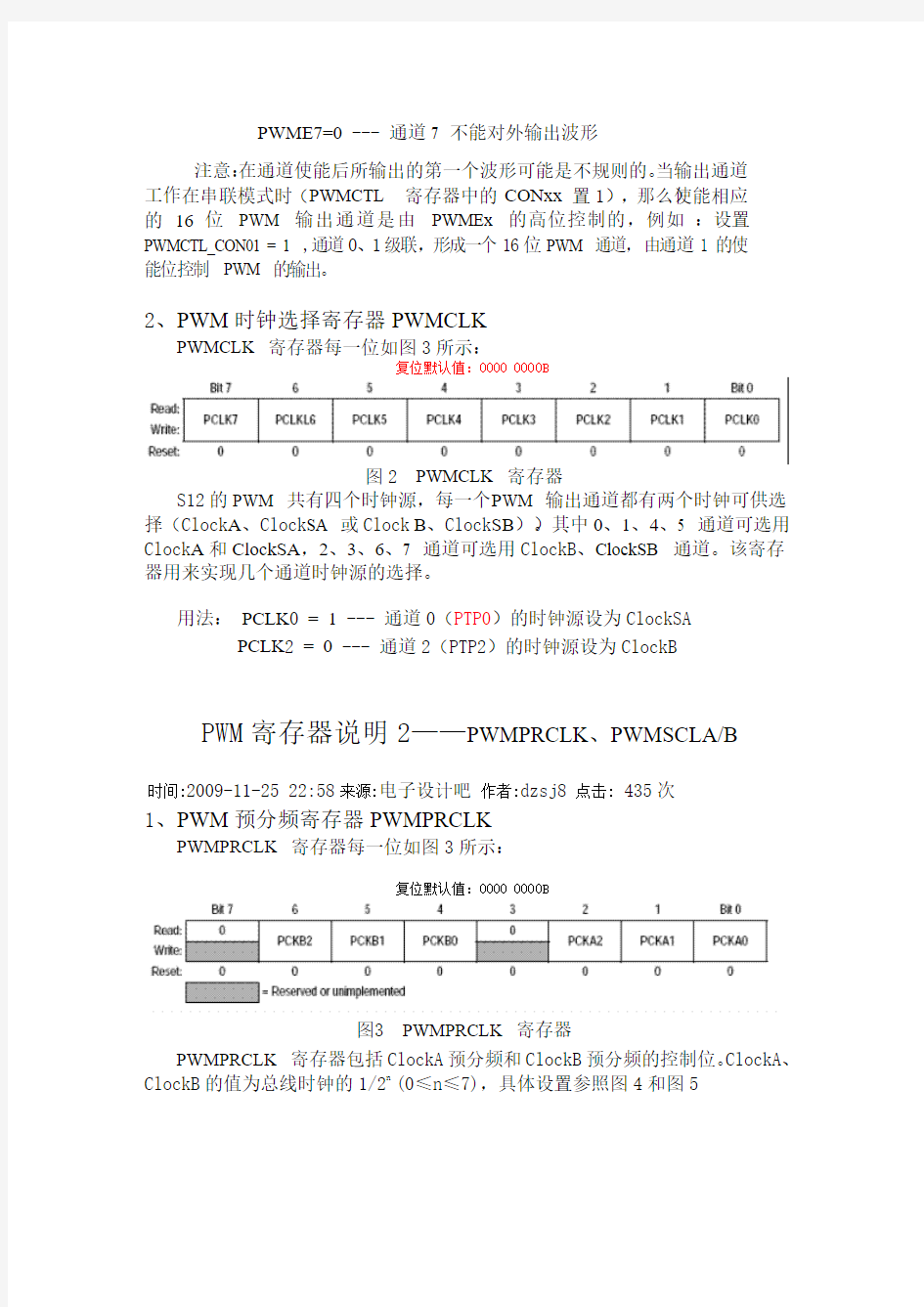

1、PWM预分频寄存器PWMPRCLK

PWMPRCLK 寄存器每一位如图3所示:

复位默认值:0000 0000B

图3PWMPRCLK 寄存器

PWMPRCLK 寄存器包括ClockA预分频和ClockB预分频的控制位。ClockA、ClockB的值为总线时钟的1/2n (0≤n≤7),具体设置参照图4和图5

图4Clock A 预分频设置

图5Clock B预分频设置

PCKB0~PCKB2是对ClockB进行预分频。

PCKA0~PCKA2是对ClockA进行预分频。

2、PWM分频寄存器PWMSCLA、PWMSCLB

PWMSCLA 寄存器每一位如图6所示:

图6 PWMSCLA寄存器

Clock SA 是通过对P WMSCLA 寄存器的设置来对ClockA 进行分频而产生的。其计算公式为:

Clock SA=Clock A /(2*PWMSCLA)

PWMSCLB 寄存器与PWMSCLA 寄存器相似,Clock S B 就是通过对PWMSCLB 寄存器的设置来对C lockB 进行分频而产生的。其计算公式为:

Clock SB=Clock B /(2*PWMSCLB)

PWM寄存器说明3——PWMPOL、PWMCAE

时间:2009-11-26 07:09来源:电子设计吧作者:dzsj8 点击: 372次

1、PWM极性选择寄存器PWMPOL

PWMPOL 寄存器每一位如图7所示:

该寄存器是0~7通道PWM输出起始极性控制位,用来设置PWM输出的

起始电平。

用法:PWMPOL_PPOL0=1--- 通道0 在周期开始时输出为高电平,当

计数器等于占空比寄存器的值时,输出为低电平。对外输出波形先是高电平

然后再变为低电平。

2、PWM波形对齐寄存器PWMCAE

PWMCAE 寄存器每一位如图8所示:

图8PWMCAE 寄存器

PWMCAE 寄存器包含8个控制位来对每个P WM 通道设置左对齐输出或中心对齐输出。

用法: PWMCAE_CAE0 = 1 --- 通道0 中心对齐输出

PWMCAE_CAE7 = 0 --- 通道7 左对齐输出

注意:只有输出通道被关闭后才能对其进行设置,即通道被激活后不能对其进行设置。

图7PWMPOL 寄存器

PWM寄存器说明4——PWMCTL

时间:2009-11-26 07:22来源:电子设计吧作者:dzsj8 点击: 389次

1、PWM控制寄存器PWMCTL

PWMCTL 寄存器每一位如图9所示:

图9PWMCTL 寄存器

该控制寄存器设定通道的级联和两种工作模式:等待模式和冻结模式。这两种模式如图10和图11所示。

图10 等待模式

图11 冻结模式

只有当相应的通道关闭后,才能改变这些控制字。

用法:

PWMCTL_CON67=1 --- 通道6、7 级联成一个16位的PWM通道。此时只有7通道的控制字起作用,原通道7的使能位、PWM输出极性选择位、时钟选择控制位以及对齐方式选择位用来设置级联后的PWM输出特性PWMCTL_CON67=0 --- 通道6,7 通道不级联

CON45、CON23、CON01 的用法同CON67 相似。设置此控制字的意义在于扩大了P WM 对外输出脉冲的频率范围。

PSW AI=1--- M CU 一旦处于等待状态,就会停止时钟的输入。这样就不会因时钟在空操作而费电;当它置为0,则M CU 就是处于等待状态,也允许时钟的输入。

P FRZ=1 --- M CU 一旦处于冻结状态,就会停止计数器工作。

PWM寄存器说明5——PWMCNTx、PWMPERx、PWMDTYx

时间:2009-11-26 07:30来源:电子设计吧作者:dzsj8 点击: 440次

1、PWM通道计数寄存器PWMCNTx

PWMCNTx 寄存器共有8个,每一个通道都有一个8位PWM加/减双向计数器,通道级联后可变成16位PWM加/减双向计数器。下面以PWMCNT0为例对P WMCNTx 寄存器进行介绍。

PWMCNT0寄存器如图12所示:

图12 PWMCNT0 寄存器

计数器以所选时钟源的频率运行。计数器在任何时候都可以被读,而不影

响计数,也不影响对P WM 通道的操作。

任何值写入PWMCNT0 寄存器都会导致计数器复位置0,且其计数方向会被设置为向上计数,并且会立刻从缓冲器载入任务和周期值,并会根据翻转极性的设置来改变输出。当计数器达到计数值后,会自动清零。只有当通道使能后,计数器才开始计数。

2、PWM通道周期寄存器PWMPERx

PWMPERx 寄存器共有8个,每一个通道都有一个这样的周期寄存器。这个寄存器的值就决定了相关P WM 通道的周期。每一个通道的周期寄存器都

是双缓冲的,因此如果当通道使能后,改变他们的值,将不会发生任何作用,除非当下列情况之一发生:

*有效的周期结束。

*对计数器进行写操作(计数器复位)

*通道不可用(PWME x = 0)

这样就会使P WM 输出波形要么是新波形要么是旧波形,并不会在两者之间进行交替变换。如果通道不可用,那么对周期寄存器进行写操作,将会直接导致周期寄存器同缓冲器一起闭锁。图13所示的是P WMPER0 寄存器:

图13 PWMPER0 寄存器

3、PWM通道占空比寄存器PWMDTYx

PWMDTYx 寄存器也有8 个,每一个通道都有一个这样的占空比常数寄存器。这个寄存器的值就决定了相关P WM 通道输出波形的占空比。每一个通道的占空比寄存器都是双缓冲的,因此如果当通道被激活后,改变他们的

值将不会发生任何作用,除非当下列情况之一发生:

*有效的周期结束。

*对计数器进行写操作(计数器复位)

*通道不可用(PWME x = 0)

这样就会使P WM 输出波形要么是新波形要么是旧波形,并不会在两者之间进行交替变换。如果通道没有被激活,那么对占空比常数寄存器进行写操作,将会直接导致周期寄存器同缓冲器一起闭锁。

当计数值与占空比常数P WMDTY 相等时,则比较输出器有效,这时就会将触发器置位,然后P WMCNT 继续计数,当计数值与周期常数P WMPER 相等时,比较器输出有效,将触发器复位,同时也使P WMCNT 复位,结束一个输出周期。

PWM工作原理

时间:2009-11-27 15:44来源:电子设计吧作者:dzsj8 点击: 490次

S12微控制器PWM模块是由独立运行的8位脉冲计数器PWMCNT、两个比较寄存器PWMPER和PWMDTY组成。

1、左对齐方式

在该方式下,脉冲计数器为循环递增计数,计数初值为0 。

当PWM使能后,计数器PWMCNT从0开始对时钟信号递增计数,开始一个输出周期。当计数值与占空比常数寄存器PWMDTY相等时,比较器1输出有效,将触发器置位,而PWMCNT继续计数;当计数值与周期常数寄存器PWMPER相等时,比较器2输出有效,将触发器复位,同时PWMCNT也复位,结束一个输出周期。原理参照图14:

图14 PWM左对齐方式

2、中心对齐方式

在该方式下,脉冲计数器为双向计数,计数初值为0 。

当PWM使能后,计数器PWMCNT从0开始对时钟信号递增计数,开始输出一个周期。当计数器与占空比常数寄存器PWMDTY相等时,比较器1输出有效,触发器翻转,而PWMCNT继续计数,当计数值与周期常数PWMPER相等时,比较器2输出有效,此时改变PWMCNT的计数方向,使其递减计数;当PWMCNT再次与PWMDTY 相等时,比较器1再一次输出有效,使触发器再次翻转,而PWMCNT继续递减计数,等待PWMCNT减回至0,完成一个输出周期。原理参照图15:

图15 中心对齐方式

3、周期计算方法

左对齐方式:

输出周期 = 通道周期× PWMPERx

中心对齐方式:

输出周期 = 通道周期× PWMPERx × 2

4、脉宽计算方法

左对齐方式:

占空比 = [ (PWMPERx - PWMDTYx) / PWMPERx ] × 100%中心对齐方式:

占空比 = [ PWMDTYx / PWMPERx ] × 100%

PWM 应用实例

时间:2009-11-28 21:49来源:电子设计吧作者:dzsj8 点击: 412次

PWM 初始化步骤总结

1、禁止PWM PWME = 0

2、选择时钟PWMPRCLK,PWMSCLA,PWMSCLB,PWMCLK

3、选择极性PWMPOL

4、选择对齐方式PWMCAE

5、选择占空比和周期PWMDTYx,PWMPERx

6、使能PWM PWME = 1

【例程1】

//------------------------------------------------------------------------------------------------------------------//

//功能说明:MC9S12XS128--PWM例程

//使用说明:实现通道3(PTP3)输出频率为1KHz,占空比为50%的方波,用示波器观察

//程序设计:电子设计吧【https://www.360docs.net/doc/c312789176.html,】

//设计时间:2010.01.21

//----------------------------------------------------------------------------------------------------------------//

#include

#include "derivative.h" /* derivative-specific definitions */

//--------------初始化函数----------------//

//-----时钟初始化程序--------//

void PLL_Init(void) //PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)

{ //锁相环时钟=2*16*(2+1)/(1+1)=48MHz

REFDV=1; //总线时钟=48/2=24MHz

SYNR=2;

while(!(CRGFLG&0x08));

CLKSEL=0x80; //选定锁相环时钟

}

//-----PWM初始化程序------//

void PWM_Init(void)

{

PWME_PWME3=0x00; // Disable PWM 禁止

PWMPRCLK=0x33; // 0011 0011 A=B=24M/8=3M 时钟预分频寄存器设置

PWMSCLA=150; // SA=A/2/150=10k 时钟设置

PWMSCLB=15; // SB=B/2/15 =100k 时钟设置

PWMCLK_PCLK3=1; // PWM3-----SB 时钟源的选择

PWMPOL_PPOL3=1; // Duty=High Time 极性设置

PWMCAE_CAE3=0; // Left-aligned 对齐方式设置

PWMCTL=0x00; // no concatenation 控制寄存器设置 PWMPER3=100; // Frequency=SB/100=1K 周期寄存器设置 PWMDTY3=50; // Duty cycle = 50% 占空比寄存器设置 PWME_PWME3=1; // Enable PWM 使能

}

//-----------------主函数--------------------//

void main(void)

{

/* put your own code here */

PLL_Init();

PWM_Init();

EnableInterrupts;

for(;;) {

_FEED_COP(); /* feeds the dog */

} /* loop forever */

/* please make sure that you never leave main */

}

A/D转换模块介绍1

时间:2009-11-30 22:10来源:电子设计吧作者:dzsj8 点击: 327次

1、A/D转换原理

A/D转换的过程是模拟信号依次通过取样、保持和量化、编码几个过程后转换为数字格式。

a)取样与保持

一般取样与保持过程是同时完成的,取样-保持电路的原理图如图16

所示,由输入放大器A

1、输出放大器A

2

、保持电容C

H

和电子开关S组成,

要求 A

V1 * A

V2

= 1。原理是:当开关S闭合时,电路处于取样阶段,电容

器充电,由于 A

V1 * A

V2

= 1,所以输出等于输入;当开关S断开时,由于

A 2输入阻抗较大而且开关理想,可认为C

H

没有放电回路,输出电压保持不

变。

图16 取样-保持电路

取样-保持以均匀间隔对模拟信号进行抽样,并且在每个抽样运算后在足够的时间内保持抽样值恒定,以保证输出值可以被A/D 转换器精确转换。

b)量化与编码

量化的方法,一般有舍尾取整法和四舍五入法,过程是先取顶量化单位Δ,量化单位取值越小,量化误差的绝对值就越小,具体过程在这里就不做介绍了。将量化后的结果用二进制码表示叫做编码。

2、A/D转换器的技术指标

a)分辨率

分辨率说明A/D转换器对输入信号的分辨能力,理论上,n位A/D转换器能区分的输入电压的最小值为满量程的1/2n 。也就是说,在参考电压一定时,输出位数越多,量化单位就越小,分辨率就越高。S12的ATD模块中,

若输出设置为8位的话,那么转换器能区分的输入信号最小电压为19.53mV。

b)转换时间

A/D转换器按其工作原理可以分为并联比较型(转换速度快ns级)、逐次逼近型(转换速度适中us级)、双积分型(速度慢抗干扰能力强)。

不同类型的转化的A/D转换器转换时间不尽相同,S12的ATD模块中,8位数字量转换时间仅有6us,10位数字量转换时间仅有7us。

A/D转换模块介绍2

时间:2009-12-09 21:32来源:电子设计吧作者:dzsj8 点击: 334次S12内置了2组10位/8位的A/D模块:ATD0和ATD1,共有16个模拟量输入通道,属于逐次逼近型A/D转换器(这个转换过程与用天平称物的原理相似)。

1、功能结构图

图17 A/D 模块功能结构图

图17所示的是A/D 模块的功能结构,这个功能模块被虚线划分成为图示所示的虚线所隔离的三个部分:IP 总线接口、转换模式控制/寄存器列表,自定义模拟量。

IP 总线接口负责该模块与总线的连接,实现A/D 模块和通用I/O 的目的,还起到分频的作用;

转换模式控制寄存器列表中有控制该模块的所有的寄存器,执行左右对齐

运行和连续扫描。

自定义模拟量负责实现模拟量到数字量的转换。包括了执行一次简单转换

所需的模拟量和数字量。

2、HCS12中A/D转化模块特点

8/10 位精度;7 us, 10-位单次转换时间.;采样缓冲放大器;可编程采样时间;左/右对齐, 有符号/无符号结果数据;外部触发控制;转换完成中断;模拟输入8通道复用;模拟/数字输入引脚复用;1 到8转换序列长度;连续转换模式;多通道扫描方式。

ATD 模块有模拟量前端、模拟量转换、控制部分及结果存储等四部分组成。其中模拟前端包括多路转换开关、采样缓冲器、放大器等,结果存储部分主要有8个16 位的存储器和反映工作状态的若干标志位。

A/D寄存器说明1——ATD0CTL2、

时间:2009-12-11 12:26来源:电子设计吧作者:dzsj8 点击: 339次

1、ATD0控制寄存器2---ATD0CTL2

ATD0CTL2主要控制ATD0的启动、状态标志以及上电模式,对寄存器进行写操作时,将中断当前的转化过程。寄存器ATD0CTL2如图18所示:

图18ATD0CTL2寄存器

ADPU:A/D 使能控制位,相当于一个开关,用来启动/禁止A/D转换

1 = A/D 模块上电

0 = 禁止A/D,以减少功耗

AFFC:A/D 快速转换完成标志位清零

1 = 快速标志位清零顺序,每次读取结果寄存器自动清零

0 = 正常标志位清零顺序,需要软件方式对状态标志位清零

AWAI:A/D 等待模式

1 = 等待模式下,ATD继续运行

0 = 等待模式下,ATD停止运行,以降低功耗

ETRIGP、ETRIGLE、ETRIGE:

ETRIGLE ETRIGP ETRIGE描述

x x 0 忽略外部触发

0 0 1 下降沿触发

0 1 1 上升沿触发

1 0 1 低电平触发

1 1 1 高电平触发

【注意】ETRIGE:外部触发使能控制位,该功能借助引脚AN7,当AN7接收到外部触发时,启动A/D转换,否则不进行转换。0--忽略外部触发;1--有外部触发时开始转换,此时AN7不能用于A/D转换。

ASCIE:A/D 转化序列转换结束中断使能控制位

1 = 允许ATD转换序列转换结束后发生中断

0 = 禁止ATD 中断

ASCIF:A/D转换序列转换结束中断标志,只用于读。

1 = 发生中断

0 = 为发生中断

A/D寄存器说明2——ATD0CTL3

时间:2009-12-12 12:06来源:电子设计吧作者:dzsj8 点击: 311次

2、ATD0控制寄存器3---ATD0CTL3

ATD0CTL3主要控制结果寄存器的映射,设置转换序列的长度,还可以暂时冻结ATD0模块,尤其确定ATD0在BDM状态下的行为。寄存器ATD0CTL3如图19所示:

图19ATD0CTL3寄存器

S1C、S2C、S4C、S8C:转换序列长度选择位控制位

【注意】ATD的每次启动要进行若干次扫描循环,每次扫描循环称为一个转换序列。

FIFO:结果寄存器FIFO模式控制位,

1 = 结果寄存器映射到转换序列

0 = 结果寄存器没有映射到转换序列

FRZ0、FRZ1:背景调试冻结控制位

FRZ Response

00Ignore IFREEZE(冻结模式下继续转换)

01Reserved(冻结模式下保留)

10Finish conversion then freeze(完成转换后冻结)

11Freeze Immediately(冻结模式下立刻冻结)

A/D寄存器说明3——ATD0CTL4

时间:2009-12-14 11:50来源:电子设计吧作者:dzsj8 点击: 298次

3、ATD0控制寄存器4---ATD0CTL4

ATD0CTL4用于选择时钟,选择采样转换时间以及选择8位/10位转换方式。寄存器ATD0CTL4如图20所示:

图20ATD0CTL4寄存器

SRES8 :A/D精度选择控制位

1 =将采集到的模拟量以8位二进制数表示

0 = 将采集到的模拟量以10位二进制数表示

SMP0、SMP1 : 采样时间选择控制位

SMP [1:0]采样时间

00 2 A/D 时钟周期

01 4 A/D 时钟周期

108 A/D 时钟周期

1116 A/D 时钟周期

PPS[0:4] : 5 位模数计数器预分频器

- 分频系数从2到64

- A/D时钟计算公式:ATDClock = BusClock/(PRS + 1) × 0.5

- A/D时钟频率应满足:

【注意】对于AD转换来说,它的转换周期包括采样时间和运算时间。如果频率太高,则采样时间过短。这对于输出阻抗比较大或信号频率比较高的信号来说,就会产生较大的采样误差,那么AD转换的精度就会受较大的影响。

A/D寄存器说明4——ATD0CTL5

时间:2009-12-17 19:39来源:电子设计吧作者:dzsj8 点击: 303次

4、ATD0控制寄存器4---ATD0CTL5

ATD0CTL5用于选择转换方式,选择转换通道,设置单/多通道转换和单次/连续转换模式以及对齐方式。寄存器ATD0CTL5如图20所示:

图20 寄存器ATD0CTL5

【注意】ATDCTRL5设置成多通道转换后,ATDCTRL3设置采集的通道数,此外ATDCTRL5中还需要设置多通道采集的起始通道。比如采集7个通道,起始通道是1,那么就采集从1-7通道,如果起始通道是2,就采集2-7,还有0通道。【注意】在S12系列中,当转换序列长度设置为1(S8C:S1C=0001),MULT=0时,只对一个通道进行一次转换。

A/D寄存器说明5——ATD0START0、ATD0START1

时间:2009-12-27 00:47来源:电子设计吧作者:dzsj8 点击: 263次

5、ATD0状态寄存器5---ATD0START0、ATD0START1

ATD0START0反映当前的转换通道、A/D转换是否结束、是否有外部触发等;ATD0START1反映转换序列中相应的转换是否完成。寄存器ATD0START0、

ATD0START1如图21所示:

SCF ---转换序列完成标志

在单次转换模式时,当转换完成后置位(SCAN = 0)

在连续转换模式时,当第一次转换完成后置位(SCAN = 1),当AFFC = 0,写1清零。

ETORF ---外部触发覆盖标志

如果在转换过程中高/低电平出现,置位F IFOR

当结果寄存器在读出之前已经被写入时,置位( CCF 没有清零)

CC[2:0]转换计数器---3位计数器指向下一个将要转换的通道

CCF7 -CCF0--独立通道转换完成标志位每个相应的通道转换结束后置位,当相应的A/D 结果寄存器被读出时,清零,注意当A FFC 位不同时的情况

A/D转换应用实例

时间:2009-12-27 00:51来源:电子设计吧作者:dzsj8 点击: 351次

第十六讲:A/D转换应用实例

要让ATD 开始转换工作,必须经过以下三个步骤:

1.将ADPU 置1,使ATD 启动;

2.按照要求对转换为数、扫描方式、采样时间、时钟频率及标志检查等方式进

行设置;

3.发出启动命令;

如果上电默认状态即能满足工作要求,那么只要将ADPU 置1,然后通过控制

寄存器发出转换命令,即可实现转换。

【例程2】

程序描述:由通道ATD0进行单通道A/D转换,转换值在B口显示

程序如下:

#include

#include

#pragma LINK_INFO DERIVATIVE "mc9s12dg128b"

/******定义变量********/

word AD_wValue;//AD转换结果

/*时钟初始化*/

void PLL_Init(void) //PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)

{ //锁相环时钟=2*16*(2+1)/(1+1)=48MHz

REFDV=1; //总线时钟=48/2=24MHz

SYNR=2;

while(!(CRGFLG&0x08));

CLKSEL=0x80;

}

/*AD初始化*/

void AD_Init(void)

{

ATD0CTL2=0xC0; // 启动A/D, 快速清零, 无等待模式, 禁止外部触发, 中断禁止

ATD0CTL3=0x20; // 转换序列长度为4, No FIFO, Freeze模式下继续转换ATD0CTL4=0x85; // 8位精度, 2个时钟,

ATDClock=[BusClock*0.5]/[PRS+1]=2MHz;PRS=5,divider=12

ATD0CTL5=0xA0; // 右对齐无符号,单通道采样,通道0

ATD0DIEN=0x00; // 禁止数字输入

}

/*读取AD转换结果*/

void AD_GetValue(word *AD_wValue)

{

*AD_wValue=ATD0DR0; //读取结果寄存器的值

}

/**********主函数**************/

void main(void)

{

PLL_Init();

AD_Init();

DDRB=0xFF;

PORTB=0x00;

EnableInterrupts;

for(;;)

{

while(!ATD0STAT1_CCF0); // 等待转换结束

while(ATDOSTAT1_CCF0==1)

AD_GetValue(&AD_wValue); // 读取转换结果

PORTB = (byte)AD_wValue; // 在B口显示转换值

}

}

Timer模块介绍1

时间:2009-12-29 11:51来源:电子设计吧作者:dzsj8 点击: 324次

1、简述

MC9S12XS128定时器模块与MC9S12DG128 ECT部分功能完全类似,以下均以ECT模块介绍xs128定时器模块。

HC12 增强型捕捉计时器模块在HCS12标准定时器的基础上增加了一些特点,用以扩展它的应用范围,特别是在汽车ABS 方面。

基准计时器的核心仍然是一个16 位的可编程计数器,其时钟源来自一个预分频器。该计时器可以被应用于多个方面,包括在对输入波形进行测量的同时产生一个输出波形。波形的脉宽可以在几微秒到数秒的范围内变化。

增强型定时器模块(ECT)的结构框图如下,ECT功能相当于高速的I/O口,由一个4位预分频器、一个16位自由运行计数器,8个16位IC/OC通道,2个16位脉冲累加器以及一个16位模数递减计数器组成。

ECT实际上是一个16位的可编程计数器,它的基本时钟频率可以通过预分频器设置,用于产生波形输出,测量输入波形,统计脉冲个数,可以作为定时中断功能和独立时钟基准。

2、运行模式

停止:由于时钟停止,计时器和计数器均关闭。

冻结:计时器和计数器均保持运行,直到T SCR($06)的T SFRZ 位被置1。

等待:计数器保持运行,直到T SCR($06)的T SWAI 位被置1。

正常:计时器和计数器均保持运行,

直到T SCR($06)的T EN 位和M CCTL($26)的

单片机各寄存器汇总

符号 地址功能介绍 B F0H B寄存器 ACC E0H 累加器 PSW D0H 程序状态字 IP B8H 中断优先级控制寄存器 P3 B0H P3口锁存器 IE A8H 中断允许控制寄存器 P2 A0H P2口锁存器 SBUF 99H 串行口锁存器 SCON 98H 串行口控制寄存器 P1 90H P1口锁存器 TH1 8DH 定时器/计数器1(高8位)TH0 8CH 定时器/计数器1(低8位)TL1 8BH 定时器/计数器0(高8位)TL0 8AH 定时器/计数器0(低8位) TMOD 89H 定时器/计数器方式控制寄存器 TCON 88H 定时器/计数器控制寄存器 DPTR 82H 83H 83H数据地址指针(高8位) PC SP 81H 堆栈指针 P0 80H P0口锁存器 PCON 87H 电源控制寄存器 、PSW-----程序状态字。 D7D6D5D4D3D2D1D0 CY AC F0 RS1 RS0 OV P 下面我们逐一介绍各位的用途 CY:进位标志。 AC:辅助进、借位(高半字节与低半字节间的进、借位)。 F0:用户标志位,由用户(编程人员)决定什么时候用,什么时候不用。 RS1、RS0:工作寄存器组选择位。这个我们已知了。 0V:溢出标志位。运算结果按补码运算理解。有溢出,OV=1;无溢出,OV=0。什么是溢出我们后面的章节会讲到。

P :奇偶校验位:它用来表示ALU 运算结果中二进制数位“1”的个数的奇偶性。若为奇数,则P=1,否则为0。 运算结果有奇数个1,P =1;运算结果有偶数个1,P =0。 例:某运算结果是78H (01111000),显然1的个数为偶数,所以P=0。 定时/计数器寄存器 1.工作方式寄存器TMOD(P134) TMOD 为T0.T1的工作方式寄存器,其各位的格式如下:TMOD D7 D6 D 5 D4 D3 D2 D1 D0 GATE C/-T M1 M0 GATE C/-T M1 M0 定时器1 定时器0 位7 GATE ——T1的门控位。 当GATE=0时,只要控制TR1置1,即可启动定时器T1开始工作; 当GATE=1时,除需要将TR1置1外,还要使INT1引脚为高电平,才能启动相应的定时器开始工作。 位6 C/—T ——T1的功能选择位。 当C/—T=0时,T1为定时器方式; 当C/—T=0时,T1为计数器方式; 位5和位4 M1和M0——T1的方式选择位。 由这两位的组合可以定义T1的3种工作方式 定时器T1工作方式选择表 如右表: 位3 GATE ——T0的门控位。 当GATE=0时,只要控制TR0置1,即可启动定时器T0开始工作; 当GATE=1时,除需要将TR0置1外,还要使INT0引脚为高电平,才能启动相应的定时器开始工作。 位2 C/T ——T1的功能选择位。 当C/—T=0时,T0为定时器方式; 当C/—T=0时,T0为计数器方式; 位1和位0 M1和M0—T0的方式选择位。 由这两位的组合可以定义T1的3种工作方式 定时器T0工作方式选择表 TMOD 不能进行位寻址,只能用字节传送指令设置定时器工作方式,低半节定义定时器0,高半字节定义定时器1。复位时,TMOD 所有位均为0,定时器处于停止工作状态。 定时/计数器控制寄存器中断请求标志寄存器TCON(P183) TCON 的作用是控制定时器的启/停,标志定时器的溢出和中断情况。定时器控制寄存器TCON 各位格式如下:TCON(88H) 8FH 8EH 8DH 8CH 8BH 8AH 89H 88H TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0 当有中断源发出请求时,有硬件将相应的中断标志位置 1.在中断请求被响应前,相应中断标志位被锁存在特殊功能寄存器TCON 或SCON 中。 TCON 为定时器T0和T1的控制寄存器,同时也锁住T0和T1的溢出中断标志及外部中断——INT0和— M1 M0 工作方式 功能描述 0 0 方式0 13位计数器 0 1 方式1 16位计数器 1 0 方式 2 自动再装入8位计数器 1 1 方式3 定时器1:停止计数 M1 M0 工作方式 功能描述 0 0 方式0 13位计数器 0 1 方式1 16位计数器 1 0 方式 2 自动再装入8位计数器 1 1 方式3 定时器0:分成2个8位计数器

寄存器组的设计与实现

寄存器组的设计与实现 第______ _________组 成员___ ____ ____ 实验日期___ _____ _____ 实验报告完成日期___________ 1、实验目的 1、学习掌握Quartus软件的基本操作; 2、理解寄存器组的工作原理和过程; 3、设计出寄存机组并对设计的正确性进行验证; 二、实验内容

1、设计出功能完善的寄存器组,并对设计的正确性进行验证。要求如下: (1)用图形方式设计出寄存器组的电路原理图 (2)测试波形时用时序仿真实现,先将不同的数据连续写入 4个寄存器后,再分别读出 (3)将设计文档封装成器件符号。 (4)数据的宽度最好是16位 2、能移位的暂存器实验,具体要求如下: (1)用图形方式设计出能移位的暂存器电路原理图,分别实 现左移、逻辑右移和算术右移。 (2)测试波形时要用时序仿真实现,测试数据不要全为0也 不要全为1,算术右移的测试数据要求为负数(即符号位为 1) (3)将设计文档封装成器件符号。 (4)数据的宽度最好是16位 三、能完善的寄存器组设计思想 1、对于寄存器组设计思路 利用具有三态功能的寄存器堆74670芯片进行设计,根据实验要求,需要设计16位的存储器组,则需要74670芯片4片,在寄存器组工作时,同时对4片74670芯片进行读写操作控制,封装后即可作为包含有4个寄存器的16位寄存器组在主机系统中调用。 2、对74670器件的学习 74670(三态输出4×4寄存器堆)提供4个4位的寄存器,在功能上可对4个寄存器去分别进行写操作和读操作。在寄存器进行写操作时,通过WB、WA两个寄存器选择端的组合和00、01、10、11、来选择寄存器,公国GWN写操作端控制进行三态控制,在GWN为低电平时将数据写入端数据D4D3D2D1写入该寄存器;在寄存

计算机原理与及设计实验报告

计算机原理与设计 实验报告 实验三多周期MIPS CPU的控制部件用有限状态机实现多周期CPU的控制部 件

一.实验目的 1、了解MIPS—CPU控制器的功能和工作原理; 2、掌握用有限状态机技术实现多周期控制器的方法; 3、熟练掌握用Verilog HDL语言设计多周期控制器的方法; 4、熟练掌握对多周期控制器的仿真实验验证和硬件测试两种调试方法; 5、掌握向MIPS-CPU顶层数据通路中增加控制单元的方法,并通过仿真验证和硬件测试两种方法对电路进行故障定位的调试技术。 二.实验内容 (1)MIPS—CPU控制器的有限状态机设计,根据MIPS—CPU 各种类型指令执行要求和有限状态机的设计原理,将多周期控制器的指令执行划分为多个状态,确定每一种指令的有限状态机,最后归纳为完整的多周期控制器有限状态机。通过Verilog HDL语言实现多周期控制器有限状态机。 (2)根据MIPS—CPU控制器的接口要求,在有限状态机的

基础上,用Verilog HDL实现完整的MIPS—CPU控制器的设计,并根据仿真波形,验证设计的正确性,并对出现的故障进行定位,修改程序,重新编译; (3)设计控制器的硬件下载测试方案。将编译通过的电路下载到实验台中。根据硬件调试结果验证设计的正确性,并对出现的故障进行定位,修改程序重新编译;最终完成控制器的硬件电路设计; (4)在MIPS—CPU指令系统的数据通路基础上,增加控制单元电路,并进行编译,仿真波形和调试。根据仿真波形,验证设计的正确性,并对出现的故障进行定位,修改程序,重新编译; (5)对增加了控制单元的顶层数据通路设计硬件下载测试方案。将编译通过的电路下载到实验台中。根据硬件调试结果验证设计的正确性,并对出现的故障进行定位,修改程序,重新编译;最终完成增加了控制单元的顶层数据通路设计。三.实验原理与步骤 1.把指令执行分成多个阶段,每个阶段在一个时钟周期内完成 (1).时钟周期以最复杂阶段所花时间为准 (2).尽量分成大致相等的若干阶段 (3).每个阶段内最多只能完成:1次访存或1次寄存器堆读/写或1次ALU

寄存器(register)

寄存器 Scope of register: 寄存器是CPU内部用来存放数据的一些小型存储区域,用来暂时存放参与运算的数据和运算结果。其实寄存器就是一种常用的时序逻辑电路,但这种时序逻辑电路只包含存储电路。寄存器的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1位二进制数,所以由N个锁存器或触发器可以构成N位寄存器。寄存器是中央处理器内的组成部份。寄存器是有限存贮容量的高速存贮部件,它们可用来暂存指令、数据和位址。在中央处理器的控制部件中,包含的寄存器有指令寄存器(IR)和程序计数器(PC)。在中央处理器的算术及逻辑部件中,包含的寄存器有累加器(ACC)。 1、寄存器- 特点及原理 寄存器又分为内部寄存器与外部寄存器,所谓内部寄存器,其实也是一些小的存储单元,也能存储数据。但同存储器相比,寄存器又有自己独有的特点: ①寄存器位于CPU内部,数量很少,仅十四个; ②寄存器所能存储的数据不一定是8bit,有一些寄存器可以存储16bit数据,对于386/486处理器中的一些寄存器则能存储32bit数据; ③每个内部寄存器都有一个名字,而没有类似存储器的地址编号。 寄存器的功能十分重要,CPU对存储器中的数据进行处理时,往往先把数据取到内部寄存器中,而后再作处理。外部寄存器是计算机中其它一些部件上用于暂存数据的寄存器,它与CPU之间通过“端口”交换数据,外部寄存器具有寄存器和内存储器双重特点。有些时候我们常把外部寄存器就称为“端口”,这种说法不太严格,但经常这样说。 外部寄存器虽然也用于存放数据,但是它保存的数据具有特殊的用途。某些寄存器中各个位的0、1状态反映了外部设备的工作状态或方式;还有一些寄存器中的各个位可对外部设备进行控制;也有一些端口作为CPU同外部设备交换数据的通路。所以说,端口是CPU和外设间的联系桥梁。CPU对端口(Ports)的访问也是依据端口的“编号”(地址),这一点又和访问存储器一样。不过考虑到机器所联接的外设数量并不多,所以在设计机器的时候仅安排了1024个端口

寄存器简单理解

GPIOB_BASE是一个地址,这个地址是GPIOB一系列寄存器的首地址,后面地址依次是GPIOB 的寄存器,将这个地址转换为结构体形式,并将后面寄存器按顺序定义在结构体里面,这样访问寄存器就可以通过引用结构体的形式了而不必书写寄存器的地址来访问寄存器。 寄存器用途: 1.可将寄存器内的数据执行算术及逻辑运算; 2.存于寄存器内的地址可用来指向内存的某个位置,即寻址; 3.可以用来读写数据到电脑的周边设备。 AX 累加器,得名原因是最初常使用ADD AX,n这样的指令 CX 计数器,得名原因是最常使用CX的值作为重复操作的次数 BX 常用作地址寄存器,如MOV AX,[BX],把BX所指地址中的数取到AX中去 DX 通用寄存器 所讲的寄存器都是以x86为基础的,那么这种CPU内,寄存器可分为以下几种: 1.EAX、EBX、ECX、EDX等通用寄存器——从通用上来讲,它所存储的东西,只要它的容积所容许的话,什么都是可以存储的; 2.CS、SS、ES等段寄存器——它所存储的只能是地址,它的作用是从寻址上可以体现出来; 3.EIP,也称为指令指针 4.EFLAGS寄存器,俗称为标志寄存器——所存储的是与CPU的每一个执行的指令有关。是关系到CPU每一个指令的执行相关内容与特殊的关联,即CPU所执行的指令是否违规,它的指令是否有进位,它的指令是否有溢出,都是在标志寄存器中能表现与表达出来; 5.浮点单元,这里面之所以只浮点单元,是因为在它里面还有一些小的寄存分类,主要是数学上的浮点上的计算 6.MMX指令使用的8个64位寄存器 7.单指令、多数据操作(SIMD,single-instruction,multiple-data)使用的8个128位XMM寄存器

杭电计组实验4-寄存器堆设计实验

杭州电子科技大学计算机学院 实验报告 实验项目: 课程名称:计算机组成原理与系统结构设计 姓名: 学号: 同组姓名: 学号 : 实 验 位 置 ( 机 号 ) : 实验日期: 指 导 教 师: 实验 内容 (算 法、 程 序、 步骤 和 方 法) 一、 实验目的 (1 )学会使用Verilog HDL 进行时序电路的设计方法。 (2)掌握灵活应用Verilog HDL 进行各种描述与建模的技巧和方法。 (3 )学习寄存器堆的数据传送与读 /写工作原理,掌握寄存器堆得设计方法。 二、 实验仪器 ISE 工具软件 三、 步骤、方法 (1) 启动Xilinx ISE 软件,选择File->New Project,输入工程名shiyan2,默认选择后,点 击Next 按钮,确认工程信息后点击 Finish 按钮,创建一个完整的工程。 (2) 在工程管理区的任意位置右击,选择 New Source 命令。弹出 New Source Wizard 对 话框, 选择Verilog Module,并输入Verilog 文件名,点击Next 按钮进入下一步, 点击Finish 完成创建。 (3) 编辑程序源代码,然后编译,综合;选择 Synthesize--XST 项中的Check Syntax 右击 选择 Run 命令,并查看RTL 视图;如果编译出错,则需要修改程序代码,直至正确。 (4) 在工程管理区将 View 类型设置成 Simulation ,在任意位置右击,选择 New Source 命 令,选择Verilog Test Fixture 选项。点击Next ,点击Finish ,完成。编写激励代码,观察仿 真波形,如果验证逻辑有误,则修改代码,重新编译,仿真,直至正确。 (5) 由于实验四并未链接实验板,所以后面的链接实验板的步骤此处没有。

msp430状态寄存器介绍概括

寄存器实在太多了。。我有个文档给你看看吧、、 MSP430寄存器中文注释---P1/2口(带中断功能) /************************************************************ * DIGITAL I/O Port1/2 寄存器定义有中断功能 ************************************************************/ #define P1IN_ 0x0020 /* P1 输入寄存器*/ const sfrb P1IN = P1IN_; #define P1OUT_ 0x0021 /* P1 输出寄存器*/ sfrb P1OUT = P1OUT_; #define P1DIR_ 0x0022 /* P1 方向选择寄存器*/ sfrb P1DIR = P1DIR_; #define P1IFG_ 0x0023 /* P1 中断标志寄存器*/ sfrb P1IFG = P1IFG_; #define P1IES_ 0x0024 /* P1 中断边沿选择寄存器*/ sfrb P1IES = P1IES_; #define P1IE_ 0x0025 /* P1 中断使能寄存器*/ sfrb P1IE = P1IE_; #define P1SEL_ 0x0026 /* P1 功能选择寄存器*/ sfrb P1SEL = P1SEL_; #define P2IN_ 0x0028 /* P2 输入寄存器*/ const sfrb P2IN = P2IN_; #define P2OUT_ 0x0029 /* P2 输出寄存器*/ sfrb P2OUT = P2OUT_; #define P2DIR_ 0x002A /* P2 方向选择寄存器*/ sfrb P2DIR = P2DIR_; #define P2IFG_ 0x002B /* P2 中断标志寄存器*/ sfrb P2IFG = P2IFG_; #define P2IES_ 0x002C /* P2 中断边沿选择寄存器*/ sfrb P2IES = P2IES_; #define P2IE_ 0x002D /* P2 中断使能寄存器*/ sfrb P2IE = P2IE_; #define P2SEL_ 0x002E /* P2 功能选择寄存器*/ sfrb P2SEL = P2SEL_; MSP430寄存器中文注释---P3/4口(无中断功能) /************************************************************ * DIGITAL I/O Port3/4寄存器定义无中断功能 ************************************************************/ #define P3IN_ 0x0018 /* P3 输入寄存器*/

实验六移位寄存器的设计

实验六移位寄存器的设计 一、实验目的 1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2、熟悉移位寄存器的应用—实现数据的串行、并行转换和构成环形计数器。 二、实验预习要求 1、复习有关寄存器及串行、并行转换器有关内容。 2、查阅CC40194、CC4011及CC4068 逻辑线路。熟悉其逻辑功能及引脚排列。 3、在对CC40194进行送数后,若要使输出端改成另外的数码,是否一定要使寄存器清零? 4、使寄存器清零,除采用R C输入低电平外,可否采用右移或左移的方法?可否使用并行送数法?若可行,如何进行操作? 5、若进行循环左移,图6-4接线应如何改接? 6、画出用两片CC40194构成的七位左移串 /并行转换器线路。 7、画出用两片CC40194构成的七位左移并 /串行转换器线路。 三、实验设备及器件 1、+5V直流电源 2、单次脉冲源 3、逻辑电平开关 4、逻辑电平显示器 5、CC40194×2(74LS194)CC4011(74LS00) CC4068(74LS30) 四、设计方法与参考资料 1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图6-1所示。 其中D0、D1、D2、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;S R为右移串行输 C为直接无条件清零端; 入端,S L为左移串行输入端;S1、S0为操作模式控制端;R

西工大2017年数字集成电路设计实验课实验一

实验四 译码器的设计及延迟估算 1、 设计译码器并估算延迟 设计一个用于16bit 寄存器堆的译码器,每一个寄存器有32bit 的宽度,每个bit 的寄存器单元形成的负载可以等效为3个单位化的晶体管(后面提到负载都为单位化后的负载)。 译码器的结构可参考典型的4-16译码器 译码器和寄存器堆的连接情况(Output 输出为1的一行寄存器被选中) ① 假定4个寄存器地址位的正反8个输入信号,每个信号的输入负载可以等效为10。确定 译码器的级数,并计算相关逻辑努力,以此来确定每一级中晶体管的尺寸(相当于多少个单位化的晶体管)及整个译码电路的延迟(以单位反相器的延迟的本征延迟Tp0为单位)。 解: 96332,10int =?==ext g C C C ,9.696/10F ==? 假定每一级的逻辑努力:G=1,又因为分支努力(每个信号连接8个与非门): 81*8*1B ==, 路径努力8.7686.91=??==GFB H 所以,使用最优锥形系数就可得到最佳的电路级数39.36.3ln 8.76ln 6.3ln ln ===H N ,故N 取3级。 因为逻辑努力:2121G =??=,路径努力:6.15386.92=??==GFB H 则使得路径延时最小的门努力 36.5)6.153(3/1===N H h 。 所以: . 36.5136.5,68.2236.5, 36.5136.5132211=========g h f g h f g h f

故第一级晶体管尺寸为7.68 1036.5=?; 第二级尺寸为956.1768.27.6=?; 第三级尺寸为96244.9636.5956.17≈=?。 故延迟为:0008.22)36.5136.5436.51(p p p t t t =+++++= ② 如果在四个寄存器地址输入的时候,只有正信号,反信号必须从正信号来获得。每个正信号的输入的等效负载为20,使用与①中同样的译码结构,在这种条件下确定晶体管的大小并评估延迟(以单位反相器的延迟的本征延迟Tp0为单位)。 解:因为输入时通过两级反相器,使这两个反相器分摊原来单个反相器的等效扇出,将两级反相器等效为一级,故其逻辑努力32.236.5h ==, 故36.5,68.2,32.2,32.24321====f f f f 所以: 第一级尺寸为:()9.2832.210=?; 第二级尺寸为:728.632.29.2=?; 第三级尺寸为:03.1868.2728.6=?; 第四级尺寸为:65.9636.503.18=? 正信号通路的延迟为:()0036.2236.5136.5436.5132.2132.2p p p t t t =++++++++= 反信号通路情况与上问相同,延迟为0008.22)36.5136.5436.51(p p p t t t =+++++= 2、 根据单位反相器(NMOS:W=0.5u L=0.5u PMOS:W=1.8u L=0.5u),设计出实 际电路,并仿真1题中第一问的路径延迟。 设计出实际电路如下:

计算机组成原理课程设计报告

序号: 学号: C H A N G Z H O U U N I V E R S I T Y 计算机组成原理 课程设计报告 题 目: 8位机微程序控制器模型计算机的设计与实现 学 生 姓 名: 学 号: 学 院(系): 专 业 班 级: 校内指导教师: 专业技术职务: 实 习 时 间: 年 月 日 年 月 日

计算机组成原理课程设计任务书

计算机科学与技术系指导教师

目录 1、课程设计的目的 (1) 2、课程设计的环境 (1) 3、课程设计的内容 (1) 3.1课程设计的原理 (1) 3.2课程设计机器指令 (3) 3.3微指令格式 (4) 3.4数据通路图 (6) 4、设计方案 (7) 4.1设计指令 (9) 4.2微程序流程图 (10) 4.3微指令二进制微代码表 (10) 5、验证与结果分析 (13) 5.1课设过程中所遇问题 (23) 5.2对应问题的解决 (23) 6、课程设计总结 (24) 6.1任务分工 (24) 6.2心得体会 (24) 参考文献 (26)

1、课程设计的目的 深入了解计算机各种指令的执行过程,以及控制器的组成,指令系统微程序设计的具体知识,进一步理解和掌握动态微程序设计的概念;完成微程序控制的特定功能计算机的指令系统设计和调试。 总体概括而言,分为两点:1、在掌握部件单元电路实验的基础上,进一步将其组成系统,构造一台基本模型计算机。2、为其定义两条以上的机器指令,并编写相应的微程序,上机调试,掌握整机概念。 2、课程设计的环境 硬件环境:TEC-9实验系统一台,排线若干,连接有关联的开关,使信号同步。 软件环境:HQFC-B1计算机组成原理软件,进行微程序的写入。 3、课程设计的内容 1、通过知识的综合运用,设计一台新的微程序控制器模型计算机。 2、选择合适的寻址方式,进行数据的提取。 3、确定你需要做的两条指令,并画出对应指令的流程图。 4、根据流程图,设计控制器代码。 5、根据控制器代码,在TEC-9实验系统上进行连线、调试,修改控制器代码。 6、最后,得出正确的控制器代码并完成实验报告、答辩,课程设计完成3.1课程设计的原理 TEC-9实验系统的组成:控制台、数据通路、控制器、时序电路、数字逻辑实验区、电源模块 时序发生器 时序发生器产生计算机模型所需的时序和数字逻辑实验所需的时钟。时序电路由一个500KHz晶振、2片GAL22V10组成。根据本机的设计,执行一条微程序指令需要4个节拍脉冲T1、T2、T3、T4,执行一条机器指令需要三个节拍电位W1、W2、W3,因此本机的基本时序如下:

UART寄存器介绍

UART寄存器介绍 UARTn_BR: UART波特率寄存器 UARTn_BR[15:0]: 由定时器的装入寄存器定时装入相应内容。 UARTn_CR.Run=0可以装入直到UARTn_CR.Run=1才写入无效 UARTn_TxBUFR:UART传输寄存器 UARTn_TxBUFR[8]: 传输数据第八位或者奇偶校验位或者唤醒位或者未定义的位有相应操作模式决定 1.如果是001模式则此位写0 2.如果是8+校验111模式则此位由UART自己处理写入软件操作无效 UARTn_TxBUFR[7]: 传输数据第七位或者奇偶校验位 1.如果是7+校验011模式同样此位由UART自己处理写入软件操作无效 UARTn_TxBUFR[6:0]:数据位 UARTn_RxBuffer: UART接收寄存器 RX[9]:桢错误标志1表示此桢有问题 RX[8]:接收数据位8,或者奇偶校验位或者唤醒位

RX[7]:接收数据位7,或者奇偶校验位 RX[6:0]:数据位 UARTn_CR:UART控制寄存器 CR[15-11]保留都是0 CR[10]FifoEnble队列模式0关闭表示TxFIFO认为是包含了16位数据才是满栈 1是开启表示TxFIFO认为当前就是才是满栈直接置TxFULL位 CR[9]SCENBLE 智能卡关闭还是开启不使用则置0 CR[8]RxEnble 接收功能关闭开启由下降沿来触发RXD脚初始化 CR[7]Run=0波特率无用=1则有用 CR[6]LoopBack=0标准的接收和发送模式=1是特殊模式。此位只由UART无效被改变 CR[5]ParityOdd选择奇偶校验=0则为偶校验=1为奇校验CR[43]StopBits 00 0.5停止位01是1个停止位10是1.5个11是2个 CR[2:0] MODE 5种模式 UARTn_IER UART的中断允许寄存器 15-9保留位为0 8 RxHalfFullIE 接收存储器超过8位则置

14、芯片与寄存器的介绍

理解芯片控制的原理 如果要说做单片机很难吗?其实并不难,用3句话就可以讲明白: 第1句话:芯片管脚不是输入,就是输出。 我们所有的程序,用单片机控制的产品,以及外设,无非就是控制芯片的各个管脚输入或者输出两个状态;例如,芯片发送数据就是输出;芯片驱动一个产品,也是输出;芯片接收数据就是输入;单片机对一个存储芯片写输入,可以理解为单片机与存储芯片连接的管脚输出状态,输出数据到存储芯片的管脚上,而存储芯片此时它的芯片对应管脚被配置成输入,将数据写入到芯片内部。 所以说,芯片管脚不是输入,就是输出,当然,如果你不使用这个管脚,也可以将它配置成某一种中间状态,免得干扰了外界,影响了PCB板上的其他元器件状态。 第2句话:芯片管脚不是高电平,就是低电平。 无论管脚是输入还是输出,它的目的是传输数据,传输信息,所以要么是高电平,要么低电平,通过010101这样的数据来传输它想传输的内容;这个就是所谓的二进制。 第3句话:传输协议。 什么是传输协议,比如与串口芯片通信,那么就要是串口协议的;如果是I2C 协议的EERPOM,那么就是I2C协议;还有其他一些比如485协议,CAN协议,USB协议,SD卡的SDIO协议…….等等数不胜数。 而这些协议,无非就是按照预先规定的表达方式进行通信,比如举个例子,我约定先连续发4个1,,然后再发4个0,就表示芯片A要开始发数据给芯片B 了,即芯片A通过它的芯片管脚发‘11110000’给到芯片B的时候,那么芯片B 就知道芯片A要给它真正的数据,它就要做好准备工作,准备好之后,芯片B 就会给芯片A一个回应,当芯片A收到芯片B的回应,就正式开始发数据。 这样通信双方之间的协商规定,就构成了协议,经过这么多年,就形成了我们所常见到的串口协议,CAN协议,USB协议(像USB协议又分为USB1.0协议,USB2.0协议,USB3.0协议,版本越高,速度就越快,协议进行优化后,通信效率也变高了)。 不知道大家理解了没有呢?所以总结下来,一个芯片最简单的外设莫过于 I/O口的高低电平控制,我们这里将详细讲解一下如何用一个I/O口去控制一个LED灯的亮灭。

设计示例2寄存器堆设计

设计示例2:寄存器堆设计 1、 功能概述: MIPS 指令格式中的寄存器号是5bits ,指令可以访问25=32个32位的寄存器。这样的一堆寄存器“堆在一起”构成一个寄存器堆(Register File )。模块框图如图1所示: Regfile 图1 模块框图 2、 结构框图: 3、 接口说明: 表1: 寄存器堆模块接口信号说明表 clk we wdata Valid Valid waddr rst_n 图2 寄存器堆写时序框图

4、设计电路源代码 //功能描述风格寄存器堆的设计 module regfile( input clk, input rst_n, //写端口 input we, //写使能 input[4:0] waddr, //写寄存器下标 input[31:0] wdata, //待写入寄存器堆的数据 //读端口1 input[4:0]raddr1, //读端口1寄存器下标 output[31:0] rdata1,//从端口1读出的寄存器堆的数据 //读端口2 input[4:0]raddr2, //读端口2寄存器下标 output[31:0] rdata2 //从端口2读出的寄存器堆的数据); reg[31:0] regs[0:31]; //32个32位寄存器堆 //Write operation always @ (posedge clk or negedge rst_n) begin if(!rst_n) begin:reset_all_registers //将32个寄存器复位为0. integer i; for(i=0;i<32;i=i+1) regs[i] = 32'd0; end else begin //写寄存器堆有效时,更新寄存器堆中某个寄存器的数据 if((we == 1'b1) && (waddr != 5'h0)) begin regs[waddr] <= wdata; end end end //Read port1 operation assign rdata1 = (raddr1 == 5'd0) ? 32'd0 : regs[raddr1]; //Read port2 operation assign rdata2 = (raddr2 == 5'd0) ? 32'd0 : regs[raddr2];

段寄存器的工作原理

一、段寄存器的产生 段寄存器的产生源于Intel 8086 CPU体系结构中数据总线与地址总线的宽度不一致。 数据总线的宽度,也即是ALU(算数逻辑单元)的宽度,平常说一个CPU是“16位”或者“32位”指的就是这个。8086CPU的数据总线是16位。 地址总线的宽度不一定要与ALU的宽度相同。因为ALU的宽度是固定的,它受限于当时的工艺水平,当时只能制造出16位的ALU;但地址总线不一样,它可以设计得更宽。地址总线的宽度如果与ALU相同当然是不错的办法,这样CPU的结构比较均衡,寻址可以在单个指令周期内完成,效率最高;而且从软件的解决来看,一个变量地址的长度可以用整型或者长整型来表示会比较方便。 但是,地址总线的宽度还要受制于需求,因为地址总线的宽度决定了系统可寻址的范围,即可以支持多少内存。如果地址总线太窄的话,可寻址范围会很小。如果地址总线设计为16位的话,可寻址空间是2^16=64KB,这在当时被认为是不够的;Intel最终决定要让8086的地址空间为1M,也就是20位地址总线。 地址总线宽度大于数据总线会带来一些麻烦,ALU无法在单个指令周期里完成对地址数据的运算。有一些容易想到的可行的办法,比如定义一个新的寄存器专门用于存放地址的高4位,但这样增加了计算的复杂性,程序员要增加成倍的汇编代码来操作地址数据而且无法保持兼容性。 Intel想到了一个折中的办法:把内存分段,并设计了4个段寄存器,CS,DS,ES和SS,分别用于指令、数据、其它和堆栈。把内存分为很多段,每一段有一个段基址,当然段基址也是一个20位的内存地址。不过段寄存器仍然是16位的,它的内容代表了段基址的高16位,这个16位的地址后面再加上4个0就构成20位的段基址。而原来的16位地址只是段内的偏移量。这样,一个完整的物理内存地址就由两部分组成,高16位的段基址和低16位的段内偏移量,当然它们有12位是重叠的,它们两部分相加在一起,才构成完整的物理地址。 Base b15 ~ b12 b11 ~ b0 Offset o15 ~ o4 o3 ~ o0 Address a19 ~ a0 这种寻址模式也就是“实地址模式”。在8086中,段寄存器还只是一个单纯的16位寄存器,而且操作寄存器的指令也不是特权指令。通过设置段寄存器和段内偏移,程序就可以访问整个

AD9833详细原理解析(附内部寄存器说明)

基于AD9833的高精度可编程波形发生器系统设计 来源:国外电子元器件 1 引言 频率合成器在通信、雷达和导航等设备中既是发射机的激励信号源,又是接收机的本地振荡器;在电子对抗设备中可作为干扰信号发生器;在测试设备中则作为标准信号源。因此频率合成器被称为许多电子系统的“心脏”。而设计高精度,易于操作的频率合成器则是核心,因此,这里提出了一种基于DDS AD9833的高精度波形发生器系统解决方案。用户可直接编辑设置所需的波形频率和峰峰值等信息,利用串口将配置信息发送到电路板,实时控制波形。该系统设计已成功应用于某型雷达测速仪测试设备。 2 AD9833简介 AD9833是ADI公司的一款低功耗、DDS器件,能够输出正弦波、三角波、方波。AD9833无需外接元件,输出频率和相位可通过软件编程设置,易于调节。其频率寄存器为28位,主频时钟为25 MHz时,其精度为0.1 Hz;主频时钟为l MHz时.精度可达0.004 Hzt2。 AD9833内部有5个可编程寄存器:1个16位控制寄存器,用于设置器件_T 作模式;2个28位频率寄存器和2个12位相位寄存器,分别用于设置器件输出正弦波的频率和相位。AD9833有3根串行接口线,可与SPI,QSPI,MICRO-WIRE 和DSP接口标准相兼容。在串口时钟SCLK的作用下,数据是以16位方式加载至设备。 AD9833的内部电路主要有数控振荡器(NCO)、频率和相位调节器、SineROM、D/A转换器、电压调整器。AD9833的核心是28位的相位累加器,它由加法器和相位寄存器组成,而相位寄存器是按每个时钟增加步长,相位寄存器的输出与相位控制字相加后输入到正弦查询表地址中。正弦查询表包含1个周期正弦波的数字幅值信息,每个地址对应正弦波中O。~360°内的1个相位点。查询表把输入的地址相位信息映射成正弦波幅值的数字量信号,驱动D/A转换器输出模拟量。 输出正弦波频率为: 式中:FREQREG为频率控制字,由频率寄存器FREQOREG或FREQlREG的值给定,其范围为0≤M<228一1。fMCLK为参考时钟频率。 输出正弦波的相位为2π/4 096xPHASEREG,其中PHASEREG是所选相位寄存器的值。输出正弦波的峰峰值固定.约600 mV,且正弦波不是标准正弦波,即波谷是0 V,而不是负电压。因此,输出正弦波为: 式中:K约600 mV,与器件内部参考电压有关。

单周期CPU设计参考

单周期CPU及其Verilog HDL设计 一、指令的设计 MIPS32的指令的三种格式的参考: R类型: I类型: J类型: R类型指令的op为0,具体操作由func指定。rs和rt是源寄存器号,rd是目的寄存器号。只有移位指令使用sa来指定移位位数。I类型指令的低16位是立即数,计算时要把它扩展到32位。依指令的不同,有零扩展和符号扩展两种。J类型指令右边26位是字地址,用于产生跳转的目标地址。具体的指令格式和内容请参考MIPS32。 设计报告中需自行设计所有指令的二进制格式和对应的汇编指令格式。 二、单周期CPU的设计 我们把时钟的电平从低到高变化的瞬间称为时钟上升沿,两个相邻时钟上升沿之间的时间间隔称为一个时钟周期。单周期CPU指的是一条指令的执行在一个这样的时钟周期内完成,然后开始下一条指令的执行,即一条指令用一个周期。 2.1执行一条指令所需的硬件电路 我们的目的地是要设计CPU的硬件电路,使其能够从存储器中读出一条条指令并执行指令所描述的操作。从存储器中读取指令的动作一般与指令本身的意义无关,可以以同样的方法把指令从存储器中取出。而执行指令则与指令本身的意义密切相关,因此最重要是首先搞清楚CPU要执行的每条指令的意义。下面以两种类型的电路来举例。 2.1.1与取指令有关的电路

指令存储在存储器中。CPU取指令时把程序计数器(PC)中的内容作为存储器的地址,根据它来访问存储器,从PC值指定的存储单元中取来一条32位指令。如果取来的指令执行时没有引起转移,PC的值要加4;如果转移,要把转移的目标地址写入PC,以便在下一个时钟周期取出下一条指令。 图2.1 取指令时用到的硬件电路和指令寄存器 如图2.1所示,PC是一个简单的32位寄存器,由32个D触发器构成。指令存储器(Inst Mem)的输入端a是地址、输出端do是数据输出,即指令。图中的加法器专供PC+4使用,它的输出接到多路器的一个输入端。如果取来的指令没有引起转移或跳转,则选择PC+4,在时钟上升沿处将其打入PC;若引起转移或跳转,则用多路器选择下一条指令该打入的PC值。 2.1.2寄存器计算类型指令执行时所需电路 寄存器类型的指令有add等。如图2.2所示是执行它们所需的部分硬件电路。大多数MIPS指令属于三操作数指令。指令格式中的rs和rt是两个5位的寄存器号,由它们从寄存器堆(Regfile)中读出两个32位的数据。由于寄存器号有5位,所以能从32个寄存器中选出一个。32个寄存器合在一起称为寄存器堆(Register File)。从寄存器堆读出的两个32位数据分别被送到ALU的a和b的输入端。 图2.2 执行寄存器计算类型指令所需电路 具体的计算由ALU完成。ALU的计算控制码aluc由控制部件(Control Unit)产生。这里的控制部件是简单的组合电路,输入信号是指令的操作码op和功能码func,输出信号3个,它们分别是ALU的操作码aluc、计算结果是否写入寄存器堆的控制信号wreg和下一条指令的地址选择信号pcsource。ALU的计算结

寄存器组的设计与实现

实验三寄存器组的设计与实现 一、实验目的 1. 学习掌握Quartus II 的图形编辑、编译、仿真的设计流程; 2. 学习74670三态输出寄存器堆的使用; 3. 理解寄存器组的工作原理和过程,设计出4个16位寄存器组并对设计的正确性进行验证 二、实验任务及要求 1. 设计出功能完善的寄存器组,并对设计的正确性进行验证。具体要求如下: (1) 用图形方式设计出寄存器组的电路原理图。 (2) 测试波形要用时序仿真实现,先将不同的数据连续写入4个寄存器后,再分别读出。 (3) 将设计文件封装成器件符号。 (4) 数据的宽度最好为16位。 三、实验装置 安装有Quartus II软件的PC机1台 四、设计思想 运用具有三态功能的芯片74670进行设计,74670为4*4(4个4位寄存器)的寄存器堆,使用四片74670并联,同时对4 片74670 芯片进行读写操作控制,从而实现4个16位数据的存储与输出。 五、逻辑电路图

74670芯片图:三态输出的4*4寄存器堆 六、实验结果: 见原理图,波形图以及元件封装图。 1.原理图分析:见设计思想

2.波形图分析: 当RE为1,WE不为1时,实现输入功能,WB,WA控制数据输入到哪个寄存器组当RE为1,WE为1时,出现高阻状态,此时既不输入也不输出 当WE为1,RE不为1时,实现输出功能,RB,RA控制哪个寄存器组的数据输出 3.封装元件的功能说明: d[15..0]16位输入数据 q[15..0]16位输出数据 gwn:写入数据使能控制端,低有效 wa,wb:选择控制端,四种组合控制16位数输入到相应四种寄存器组 grn:读出数据使能控制端,低有效 ra,rb:选择控制端,四种组合控制从四种寄存器组读出相应16位数

寄存器组的设计与实现预习

寄存器组的设计与实现

一、实验目的 1、学习掌握Quartus||软件的基本操作; 2、理解寄存器组的工作原理和过程; 2、设计出寄存器组并对设计的正确性进行验证。 二、实验内容 1、设计出功能完善的寄存器数组并对设计的正确性进行验证。 (1)用图形方式设计出寄存器的电路原理图; (2)测试波形时用时序仿真实现,先将不同的数据连续写入4个寄存器后,再分别读出;(3)将设计文件封装成器件符号; (4)数据宽度最好为16位。 三、实验设计 1、集成电路芯片 (1)74760:三态输出4*4寄存器堆 74760提供了4个4位寄存器。在功能上可对这4个寄存器分别进行写操作和读操作。在寄存器写操作时,通过WB、WA两个寄存器选择端的组合00、01、10、11选择寄存器。通过GWN写控制端进行三态控制,GWN为低电平时将数据写入端数据D4D3D2D1写入该寄存器。在寄存器读操作时,通过RB、RA两个寄存器选择端的组合00、01、10、11选择寄存器,通过GRN读控制端进行三态控制,在GRN为低电平时,将所选寄存器数据通过Q4Q3Q2Q1进行输出。 “写”功能表

“读”功能表 2、设计原理 要设计16位的存储器组,需要74670芯片4片,在寄存器组工作时,同时对4片74670芯片进行操作,封装后即可作为包含有4个16位寄存器的寄存器组在主机系统中调用。 四、实验结果 1、原理图

寄存器组由4个74670组成,将4个芯片的GWN、WA、WB、GRN、RA、RB 分别连在一起,共同控制4个芯片的读写操作。总共有22个输入端。即 IN[15]、IN[14]....IN[1]、IN[0]和GWN、WA、WB、GRN、RA、RB。16个输出 端。即OUT[15]、OUT[14]...OUT[1]、OUT[0]。

ARM寄存器简介

ARM寄存器简介 ARM处理器含有37个寄存器,这些寄存器包括以下两类寄存器。 (1)31个通用寄存器:包括程序计数器PC等,这些寄存器都是32位寄存器。 (2)6个状态寄存器:状态寄存器也是32位的寄存器,但是只使用了其中的12位。 1.通用寄存器 在ARM处理器的7种模式下都有一组对应的寄存器组。在任意时刻,可见的寄存器组包括15个通用寄存器R0~R14、一个或两个状态寄存器和PC。在所有的寄存器中,有些是各种模式下共用的同一个物理寄存器,有些是各种模式自己独立拥有的物理寄存器。详细如表1-3所示。 表1-3 ARM物理寄存器 用户模式系统模 式特权模式中止模式未定义指令 模 外部中断模快速中断模 R0 R0 R0 R0 R0 R0 R0 R1 R1 R1 R1 R1 R1 R1 R2 R2 R2 R2 R2 R2 R2 R3 R3 R3 R3 R3 R3 R3 R4 R4 R4 R4 R4 R4 R4 R5 R5 R5 R5 R5 R5 R5 R6 R6 R6 R6 R6 R6 R6 R7 R7 R7 R7 R7 R7 R7 R8 R8 R8 R8 R8 R8 R8_fiq R9 R9 R9 R9 R9 R9 R9_fiq R10 R10 R10 R10 R10 R10 R10_fiq R11 R11 R11 R11 R11 R11 R11_fiq R12 R12 R12 R12 R12 R12 R12_fiq R13 R13 R13_svc R13_abt R13_und R13_irq R13_fiq R14 R14 R14_svc R14_abt R14_und R14_irq R14_fiq PC PC PC PC PC PC PC CPSR CPSR CPSR CPSR CPSR CPSR CPSR SPSR_svc S PSR_abt SPSR_und SPSR_irq SPSR_fiq 通用寄存器通常又可以分为下面3类。 n 未备份寄存器:包括R0~R7。 n 备份寄存器:包括R8~R14。