FT功能详解与测试

一、什么是FT功能

Vmware fault tolerance(FT)功能创建一个虚拟机设置可以提供连续性能力。FT建立在ESX/ESXi主机平台。通过创建一个虚拟机一个完全相同的副本。

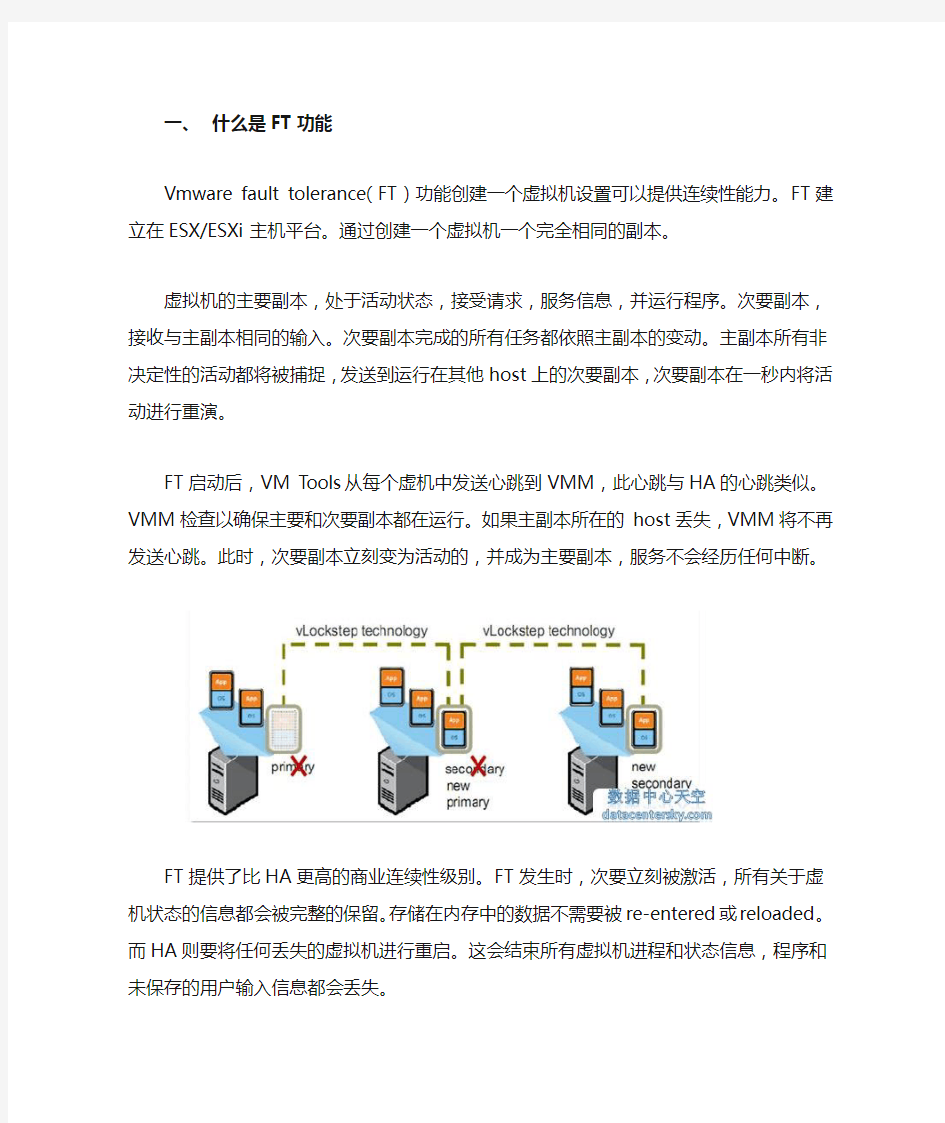

虚拟机的主要副本,处于活动状态,接受请求,服务信息,并运行程序。次要副本,接收与主副本相同的输入。次要副本完成的所有任务都依照主副本的变动。主副本所有非决定性的活动都将被捕捉,发送到运行在其他host 上的次要副本,次要副本在一秒内将活动进行重演。

FT启动后,VM Tools从每个虚机中发送心跳到VMM,此心跳与HA的心跳类似。VMM检查以确保主要和次要副本都在运行。如果主副本所在的host丢失,VMM将不再发送心跳。此时,次要副本立刻变为活动的,并成为主要副本,服务不会经历任何中断。

FT提供了比HA更高的商业连续性级别。FT发生时,次要立刻被激活,所有关于虚机状态的信息都会被完整的保留。存储在内存中的数据不需要被

re-entered或reloaded。而HA则要将任何丢失的虚拟机进行重启。这会结束所有虚拟机进程和状态信息,程序和未保存的用户输入信息都会丢失。

二、VMware FT 容错的工作方式

VMware 容错可通过创建和维护等同于主虚拟机并可在发生故障切换时替换主虚拟机的辅助虚拟机来为虚拟机提供连续可用性。

可以为大多数任务关键虚拟机启用容错。并会创建一个重复虚拟机(称为辅助虚拟机),该虚拟机会以虚拟锁步方式随主虚拟机一起运行。VMware vLockstep 可捕获主虚拟机上发生的输入和事件,并将这些输入和事件发送到正在另一主机上运行的辅助虚拟机。使用此信息,辅助虚拟机的执行将等同于主虚拟机的执行。因为辅助虚拟机与主虚拟机一起以虚拟锁步方式运行,所以它可以无中断地接管任何点处的执行,从而提供容错保护。

虚拟机和辅助虚拟机可持续交换检测信号。这使得虚拟机对中的虚拟机能够监控彼此的状态以确保持续提供容错保护。如果运行主虚拟机的主机发生故障,系统将会执行透明故障切换,此时会立即启用辅助虚拟机以替换主虚拟机,并将启动新的辅助虚拟机,同时在几秒钟内重新建立容错冗余。如果运行辅助虚拟机的主机发生故障,则该主机也会立即被替换。在任一情况下,用户都不会遭遇服务中断和数据丢失的情况。

容错虚拟机及其辅助副本不允许在相同主机上运行。容错功能使用反关联性规则,这些规则可确保容错虚拟机的两个实例永远不会在同一主机上。这可确保主机故障无法导致两个虚拟机都缺失

容错可避免“裂脑”情况的发生,此情况可能会导致虚拟机在从故障中恢复后存在两个活动副本。共享存储器上锁定的原子文件用于协调故障切换,以便只有一端可作为主虚拟机继续运行,并由系统自动重新生成新辅助虚拟机。

三、VMware FT 容错提供连续可用性

VMware HA 通过在主机出现故障时重新启动虚拟机来为虚拟机提供基本级别的保护。VMware 容错可提供更高级别的可用性,允许用户对任何虚拟机进行保护以防止主机发生数据、事务或连接丢失等故障。

容错使用 ESX/ESXi 主机平台上的VMware vLockstep 技术以提供连续可用性。通过确保主虚拟机和辅助虚拟机的状态在虚拟机的指令执行的任何时间点均相同来完成此过程。vLockstep 通过使主虚拟机和辅助虚拟机执行相同顺序的x86 指令来完成此过程。主虚拟机捕获所有输入和事件—从处理器到虚拟I/O 设备—并在辅助虚拟机上进行重放。辅助虚拟机执行与主虚拟机同一系列的指令,而仅可看到单个虚拟机映像(主虚拟机)在执行工作负载。

如果运行主虚拟机的主机或运行辅助虚拟机的主机发生故障,则会发生透明故障切换,仍在无缝工作的主机将借此变为主虚拟机的主机。使用透明故障切换,不会有数据损失,并且可以维护网络连接。在发生透明故障切换之后,将自动重新生成新的辅助虚拟机,并将重新建立冗余。整个过程是透明且全自动的,并且即使 vCenter Server 不可用,也会发生。

四、VMware FT 容错与HA协作, FT容错的要求

与VMware HA 在默认情况下保护群集内的每个虚拟机不同,VMware 容错在单个虚拟机上启用。要使群集支持VMware 容错,必须满足以下必备条件:群集/主机必备条件

虚拟机要求

在可以打开容错前,虚拟机必须满足最低要求。

1.虚拟机文件必须存储在共享存储器上。可接受共享的存储解决方案包括光

纤通道、(硬件和软件)iSCSI、NFS 和NAS。

2.虚拟机必须存储在虚拟RDM 或厚置备的虚拟机磁盘(VMDK) 文件

(已启用“群集功能”选项)中。如果将虚拟机存储在精简置备或厚置备的 VMDK 文件(未启用群集功能)中,则在尝试启用容错时将会出现一则指示必须转换 VMDK 文件的消息。用户可以接受此自动转换(需要关

闭虚拟机),允许转换磁盘并使用容错保护虚拟机。此转换过程所需的时

间根据磁盘的大小和主机处理器类型而有所不同。

3.虚拟机必须在一个受支持的客户机操作系统上运行。

五、容错与vSphere 其他功能兼容

容错虚拟机不支持以下vSphere 功能。

1.快照在虚拟机上启用容错前,必须移除或提交快照。此外,不可能对已

启用容错的虚拟机执行快照。

2.Storage VMotion 不能为已启用容错的虚拟机调用Storage VMotion。

要迁移存储器,应当先暂时关闭容错,然后再执行Storage VMotion 操

作。在完成迁移之后,可以重新打开容错。

3.DRS 功能容错虚拟机会自动配置为禁用DRS。DRS 最初将放置一个辅

助虚拟机,但在对群集进行负载平衡时,DRS 不会提出建议,也不会对

主虚拟机或辅助虚拟机进行负载平衡。主虚拟机和辅助虚拟机在正常运行

期间可以进行手动迁移。

4.不与容错兼容的其他功能

六、VMware FT 容错测试

打开两个VM的concole,一个完全是另外一个镜像,且为read-only,是不接受任何输入的:

FT虚拟机开关机测试:

所谓镜像就是不管是在console选择还是在vCenter操作,主次VM都会同时开关机

虚拟机系统崩溃测试:

运行一个程序,人为将主VM蓝屏,发现此时次VM同时蓝屏,再一次证明两边运行的指令是同步的。

重启host测试:

重主VM所在的host,次VM立即接管工作,从ping的相应来看,应该是零宕机时间:

总结:

1.只支持1个虚拟CPU

2.需要启用FT的虚拟机,其虚拟磁盘格式必须从原来的THIN DISK或者

ZEROED THICK DISK 方式转化成EAGER ZEROED THICK DISK 磁盘

格式,这个转化过程会占用大量的时间,因为这这个转化的过程和安全擦

除操作类似,需要涉及对虚拟磁盘中每个扇区做清零操作。

3.只能防止Host级别的物理故障或任何导致主VM所在host丢失的情况。

晶圆封装测试工序和半导体制造工艺流程

A.晶圆封装测试工序 一、 IC检测 1. 缺陷检查Defect Inspection 2. DR-SEM(Defect Review Scanning Electron Microscopy) 用来检测出晶圆上是否有瑕疵,主要是微尘粒子、刮痕、残留物等问题。此外,对已印有电路图案的图案晶圆成品而言,则需要进行深次微米范围之瑕疵检测。一般来说,图案晶圆检测系统系以白光或雷射光来照射晶圆表面。再由一或多组侦测器接收自晶圆表面绕射出来的光线,并将该影像交由高功能软件进行底层图案消除,以辨识并发现瑕疵。 3. CD-SEM(Critical Dimensioin Measurement) 对蚀刻后的图案作精确的尺寸检测。 二、 IC封装 1. 构装(Packaging) IC构装依使用材料可分为陶瓷(ceramic)及塑胶(plastic)两种,而目前商业应用上则以塑胶构装为主。以塑胶构装中打线接合为例,其步骤依序为晶片切割(die saw)、黏晶(die mount / die bond)、焊线(wire bond)、封胶(mold)、剪切/成形(trim / form)、印字(mark)、电镀(plating)及检验(inspection)等。 (1) 晶片切割(die saw) 晶片切割之目的为将前制程加工完成之晶圆上一颗颗之晶粒(die)切割分离。举例来说:以0.2微米制程技术生产,每片八寸晶圆上可制作近六百颗以上的64M微量。 欲进行晶片切割,首先必须进行晶圆黏片,而后再送至晶片切割机上进行切割。切割完后之晶粒井然有序排列于胶带上,而框架的支撐避免了胶带的皱褶与晶粒之相互碰撞。 (2) 黏晶(die mount / die bond) 黏晶之目的乃将一颗颗之晶粒置于导线架上并以银胶(epoxy)粘着固定。黏晶完成后之导线架则经由传输设备送至弹匣(magazine)内,以送至下一制程进行焊线。 (3) 焊线(wire bond) IC构装制程(Packaging)则是利用塑胶或陶瓷包装晶粒与配线以成集成电路(Integrated Circuit;简称IC),此制程的目的是为了制造出所生产的电路的保护层,避免电路受到机械性刮伤或是高温破坏。最后整个集成电路的周围会向外拉出脚架(Pin),称之为打线,作为与外界电路板连接之用。

手机基本功能测试方式

手机基本功能测试 手机基本测试软件测试 关于手机软件测试的工具应用 手机软件测试是否也和以下联系起来: 漫谈人机界面测试 【正文】本文列数了软件黑盒测试过程中,在被测试软件中可能存在的常见软件问题。本文不会详细讨论基本的软件测试思想与常用技术,仅针对在软件黑盒测试过程中若干的问题做描述,并提供个人的参考测试意见与防范意见,希望可以为初学者提供些许帮助。 俗话说“人靠衣裳马靠鞍”,良好的外观往往能够吸引眼球,激发顾客(用户)的购买欲望,最终达成商业利益的实现。软件的设计亦如此,Window XP 在商业上的巨大成功很大一方面来自于它一改往日呆板,以突出“应用”的灰色界面,从“用户体验”角度来设计界面,使界面具有较大的亲和力。就目前的软件设计的发展趋势来说,良好的人机界面设计越来越受到系统分析、设计人员的重视。但是如何对设计的人机界面(包括帮助等)进行测试,给出客观、公正的评价,却鲜见于报端。本文试从共性分析和个性分析的角度,给出一些测试意见和原则,简单且易于上手。起到一个抛砖引玉的目的、以飨读者。 我们知道:“不立规矩无以成方圆”。在软件界面设计强调张扬个性的同时,我们不能忘记软件界面的设计先要讲求规矩-简洁、一致、易用,这是一切软件界面设计和测试的必循之道,是软件人机界面在突出自我时的群体定位。美观、规整的软件人机界面破除新用户

对软件的生疏感,使老用户更易于上手、充分重用已有使用经验,并尽量少犯错误。由此我们在对软件人机界面进行测试时(设计评审阶段和系统测试阶段结合进行),不妨从下列一些角度测试软件的人机界面。 一致性测试 一致性使软件人机界面的一个基本要求。目的是使用户在使用时,很快熟悉软件的操作环境,同时避免对相关软件操作发生理解歧义。这要求我们在进行测试时,需要判断软件的人机界面是否可以作为一个整体而存在。下面是进行一致性测试的一些参考意见:――提示的格式是否一致 ――菜单的格式是否一致 ――帮助的格式是否一致 ――提示、菜单、帮助中的术语是否一致 ――各个控件之间的对齐方式是否一致 ――输入界面和输出界面在外观、布局、交互方式上是否一致 ――命令语言的语法是否一致 ――功能类似的相关界面是否在在外观、布局、交互方式上是否一致(比如商品代码检索和商品名称检索) ――存在同一产品族的时候,是否与其他产品在外观、布局、交互方式上是否一致(例:Office产品族)

【半导体研磨 精】半导体晶圆的生产工艺流程介绍

?从大的方面来讲,晶圆生产包括晶棒制造和晶片制造两大步骤,它又可细分为以下几道主要工序(其中晶棒制造只包括下面的第一道工序,其余的全部属晶片制造,所以有时又统称它们为晶柱切片后处理工序): 晶棒成长--> 晶棒裁切与检测--> 外径研磨--> 切片--> 圆边--> 表层研磨--> 蚀刻--> 去疵--> 抛光--> 清洗--> 检验--> 包装 1 晶棒成长工序:它又可细分为: 1)融化(Melt Down) 将块状的高纯度复晶硅置于石英坩锅内,加热到其熔点1420°C以上,使其完全融化。 2)颈部成长(Neck Growth) 待硅融浆的温度稳定之后,将〈1.0.0〉方向的晶种慢慢插入其中,接着将晶种慢慢往上提升,使其直径缩小到一定尺寸(一般约6mm左右),维持此直径并拉长 100-200mm,以消除晶种内的晶粒排列取向差异。 3)晶冠成长(Crown Growth) 颈部成长完成后,慢慢降低提升速度和温度,使颈部直径逐渐加大到所需尺寸(如 5、6、8、12吋等)。 4)晶体成长(Body Growth) 不断调整提升速度和融炼温度,维持固定的晶棒直径,只到晶棒长度达到预定值。 5)尾部成长(Tail Growth) 1

当晶棒长度达到预定值后再逐渐加快提升速度并提高融炼温度,使晶棒直径逐渐变小,以避免因热应力造成排差和滑移等现象产生,最终使晶棒与液面完全分离。到此即得到一根完整的晶棒。 2 晶棒裁切与检测(Cutting & Inspection) 将长成的晶棒去掉直径偏小的头、尾部分,并对尺寸进行检测,以决定下步加工的工艺参数。 3 外径研磨(Su rf ace Grinding & Shaping) 由于在晶棒成长过程中,其外径尺寸和圆度均有一定偏差,其外园柱面也凹凸不平,所以必须对外径进行修整、研磨,使其尺寸、形状误差均小于允许偏差。 4 切片(Wire Saw Sl ic ing) 由于硅的硬度非常大,所以在本工序里,采用环状、其内径边缘镶嵌有钻石颗粒的薄片锯片将晶棒切割成一片片薄片。 5 圆边(Edge Profiling) 由于刚切下来的晶片外边缘很锋利,硅单晶又是脆性材料,为避免边角崩裂影响晶片强度、破坏晶片表面光洁和对后工序带来污染颗粒,必须用专用的电脑控制设备自动修整晶片边缘形状和外径尺寸。 ? 6 研磨(Lapping) 研磨的目的在于去掉切割时在晶片表面产生的锯痕和破损,使晶片表面达到所要求的光洁度。 7 蚀刻(Etching) 1

史上最全的手机硬件测试用例

XXX手机硬件测试列表 1.1.1 LCD测试 1.数量:2pcs以上; 2.测试方法及内容:手机正常开机后,距离30cm,与水平成45o角并在各个方向15o范围内观察LCD工作是否正常。 a. LCD显示是否正常,是否存在斑点、阴影等; b.彩屏LCD各种颜色能否正常显示,分辨率、色素、响应时间等性能指标是否符合要求; c.分别在暗室、荧光(约750Lux)和阳光(大于3500Lux)下测试LCD显示是否正常,各性能指标是否符合要求; d.将电源设置成高(4.2v)、中(3.8v)、低(3.5v)不同电压,LCD显示是否有差异或异常。 3.预期结果: a. LCD显示正常,不存在斑点、阴影等; b.彩屏LCD各种颜色正常显示,分辨率、色素、响应时间等性能指标符合要求(结合项目的具体指标规定); c.在暗室、荧光(约750Lux)和阳光(大于3500Lux)下测试LCD显示均应正常,各项性能符合项目的具体指标要求; d.在高、中、低不同电压下,LCD显示应正常且基本一致。 1.1.2 LCD背光及键盘背光测试 1.数量:2pcs以上; 2.测试方法及内容:手机正常开机后,选择进入手机功能菜单中的相应设置进行测试。 a.测试手机背光及LED能够正常工作; b.分别在暗室、荧光(约750Lux)和阳光(约2000Lux)下测试LED亮度是否正常; c.背光亮度是否符合要求,测试在不同电池电压情况下,背灯的亮度是否具有一致性; d. LED是否能够按照要求打开和关闭。 3.预期结果: a.手机背光及LED工作正常; b.在暗室、荧光(约750Lux)和阳光(约2000Lux)下,LED亮度均应正常; c.背光亮度应符合要求且在不同电池电压情况下,背灯亮度基本一致; d. LED能够按照要求打开和关闭,且亮度正常。 1.1.3 TP触摸屏承重能力测试 4.数量:5pcs以上; 5.测试方法及内容:重压头25kg,静压30秒之后,等待30秒,再重新放置重压头。 6.预期结果: a. 200次重压后样品不出现牛顿环,则为良品; 1.1.4 Camera测试 1.数量:4pcs以上; 2.测试方法及内容:手机正常开机后,选择手机功能菜单进入拍照状态,对标准测试板进行拍照。 a. Camera是否能够正常工作; b. 拍摄的照片效果是否符合规范要求; c. 用标准色板照片色块的对比测试; d. 测试Digital Camera的反应时间; e. 开启闪光灯功能,看闪光灯是否正常工作。 3.预期结果: a. Camera工作正常,能正常开启与关闭; b.照片效果符合规范要求,参考Camera Spec; c.反应时间达到规范要求;

半导体制造工艺流程

半导体制造工艺流程 N型硅:掺入V族元素--磷P、砷As、锑Sb P型硅:掺入III族元素—镓Ga、硼B PN结: 半导体元件制造过程可分为 前段(FrontEnd)制程 晶圆处理制程(WaferFabrication;简称WaferFab)、 晶圆针测制程(WaferProbe); 後段(BackEnd) 构装(Packaging)、 测试制程(InitialTestandFinalTest) 一、晶圆处理制程 晶圆处理制程之主要工作为在矽晶圆上制作电路与电子元件(如电晶体、电容体、逻辑闸等),为上述各制程中所需技术最复杂且资金投入最多的过程,以微处理器(Microprocessor)为例,其所需处理步骤可达数百道,而其所需加工机台先进且昂贵,动辄数千万一台,其所需制造环境为为一温度、湿度与含尘(Particle)均需控制的无尘室(Clean-Room),虽然详细的处理程序是随著产品种类与所使用的技术有关;不过其基本处理步骤通常是晶圆先经过适当的清洗(Cleaning)之後,接著进行氧化(Oxidation)及沈积,最後进行微影、蚀刻及离子植入等反覆步骤,以完成晶圆上电路的加工与制作。 二、晶圆针测制程 经过WaferFab之制程後,晶圆上即形成一格格的小格,我们称之为晶方或是晶粒(Die),在一般情形下,同一片晶圆上皆制作相同的晶片,但是也有可能在同一片晶圆上制作不同规格的产品;这些晶圆必须通过晶片允收测试,晶粒将会一一经过针测(Probe)仪器以测试其电气特性,而不合格的的晶粒将会被标上记号(InkDot),此程序即称之为晶圆针测制程(WaferProbe)。然後晶圆将依晶粒为单位分割成一粒粒独立的晶粒 三、IC构装制程 IC構裝製程(Packaging):利用塑膠或陶瓷包裝晶粒與配線以成積體電路目的:是為了製造出所生產的電路的保護層,避免電路受到機械性刮傷或是高溫破壞。 半导体制造工艺分类 半导体制造工艺分类 一双极型IC的基本制造工艺: A在元器件间要做电隔离区(PN结隔离、全介质隔离及PN结介质混合隔离)ECL(不掺金)(非饱和型)、TTL/DTL(饱和型)、STTL(饱和型)B在元器件间自然隔离 I2L(饱和型) 半导体制造工艺分类 二MOSIC的基本制造工艺: 根据栅工艺分类 A铝栅工艺 B硅栅工艺

晶圆封装测试工序和半导体制造工艺流程0001

盛年不重来,一日难再晨。及时宜自勉,岁月不待人 盛年不重来,一日难再晨。及时宜自勉,岁月不待人 A.晶圆封装测试工序 一、IC检测 1. 缺陷检查Defect Inspection 2. DR-SEM(Defect Review Scanning Electro n Microscopy) 用来检测出晶圆上是否有瑕疵,主要是微尘粒子、刮痕、残留物等问题。此外,对已印有电路图案的图案晶圆成品而言,则需要进行深次微米范围之瑕疵检测。一般来说,图案晶圆检测系统系以白光或雷射光来照射晶圆表面。再由一或多组侦测器接收自晶圆表面绕射出来的光线,并将该影像交由高功能软件进行底层图案消除,以辨识并发现瑕疵。 3. CD-SEM(Critical Dime nsioi n Measureme nt) 对蚀刻后的图案作精确的尺寸检测。 二、IC封装 1. 构装(Packaging) IC构装依使用材料可分为陶瓷(ceramic )及塑胶(plastic )两种,而目前商业应用上则以塑胶构装为主。以塑胶构装中打线接合为例,其步骤依序为晶片切割( die saw)、黏晶(die mount / die bond)、焊线(wire bon d)、圭寸胶(mold )、剪切/ 成形(trim / form )、印字(mark )、电镀(plating )及检验(inspection )等。 (1) 晶片切割(die saw ) 晶片切割之目的为将前制程加工完成之晶圆上一颗颗之晶粒(die )切割分离。举例来说:以 0.2微米制程技术生产,每片八寸晶圆上可制作近六百颗以上的64M微量。 欲进行晶片切割,首先必须进行晶圆黏片,而后再送至晶片切割机上进行切割。切割完后之 晶粒井然有序排列于胶带上,而框架的支撐避免了胶带的皱褶与晶粒之相互碰撞。 (2) 黏晶(die mou nt / die bo nd ) 黏晶之目的乃将一颗颗之晶粒置于导线架上并以银胶(epoxy)粘着固定。黏晶完成后之导线 架则经由传输设备送至弹匣( magazi ne )内,以送至下一制程进行焊线。 ⑶焊线(wire bond ) IC构装制程(Packaging )则是利用塑胶或陶瓷包装晶粒与配线以成集成电路( Integrated Circuit ;简称IC),此制程的目的是为了制造出所生产的电路的保护层,避免电路受到机械

手机app测试方法

1 APP测试基本流程 1.1流程图 仍然为测试环境

1.2测试周期 测试周期可按项目的开发周期来确定测试时间,一般测试时间为两三周(即15个工作日),根据项目情况以及版本质量可适当缩短或延长测试时间。正式测试前先向主管确认项目排期。 1.3测试资源 测试任务开始前,检查各项测试资源。 --产品功能需求文档; --产品原型图; --产品效果图; --行为统计分析定义文档; --测试设备(ios3.1.3-ios5.0.1;Android1.6-Android4.0;Winphone7.1及以上;Symbian v3/v5/Nokia Belle等); --其他。 1.4日报及产品上线报告 1)测试人员每天需对所测项目发送测试日报。 2)测试日报所包含的内容为: --对当前测试版本质量进行分级; --对较严重的问题进行例举,提示开发人员优先修改; --对版本的整体情况进行评估。 3)产品上线前,测试人员发送产品上线报告。 4)上线报告所包含的内容为: ---对当前版本质量进行分级; ---附上测试报告(功能测试报告、兼容性测试报告、性能测试报告以及app可用性能标准结果); --总结上线版本的基本情况。若有遗留问题必须列出并记录解决方案。 2 App测试点 2.1安全测试 2.1.1软件权限 1)扣费风险:包括发送短信、拨打电话、连接网络等

2)隐私泄露风险:包括访问手机信息、访问联系人信息等 3)对App的输入有效性校验、认证、授权、敏感数据存储、数据加密等方面进行检测 4)限制/允许使用手机功能接人互联网 5)限制/允许使用手机发送接受信息功能 6)限制/允许应用程序来注册自动启动应用程序 7)限制或使用本地连接 8)限制/允许使用手机拍照或录音 9)限制/允许使用手机读取用户数据 10) 限制/允许使用手机写人用户数据 11) 检测App的用户授权级别、数据泄漏、非法授权访问等 2.1.2安装与卸载安全性 1)应用程序应能正确安装到设备驱动程序上 2)能够在安装设备驱动程序上找到应用程序的相应图标 3)是否包含数字签名信息 4)JAD文件和JAR包中包含的所有托管属性及其值必需是正确的 5)JAD文件显示的资料内容与应用程序显示的资料内容应一致 6)安装路径应能指定 7)没有用户的允许,应用程序不能预先设定自动启动 8)卸载是否安全,其安装进去的文件是否全部卸载 9)卸载用户使用过程中产生的文件是否有提示 10)其修改的配置信息是否复原 11)卸载是否影响其他软件的功能 12)卸载应该移除所有的文件 2.1.3数据安全性 1)当将密码或其他的敏感数据输人到应用程序时,其不会被储存在设备中,同时密码也不会被解码 2)输人的密码将不以明文形式进行显示 3)密码,信用卡明细,或其他的敏感数据将不被储存在它们预输人的位置上 4)不同的应用程序的个人身份证或密码长度必需至少在4一8个数字长度之间 5)当应用程序处理信用卡明细,或其他的敏感数据时,不以明文形式将数据写到其它单独的文件或者临时文件中。以防止应用程序异常终止而又没有侧除它的临时文件,文件可能遭受人侵者的袭击,然后读取这些数据信息。 6)当将敏感数据输人到应用程序时,其不会被储存在设备中 7)备份应该加密,恢复数据应考虑恢复过程的异常通讯中断等,数据恢复后再使用前应该经过校验 8)应用程序应考虑系统或者虚拟机器产生的用户提示信息或安全替告 9)应用程序不能忽略系统或者虚拟机器产生的用户提示信息或安全警告,更不能在安全警

半导体工艺流程

1、清洗 集成电路芯片生产的清洗包括硅片的清洗和工器具的清洗。由于半导体生产污染要求非常严格,清洗工艺需要消耗大量的高纯水;且为进行特殊过滤和纯化广泛使用化学试剂和有机溶剂。 在硅片的加工工艺中,硅片先按各自的要求放入各种药液槽进行表面化学处理,再送入清洗槽,将其表面粘附的药液清洗干净后进入下一道工序。常用的清洗方式是将硅片沉浸在液体槽内或使用液体喷雾清洗,同时为有更好的清洗效果,通常使用超声波激励和擦片措施,一般在有机溶剂清洗后立即采用无机酸将其氧化去除,最后用超纯水进行清洗,如图1 —6所示。 图1—6硅片清洗工艺示意图 工具的清洗基本米用硅片清洗同样的方法。 2、热氧化 热氧化是在800~1250C高温的氧气氛围和惰性携带气体(N2)下使硅片表面的硅氧化生成二氧化硅膜的过程,产生的二氧化硅用以作 为扩散、离子注入的阻挡层,或介质隔离层。典型的热氧化化学反应为:

Si + O2f SiO2 3、扩散 扩散是在硅表面掺入纯杂质原子的过程。通常是使用乙硼烷(B2H6)作为N —源和磷烷(PH3)作为P+源。工艺生产过程中通常 分为沉积源和驱赶两步,典型的化学反应为: 2PH3 f 2P + 3H2 4、离子注入 离子注入也是一种给硅片掺杂的过程。它的基本原理是把掺杂物质(原子)离子化后,在数千到数百万伏特电压的电场下得到加速,以较高的能量注入到硅片表面或其它薄膜中。经高温退火后,注入离子活化,起施主或受主的作用。 5、光刻 光刻包括涂胶、曝光、显影等过程。涂胶是通过硅片高速旋转在硅片表面均匀涂上光刻胶的过程;曝光是使用光刻机,并透过光掩膜版对涂胶的硅片进行光照,使部分光刻胶得到光照,另外,部分光刻胶得不到光照,从而改变光刻胶性质;显影是对曝光后的光刻胶进行去除,由于光照后的光刻胶和未被光照的光刻胶将分别溶于显影液和不溶于显影液,这样就使光刻胶上 形成了沟槽。 光刻胶 基片------------ ?涂胶后基片 1 1 1 1 ~ 显影后基片V------------- 曝光后基片 6、湿法腐蚀和等离子刻蚀

晶圆封装测试工序和半导体制造工艺流程

A.晶圆封装测试工序 一、IC检测 1. 缺陷检查Defect Inspection 2. DR-SEM(Defect Review Scanning Electron Microscopy) 用来检测出晶圆上是否有瑕疵,主要是微尘粒子、刮痕、残留物等问题。此外,对已印有电路图案的图案晶圆成品而言,则需要进行深次微米范围之瑕疵检测。一般来说,图案晶圆检测系统系以白光或雷射光来照射晶圆表面。再由一或多组侦测器接收自晶圆表面绕射出来的光线,并将该影像交由高功能软件进行底层图案消除,以辨识并发现瑕疵。 3. CD-SEM(Critical Dimensioin Measurement) 对蚀刻后的图案作精确的尺寸检测。 二、IC封装 1. 构装(Packaging) IC构装依使用材料可分为陶瓷(ceramic)及塑胶(plastic)两种,而目前商业应用上则以塑胶构装为主。以塑胶构装中打线接合为例,其步骤依序为晶片切割(die saw)、黏晶(die mount / die bond)、焊线(wire bond)、封胶(mold)、剪切/成形(trim / form)、印字(mark)、电镀(plating)及检验(inspection)等。 (1) 晶片切割(die saw) 晶片切割之目的为将前制程加工完成之晶圆上一颗颗之晶粒(die)切割分离。举例来说:以

0.2微米制程技术生产,每片八寸晶圆上可制作近六百颗以上的64M微量。 欲进行晶片切割,首先必须进行晶圆黏片,而后再送至晶片切割机上进行切割。切割完后之晶粒井然有序排列于胶带上,而框架的支撐避免了胶带的皱褶与晶粒之相互碰撞。 (2) 黏晶(die mount / die bond) 黏晶之目的乃将一颗颗之晶粒置于导线架上并以银胶(epoxy)粘着固定。黏晶完成后之导线架则经由传输设备送至弹匣(magazine)内,以送至下一制程进行焊线。 (3) 焊线(wire bond) IC构装制程(Packaging)则是利用塑胶或陶瓷包装晶粒与配线以成集成电路(Integrated Circuit;简称IC),此制程的目的是为了制造出所生产的电路的保护层,避免电路受到机械性刮伤或是高温破坏。最后整个集成电路的周围会向外拉出脚架(Pin),称之为打线,作为与外界电路板连接之用。 (4) 封胶(mold) 封胶之主要目的为防止湿气由外部侵入、以机械方式支持导线、內部产生热量之去除及提供能够手持之形体。其过程为将导线架置于框架上并预热,再将框架置于压模机上的构装模上,再以树脂充填并待硬化。 (5) 剪切/成形(trim / form) 剪切之目的为将导线架上构装完成之晶粒独立分开,并把不需要的连接用材料及部份凸出之树脂切除(dejunk)。成形之目的则是将外引脚压成各种预先设计好之形状,以便于装置于

晶圆封装测试工序和半导体制造工艺流程

晶圆封装测试工序和半导体制造工艺流程 A.晶圆封装测试工序 一、 IC检测 1. 缺陷检查Defect Inspection 2. DR-SEM(Defect Review Scanning Electron Microscopy) 用来检测出晶圆上是否有瑕疵,主要是微尘粒子、刮痕、残留物等问题。此外,对已印有电路图案的图案晶圆成品而言,则需要进行深次微米范围之瑕疵检测。一般来说,图案晶圆检测系统系以白光或雷射光来照射晶圆表面。再由一或多组侦测器接收自晶圆表面绕射出来的光线,并将该影像交由高功能软件进行底层图案消除,以辨识并发现瑕疵。 3. CD-SEM(Critical Dimensioin Measurement) 对蚀刻后的图案作精确的尺寸检测。 二、 IC封装 1. 构装(Packaging) IC构装依使用材料可分为陶瓷(ceramic)及塑胶(plastic)两种,而目前商业应用上则以塑胶构装为主。以塑胶构装中打线接合为例,其步骤依序为晶片切割(die saw)、黏晶(die mount / die bond)、焊线(wire bond)、封胶(mold)、剪切/成形(trim / form)、印字(mark)、电镀(plating)及检验(inspection)等。 (1) 晶片切割(die saw) 晶片切割之目的为将前制程加工完成之晶圆上一颗颗之晶粒(die)切割分离。 举例来说:以0.2微米制程技术生产,每片八寸晶圆上可制作近六百颗以上的64M 微量。

欲进行晶片切割,首先必须进行晶圆黏片,而后再送至晶片切割机上进行切割。切割完后之晶粒井然有序排列于胶带上,而框架的支撐避免了胶带的皱褶与晶粒之相互碰撞。 (2) 黏晶(die mount / die bond) 黏晶之目的乃将一颗颗之晶粒置于导线架上并以银胶(epoxy)粘着固定。黏晶完成后之导线架则经由传输设备送至弹匣(magazine)内,以送至下一制程进行焊线。 (3) 焊线(wire bond) IC构装制程(Packaging)则是利用塑胶或陶瓷包装晶粒与配线以成集成电路(Integrated Circuit;简称IC),此制程的目的是为了制造出所生产的电路的保护层,避免电路受到机械性刮伤或是高温破坏。最后整个集成电路的周围会向外拉出脚架(Pin),称之为打线,作为与外界电路板连接之用。 (4) 封胶(mold) 封胶之主要目的为防止湿气由外部侵入、以机械方式支持导线、內部产生热量之去除及提供能够手持之形体。其过程为将导线架置于框架上并预热,再将框架置于压模机上的构装模上,再以树脂充填并待硬化。 (5) 剪切/成形(trim / form) 剪切之目的为将导线架上构装完成之晶粒独立分开,并把不需要的连接用材料及部份凸出之树脂切除(dejunk)。成形之目的则是将外引脚压成各种预先设计好之形状,以便于装置于电路板上使用。剪切与成形主要由一部冲压机配上多套不同制程之模具,加上进料及出料机构所組成。 (6) 印字(mark)及电镀(plating) 印字乃将字体印于构装完的胶体之上,其目的在于注明商品之规格及制造者等资讯。

半导体封装方式

半导体封装简介: 半导体生产流程由晶圆制造、晶圆测试、芯片封装和封装后测试组成。塑封之后,还要进行一系列操作,如后固化(Post Mold Cure)、切筋和成型 (Trim&Form)、电镀(Plating)以及打印等工艺。典型的封装工艺流程为: 划片装片键合塑封去飞边电镀打印切筋和成型外观检查成品测试包装出货。 一、DIP双列直插式封装 1. 适合在PCB(印刷电路板)上穿孔焊接,操作方便。 2. 芯片面积与封装面积之间的比值较大,故体积也较大。 二、QFP塑料方型扁平式封装和PFP塑料扁平组件式封装 QFP封装的芯片引脚之间距离很小,管脚很细,一般大规模或超大型集 成电路都采用这种封装形式,其引脚数一般在100个以上。用这种形式 封装的芯片必须采用SMD(表面安装设备技术)将芯片与主板焊接起来。 采用SMD安装的芯片不必在主板上打孔,一般在主板表面上有设计好 的相应管脚的焊点。将芯片各脚对准相应的焊点,即可实现与主板的焊 接。用这种方法焊上去的芯片,如果不用专用工具是很难拆卸下来的。 PFP(Plastic Flat Package)方式封装的芯片与QFP方式基本相同。唯一的 区别是QFP一般为正方形,而PFP既可以是正方形,也可以是长方形。 QFP/PFP封装具有以下特点: 1.适用于SMD表面安装技术在PCB电路板上安装布线。 2.适合高频使用。 3.操作方便,可靠性高。 4.芯片面积与封装面积之间的比值较小。 三、PGA插针网格阵列封装 一种名为ZIF的CPU插座,专门用来满足PGA封装的CPU在安装和 拆卸上的要求。ZIF(Zero Insertion Force Socket)是指零插拔力的插座。 1. 插拔操作更方便,可靠性高。 2. 可适应更高的频率。

(工艺流程)2020年半导体硅片生产工艺流程及工艺注意要点

硅片生产工艺流程及注意要点 简介 硅片的准备过程从硅单晶棒开始,到清洁的抛光片结束,以能够在绝好的环境中使用。期间,从一单晶硅棒到加工成数片能满足特殊要求的硅片要经过很多流程和清洗步骤。除了有许多工艺步骤之外,整个过程几乎都要在无尘的环境中进行。硅片的加工从一相对较脏的环境开始,最终在10级净空房内完成。 工艺过程综述 硅片加工过程包括许多步骤。所有的步骤概括为三个主要种类:能修正物理性能如尺寸、形状、平整度、或一些体材料的性能;能减少不期望的表面损伤的数量;或能消除表面沾污和颗粒。硅片加工的主要的步骤如表1.1的典型流程所示。工艺步骤的顺序是很重要的,因为这些步骤的决定能使硅片受到尽可能少的损伤并且可以减少硅片的沾污。在以下的章节中,每一步骤都会得到详细介绍。 表1.1 硅片加工过程步骤 1.切片 2.激光标识 3.倒角 4.磨片 5.腐蚀 6.背损伤 7.边缘镜面抛光 8.预热清洗 9.抵抗稳定——退火 10.背封 11.粘片 12.抛光 13.检查前清洗 14.外观检查

15.金属清洗 16.擦片 17.激光检查 18.包装/货运 切片(class 500k) 硅片加工的介绍中,从单晶硅棒开始的第一个步骤就是切片。这一步骤的关键是如何在将单晶硅棒加工成硅片时尽可能地降低损耗,也就是要求将单晶棒尽可能多地加工成有用的硅片。为了尽量得到最好的硅片,硅片要求有最小量的翘曲和最少量的刀缝损耗。切片过程定义了平整度可以基本上适合器件的制备。 切片过程中有两种主要方式——内圆切割和线切割。这两种形式的切割方式被应用的原因是它们能将材料损失减少到最小,对硅片的损伤也最小,并且允许硅片的翘曲也是最小。 切片是一个相对较脏的过程,可以描述为一个研磨的过程,这一过程会产生大量的颗粒和大量的很浅表面损伤。 硅片切割完成后,所粘的碳板和用来粘碳板的粘结剂必须从硅片上清除。在这清除和清洗过程中,很重要的一点就是保持硅片的顺序,因为这时它们还没有被标识区分。 激光标识(Class 500k) 在晶棒被切割成一片片硅片之后,硅片会被用激光刻上标识。一台高功率的激光打印机用来在硅片表面刻上标识。硅片按从晶棒切割下的相同顺序进行编码,因而能知道硅片的正确位置。这一编码应是统一的,用来识别硅片并知道它的来源。编码能表明该硅片从哪一单晶棒的什么位置切割下来的。保持这样的追溯是很重要的,因为单晶的整体特性会随着晶棒的一头到另一头而变化。编号需刻的足够深,从而到最终硅片抛光完毕后仍能保持。在硅片上刻下编码后,即使硅片有遗漏,也能追溯到原来位置,而且如果趋向明了,那么就可以采取正确的措施。激光标识可以在硅片的正面也可在背面,尽管正面通常会被用到。

手机黑盒测试介绍

手机黑盒测试介绍 手机黑盒测试介绍软件测试 黑盒测试(black—box testing)又称功能测试、数据驱动测试或基于规范的测试。用这种方法进行测试时,被测程序被当作看不见内部的黑盒。在完全不考虑程序内部结构和内部特性的情况下,测试者仅依据程序功能的需求规范考虑确定测试用例和推断测试结果的正确性。因此黑盒测试是从用户观点出发的测试,黑盒测试直观的想法就是既然程序被规定做某些事,那我们就看看它是不是在任何情况下都做的对。完整的“任何情况”是无法验证的,为此黑盒测试也有一套产生测试用例的方法,以产生有限的测试用例而覆盖足够多的“任何情况”。由于黑盒测试不需要了解程序内部结构,所以许多高层的测试如确认测试、系统测试、验收测试都采用黑盒测试。 黑盒测试首先是程序通常的功能性测试。要求: 每个软件特性必须被一个测试用例或一个被认可的异常所覆盖。 用数据类型和数据值的最小集测试。 用一系列真实的数据类型和数据值运行,测试超负荷、饱和及其他“最坏情况”的结果; 用假想的数据类型和数据值运行,测试排斥不规则输入的能力; 对影响性能的关键模块,如基本算法、应测试单元性能(包括精度、时间、容量等)。 不仅要考核“程序是否做了该做的?”还要考察“程序是否没做不该做的2”同时还要考察程序在其他一些情况下是否正常。这些情况包括数据类型和数

据值的异常等等。下述几种方法:(a)等价类划分,(b)因果图方法,(c)边值分析法,(d)猜错法,(e)随机数法,就是从更广泛的角度来进行黑盒测试。每一个方法都力图能涵盖更多的“任何情况”,但又各有长处,综合使用这些方法,会得到一个较好的测试用例集。 1.等价类划分 等价类划分是一种典型的黑盒测试方法。等价类是指某个输入域的集合。它表示对揭露程序中的错误来说,集合中的每个输入条件是等效的。因此我们只要在一个集合中选取一个测试数据即可。等价类划分的办法是把程序的输入域划分成若干等价类,然后从每个部分中选取少数代表性数据当作测试用例。这样就可使用少数测试用例检验程序在一大类情况下的反映。 在考虑等价类时,应该注意区别以下两种不同的情况: 有效等价类:有效等价类指的是对程序的规范是有意义的、合理的输入数据所构成的集合。在具体问题中,有效等价类可以是一个,也可以是多个。 无效等价类:无效等价类指对程序的规范是不合理的或无意义的输入数据所构成的集合。对于具体的问题,无效等价类至少应有一个,也可能有多个。 确定等价类有以下几条原则: 如果输入条件规定了取值范围或值的个数,则可确定一个有效等价类和两个无效等价类。例如,程序的规范中提到的输入条包括“……项数可以从1到999……”,则可取有效等价类为“l考项数<999”,无效等价类为“项数999”。 输入条件规定了输入值的集合,或是规定了“必须如何”的条件,则可确定一个有效等价类和一个无效等价类。如某程序涉及标识符,其输入条件规定“标

非常全面的手机测试流程(精)

非常全面的手机测试流程目录 1、基本通话 1.1 来电响铃时 1.1.1来电响铃时的接通操作…………………………………………………………… 1.1.2来电响铃结束操作………………………………………………………………… 1.1.3来电响铃过程中有效功能的按键操作(除接通、结束……………………… 1.1.4来电响铃时的无效按键操作……………………………………………………… 1.2 来电通话 1.2.1来电通话中的基本菜单操作(除挂机…………………………………………. 1.2.2通话中的功能键……………………………………………………………………. 1.2.3结束通话……………………………………………………………………………. 1.3 呼叫功能 1.3.1拨号呼出………………………………………………………………………….. 1.3.2结束呼叫响铃…………………………………………………………………….

1.3.3呼叫中的无效操作………………………………………………………………. 1.3.4主叫通话时功能操作……………………………………………………………. 1.3.5 结束主叫通话…………………………………………………………………… 1.4多方通话 1.4.1主叫多方通话……………………………………………………………………. 1.4.2被叫多方通话……………………………………………………………………. 2、通话设置 2.1 翻盖应答………………………………………………………………………………… 2.2 单键拨号………………………………………………………………………………… 2.3自动重拨…………………………………………………………………………………. 2.4 任意键应答……………………………………………………………………………… 2.5 呼叫等待…………………………………………………………………………………

半导体制造工艺流程简介

半导体制造工艺流程简介 半导体制造工艺 1 NPN高频小功率晶体管制造的工艺流程为: 外延片——编批——清洗——水汽氧化——一次光刻——检查——清洗——干氧氧化——硼注入——清洗——UDO淀积——清洗——硼再扩散——二次光刻——检查——单结测试——清洗——干氧氧化——磷注入——清洗——铝下CVD——清洗——发射区再扩散——三次光刻——检查——双结测试——清洗——铝蒸发——四次光刻——检查——氢气合金——正向测试——清洗——铝上CVD——检查——五次光刻——检查——氮气烘焙——检查——中测——中测检查——粘片——减薄——减薄后处理——检查——清洗——背面蒸发——贴膜——划片——检查——裂片——外观检查——综合检查——入中间库。 PNP小功率晶体管制造的工艺流程为: 外延片——编批——擦片——前处理——一次氧化——QC检查(tox)——一次光刻——QC检查——前处理——基区CSD涂覆——CSD预淀积——后处理——QC 检查(R?)——前处理——基区氧化扩散——QC检查(tox、R?)——二次光刻——QC 检查——单结测试——前处理——POCl3预淀积——后处理(P液)——QC检查——前处理——发射区氧化——QC检查(tox)——前处理——发射区再扩散(R?)——前处理——铝下CVD——QC检查(tox、R?)——前处理——HCl氧化——前处理——氢气处 理——三次光刻——QC检查——追扩散——双结测试——前处理——铝蒸发——QC检查(tAl)——四次光刻——QC检查——前处理——氮气合金——氮气烘焙——QC检查(ts)——五次光刻——QC检查——大片测试——中测——中测检查(——

IC半导体封装测试流程

IC半导体封装测试流程 更多免费资料下载请进:https://www.360docs.net/doc/d67055691.html,好好学习社区

IC半导体封装测试流程 第1章前言 1.1 半导体芯片封装的目的 半导体芯片封装主要基于以下四个目的[10, 13]: ●防护 ●支撑 ●连接 ●可靠性 图1-1 TSOP封装的剖面结构图 Figure 1-1 TSOP Package Cross-section 第一,保护:半导体芯片的生产车间都有非常严格的生产条件控制,恒定的温度(230±3℃)、恒定的湿度(50±10%)、严格的空气尘埃颗粒度控制(一般介于1K到10K)及严格的静电保护措施,裸露的装芯片只有在这种严格的环境控制下才不会失效。但是,我们所生活的周围环境完全不可能具备这种条件,低温可能会有-40℃、高温可能会有60℃、湿度可能达到100%,如果是汽车产品,其工作温度可能高达120℃以上,为了要保护芯片,所以我们需要封装。 第二,支撑:支撑有两个作用,一是支撑芯片,将芯片固定好便于电路的连接,二是封装完成以后,形成一定的外形以支撑整个器件、使得整个器件不易损坏。 第三,连接:连接的作用是将芯片的电极和外界的电路连通。

引脚用于和外界电路连通,金线则将引脚和芯片的电路连接起来。载片台用于承载芯片,环氧树脂粘合剂用于将芯片粘贴在载片台上,引脚用于支撑整个器件,而塑封体则起到固定及保护作用。 第四,可靠性:任何封装都需要形成一定的可靠性,这是整个封装工艺中最重要的衡量指标。原始的芯片离开特定的生存环境后就会损毁,需要封装。芯片的工作寿命,主要决于对封装材料和封装工艺的选择。 1.2 半导体芯片封装技术的发展趋势 ● 封装尺寸变得越来越小、越来越薄 ● 引脚数变得越来越多 ● 芯片制造与封装工艺逐渐溶合 ● 焊盘大小、节距变得越来越小 ● 成本越来越低 ● 绿色、环保 以下半导体封装技术的发展趋势图[2,3,4,11,12,13]: 图1-2 半导体封装技术发展趋势 Figure 1-2 Assembly Technology Development Trend 小型化

半导体的生产工艺流程(精)

半导体的生产工艺流程 微机电制作技术,尤其是最大宗以硅半导体为基础的微细加工技术(silicon- based micromachining,原本就肇源于半导体组件的制程技术,所以必须先介绍清楚这类制程,以免沦于夏虫语冰的窘态。 一、洁净室 一般的机械加工是不需要洁净室(clean room的,因为加工分辨率在数十微米以上,远比日常环境的微尘颗粒为大。但进入半导体组件或微细加工的世界,空间单位都是以微米计算,因此微尘颗粒沾附在制作半导体组件的晶圆上,便有可能影响到其上精密导线布局的样式,造成电性短路或断路的严重后果。 为此,所有半导体制程设备,都必须安置在隔绝粉尘进入的密闭空间中,这就是洁净室的来由。洁净室的洁净等级,有一公认的标准,以class 10为例,意谓在单位立方英呎的洁净室空间内,平均只有粒径0.5微米以上的粉尘10粒。所以class后头数字越小,洁净度越佳,当然其造价也越昂贵(参见图2-1。 为营造洁净室的环境,有专业的建造厂家,及其相关的技术与使用管理办法如下: 1、内部要保持大于一大气压的环境,以确保粉尘只出不进。所以需要大型鼓风机,将经滤网的空气源源不绝地打入洁净室中。 2、为保持温度与湿度的恒定,大型空调设备须搭配于前述之鼓风加压系统中。换言之,鼓风机加压多久,冷气空调也开多久。 3、所有气流方向均由上往下为主,尽量减少突兀之室内空间设计或机台摆放调配,使粉尘在洁净室内回旋停滞的机会与时间减至最低程度。 4、所有建材均以不易产生静电吸附的材质为主。 5、所有人事物进出,都必须经过空气吹浴 (air shower 的程序,将表面粉尘先行去除。

6、人体及衣物的毛屑是一项主要粉尘来源,为此务必严格要求进出使用人员穿戴无尘衣,除了眼睛部位外,均需与外界隔绝接触 (在次微米制程技术的工厂内,工作人员几乎穿戴得像航天员一样。当然,化妆是在禁绝之内,铅笔等也禁止使用。 7、除了空气外,水的使用也只能限用去离子水 (DI water, de-ionized water。一则防止水中粉粒污染晶圆,二则防止水中重金属离子,如钾、钠离子污染金氧半(MOS 晶体管结构之带电载子信道 (carrier channel,影响半导体组件的工作特性。去离子水以电阻 率 (resistivity 来定义好坏,一般要求至17.5MΩ-cm以上才算合格;为此需动用多重离子交换树脂、RO逆渗透、与UV紫外线杀菌等重重关卡,才能放行使用。由于去离子水是最佳的溶剂与清洁剂,其在半导体工业之使用量极为惊人! 8、洁净室所有用得到的气源,包括吹干晶圆及机台空压所需要的,都得使用氮气(98%,吹干晶圆的氮气甚至要求99.8%以上的高纯氮!以上八点说明是最基本的要求,另还有污水处理、废气排放的环保问题,再再需要大笔大笔的建造与维护费用! 二、晶圆制作 硅晶圆 (silicon wafer 是一切集成电路芯片的制作母材。既然说到晶体,显然是经过纯炼与结晶的程序。目前晶体化的制程,大多是采「柴可拉斯基」(Czycrasky 拉晶法 (CZ法。拉晶时,将特定晶向 (orientation 的晶种 (seed,浸入过饱和的纯硅熔汤 (Melt 中,并同时旋转拉出,硅原子便依照晶种晶向,乖乖地一层层成长上去,而得出所谓的晶棒 (ingot。晶棒的阻值如果太低,代表其中导电杂质 (impurity dopant 太多,还需经过FZ 法 (floating-zone 的再结晶 (re-crystallization,将杂质逐出,提高纯度与阻值。 辅拉出的晶棒,外缘像椰子树干般,外径不甚一致,需予以机械加工修边,然后以X 光绕射法,定出主切面 (primary flat 的所在,磨出该平面;再以内刃环锯,削下一片片的硅晶圆。最后经过粗磨 (lapping、化学蚀平 (chemical etching 与拋光 (polishing 等程序,得出具表面粗糙度在0.3微米以下拋光面之晶圆。(至于晶圆厚度,与其外径有