Triple-Speed Ethernet 仿真

虽然很艰辛,出了大堆问题,但总算一一解决了,即使是别人提供现成的IP核和testbench,说起来容易,但是做起来难,版本差别,软件设置,总有这些问题在困扰一穷二白的初学者,并阻挡前进的步伐,现在总结一下我做altera triple speed Ethernet这个IP核生成和编译仿真的全过程:(附操作图片)

1、生成IP core:

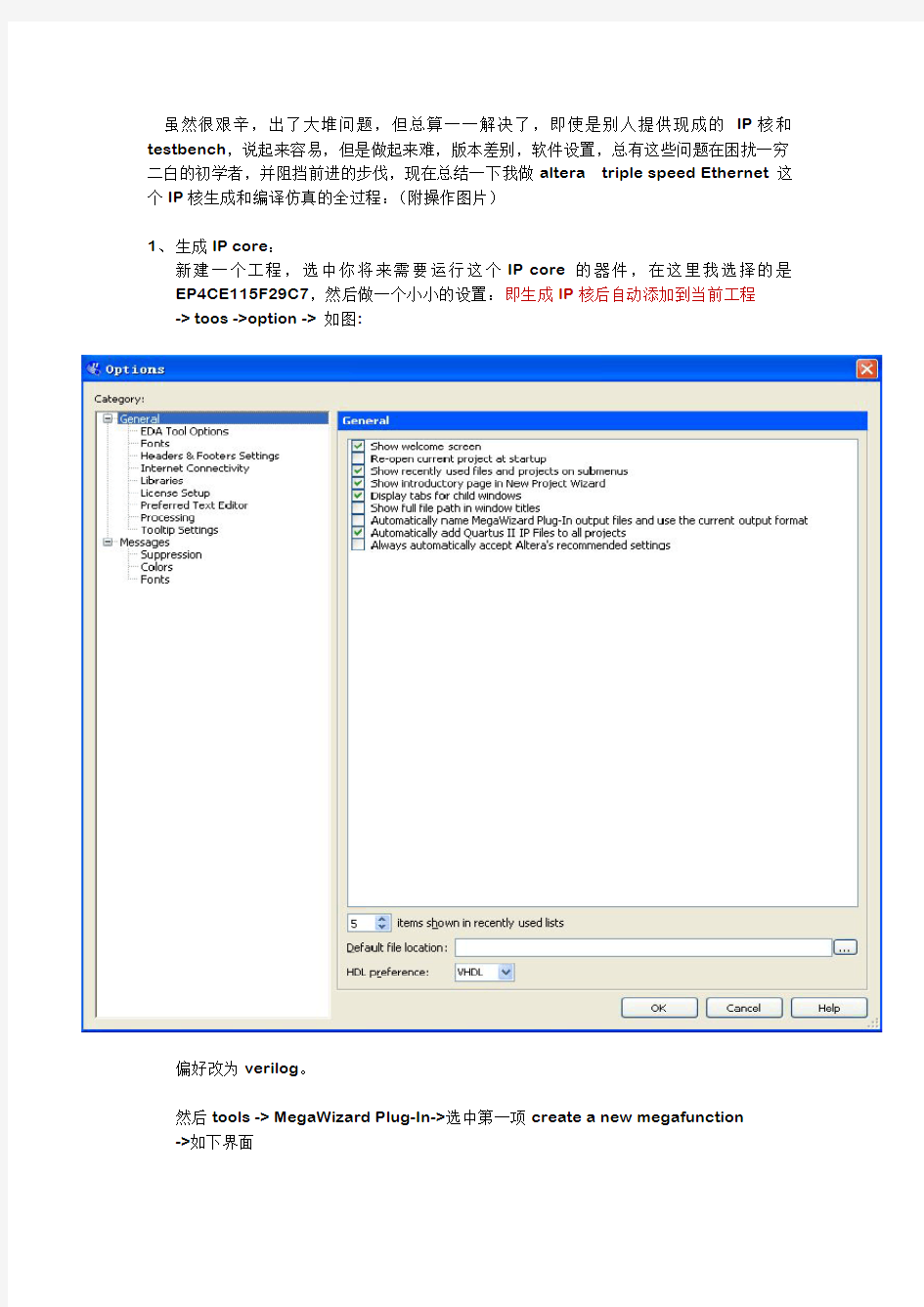

新建一个工程,选中你将来需要运行这个IP core的器件,在这里我选择的是EP4CE115F29C7,然后做一个小小的设置:即生成IP核后自动添加到当前工程->toos->option->如图:

偏好改为verilog。

然后tools->MegaWizard Plug-In->选中第一项create a new megafunction

->如下界面

注意一般应用IP核选择第一项Installed Plug-Ins,不要选中第二项IP MegaStore,原因在于第二项中多是altea合作伙伴开发的IP核,一般需要license才能仿真试用,比较麻烦,第一项几乎全都是随quartus II装好的IP核,所以可以支持opencore-plus功能,这样方便试用和仿真,只要通过下载电缆和相应支持的开发板连接就可以再开发板上面运行IP核,一般支持1小时的有效时间,已经够用。

接下来指定IP核输出路径,并指定IP核文件输出名称(加在路径后面),例如命名为tri_megacore,点击next->

如图是我的设置,因FPGA内部MAC与PHY连接接口选用RGMII,故选用该设置,使用内部FIFO,点击next->

一般按照默认设置既可,因仿真或者设计需要,另外选中第二项、第四项(包括64-bit counter)、第七项,同时选中包含MDIO module,将时钟分频改为50,MAC使用125MHz 时钟,分频50得到2.5MHz时钟,极为MDIO的工作时钟。

点击next->

内部FIFO设置,2048是深度(根据前段设计的数据吞吐量来定,当然一般定得大些比较好了)、8bit是位宽,这个FIFO的选择也决定avalon-ST总线的位宽。

点击next->

选中生成simulation model(仿真用)和netlist 点击next->

接下来IP core生成成功了,准备进行编译工作。

2、编译IP core:

第一次编译IP核建议在quartusII中进行,而不要再第三方的工具中进行,因为altera 自己的IP,自己的工具支持得最好,并且智能化程度很高,

首先工程窗口中点击files,右击tri_megacore.qip,

编译之前注意以下事项:

即仿真工具选择为none,原因在于quartus II在编译过程不支持第三方的工具。

编译一般木有啥问题。

接下来在开始调用modelsim SE6.5仿真之前,先编译好IP核需要的仿真库和器件库,

这一步比较重要,其中仿真工具的选择和路径指定、器件选择、仿真库的输出路径设置很关键,以后步骤还可能会用到。

编译完成后可以去改路径看看生成了什么东东:

不错,你看到就是自动生成的仿真需要用的所有仿真库文件。

然后在modelsim安装路径中找到modelsim.ini这个文件,去掉只读属性,并在library一栏加入:

altera_lnsim_ver=D:/Altera/quartus/eda/sim_lib/modelsim/verilog_libs/altera_lnsim_ver altera_mf_ver=D:/Altera/quartus/eda/sim_lib/modelsim/verilog_libs/altera_mf_ver

altera_ver=D:/Altera/quartus/eda/sim_lib/modelsim/verilog_libs/verilog_libs/altera_ver cycloneive_ver=D:/Altera/quartus/eda/sim_lib/modelsim/verilog_libs/cycloneive_ver

lpm_ver=D:/Altera/quartus/eda/sim_lib/modelsim/verilog_libs/lpm_ver

sgate_ver=D:/Altera/quartus/eda/sim_lib/modelsim/verilog_libs/sgate_ver

注意路径用正斜杠,不要用windows下面的反斜杠,因为这是modelsim的读路径要求!否则modelsim 找不到库文件,做这个的目的在于把这些库作为modelsim的默认库,以后都可以启动就直接调用。

OK,可以开始准备仿真了!!!

3、仿真IP core:

-assignment->settings->如下图:

选择好仿真工具为modelsim,大部分默认,点击More NativeLink Settings按钮,设置用户已编译仿真库位置,如下图:

在setting中选择刚刚输出编译好的仿真库的路径-tool->option->

开启功能仿真过程:

第一次功能仿真几乎肯定是不成功的,错误如下:

在E:\module\Eth_megacore\testbench\model下面找到这些文件

这些就是传说中的仿真模型simulation model!也就是说仿真没有能够成功加载仿真模型,肯定无法成功了!

在modelsim中点击compile,出现下面窗口:

选择E:\module\Eth_megacore\testbench\model中所有文件(除timing开头的那些,那些是做时序仿真用的),编译到work库中去,然后查看仿真脚本文件transcript,可以看出

刚才编译的脚本语句为:

vlog-reportprogress300-work work

E:/module/Eth_megacore/testbench/model/top_mdio_slave.v

E:/module/Eth_megacore/testbench/model/ethgen2.v

E:/module/Eth_megacore/testbench/model/ethgen.v

E:/module/Eth_megacore/testbench/model/ethmon2.v

E:/module/Eth_megacore/testbench/model/ethmon.v

E:/module/Eth_megacore/testbench/model/loopback_adapter.v

E:/module/Eth_megacore/testbench/model/loopback_adapter_fifo.v

E:/module/Eth_megacore/testbench/model/mdio_reg.v

E:/module/Eth_megacore/testbench/model/mdio_slave.v

把这些语句全部复制到do文件中去

粘贴的位置不能错,错了就无法启动功能仿真了!

OK!终于看到仿真波形了:

注意testbench采用了loopback技术,即自发自收,即如果能够收到和自己发送的相同数据的话,那么这个IP的功能就实现了,从图中看出RGMII接口的输入和输出数据均为1010,故整个的基本收发功能是正确的!

查看脚本,也可以证实这一点:

WIDTH=8;DEPTH=256;

ADDRESS_RADIX=UNS;DATA_RADIX=UNS;

CONTENT BEGIN