openwebmail问题集

openwebmail问题集

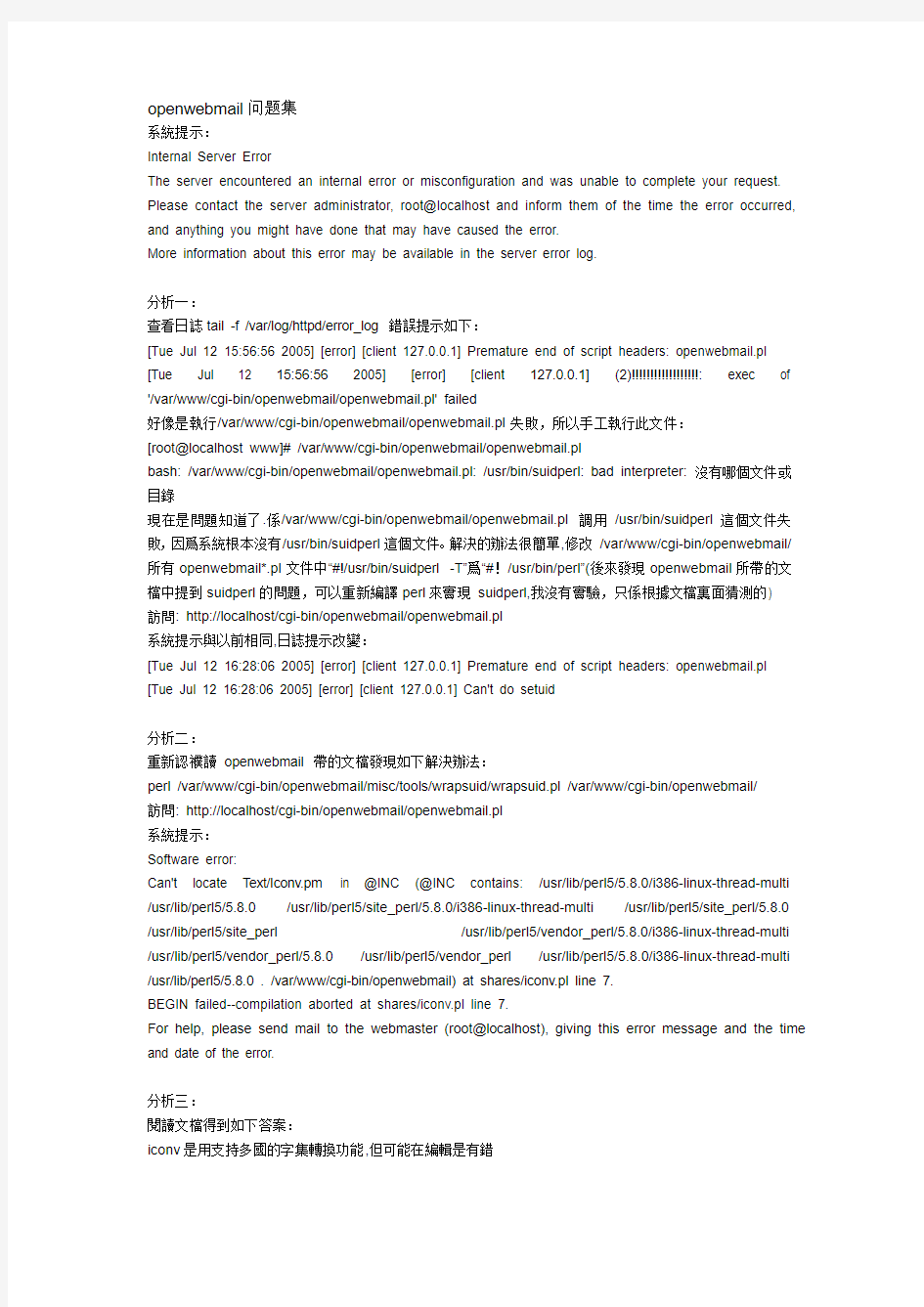

系統提示:

Internal Server Error

The server encountered an internal error or misconfiguration and was unable to complete your request. Please contact the server administrator, root@localhost and inform them of the time the error occurred, and anything you might have done that may have caused the error.

More information about this error may be available in the server error log.

分析一:

查看日誌tail -f /var/log/httpd/error_log 錯誤提示如下:

[Tue Jul 12 15:56:56 2005] [error] [client 127.0.0.1] Premature end of script headers: openwebmail.pl [Tue Jul 12 15:56:56 2005] [error] [client 127.0.0.1] (2)!!!!!!!!!!!!!!!!!!: exec of '/var/www/cgi-bin/openwebmail/openwebmail.pl' failed

好像是執行/var/www/cgi-bin/openwebmail/openwebmail.pl失敗,所以手工執行此文件:

[root@localhost www]# /var/www/cgi-bin/openwebmail/openwebmail.pl

bash: /var/www/cgi-bin/openwebmail/openwebmail.pl: /usr/bin/suidperl: bad interpreter: 沒有哪個文件或目錄

現在是問題知道了.係/var/www/cgi-bin/openwebmail/openwebmail.pl 調用/usr/bin/suidperl這個文件失敗,因爲系統根本沒有/usr/bin/suidperl這個文件。解決的辦法很簡單,修改/var/www/cgi-bin/openwebmail/所有openwebmail*.pl文件中“#!/usr/bin/suidperl -T”爲“#!/usr/bin/perl”(後來發現openwebmail所帶的文檔中提到suidperl的問題,可以重新編譯perl來實現suidperl,我沒有實驗,只係根據文檔裏面猜測的)

訪問: http://localhost/cgi-bin/openwebmail/openwebmail.pl

系統提示與以前相同,日誌提示改變:

[Tue Jul 12 16:28:06 2005] [error] [client 127.0.0.1] Premature end of script headers: openwebmail.pl [Tue Jul 12 16:28:06 2005] [error] [client 127.0.0.1] Can't do setuid

分析二:

重新認襥讀openwebmail 帶的文檔發現如下解決辦法:

perl /var/www/cgi-bin/openwebmail/misc/tools/wrapsuid/wrapsuid.pl /var/www/cgi-bin/openwebmail/

訪問: http://localhost/cgi-bin/openwebmail/openwebmail.pl

系統提示:

Software error:

Can't locate Text/Iconv.pm in @INC (@INC contains: /usr/lib/perl5/5.8.0/i386-linux-thread-multi /usr/lib/perl5/5.8.0 /usr/lib/perl5/site_perl/5.8.0/i386-linux-thread-multi /usr/lib/perl5/site_perl/5.8.0 /usr/lib/perl5/site_perl /usr/lib/perl5/vendor_perl/5.8.0/i386-linux-thread-multi /usr/lib/perl5/vendor_perl/5.8.0 /usr/lib/perl5/vendor_perl /usr/lib/perl5/5.8.0/i386-linux-thread-multi /usr/lib/perl5/5.8.0 . /var/www/cgi-bin/openwebmail) at shares/iconv.pl line 7.

BEGIN failed--compilation aborted at shares/iconv.pl line 7.

For help, please send mail to the webmaster (root@localhost), giving this error message and the time and date of the error.

分析三:

閱讀文檔得到如下答案:

iconv是用支持多國的字集轉換功能,但可能在編輯是有錯

cp /var/www/cgi-bin/openwebmail/misc/patches/iconv.pl.fake /var/www/cgi-bin/openwebmail/shares/iconv.pl

訪問: http://localhost/cgi-bin/openwebmail/openwebmail.pl

系統提示:

Please execute '/var/www/cgi-bin/openwebmail/openwebmail-tool.pl --init' on server first!

分析四:

提示什揦就做什揦,在命令下執行

/var/www/cgi-bin/openwebmail/openwebmail-tool.pl --init

提示如下

[root@localhost openwebmail]# /var/www/cgi-bin/openwebmail/openwebmail-tool.pl --init

Please change '/var/www/cgi-bin/openwebmail/etc/dbm.conf' from

dbm_ext .db

dbmopen_ext none

dbmopen_haslock no

to

dbm_ext .db

dbmopen_ext .db

dbmopen_haslock no

And execute '/var/www/cgi-bin/openwebmail/openwebmail-tool.pl --init' again!

ps: If you are running openwebmail in persistent mode,

don't forget to 'touch openwebmail*.pl', so speedycgi

will reload all scripts, modules and conf files in --init

分析五:

去修改/var/www/cgi-bin/openwebmail/etc/dbm.conf 這個文檔,如果沒有就新建,內容爲:

dbm_ext .db

dbmopen_ext .db

dbmopen_haslock no

然後再執行一次/var/www/cgi-bin/openwebmail/openwebmail-tool.pl --init

訪問: http://localhost/cgi-bin/openwebmail/openwebmail.pl

系統提示:

'/var/www/cgi-bin/openwebmail/.openwebmail.pl' must setuid to root

分析六:

原來剛才執行的perl /var/www/cgi-bin/openwebmail/misc/tools/wrapsuid/wrapsuid.pl /var/www/cgi-bin/openwebmail/後,所有openwebmail*.pl文檔的S位置沒有了.所以執行chmod 4755 /var/www/cgi-bin/openwebmail/openwebmail*.pl

訪問: http://localhost/cgi-bin/openwebmail/openwebmail.pl

OK,可以登陸了.

关于《国家税务总局关于纳税人对外开具增值税专用发票有关问题的公告》的解读

关于《国家税务总局关于纳税人对外开具增值税专用发票有关问题的公告》的解读 2014年07月08日 国家税务总局办公厅 虚开增值税专用发票,以危害税收征管罪入刑,属于比较严重的刑事犯罪。纳税人对外开具增值税专用发票,是否属于虚开增值税专用发票,需要以事实为依据,准确进行界定。 为此,税务总局制定发布了《国家税务总局关于纳税人对外开具增值税专用发票有关问题的公告》。公告列举了三种情形,纳税人对外开具增值税专用发票,同时符合的,则不属于虚开增值税专用发票,受票方可以抵扣进项税额。 理解本公告,需要把握以下几点: 一、纳税人对外开具的销售货物的增值税专用发票,纳税人应当拥有货物的所有权,包括以直接购买方式取得货物的所有权,也包括“先卖后买”方式取得货物的所有权。所谓“先卖后买”,是指纳税人将货物销售给下家在前,从上家购买货物在后。 二、以挂靠方式开展经营活动在社会经济生活中普遍存在,挂靠行为如何适用本公告,需要视不同情况分别确定。 第一,如果挂靠方以被挂靠方名义,向受票方纳税人销售货物、提供增值税应税劳务或者应税服务,应以被挂靠方为纳税人。被挂靠方作为货物的销售方或者应税劳务、应税服务的提供方,按照相关规定向受票方开具增值税专用发票,属于本公告规定的情形。 第二,如果挂靠方以自己名义向受票方纳税人销售货物、提供增值税应税劳务或者应税服务,被挂靠方与此项业务无关,则应以挂靠方为纳税人。这种情况下,被挂靠方向受票方纳税人就该项业务开具增值税专用发票,不在本公告规定之列。 三、本公告是对纳税人的某一种行为不属于虚开增值税专用发票所做的明确,目的在于既保护好国家税款安全,又维护好纳税人的合法权益。换一个角度说,本公告仅仅界定了纳税人的某一行为不属于虚开增值税专用发票,并不意味着非此即彼,从本公告并不能反推出不符合三种情形的行为就是虚开。 比如,某一正常经营的研发企业,与客户签订了研发合同,收取了研发费用,开具了专用发票,但研发服务还没有发生或者还没有完成。这种情况下不能因为本公告列举了“向受票方纳税人销售了货物,或者提供了增值税应税劳务、应税服务”,就判定研发企业虚开增值税专用发票。

FPGA习题集及参考答案

习题集及参考答案 一、填空题 1.一般把EDA技术的发展分为()个阶段。 2.FPGA/CPLD有如下设计步骤:①原理图/HDL文本输入、②适配、③功能仿真、④综合、 ⑤编程下载、⑥硬件测试,正确的设计顺序是①()⑤⑥。 3.在EDA工具中,能完成在目标系统器件上布局布线的软件称为()。 4.设计输入完成之后,应立即对文件进行()。 5.基于硬件描述语言的数字系统设计目前最常用的设计方法称为()设计法。 6.将硬件描述语言转化为硬件电路的过程称为()。 7.IP核在EDA技术和开发中具有十分重要的地位,以HDL方式提供的IP被称为() IP。 8.SOC系统又称为()系统。SOPC系统又称为()系统。 9.将硬核和固核作为()IP核,而软核作为()IP核。 10.IP核在EDA技术和开发中具有十分重要的地位,以HDL方式提供的IP被称为()。 11.HDL综合器就是逻辑综合的过程,把可综合的VHDL/Verilog HDL转化成硬件电路时, 包含了三个过程,分别是()、()、()。 12.EDA软件工具大致可以由五个模块构成,分别是设计输入编辑器、()、()、 ()和()。 13.按仿真电路描述级别的不同,HDL仿真器分为()仿真、()仿真、() 仿真和门级仿真。 14.系统仿真分为()、()和()。 15.()仿真是对设计输入的规范检测,这种仿真通过只能表示编译通过,说明设计 满足一定的语法规范,但不能保证设计功能满足期望。 16.()仿真是对综合后的网表进行的仿真,它验证设计模块的基本逻辑功能,但不 带有布局布线后产生的时序信息,是理想情况下的验证。 17.()仿真是布局布线后进行的后仿真,仿真时考虑了布线延时,和芯片实际的工 作情况更加接近。 18.目前Xilinx公司生产的FPGA主要采用了()配置存储器结构。 19.描述测试信号的变化和测试工程的模块叫做()。 20.现代电子系统设计领域中的EDA采用()的设计方法。 21.有限状态机可分为()状态机和()状态机两类。 22.Verilog HDL中的端口类型有三类:()、()、输入/输出端口。 23.Verilog HDL常用两大数据类型:()、()。 24.FPGA / CPLD设计流程为:原理图/HDL文本输入→()→综合→适配→()→ 编程下载→硬件测试。 25.()是描述数据在寄存器之间流动和处理的过程。 26.连续赋值常用于数据流行为建模,常以()为关键词。 27.Verilog HDL有两种过程赋值方式:()和()。 28.`timescale 1ns/100ps中1ns代表(),100ps代表()。 29.未来的集成电路技术的发展趋势,把整上系统集成在一个芯片上去,这种芯片被称为 ()。 30.从互连结构上可将PLD分为确定型和统计型两类。确定型结构的代表是(),

PowerPCB使用技巧

PowerPCB使用技巧 PowerPCB使用技巧 PowerPCB目前已在我所推广使用,它的基本使用技术已有培训 教材进行了详细的讲解,而对于我所广大电子应用工程师来说,其 问题在于已经熟练掌握了TANGO之类的布线工具之后,如何转到PowerPCB的应用上来。所以,本文就此类应用和培训教材上没有讲到,而我们应用较多的一些技术技巧作了论述。 1.输入的规范问题 对于大多数使用过TANGO的人来说,刚开始使用PowerPCB的时候,可能会觉得PowerPCB的限制太多。因为PowerPCB对原理图输 入和原理图到PCB的规则传输上是以保证其正确性为前提的。所以,它的原理图中没有能够将一根电气连线断开的功能,也不能随意将 一根电气连线在某个位置停止,它要保证每一根电气连线都要有起 始管脚和终止管脚,或是接在软件提供的连接器上,以供不同页面 间的信息传输。这是它防止错误发生的一种手段,其实,也是我们 应该遵守的一种规范化的原理图输入方式。 在PowerPCB设计中,凡是与原理图网表不一致的改动都要到 ECO方式下进行,但它给用户提供了OLE链接,可以将原理图中的 修改传到PCB中,也可以将PCB中的修改传回原理图。这样,既防 止了由于疏忽引起的错误,又给真正需要进行修改提供了方便。但是,要注意的是,进入ECO方式时要选择“写ECO文件”选项,而 只有退出ECO方式,才会进行写ECO文件操作。 2.电源层和地层的选择 PowerPCB中对电源层和地层的设置有两种选择,CAMPlane和 Split/Mixed。Split/Mixed主要用于多个电源或地共用一个层的情况,但只有一个电源和地时也可以用。它的主要优点是输出时的图

国家税务总局办公厅关于全国税务系统稽查人员业务考试的通知

乐税智库文档 财税法规 策划 乐税网

国家税务总局办公厅关于全国税务系统稽查人员业务考试的通知 【标 签】稽查人员业务考试,全国税务系统 【颁布单位】国家税务总局 【文 号】国税办发﹝2008﹞126号 【发文日期】2008-12-05 【实施时间】2008-12-05 【 有效性 】全文有效 【税 种】征收管理 国税办发[2008]126号 各省、自治区、直辖市国家税务局、地方税务局: 根据工作安排,现就2009年全国税务系统稽查人员业务考试工作有关事宜通知如下: 一、考试目的 进一步加强税务稽查专业队伍业务建设和人才队伍建设,检验税务稽查培训工作质量和效果,积极推进公务员分类管理,并作为选拔稽查人才、建立稽查等级制度的重要依据。 二、指导思想 稽查人员业务考试工作要以《干部教育培训工作条例(试行)》和全国税务工作会议精神为指导,坚持公平、公正、公开原则,坚持检验培训质量和效果与选拔专业人才相结合,为建设一支专业化税务稽查人才队伍奠定基础。 三、组织领导与职责分工 税务总局成立稽查业务考试领导小组,税务总局党组成员、人事司司长董志林任组长,稽查局局长马毅民、监察局局长郝一心、教育中心副主任魏仲瑜、人事司副巡视员蔡连山为副组长,教育中心、稽查局、监察局、人事司有关处室负责人为成员。下设考试工作办公室,办公室设在教育中心,魏仲瑜任办公室主任。

在税务总局领导小组领导下,教育中心负责考试工作组织协调、组织命题、考务、考试大纲编写等工作,人事司负责资格审查,稽查局参与命题、考试大纲编写等工作,监察局负责对考试工作全过程监督。 全国税务系统稽查人员业务考试工作,原则上以省(区、市)为单位组织。各省(区、市)国家税务局和地方税务局要成立考试领导小组和考试工作办公室,负责对所属系统组织考试的具体工作。 四、考试范围 此次稽查人员业务考试范围为全国税务系统全体在职稽查人员,其中50周岁以上、副处级以上干部可自愿参加。 五、考试教材 此次考试以《税务稽查管理》、《税务稽查方法》、《税务稽查案例》(中国税务出版社,2008年9月版)为教材,同时以《全国税务系统稽查人员业务考试大纲》为参考。 六、考试题型 考试试题分为综合理论题和实务题,总分为150分,综合理论题和实务题分别占70分和80分,试题题型分为单选、多选、判断、改错、案例分析等。考试时间为180分钟。 七、考试时间 考试时间初步安排在2009年3月下旬,具体考试时间及考务工作安排另行通知。 八、有关要求 (一)各省(区、市)国家税务局和地方税务局要高度重视全国税务系统稽查人员业务考试,认真组织好稽查人员的学习、辅导和培训,正确处理好考试与工作的关系,确保考试与工作两不误。 (二)此次稽查人员业务考试由总局指定考试教材和考试大纲,税务总局不指定任何人进行辅导,各地也不要邀请税务总局人员及教材编写人员进行辅导,凡购买或参加除此之外社会上任何考试教材、大纲、考试辅导班等产生不良后果的由本人负责。 国家税务总局办公厅

EDA技术课后参考答案

第一章 的英文全称及其中文含义是什么? 答:EDA是Electronic Design Automation,其中文含义是“电子设计自动化”。 2.什么叫EDA技术?简述EDA技术的发展历程。 答:EDA技术有狭义和广义之分,狭义EDA技术就是以大规模可编程逻辑器件为设计载体,以硬件描述语言为系统逻辑描述的主要表达方式,以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具,通过有关的开发软件,自动完成用软件的方式设计的电子系统到硬件系统的逻辑编译、逻辑化简、逻辑分割、逻辑综合及优化、逻辑布局布线、逻辑仿真,直至完成对于特定目标芯片的适配编译、逻辑映射、编程下载等工作,最终形成集成电子系统或专用集成芯片的一门新技术,或称为IES/ASIC自动设计技术。 3.简述用EDA技术设计电路的设计流程。 答 EDA设计流程包括:设计准备、设计输入、设计处理、设计校验、器件编程、器件测试和设计验证。 4.什么叫”综合”和”网表文件”? 答: (A)在电子设计领域中综合的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。(1)从自然语言转换到 VHDL 语言算法表示,即自然语言综合。(2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。(3)从 RTL 级表示转换到逻辑门(包括触发器)的表示,即逻辑综合。(4)从逻辑门表示转换到版图表示(ASIC 设计),或转换到 FPGA 的配置网表文件,可称为版图综合或结构综合。综合在电子设计自动化中处于核心地位。 (B)网表文件是描述电路的连接关系的文件,一般以文本文件的形式存在。英文为netlist file格式有cdl, spice, aucdl...等 5.从使用的角度来讲,EDA技术主要包括几个方面的内容?这几个方面在整个电子系统的设计中分别起什么作用? 答: EDA技术的学习主要应掌握4个方面的内容:① 大规模可编程逻辑器件;② 硬件描述语言;③ 软件开发工具;④ 实验开发系统。 6.目前流行的主流厂家的EDA的软件工具有哪些?比较这些EDA软件的差异。 答: (1)目前比较流行的主流厂家的EDA的软件工具有Altera的MAX+plus II、Quartus II 、Lattice的ispEXPERT、Xilinx的Foundation Series。 (2)Max+plus II 是A1tera公司推出的一个使用非常广泛的EDA软件工具,它支持原理图、VHDL和Verilog语言的文本文件,以及波形图与EDIF等格式的文件作为设计输入,并支持这些文件的任意混合设计。它具有门级仿真器,可以进行功能仿真和时序仿真,能够产生精确的仿真结果。在适配之后,Max+plus II生成供时序仿真用的Edif、VHDL和Verilog 3种不同格式的网表文件。Max+plus II界面友好,使用便捷,被誉为业界最易学易用的EDA 软件,并支持主流的第三方EDA工具,支持除APEx20K系列之外的所有A1tera公司的FPGA /CPLD大规模逻辑器件。 Quartus II是A1tera公司新近推出的EDA软件工具,其设计工具完全支持VHDL和Verilog 的设计流程,其内部嵌有VHDL、Verilog逻辑综合器。第三方的综合工具,如Leonardo Spectrum、Synplify pro和FPGA Compiler II有着更好的综合效果,Quartus II可以直接

PowerPCB使用经验与技巧

PowerPCB使用经验与技巧 1.powerpcb中本身自带有特性阻抗计算的功能,用法如下: 在setup/layer definition中把需要定义为地或电源层相应层定义为CAM PLANE。并在layer thinkness中输入你的层叠的结构,比如各层的厚度、板材的介电常数等。通过以上的设置,选定某一根网络并按CTRL+Q,就可以看到该网络相关的特性阻抗、延时等。 2.关于在powerpcb中快速删除已经定义的地或电源铜皮框的方法: 第一步:将要删除的铜皮框移出板外。 第二步:对移出板外的铜皮框重新进行灌水。 第三步:将铜皮框的网络重新定义为none,然后删除。 3.关于在powerpcb中会速绕线的方法: 第一步:在setup/preferences面板的design下的miters中设置为arc,且ratio为3.5。 第二步:布直角的线。 第三步:按着shift点线,选中后,右键点出菜单,选中add miters命令即可很快画出绕线 4.下面我在一个在powerpcb4.0中应该注意的一个问题: 一般情况下,产品的外框均是通过*.dxf的文件导入。但是pcb文件导入*.dxf文件后很容易出现数据库错误,给以后的设计买下祸根。好的处理办法是:把*.dxf文件导入一个新的pcb文件中,然后从这个pcb文件中copy所需的text、line到设计设计的pcb文件中,这样不会破坏设计的pcb 文件的数据。 5.四层板删除layer2、layer3层,变成2层板的做法如下: 第一步:删除layer2层的电特性数据,包括走在该层的traces、copper、via。 第二步:删除layer2层的电特性数据,包括走在该层的traces、copper、via。 第三步:进入菜单setup/Layer Definition面板。在Electrical layers栏中点击modify按钮。在弹出的对话框中输入2。如果layer2、layer3已经没有电特性数据,那么4层就变成2层板了。如果layer2、layer3已经还有电特性数据,会出现一个警告说layer2、layer3已经还有电特性数据。按第一、第二步骤删除它,再进入第三步。 第四步:将原先布在layer2、layer3的相关部分布到top、bottom层即可。 6. 删除铜皮还有一个方法: 第一步:选择FILTER用SHAPE 第二步:框住要删除的铜皮 第三步:按DEL键,零碎的铜皮就变成了一个框(加铜皮的时候定义的)再按DEL键,框也没有了,完成删除。特别适合整块删除的操作 7. power pcb3.5版本的library怎么转到power pcb4.0中? 在POWERPCB的目录下找到Libconv4.exe文件。运行它,按要求输入power pcb3.5的库文件就可以转为power pcb4.0库了。 8.在PowerPCB中做椭圆形孔的方法: 第一步:选择要改变的孔右击如图1所示的选择Query/Modify 第二步:点击pad stack进入图2,选上Slotte,就可以的孔长度进行设置。

FPGA试卷+答案+超详细解答

20XX—20XX学年度第(X)学期期末考试试卷科目:<

3.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是___C___。 A.FPGA是基于乘积项结构的可编程逻辑器件; (FPGA芯片基于查找表的可编程逻辑结构) B.FPGA是全称为复杂可编程逻辑器件; (FPGA 现场可编程逻辑门阵列,CPLD才是复杂可编程逻辑器件) C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置; D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。 (MAX7000系列属CPLD结构) 4.进程中的变量赋值语句,其变量更新是___A___。 (变量(variable)是立即完成的,信号(signal)有延时) A.立即完成; B.按顺序完成; C.在进程的最后完成; D.都不对。 5.VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述___D___。(结构体实现实体的功能,通过对实体的逻辑功能进行描述) A.器件外部特性; B.器件的综合约束; C.器件外部特性与内部功能; D.器件的内部功能。 6.CASE语句是___A___。(case语句时顺序语句中最重要最常用的顺序语句) A. 顺序语句 B. 并行语句 C. 其它 D.组合逻辑控制电路语句 7. LIBRARY ___A___; --库的声明 USE IEEE.STD_LOGIC_1164.ALL; --库的引用,引用IEEE库中的std_logic_1164中的所有项目A. IEEE B. STD C.WORK D.ENTITY counter IS

国家税务总局文件

国家税务总局文件 国税发…2008?93号 国家税务总局关于印发 《纳税人涉税保密信息管理暂行办法》的通知 各省、自治区、直辖市和计划单列市国家税务局、地方税务局:为维护纳税人合法权益,完善税务机关对纳税人涉税信息资料的保密管理制度,规范税务机关受理外部门查询纳税人涉税保密信息的程序,根据《中华人民共和国税收征收管理法》及其实施细则,税务总局制定了《纳税人涉税保密信息管理暂行办法》。现印发给你们,请认真遵照执行。在执行过程中遇到的问题,请及时报告税务总局(纳税服务司)。 附件:纳税人、扣缴义务人涉税保密信息查询申请表 二○○八年十月九日 — 1 —

纳税人涉税保密信息管理暂行办法 第一章总则 第一条为维护纳税人的合法权益,规范对纳税人涉税保密信息管理工作,根据《中华人民共和国税收征收管理法》和《中华人民共和国税收征收管理法实施细则》及相关法律、法规的规定,制定本办法。 第二条本办法所称纳税人涉税保密信息,是指税务机关在税收征收管理工作中依法制作或者采集的,以一定形式记录、保存的涉及到纳税人商业秘密和个人隐私的信息。主要包括纳税人的技术信息、经营信息和纳税人、主要投资人以及经营者不愿公开的个人事项。 纳税人的税收违法行为信息不属于保密信息范围。 第三条对于纳税人的涉税保密信息,税务机关和税务人员应依法为其保密。除下列情形外,不得向外部门、社会公众或个人提供: (一)按照法律、法规的规定应予公布的信息; (二)法定第三方依法查询的信息; (三)纳税人自身查询的信息; (四)经纳税人同意公开的信息。 — 2 —

第四条根据法律、法规的要求和履行职责的需要,税务机关可以披露纳税人的有关涉税信息,主要包括:根据纳税人信息汇总的行业性、区域性等综合涉税信息、税收核算分析数据、纳税信用等级以及定期定额户的定额等信息。 第五条各级税务机关应指定专门部门负责纳税人涉税非保密信息的对外披露、纳税人涉税保密信息查询的受理和纳税人涉税保密信息的对外提供工作。要制定严格的信息披露、提供和查询程序,明确工作职责。 第二章涉税保密信息的内部管理 第六条在税收征收管理工作中,税务机关、税务人员应根据有关法律、法规规定和征管工作需要,向纳税人采集涉税信息资料。 第七条税务机关、税务人员在税收征收管理工作各环节采集、接触到纳税人涉税保密信息的,应当为纳税人保密。 第八条税务机关内部各业务部门、各岗位人员必须在职责范围内接收、使用和传递纳税人涉税保密信息。 对涉税保密信息纸质资料,税务机关应明确责任人员,严格按照程序受理、审核、登记、建档、保管和使用。 对涉税保密信息电子数据,应由专门人员负责采集、传输和储存、分级授权查询,避免无关人员接触纳税人的涉税保密信息。 — 3 —

ARM嵌入式系统开发与应用课后题答案与习题

课后题答案:第一章 1.写出下列英文缩写的英文原文及中文含义。 RAM随机存储器 DRAM动态随机存储器 ROM只读存储器 PROM可编程只读存储器 EPROM可插除可编程只读存储器 CANCAN总线 RTOS实时操作系统 SOPC片上可编程系统 ICE硬件调试器 FI快速终端请求 EEPROM电可插除可编程只读存储器 API应用程序接 DMA直接内存存取 RISC精简指令集计算机 SPI串行万维指令 MMU存储管理单元 UART异步接受发送装置 ARM先进RISC存储器 SWI软件终端指令 2、什么是嵌入式系统? P3 嵌入式系统是用于检测、控制、辅助、操作机械设备的装置。以应用为中心,一计算机技术为基础,软硬件可裁剪,适应应用系统对功能、可靠性、成本、体积和功耗等严格要求的专用计算机系统。 3、是比较嵌入式系统与通用PC的区别。P3 (1)嵌入式系统是专用的计算机系统,而PC是通用的计算机系统。 (2)技术要求不同,通用PC追求高速、海量的数据运算;嵌入式要求对象体系的智能化控制。(3)发展方向不同,PC追求总线速度的不断提升,存储容量不断扩大;嵌入式追求特定对象系统的智能性,嵌入式,专用性。 4、嵌入式体统有哪些部分组成?简单说明各部分的功能与作用 (1)硬件层是整个核心控制模块(由嵌入式微处理器、存储系统、通信模块、人机接口、其他I/O 接口以及电源组成),嵌入式系统的硬件层以嵌入式微处理器为核心,在嵌入式微处理器基础上增加电源电路、时钟电路、和存储器电路(RAM和ROM等),这就构成了一个嵌入式核心控制模块,操作系统和应用程序都可以固化在ROM中。 (2)中间层把系统软件与底层硬件部分隔离,使得系统的底层设备驱动程序与硬件无关。一般包括硬件抽象层(Hardware Abstract Layer,HAL)和板级支持包(Board Support Package,BSP)。(3)软件层由实时操作系统(Real Time Operating System,RTOS)、文件系统、图形用户接口(Graphical User Interfaces,GUI)、网络组件组成。 (4)功能层是面向被控对象和用户的,当需要用户操作是往往需要提供一个友好的人机界面。 5、什么是可编程片上系统?在技术上它有哪些特点? 用可编程逻辑技术把整个系统放到一块硅片上,称作可编程片上系统SOPC,特点如下:实现复杂系统功能的VLSI;采用超深亚微米工艺技术;使用一个以上的嵌入式处理器/DSP;外部可对芯片进行编程;主要采用第三方IP进行设计;足够的片上可编程逻辑资源;具有处理器调试接口和FPGA编程接口;可能包含部分可编程模拟电路;单芯片,低功耗,微封装;微处理器/dsp以ip核的形式方便的嵌入在FPGA中。 6、什么是嵌入式外围设备?简要说明嵌入式外围设备是如何分类的。 嵌入式外围设备,是指在一个嵌入式系统硬件构成中,除了核心控制部件-----嵌入式微处理器/DSP 以外的各种存储器,输入/输出接口、人机接口的显示器/键盘、串行通信接口等。根据外围设备的功能可分为以下五类:存储器类型;通信接口;输入/输出设备;设备扩展接口;电源及辅助设备。 7、.简述嵌入式系统软件的组成和功能? 组成:应用层,OS层,BSP层 11、什么是软硬件协同设计?他最大的特点是什么?嵌入式系统开发为什么可以采用这种方法进行。嵌入式是系统设计时使用一组物理硬件和软件来完成所需功能的过程。系统是指任何由硬件,软件或者两者的结合来构成的功能设备。由于嵌入式系统是一个专用系统,所以在嵌入式产品的设计过程中,软件设计和硬件设计是紧密结合的、相互协调的;特点是:在设计时从系统功能的是先考虑,把实现时的软硬件同时考虑进去,硬件设计包括芯片级“功能定制”设计。这样既可最大限度的利用有效资源,缩短开发周期,又能取得更好的设计效果。 第二章 1、CISC与RISC分别指什么?说明他们各自有什么特点,应用领域和发展趋势如何? 复杂指令集CPU内部为将较复杂的指令译码,也就是指令较长,分成几个微指令去执行,正是如此开发程序比较容易(指令多的缘故),但是由于指令复杂,执行工作效率较差,处理数据速度较慢,PC 中 Pentium的结构都为CISC CPU。 RISC是精简指令集CPU,指令位数较短,内部还有快速处理指令的电路,使得指令的译码与数据的处理较快,所以执行效率比CISC高,不过,必须经过编译程序的处理,才能发挥它的效率,我所知道的IBM的 Power PC为RISC CPU的结构,CISCO 的CPU也是RISC的结构。 RISC与CISC的主要特征对比 比较内容 CISC RISC 指令系统复杂,庞大简单,精简 指令数目一般大于200 一般小于100 指令格式一般大于4 一般小于4 寻址方式一般大于4 一般小于4 指令字长不固定等长 可访存指令不加限制只有LOAD/STORE指令 各种指令使用频率相差很大相差不大

FPGA试卷+答案+超详细解答

广东技术师范学院电子与信息学院10应用电子技术教育2班 20XX—20XX学年度第(X)学期期末考试试卷科目:<

3.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是___C___。 A.FPGA是基于乘积项结构的可编程逻辑器件; (FPGA芯片基于查找表的可编程逻辑结构) B.FPGA是全称为复杂可编程逻辑器件; (FPGA 现场可编程逻辑门阵列,CPLD才是复杂可编程逻辑器件) C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置; D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。 (MAX7000系列属CPLD结构) 4.进程中的变量赋值语句,其变量更新是___A___。 (变量(variable)是立即完成的,信号(signal)有延时) A.立即完成; B.按顺序完成; C.在进程的最后完成; D.都不对。 5.VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述___D___。(结构体实现实体的功能,通过对实体的逻辑功能进行描述) A.器件外部特性; B.器件的综合约束; C.器件外部特性与内部功能; D.器件的内部功能。 6.CASE语句是___A___。(case语句时顺序语句中最重要最常用的顺序语句) A. 顺序语句 B. 并行语句 C. 其它 D.组合逻辑控制电路语句 7.LIBRARY ___A___; --库的声明 USE IEEE.STD_LOGIC_1164.ALL; --库的引用,引用IEEE库中的std_logic_1164中的所有项目A. IEEE B. STD C.WORK D.ENTITY counter IS

FPGA笔试题及答案总结

第 1 章 FPGA基础知识 1.1 FPGA设计工程师努力的方向 SOPC,高速串行I/O,低功耗,可靠性,可测试性和设计验证流程的优化等方面。随着芯片工艺的提高,芯片容量、集成度都在增加,FPGA 设计也朝着高速、高度集成、低功耗、高可靠性、高可测、可验证性发展。芯片可测、可验证,正在成为复杂设计所必备的条件,尽量在上板之前查出bug,将发现bug的时间提前,这也是一些公司花大力气设计仿真平台的原因。另外随着单板功能的提高、成本的压力,低功耗也逐渐进入FPGA设计者的考虑范围,完成相同的功能下,考虑如何能够使芯片的功耗最低。高速串行IO的应用,也丰富了FPGA 的应用范围,象xilinx的v2pro中的高速链路也逐渐被应用。总之,学无止境,当掌握一定概念、方法之后,就要开始考虑FPGA其它方面的问题了。 1.2 简述FPGA等可编程逻辑器件设计流程 系统设计电路构思,设计说明与设计划分,电路设计与输入(HDL代码、原理图),功能仿真与测试,逻辑综合,门级综合,逻辑验证与测试(综合后仿真),布局布线,时序仿真,板级验证与仿真,加载配置,在线调试。常用开发工具(Altera FPGA) HDL语言输入:Text Editor(HDL语言输入),还可以使用Ultra Edit 原理图输入:Schematic Editor IP Core输入:MegaWinzad 综合工具:Synplify/Synplify Pro,Qaustus II内嵌综合工具仿真工具:

ModelSim 实现与优化工具:Quartus II集成的实现工具有Assignment Editor(约束编辑器)、LogicLock(逻辑锁定工具)、PowerFit Fitter(布局布线器)、Timing Analyzer(时序分析器,STA分析工具)、Floorplan Editor(布局规划器)、Chip Editor(底层编辑器)、Design Space Explorer(设计空间管理器)、Design Assistant(检查设计可靠性)等。后端辅助工具:Assembler(编程文件生成工具),Programmer(下载编程工具),PowerGauge(功耗仿真器) 调试工具:SignalTap II(在线逻辑分析仪),SignalProbe(信号探针)。系统级设计环境:SOPC Builder,DSP Builder,Software Builder。 1.3 Quartus文件管理 1. 编译必需的文件:设计文件(.gdf、.bdf、EDIF输入文件、.tdf、verilog 设计文件、.vqm、.vt、VHDL设计文件、. vht)、存储器初始化文件(.mif、.rif、.hex)、配置文件(.qsf、.tcl)、工程文件(.qpf)。 2. 编译过程中生成的中间文件(.eqn文件和db目录下的所有文件.tdf,.hdb,.xml等) 3. 编译结束后生成的报告文件(.rpt、.qsmg 等) 4. 根据个人使用习惯生成的界面配置文件(.qws等) 5. 编程文件(.sof、.pof、.ttf等) 1.4 IC设计流程

PADS POWERPCB常用快捷键

POWERPCB常用快捷键 1.如改变当前层时,只要从键盘上输入快捷命令L、然后输入新的布线层(如数字2)再再输入回车键即可完成。2.C 补充格式,在内层负片设计时用来显示Plane 层的焊盘及Thermal。 使用方法是,从键盘上输入C 显示,再次输入C 可去除显示。 3.打开/关闭当前层显示,从键盘上输入D 来切换。 4.DO 贯通孔外形显示切换。ON时孔径高亮显示,焊盘则以底色调显示。键盘上输入DO来切换。 5.E 布线终止方式切换,可在下列3种方式间切换。 End No Via 布线时Ctrl+点击时配线以无VIA 方式终止 End Via 布线时Ctrl+点击时配线以VIA 方式终止 End Test Point 布线时Ctrl+点击时配线以测试PIN 的VIA 方式终止 6.I 数据库完整性测试,设计过程中发现系统异常时,可试着敲此键。 7.N 用来让NET 高亮显示,为要显示的信号名。可以堆栈方式逐个显 示信号,如N GND 会高亮显示整个GND。 N-会逐个去除信号 N 将会去除所有的高亮信号 8.O 选择用外形线来显示焊盘与配线。 9.PO 自动敷铜外形线on/off 切换。 10.Q 快速测量命令。可以快速.测量dx,dy 和d 。注意精确测量时将状态框中的Snaps to the design grid 取消。11.QL 快速测量配线长度。可对线段、网络、配线对进行测量。 测量方式如下:首先选择线段、网络或者配线对,然后输入QL 就会得到相关长度报告。 12.R 改变显示线宽到, 如, R 50。 13.RV 在输出再使用文件Reuse 时,用于切换参数设定。有关详细信息请参 见"To Make a Like Reuse in Object Mode" SPD 显示split/mixed planes 层数据,该命令控制split/mixed planes 参数对话框中的一个参数。 SPI 显示plane 层的thermal 。该命令控制split/mixed planes 参数对话框中的一个参数。 SPO 显示split/mixed planes 层的外形线。该命令控制split/mixed planes参数对话框中的一个参数。 T 透明显示切换。在复杂板子设计时很有用。 Text 文字外形线显示切换。 W 改变线宽到,如W 5 。 14.G {} Grid 全局设定,第二个参数为可选项。可同时改变设计与VIA Grid。如G25 或者G25 25。 15.GD {} 屏幕上的显示Grid 设定。第二个参数为可选项。如GD25 25 或者GD100。 GP 切换极坐标grid 。极坐标grid 在设计外形为圆形、或者元件布局按 极坐标方式放置时使用。 GP r a 极坐标下的元件指定移动方式(r 为半径,a 为角度)。 GPR r 极坐标下的元件指定移动方式,在角度不变时,改变到半径r。 GPA a 极坐标下的元件指定移动方式,在半径不变时,改变到角度a。 GPRA da 极坐标下的元件指定移动方式,在半径不变时,改变到当前角度da GPRR dr 极坐标下的元件指定移动方式,在角度不变时,改变到当前半径r。 GR 设计grid 设定, 如GR 8-1/3, GR 25 25, G 25 。 GV 贯通孔Via grid 设定, 如GV 8-1/3, GV 25 25, or GV 25 。 检索命令 16.S 检索元件参照名或是端子,如S U1 、S U1.1 S 检索绝对坐标,如S 1000 1000。 SR 检索相对坐标X 与Y, 如SR -200 100 。

Altium Designer 导入powerPCB中的pcb文件

怎么把powerPCB中的.pcb转到protel中的.pcb? 关于此问题,在这里提供几个方法给你。 如果用户现有的是Protel99SE 。ProtelDXP,Protel2004版本: 1在powerpcb 软件的中打开PCB文件,选择导出ASCII文件(export ascii file),ascii file的版本应该选择3.5 及以下的版本。 2 a在Protel99SE 。ProtelDXP ,选择 File->Import->在出现的对话框中,选择文件类型中的PADS Ascil Files (*.ASC)输入对应文件即可 1.powerpcb-->export ascii file--->import ascii file with protel99 se sp5(u must install padsimportor that is an add-on for 99sesp5 which can downloan from protel company ). 2.powerpcb-->export ascii file-->import ascii file in orcad layout-->import max file(orcad pcb file)with protel 99 or 99se. 要注意: 1 Protel2004版本中选择 File->Open ->在出现的对话框中,选择文件类型中的PADS PCB Files (*.ASC)输入对应文件即可 . 2 在Protel的最新版本Altium Designer 6.0(简称AD6)版本中选择 File->Import Wizard ?Next-> PADS Ascil PCB (*.ASC) ?Next->再选择要打开的 PowerPCB 导出的PADS Ascil PCB文件。 现在,AD6 支持的POWERPCB 的Ascil 文件的版本有: POWERPCB V1 POWERPCB V1.5 POWERPCB V2 POWERPCB V3.0 POWERPCB V3.5 POWERPCB V4.0 POWERPCB V5.0 POWERPCB V2005.0 PADS-PCB

2020年智慧树知道网课《EDA技术》课后章节测试满分答案

绪论单元测试 1 【多选题】(10分) 学习EDA技术这门课程的具体要求是() A. 初步掌握基于FPGA的VLSI系统设计与实现的方法和技术,具备分析、解决实际问题的能力,具有较强的专业实践能力和创新能力。 B. 较好地掌握应用EDA技术进行系统设计开发的方法,具备应用EDA技术进行综合性数字系统设计的初步能力,经过后续的综合应用实践,能够从事FPGA的设计与开发、SOPC的设计与开发以及ASIC的前端设计等工作。 C. 掌握EDA技术的基本概念、基础知识;了解FPGA/CPLD的结构、工作原理、性能指标及应用选择;熟练掌握硬件描述语言VHDL的编程;熟练掌握EDA技术的开发软件及EDA实验开发系统的使用。 2 【多选题】(10分) 学习EDA技术这门课程,我们希望达到的学习目标是() A. 基本掌握ASIC的后端设计与开发 B. 基本掌握ASIC的前端设计与开发 C. 掌握一种硬件描述语言VHDL D.

基本掌握SOC的设计与开发方法 E. 基本掌握SOPC的设计与开发方法 F. 熟悉FPGA的设计与开发 3 【多选题】(10分) EDA技术课程的学习要点是() A. 以课题为中心,以研究式教学为主要形式 B. 抓住一个重点(硬件描述语言编程) C. 掌握两个工具(FPGA/CPLD开发软件、EDA实验开发系统的使用) D. 运用四种手段(案例分析、应用设计、线上学习、上机实践) E. 采用五个结合(边学边用相结合、边用边学相结合、理论与实践相结合、线上与线下相结合、课内与课外相结合)

第一章测试 1 【单选题】(10分) EDA的中文含义是() A. 计算机辅助工程设计 B. 计算机辅助设计 C. 电子设计自动化 2 【判断题】(10分) 狭义的EDA技术,就是指以大规模可编程逻辑器件为设计载体,以硬件描述语言为系统逻辑描述的主要表达方式,以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具,通过有关的开发软件,自动完成用软件方式设计的电子系统到硬件系统的逻辑编译、逻辑化简、逻辑分割、逻辑综合及优化、逻辑布局布线、逻辑仿真,直至对于特定目标芯片的适配编译、逻辑映射、编程下载等工作,最终形成集成电子系统或专用集成芯片的一门新技术,或称为IES/ASIC自动设计技术。 A. 对 B. 错

POWERPCB常用快捷键和一些技巧

POWERPCB常用快捷键和一些技巧 1.移动元件时可按TAB键翻转。 2.加任何形状的孔(包括方形元件脚):可在24层用二维线画。 3.加裸铜(即阻焊,在加大导通电流和增加焊接附着力时经常用到)用铺铜功能在28层加。 4.把当前PCB板用到的元件封装存入自已的库:圈住所有元件按右键选SAVE TO LIB...,再选所需的库即可.(把别人的库占为已有算是不费吹灰之力) 5.在POWERPCB把二维线图形存入库:先用二维线功能画好所需的图形(可加上文字)把它们全部圈住按右键选SAVE TO LIB...,再选所需的库即可.(方便日后调用) 在POWERPCB中,将两块板合并成一块板的方法: 1.打开要复制的线路板文件,打开ECO模式 2.全选(可用单击鼠标右键选择SELECT ALL) 3.复制 4.打开复制到的线路板文件,打开ECO模式 5.粘帖 6.移动到合适位置 7. OK! POWERPCB常用快捷键 PowerPCB 为用户提供了一套快捷命令。快捷命令主要用于那些在设计过程需频繁更改设 定的操作,如改变线宽、布线层、改变设计Grid 等都可以通过快捷命令来实现。 快捷命令命令的操作方法如下:从键盘上输入命令字符串,按照格式输入数值,然后再输入 回车键即可。 如改变当前层时,只要从键盘上输入快捷命令L、然后输入新的布线层(如数字2)最后再 再输入回车键即可完成,非常方便。 全局设置命令 命令字符命令含义及用途 C 补充格式,在内层负片设计时用来显示Plane 层的焊盘及Thermal。 使用方法是,从键盘上输入C 显示,再次输入C 可去除显示。 D 打开/关闭当前层显示,使用方法是,从键盘上输入D 来切换。建议设 计时用D 将Display Current Layer Last=ON的状态下。 . DO 贯通孔外形显示切换。ON时孔径高亮显示,焊盘则以底色调显示。 使用方法是,从键盘上输入DO来切换。 E 布线终止方式切换,可在下列3种方式间切换。 End No Via 布线时Ctrl+点击时配线以无VIA 方式终止 End Via 布线时Ctrl+点击时配线以VIA 方式终止 End Test Point 布线时Ctrl+点击时配线以测试PIN 的VIA 方式终止 使用方法是,从键盘上输入E 来切换。 I 数据库完整性测试,设计过程中发现系统异常时,可试着敲此键。 L 用来让NET 高亮显示,为要显示的信号名。可以堆栈方式逐个显 示信号,如N GND 会高亮显示整个GND。 N-会逐个去除信号 N 将会去除所有的高亮信号 O