12V1A内置MOS OB2538

Revision History

-

B r

i g h

t i n t e

r

a l

u s e

o l y

Bottom

Bottom

Top

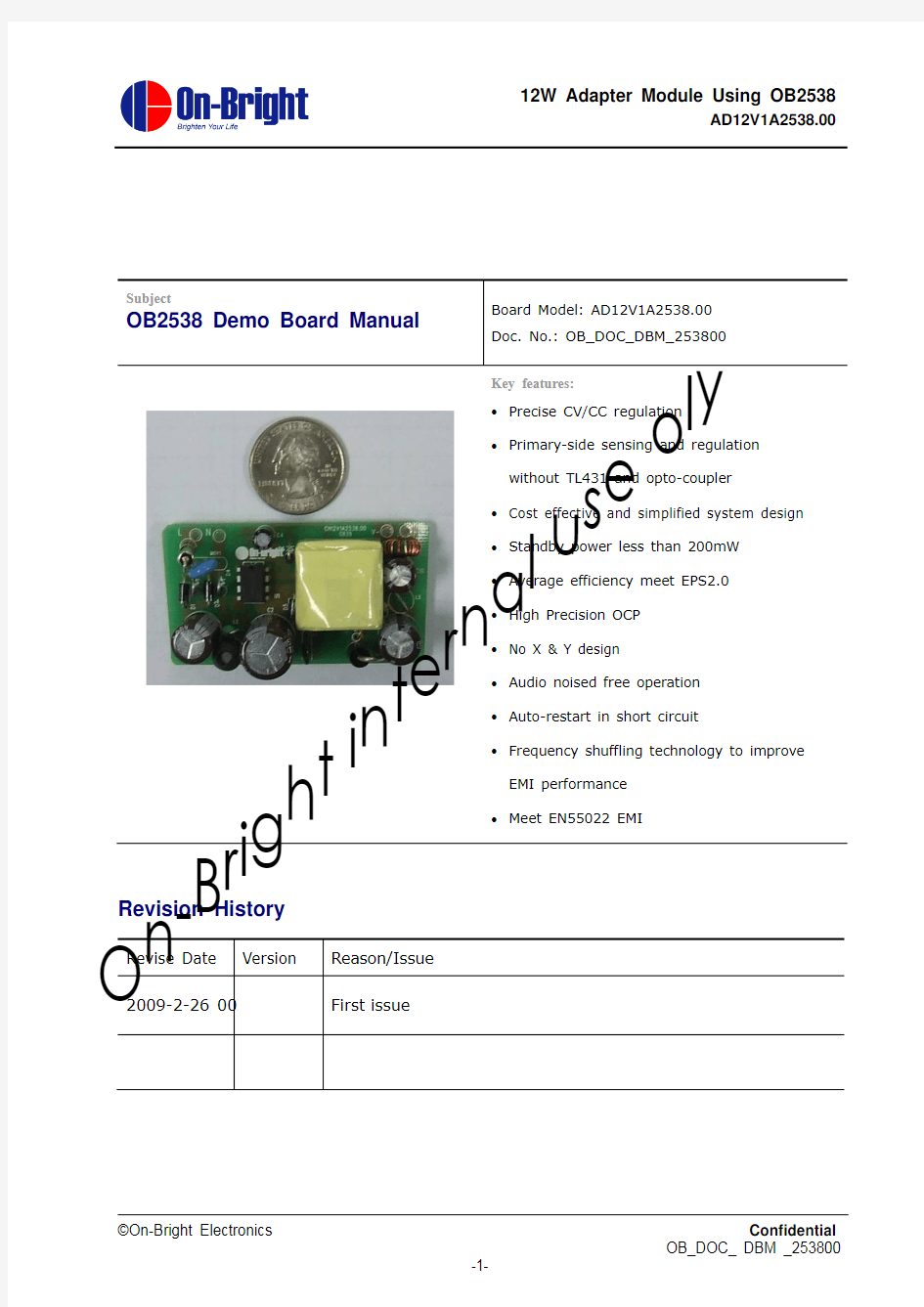

2.4. Adapter Module Snapshot

O

n -

B r

i g h

t i n

t e

r e

o l y

Winging Start Remark

N1 0.21N2 0.21TAPE TAPE W=12mm (Y)

2 Copper W 12mm 4 1.1

TAPE TAPE W=12mm (Y)

8 N3 0.50 Φ*1 triple insulated wire 16 TAPE TAPE W=12mm (Y) 2 N6 0.18*3 2UEW

TAPE TAPE W=12mm (Y) Copper Outcopper W 11mm TAPE

TAPE W=12mm (Y)

O

n -

B r

i g

h

t i n

t e

r n

a

264Vac/50HZ 172

11.860

Fig. 1 No-load Input Power vs. Input Line Voltage

3.1.2. Efficiency

25% 50% 75% 100% Aver. Eff. 115Vac/60HZ 78.74 80.58 80.39 79.94 79.91230Vac/50HZ 76.92

79.84

80.86

80.83

79.61Fig. 2 Efficiency vs. Percent of Rated Output Power

B r

i g h

t i n

t e

r n a l

u s e

o

Fig. 3 Measured ripple& noise waveform@90Vac/60HZ, no

load

Fig. 4 Measured ripple& noise waveform@90Vac/60HZ, full load

O

n -

B r

i g h

t i n

t

Fig. 5 Measured ripple& noise waveform@264Vac/50HZ, no load Fig. 6 Measured ripple& noise waveform@264Vac/50HZ, full load

3.2.3. Over Shoot & Under Shoot

Over shoot and under shoot were measured under below conditions. a. AC input switch on for over shoot and off for under shoot. b. Input voltage ranges from 90Vac/60HZ~264Vac/50HZ. Table. 5 Over shoot & under shoot measurement results

Input load

Remark over shoot Fig. 8 Full load

Fig. 7 Measured overshoot waveform@90Vac/60HZ, full load

O

n -

B r n a l

u

s e

o l y

O

n -

B r

i g h

t i n

o l y

Fig. 13 Turn on delay time measured waveform @100Vac/60HZ,full load

Fig. 14 Turn on delay time measured waveform @240Vac/50HZ,full load

Fig. 15 Hold-up time measured waveform@100Vac/60HZ,full load

Fig. 16 Rise time measured waveform@100Vac/60HZ,full load

O

n -

B r

i g h

t i n

t e

r n a l

u s e

o

Fig. 19 Fall time measured waveform@240Vac/50HZ,full load

3.3. EMI Test

The Power supply passed EN55022 Class B EMI requirement with more than 6dB margin O

n -

B r

i g h

t i n

t e

r n o l y

O

n -

B r

i g h

t i n

t e

r n a l

u s e

o l y

O

n -

B r

i g h

t i n

t e

r n a l

u s e

o l y

O

n -

B r

i g h

t i n

t e

r n a l

u s e

o l y

removed.

Fig. 20 Output short, Vdd 、Cs 、Vds waveform@90 Vac/60Hz, full load Fig. 21 Output short, Vdd 、Cs 、Vdd waveform@264 Vac/50Hz,

full load

4.3. Open Loop Protection

Table. 9 OLP @ Full load

Input OLP Protection

115Vac/60Hz OK 230Vac/50Hz OK

4.4. Over Current Protection

Table. 10 Over current Protection Input OCP Current

B r

i g h

t i n

t e

r n a l

u s e

o l y

a l

u s e

o l y

MOS管的结构和工作原理

在P 型衬底上,制作两个高掺杂浓度的N 型区,形成源极(Source )和漏极(Drian ),另外一个是栅极(Gate ).当Vi=Vgs

MOS管工作原理及芯片汇总

MOS管工作原理及芯片汇总 一:MOS管参数解释 MOS管介绍 在使用MOS管设计开关电源或者马达驱动电路的时候,一般都要考虑MOS的导通电阻,最大电压等,最大电流等因素。 MOSFET管是FET的一种,可以被制造成增强型或耗尽型,P沟道或N沟道共4种类型,一般主要应用的为增强型的NMOS管和增强型的PMOS管,所以通常提到的就是这两种。 这两种增强型MOS管,比较常用的是NMOS。原因是导通电阻小且容易制造。所以开关电源和马达驱动的应用中,一般都用NMOS。 在MOS管内部,漏极和源极之间会寄生一个二极管。这个叫体二极管,在驱动感性负载(如马达),这个二极管很重要,并且只在单个的MOS管中存在此二极管,在集成电路芯片内部通常是没有的。 MOS管的三个管脚之间有寄生电容存在,这不是我们需要的,而是由于制造工艺限制产生的。寄生电容的存在使得在设计或选择驱动电路的时候要麻烦一些,但没有办法避免。 MOS管导通特性 导通的意思是作为开关,相当于开关闭合。 NMOS的特性,Vgs大于一定的值就会导通,适合用于源极接地时的情况(低端驱动),只要栅极电压达到一定电压(如4V或10V, 其他电压,看手册)就可以了。PMOS的特性,Vgs小于一定的值就会导通,适合用于源极接VCC时的情况(高端驱动)。但是,虽然PMOS可以很方便地用作高端驱动,但由于导通电阻大,价格贵,替换种类少等原因,在高端驱动中,通常还是使用NMOS。 MOS开关管损失 不管是NMOS还是PMOS,导通后都有导通电阻存在,因而在DS间流过电流的同时,两端还会有电压,这样电流就会在这个电阻上消耗能量,这部分消耗的能量叫做导通损耗。选择导通电阻小的MOS管会减小导通损耗。现在的小功率M OS管导通电阻一般在几毫欧,几十毫欧左右 MOS在导通和截止的时候,一定不是在瞬间完成的。MOS两端的电压有一个下降的过程,流过的电流有一个上升的过程,在这段时间内,MOS管的损失是电压和电流的乘积,叫做开关损失。通常开关损失比导通损失大得多,而且开关频率越快,导通瞬间电压和电流的乘积很大,造成的损失也就很大。降低开关时间,可以减小每次导通时的损失;降低开关频率,可以减小单位时间内的开关次数。这两种办法都可以减小开关损失。 MOS管驱动 MOS管导通不需要电流,只要GS电压高于一定的值,就可以了。但是,我们还需要速度。

西安电子科技大学2018考研大纲:半导体物理与器件物理.doc

西安电子科技大学2018考研大纲:半导体 物理与器件物 出国留学考研网为大家提供西安电子科技大学2018考研大纲:801半导体物理与器件物理基础,更多考研资讯请关注我们网站的更新! 西安电子科技大学2018考研大纲:801半导体物理与器件物理基础 “半导体物理与器件物理”(801) 一、 总体要求 “半导体物理与器件物理”(801)由半导体物理、半导体器件物理二部分组成,半导体物理占60%(90分)、器件物理占40%(60分)。 “半导体物理”要求学生熟练掌握半导体的相关基础理论,了解半导体性质以及受外界因素的影响及其变化规律。重点掌握半导体中的电子状态和带、半导体中的杂质和缺陷能级、半导体中载流子的统计分布、半导体的导电性、半导体中的非平衡载流子等相关知识、基本概念及相关理论,掌握半导体中载流子浓度计算、电阻(导)率计算以及运用连续性方程解决载流子浓度随时间或位置的变化及其分布规律等。 “器件物理”要求学生掌握MOSFET器件物理的基本理

论和基本的分析方法,使学生具备基本的器件分析、求解、应用能力。要求掌握MOS基本结构和电容电压特性;MESFET器件的基本工作原理;MOSFET器件的频率特性;MOSFET器件中的非理想效应;MOSFET器件按比例缩小理论;阈值电压的影响因素;MOSFET的击穿特性;掌握器件特性的基本分析方法。 “半导体物理与器件物理”(801)研究生入学考试是所学知识的总结性考试,考试水平应达到或超过本科专业相应的课程要求水平。 二、 各部分复习要点 ●“半导体物理”部分各章复习要点 (一)半导体中的电子状态 1.复习内容 半导体晶体结构与化学键性质,半导体中电子状态与能带,电子的运动与有效质量,空穴,回旋共振,元素半导体和典型化合物半导体的能带结构。 2.具体要求 半导体中的电子状态和能带 半导体中电子的运动和有效质量 本征半导体的导电机构

MOS管工作原理及其驱动电路

功率场效应晶体管MOSFET 技术分类:电源技术模拟设计 | 2007-06-07 来源:全网电子 1.概述 MOSFET的原意是:MOS(Metal Oxide Semiconductor金属氧化物半导体),FET(Field Effect Transistor场效应晶体管),即以金属层(M)的栅极隔着氧化层(O)利用电场的效应来控制半导体(S)的场效应晶体管。 功率场效应晶体管也分为结型和绝缘栅型,但通常主要指绝缘栅型中的 MOS型(Metal Oxide Semiconductor FET),简称功率MOSFET(Power MOSFET)。结型功率场效应晶体管一般称作静电感应晶体管(Static Induction Transistor——SIT)。其特点是用栅极电压来控制漏极电流,驱动电路简单,需要的驱动功率小,开关速度快,工作频率高,热稳定性优于GTR,但其电流容量小,耐压低,一般只适用于功率不超过10kW的电力电子装置。 2.功率MOSFET的结构和工作原理 功率MOSFET的种类:按导电沟道可分为P沟道和N沟道。按栅极电压幅值可分为;耗尽型;当栅极电压为零时漏源极之间就存在导电沟道,增强型;对于N(P)沟道器件,栅极电压大于(小于)零时才存在导电沟道,功率MOSFET 主要是N沟道增强型。 2.1功率MOSFET的结构 功率MOSFET的内部结构和电气符号如图1所示;其导通时只有一种极性的载流子(多子)参与导电,是单极型晶体管。导电机理与小功率mos管相同,但结构上有较大区别,小功率MOS管是横向导电器件,功率MOSFET大都采用垂直导电结构,又称为VMOSFET(Vertical MOSFET),大大提高了MOSFET 器件的耐压和耐电流能力。

最新尼尔曼第三版半导体物理与器件小结+重要术语解释+知识点+复习题

尼尔曼第三版半导体物理与器件小结+重要术语解释+知识点+复 习题

第一章固体晶体结构 (3) 小结 (3) 重要术语解释 (3) 知识点 (3) 复习题 (3) 第二章量子力学初步 (4) 小结 (4) 重要术语解释 (4) 第三章固体量子理论初步 (4) 小结 (4) 重要术语解释 (4) 知识点 (5) 复习题 (5) 第四章平衡半导体 (6) 小结 (6) 重要术语解释 (6) 知识点 (6) 复习题 (7) 第五章载流子运输现象 (7) 小结 (7) 重要术语解释 (8) 知识点 (8) 复习题 (8) 第六章半导体中的非平衡过剩载流子 (8) 小结 (8) 重要术语解释 (9) 知识点 (9) 复习题 (10) 第七章pn结 (10) 小结 (10) 重要术语解释 (10) 知识点 (11) 复习题 (11) 第八章pn结二极管 (11) 小结 (11) 重要术语解释 (12) 知识点 (12) 复习题 (13) 第九章金属半导体和半导体异质结 (13) 小结 (13) 重要术语解释 (13) 知识点 (14) 复习题 (14) 第十章双极晶体管 (14)

小结 (14) 重要术语解释 (15) 知识点 (16) 复习题 (16) 第十一章金属-氧化物-半导体场效应晶体管基础 (16) 小结 (16) 重要术语解释 (17) 知识点 (18) 复习题 (18) 第十二章金属-氧化物-半导体场效应管:概念的深入 (18) 小结 (19) 重要术语解释 (19) 知识点 (19) 复习题 (20)

第一章固体晶体结构 小结 1.硅是最普遍的半导体材料。 2.半导体和其他材料的属性很大程度上由其单晶的晶格结构决定。晶胞是晶体 中的一小块体积,用它可以重构出整个晶体。三种基本的晶胞是简立方、体心立方和面心立方。 3.硅具有金刚石晶体结构。原子都被由4个紧邻原子构成的四面体包在中间。 二元半导体具有闪锌矿结构,它与金刚石晶格基本相同。 4.引用米勒系数来描述晶面。这些晶面可以用于描述半导体材料的表面。密勒 系数也可以用来描述晶向。 5.半导体材料中存在缺陷,如空位、替位杂质和填隙杂质。少量可控的替位杂 质有益于改变半导体的特性。 6.给出了一些半导体生长技术的简单描述。体生长生成了基础半导体材料,即 衬底。外延生长可以用来控制半导体的表面特性。大多数半导体器件是在外延层上制作的。 重要术语解释 1.二元半导体:两元素化合物半导体,如GaAs。 2.共价键:共享价电子的原子间键合。 3.金刚石晶格:硅的院子晶体结构,亦即每个原子有四个紧邻原子,形成一个 四面体组态。 4.掺杂:为了有效地改变电学特性,往半导体中加入特定类型的原子的工艺。 5.元素半导体:单一元素构成的半导体,比如硅、锗。

半导体物理与器件第四版课后习题答案(供参考)

Chapter 4 4.1 ??? ? ? ?-=kT E N N n g c i exp 2υ ??? ? ??-??? ??=kT E T N N g O cO exp 3003 υ where cO N and O N υ are the values at 300 K. (b) Germanium _______________________________________ 4.2 Plot _______________________________________ 4.3 (a) ??? ? ??-=kT E N N n g c i exp 2υ ( )( )( ) 3 19 19 2 113001004.1108.2105?? ? ????=?T ()()?? ????-?3000259.012.1exp T () 3 382330010912.2105.2?? ? ???=?T ()()()()?? ????-?T 0259.030012.1exp By trial and error, 5.367?T K (b) () 252 12 2105.2105?=?=i n ( ) ()()()()?? ????-??? ???=T T 0259.030012.1exp 30010912.23 38 By trial and error, 5.417?T K _______________________________________ 4.4 At 200=T K, ()?? ? ??=3002000259.0kT 017267.0=eV At 400=T K, ()?? ? ??=3004000259.0kT 034533.0=eV ()()()() 172 22102 210025.31040.11070.7200400?=??= i i n n ? ? ????-??????-???? ??? ?? ??=017267.0exp 034533.0exp 3002003004003 3 g g E E ?? ? ???-=034533.0017267.0exp 8g g E E ()[] 9578.289139.57exp 810025.317-=?g E or ()1714.38810025.3ln 9561.2817=??? ? ???=g E or 318.1=g E eV Now ( ) 3 2 1030040010 70.7?? ? ??=?o co N N υ

详细讲解MOS管工作原理

详细讲解MOSFET管驱动电路 在使用MOS管设计开关电源或者马达驱动电路的时候,大部分人都会考虑MOS的导通电阻,最大电压等,最大电流等,也有很多人仅仅考虑这些因素。这样的电路也许是可以工作的,但并不是优秀的,作为正式的产品设计也是不允许的。 下面是我对MOSFET及MOSFET驱动电路基础的一点总结,其中参考了一些资料,非全部原创。包括MOS管的介绍,特性,驱动以及应用电路。 1,MOS管种类和结构 MOSFET管是FET的一种(另一种是JFET),可以被制造成增强型或耗尽型,P沟道或N沟道共4种类型,但实际应用的只有增强型的N沟道MOS管和增强型的P沟道MOS管,所以通常提到NMOS,或者PMOS指的就是这两种。 至于为什么不使用耗尽型的MOS管,不建议刨根问底。 对于这两种增强型MOS管,比较常用的是NMOS。原因是导通电阻小,且容易制造。所以开关电源和马达驱动的应用中,一般都用NMOS。下面的介绍中,也多以NMOS为主。 MOS管的三个管脚之间有寄生电容存在,这不是我们需要的,而是由于制造工艺限制产生的。寄生电容的存在使得在设计或选择驱动电路的时候要麻烦一些,但没有办法避免,后边再详细介绍。 在MOS管原理图上可以看到,漏极和源极之间有一个寄生二极管。这个叫体二极管,在驱动感性负载(如马达),这个二极管很重要。顺便说一句,体二极管只在单个的MOS管中存在,在集成电路芯片内部通常是没有的。 2,MOS管导通特性 导通的意思是作为开关,相当于开关闭合。

NMOS的特性,Vgs大于一定的值就会导通,适合用于源极接地时的情况(低端驱动),只要栅极电压达到4V或10V就可以了。 PMOS的特性,Vgs小于一定的值就会导通,适合用于源极接VCC 时的情况(高端驱动)。但是,虽然PMOS可以很方便地用作高端驱动,但由于导通电阻大,价格贵,替换种类少等原因,在高端驱动中,通常还是使用NMOS。 3,MOS开关管损失 不管是NMOS还是PMOS,导通后都有导通电阻存在,这样电流就会在这个电阻上消耗能量,这部分消耗的能量叫做导通损耗。选择导通电阻小的MOS管会减小导通损耗。现在的小功率MOS管导通电阻一般在几十毫欧左右,几毫欧的也有。 MOS在导通和截止的时候,一定不是在瞬间完成的。MOS两端的电压有一个下降的过程,流过的电流有一个上升的过程,在这段时间内,MOS管的损失是电压和电流的乘积,叫做开关损失。通常开关损失比导通损失大得多,而且开关频率越快,损失也越大。 导通瞬间电压和电流的乘积很大,造成的损失也就很大。缩短开关时间,可以减小每次导通时的损失;降低开关频率,可以减小单位时间内的开关次数。这两种办法都可以减小开关损失。 4,MOS管驱动 跟双极性晶体管相比,一般认为使MOS管导通不需要电流,只要GS电压高于一定的值,就可以了。这个很容易做到,但是,我们还需要速度。 在MOS管的结构中可以看到,在GS,GD之间存在寄生电容,而MOS管的驱动,实际上就是对电容的充放电。对电容的充电需要一个电流,因为对电容充电瞬间可以把电容看成短路,所以瞬间电流会比较大。选择/设计MOS管驱动时第一要注意的是可提供瞬间短路电流的大小。

半导体物理与器件实验报告

课程实习报告 HUNAN UNIVERSITY 题目:半导体物理与器件 学生姓名:周强强 学生学号:20100820225 专业班级:通信二班 完成日期:2012.12.22

运行结果截图: 2.2 函数(),cos(2/)V x t x t πλω=-也是经典波动方程的解。令03x λ≤≤,请在同一坐标中 绘出x 的函数(),V x t 在不同情况下的图形。 (1)0;(2)0.25;(3)0.5;(4)0.75;(5)t t t t t ωωπωπωπωπ =====。 3.27根据式(3.79),绘制出0.2()0.2F E E eV -≤-≤范围内,不同温度条件下的费米-狄拉克概率函数:()200,()300,()400a T K b T K c T K ===。

4.3 画出a ()硅,b ()锗,c ()砷化镓在温度范围200600K T K ≤≤内的本征载流子浓度曲线 (采用对数坐标)。

4.46 已知锗的掺杂浓度为15 3a =310 cm N -?,d =0N 。画出费米能级相对于本征费米能级的位 置随温度变化 200600)K T K ≤≤(的曲线。

5.20硅中有效状态密度为 19 3/2c 2.8 10()300T N =? 193/2 1..0410() 300 T N ν=? 设迁移率为 3/2 n =1350300T μ-?? ? ?? 3/2 =480300T ρμ-?? ? ?? 设禁带宽带为g =1.12V E e ,且不随温度变化。画出200600K T K ≤≤范围内,本征电导率随绝对温度T 变化的关系曲线。

半导体物理与器件公式以及全参数

半导体物理与器件公式以及参数 KT =0.0259ev N c =2.8?1019N v =1.04?1019 SI 材料的禁带宽度为:1.12ev. 硅材料的n i =1.5?1010 Ge 材料的n i =2.4?1013 GaAs 材料的n i =1.8?106 介电弛豫时间函数:瞬间给半导体某一表面增加某种载流子,最终达到电中性的时间,ρ(t )=ρ(0)e ?(t /τd ),其中τd =?σ,最终通过证明这个时间与普通载流子的寿命时间相比十分的短暂,由此就可以证明准电中性的条件。 E F 热平衡状态下半导体的费米能级,E Fi 本征半导体的费米能级,重新定义的E Fn 是存在过剩载流子时的准费米能级。 准费米能级:半导体中存在过剩载流子,则半导体就不会处于热平衡状态,费米能级就会发生变化,定义准费米能级。 n 0+?n =n i exp (E Fn ?E Fi kT )p 0+?p =n i exp [?(E Fp ?E Fi )kT ] 用这两组公式求解问题。 通过计算可知,电子的准费米能级高于E Fi ,空穴的准费米能级低于E Fi ,对于多子来讲,由于载流子浓度变化不大,所以准费米能级基本靠近热平衡态下的费米能级,但是对于少子来讲,少子浓度发生了很大的变化,所以费米能级有相对比较大的变化,由于注入过剩载流子,所以导致各自的准费米能级都靠近各自的价带。

过剩载流子的寿命: 半导体材料:半导体材料多是单晶材料,单晶材料的电学特性不仅和化学组成相关而且还与原子排列有关系。半导体基本分为两类,元素半导体材料和化合物半导体材料。 GaAs主要用于光学器件或者是高速器件。 固体的类型:无定型(个别原子或分子尺度内有序)、单晶(许多原子或分子的尺度上有序)、多晶(整个范围内都有很好的周期性),单晶的区域成为晶粒,晶界将各个晶粒分开,并且晶界会导致半导体材料的电学特性衰退。 空间晶格:晶格是指晶体中这种原子的周期性排列,晶胞就是可以复制出整个晶体的一小部分晶体,晶胞的结构可能会有很多种。原胞就是可以通过重复排列形成晶体的最小晶胞。三维晶体中每一个等效的格点都可以采用矢量表示为r=pa?+qb?+sc?,其中矢量a?,b?,c?称为晶格常数。晶体中三种结构,简立方、体心立方、面心立方。 原子体密度=每晶胞的原子数每晶胞的体积

半导体物理与器件基础知识

9金属半导体与半导体异质结 一、肖特基势垒二极管 欧姆接触:通过金属-半导体的接触实现的连接。接触电阻很低。 金属与半导体接触时,在未接触时,半导体的费米能级高于金属的费米能级,接触后,半导体的电子流向金属,使得金属的费米能级上升。之间形成势垒为肖特基势垒。 在金属与半导体接触处,场强达到最大值,由于金属中场强为零,所以在金属——半导体结的金属区中存在表面负电荷。 影响肖特基势垒高度的非理想因素:肖特基效应的影响,即势垒的镜像力降低效应。金属中的电子镜像到半导体中的空穴使得半导体的费米能级程下降曲线。附图: 电流——电压关系:金属半导体结中的电流运输机制不同于pn结的少数载流子的扩散运动决定电流,而是取决于多数载流子通过热电子发射跃迁过内建电势差形成。附肖特基势垒二极管加反偏电压时的I-V曲线:反向电流随反偏电压增大而增大是由于势垒降低的影响。 肖特基势垒二极管与Pn结二极管的比较:1.反向饱和电流密度(同上),有效开启电压低于Pn结二极管的有效开启电压。2.开关特性肖特基二极管更好。应为肖特基二极管是一个多子导电器件,加正向偏压时不会产生扩散电容。从正偏到反偏时也不存在像Pn结器件的少数载流子存储效应。 二、金属-半导体的欧姆接触 附金属分别与N型p型半导体接触的能带示意图 三、异质结:两种不同的半导体形成一个结 小结:1.当在金属与半导体之间加一个正向电压时,半导体与金属之间的势垒高度降低,电子很容易从半导体流向金属,称为热电子发射。 2.肖特基二极管的反向饱和电流比pn结的大,因此达到相同电流时,肖特基二极管所需的反偏电压要低。 10双极型晶体管 双极型晶体管有三个掺杂不同的扩散区和两个Pn结,两个结很近所以之间可以互相作用。之所以成为双极型晶体管,是应为这种器件中包含电子和空穴两种极性不同的载流子运动。 一、工作原理 附npn型和pnp型的结构图 发射区掺杂浓度最高,集电区掺杂浓度最低 附常规npn截面图 造成实际结构复杂的原因是:1.各端点引线要做在表面上,为了降低半导体的电阻,必须要有重掺杂的N+型掩埋层。2.一片半导体材料上要做很多的双极型晶体管,各自必须隔离,应为不是所有的集电极都是同一个电位。 通常情况下,BE结是正偏的,BC结是反偏的。称为正向有源。附图: 由于发射结正偏,电子就从发射区越过发射结注入到基区。BC结反偏,所以在BC结边界,理想情况下少子电子浓度为零。 附基区中电子浓度示意图: 电子浓度梯度表明,从发射区注入的电子会越过基区扩散到BC结的空间电荷区,

半导体物理与器件第四版课后习题答案

Chapter 3 3、1 If were to increase, the bandgap energy would decrease and the material would begin to behave less like a semiconductor and more like a metal、 If were to decrease, the bandgap energy would increase and the material would begin to behave more like an insulator、 _______________________________________ 3、2 Schrodinger's wave equation is: Assume the solution is of the form: Region I: 、 Substituting the assumed solution into the wave equation, we obtain: which bees This equation may be written as Setting for region I, the equation bees: where Q、E、D、 In Region II, 、 Assume the same form of the solution: Substituting into Schrodinger's wave equation, we find: This equation can be written as: Setting for region II, this equation bees where again Q、E、D、 _______________________________________ 3、3 We have Assume the solution is of the form: The first derivative is and the second derivative bees Substituting these equations into the differential equation, we find bining terms, we obtain We find that Q、E、D、 For the differential equation in and the proposed solution, the procedure is exactly the same as above、 _______________________________________ 3、4 We have the solutions for and for 、 The first boundary condition is which yields The second boundary condition is which yields The third boundary condition is which yields

半导体物理与器件复习资料

非平衡载流子寿命公式: 本征载流子浓度公式: 本征半导体:晶体中不含有杂质原子的材料 半导体功函数:指真空电子能级E 0与半导体的费米能级E f 之差 电子>(<)空穴为n(p)型半导体,掺入的是施主(受主)杂质原子。 Pn 结击穿的的两种机制:齐纳效应和雪崩效应 载流子的迁移率 扩散系数 爱因斯坦关系式 两种扩散机制:晶格扩散,电离杂质扩散 迁移率受掺杂浓度和温度的影响 金属导电是由于自由电子;半导体则是因为自由电子和空穴;绝缘体没有自由移动的带电粒子,其不导电。 空间电荷区:冶金结两侧由于n 区内施主电离和p 区内受主电离而形成的带净正电与负电的区域。 存储时间:当pn 结二极管由正偏变为反偏是,空间电荷区边缘的过剩少子浓度由稳定值变为零所用的时间。 费米能级:是指绝对零度时,电子填充最高能级的能量位置。 准费米能级:在非平衡状度下,由于导带和介质在总体上处于非平衡,不能用统一的费米能级来描述电子和空穴按能级分布的问题,但由于导带中的电子和价带中的空穴按能量在各自能带中处于准平衡分布,可以有各自的费米能级成为准费米能级。 肖特基接触:指金属与半导体接触时,在界面处的能带弯曲,形成肖特基势垒,该势垒导放大的界面电阻值。 非本征半导体:将掺入了定量的特定杂质原子,从而将热平衡状态电子和空穴浓度不同于本征载流子浓度的材料定义为非本征半导体。 简并半导体:电子或空穴的浓度大于有效状态密度,费米能级位于导带中(n 型)或价带中(p 型)的半导体。 直接带隙半导体:导带边和价带边处于k 空间相同点的半导体。 电子有效质量:并不代表真正的质量,而是代表能带中电子受外力时,外力与加速度的一个比例常熟。 雪崩击穿:由空间电荷区内电子或空穴与原子电子碰撞而产生电子--空穴对时,创建较大反偏pn 结电流的过程 1、什么是单边突变结?为什么pn 结低掺杂一侧的空间电荷区较宽? ①冶金结一侧的掺杂浓度大于另一侧的掺杂浓度的pn 结;②由于pn 结空间电荷区p 区的受主离子所带负电荷与N 区的施主离子所带正电荷的量是相等的,而这两种带点离子不能自由移动的,所以空间电荷区内的低掺杂一侧,其带点离子的浓度相对较低,为了与高掺杂一侧的带电离子的数量进行匹配,只有增加低掺杂一侧的宽度 。 2、为什么随着掺杂弄得的增大,击穿电压反而下降? 随着掺杂浓度的增大,杂质原子之间彼此靠的很近而发生相互影响,分离能级就会扩展成微带,会使原奶的导带往下移,造成禁带宽度变宽,不如外加电压时,能带的倾斜处隧长度Δx 变得更短,当Δx 短到一定程度,当加微小电压时,就会使p 区价带中电子通过隧道效应通过禁带而到达N 区导带,是的反响电流急剧增大而发生隧道击穿,所以。。。。。。 3、对于重掺杂半导体和一般掺杂半导体,为何前者的迁移率随温度的变化趋势不同?试加以定性分析。 对于重掺杂半导体,在低温时,杂质散射起主导作用,而晶格振动散射与一般掺杂半导体相比较影响并不大,所以这时随着温度的升高,重掺杂半导体的迁移率反而增加;温度继续增加下,晶格振动散射起主导作用,导致迁移率下降。 对于一般掺杂半导体,由于杂质浓度低,电离杂子散射基本可以忽略,其主要作用的是晶格振动散射,所以温度越高,迁移率越小。 4、漂移运动和扩散运动有什么不同?对于非简并半导体而言,迁移率和扩散系数之间满足什么关系? 漂移运动是载流子在外电场的作用下发生的定向运动,而扩散运动是由于浓度分布不均,导致载流子从浓度高的地方向浓度低的地方定向运动。前者的推动力是外电场,后者的推动力是载流子的分布引起的。 关系为:T k D 0 //εμ= 5、什么叫统计分布函数?并说明麦克斯韦-玻尔兹曼、玻色-爱因斯坦、费米狄拉克分布函数的区别? 描述大量粒子的分部规律的函数。 ①麦克--滋曼分布函数:经典离子,粒子可区分,而且每个能态多容纳的粒子数没有限制。 ②波色--斯坦分部函数:光子,粒子不可区分,每个能态所能容纳的粒子数没有限制。 ③费米狄拉克分布函数:晶体中的电子,粒子不可分辨,而且每个量子态,只允许一个粒子。 6、画出肖特基二极管和pn 结二极管的正偏特性曲线;并说明它们之间的差别。 两个重要的区别:反向饱和电流密度的数量级,开关特性; 两种器件的电流输运机构不同:pn 结中的电流是由少数载流子的扩散运动决定的,而肖特基势垒二极管中的电流是由多数载流子通过热电子发射越过内建电势差而形成的。 肖特基二极管的有效开启电压低于pn 结二极管的有效开启电压。 7、(a )5个电子处于3个宽度都为a=12A °的三维无限深势阱中,假设质量为自由电子质量,求T=0k 时费米能级(b )对于13个电子呢? 解:对于三维无限深势阱 对于5个电子状态,对应nxnynz=221=122包含一个电子和空穴的状态 ev E F 349.2)122(261.022=++?= 对于13个电子……=323=233 ev E F 5.742)323(261.0222=++?= 8、T=300k 时,硅的实验测定值为p 0=2×104cm -3,Na=7*1015cm -3, (a)因为P 0 MOS/CMOS集成电路简介及N沟道MOS管和P沟道MOS管 在实际项目中,我们基本都用增强型mos管,分为N沟道和P沟道两种。 我们常用的是NMOS,因为其导通电阻小,且容易制造。在MOS管原理图上可以看到,漏极和源极之间有一个寄生二极管。这个叫体二极管,在驱动感性负载(如马达),这个二极管很重要。顺便说一句,体二极管只在单个的MOS管中存在,在集成电路芯片内部通常是没有的。 1.导通特性 NMOS的特性,Vgs大于一定的值就会导通,适合用于源极接地时的情况(低 端驱动),只要栅极电压达到4V或10V就可以了。 PMOS的特性,Vgs小于一定的值就会导通,适合用于源极接VCC时的情况(高端驱动)。但是,虽然PMOS可以很方便地用作高端驱动,但由于导通电阻大,价格贵,替换种类少等原因,在高端驱动中,通常还是使用NMOS。 2.MOS开关管损失 不管是NMOS还是PMOS,导通后都有导通电阻存在,这样电流就会在这个电阻上消耗能量,这部分消耗的能量叫做导通损耗。选择导通电阻小的MOS管会减小导通损耗。现在的小功率MOS管导通电阻一般在几十毫欧左右,几毫欧的也有。 MOS在导通和截止的时候,一定不是在瞬间完成的。MOS两端的电压有一个下降的过程,流过的电流有一个上升的过程,在这段时间内,MOS管的损失是电压和电流的乘积,叫做开关损失。通常开关损失比导通损失大得多,而且开关频率越高,损失也越大。 导通瞬间电压和电流的乘积很大,造成的损失也就很大。缩短开关时间,可以减小每次导通时的损失;降低开关频率,可以减小单位时间内的开关次数。这两种办法都可以减小开关损失。 3.MOS管驱动 跟双极性晶体管相比,一般认为使MOS管导通不需要电流,只要GS电压高于一定的值,就可以了。这个很容易做到,但是,我们还需要速度。 在MOS管的结构中可以看到,在GS,GD之间存在寄生电容,而MOS管的驱动,实际上就是对电容的充放电。对电容的充电需要一个电流,因为对电容充电瞬间可以把电容看成短路,所以瞬间电流会比较大。选择/设计MOS管驱动时第一要注意的是可提供瞬间短路电流的大小。 第二注意的是,普遍用于高端驱动的NMOS,导通时需要是栅极电压大于源极 半导体物理与器件课程总结 吕游微电子与固体电子学201212171909 2012-2013学年第二学期,在尊敬的李常青老师的指导下学习了《半导体物理与器件》这门课程,我们按照章节划分,有侧重点的进行了个人重点学习并且在课堂上进行讲解演示,可谓受益匪浅。在以下的部分我将对这学期的课程学习做出总结。 首先,在第一部分,我针对《半导体物理与器件》课程做一个总体的概述,谈谈学习完本书后我的个人所得与感想。《半导体物理与器件》一书是一本有关半导体物理器件理论的入门书籍,它不但包含了诸多半导体器件的特性、工作原理以及局限性的理论基础知识,还附带了很多图示和生动的例子,对于一个半导体初学者来说大有帮助。 本书从基础物理讲起,而后转至半导体材料物理,最后讨论半导体器件物理。第1章先从固体的晶体结构开始,然后过渡到理想单晶体材料。第2章和第3章介绍了量子力学和固体物理,这些都是必须掌握的基础物理知识。第4章到第6章覆盖了半导体材料物理知识。其中,第4章讨论了热平衡半导体物理;第5章讨论了半导体内部的载流子输运现象;第6章主要介绍非平衡过剩载流子。理解半导体的过剩载流子行为对于理解器件物理是至关重要的。第7章到第13章对基本半导体器件物理进行了详细的描述。第7章主要讨论pn结电子学;第8章讨论pn结电流-电压特性;第9章讨论整流及非整流金属半导体结和半导体异质结;第10章探讨双极型晶体管。第11章、第12章阐述了MOS场效应管理论;第13章则阐述了结型场效应管。以上便是这本书的简要内容,这些章节之间既有联系又是相互独立的。 从这一部分开始,我将对本人重点学习的章节-第11章MOS场效应晶体管基础-做一个详细的讲解。这一章中,我所重点研究的内容是前两节,金属-氧化物-半导体场效应管的物理基础,这部分内容与前面的知识关联不太大,只依赖与半导体材料的性质和pn结的特性。所以,即使你是以前并没有接触过半导体知识的初学者,只要用心学习,也是不难理解的。 MOSFET是金属-氧化物-半导体场效应晶体管的简称。我们知道,MOSFET是当今集成电路设计的核心,可见学习MOSFET的重要性。其中,MOSFET的核心部分是一个称为MOS电容的金属-氧化物-半导体的结构。在本章中,我们首先阐述各种类型的MOSFET,并定性的讨论其电流-电压特性;然后将详细分析这种特性的理论来源以及数学推导过程;此外还将讨论MOSFET的频率特性。 11.1MOS电容 MOS结构的物理性质可以借助比较容易理解的平行板电容器加以说明。下图是MOS电容的结构。其中d是氧化层的厚度,金属栅极的材料是Al,氧化层的材料是 二氧化硅,衬底是晶体硅。 通常情况下,Si基板接地,对于p 型衬底的MOS管,当金属栅极加上正电 压时,称为正偏;而金属栅极加上负电 压时称为反偏。当上面的金属栅被施加 一个负电压,负电荷出现在上面的金属 板上,半导体内产生一个电场,多为多 子的空穴被推向半导体-氧化物表面,形 万联芯城致力于打造一个方便快捷的电子物料采购平台。采购MOS管等电子元器件,就到万联芯城,万联芯城MOS场效应管主打 IR,AOS,VISHAY等知名国际品牌,均为原装进口货源,当天可发货。点击进入万联芯城 点击进入万联芯城 MOS管是FET的一种(另一种是JFET),可以被制造成增强型或耗尽型,P沟道或N沟道共4种类型,但实际应用的只有增强型的N沟道MOS 管和增强型的P沟道MOS管,所以通常提到NMOS,或者PMOS指的就是这两种。 对于这两种增强型MOS管,比较常用的是NMOS。原因是导通电阻小,且容易制造。所以开关电源和马达驱动的应用中,一般都用NMOS。 下面的介绍中,也多以NMOS为主。 MOS管的三个管脚之间有寄生电容存在,这不是我们需要的,而是由于制造工艺限制产生的。寄生电容的存在使得在设计或选择驱动电路的时候要麻烦一些,但没有办法避免,后边再详细介绍。 在MOS管工作原理图上可以看到,漏极和源极之间有一个寄生二极管。这个叫体二极管,在驱动感性负载(如马达),这个二极管很重要。顺便说一句,体二极管只在单个的MOS管中存在,在集成电路芯片内部通常是没有的。 MOS管工作原理图电源开关电路详解 这是该装置的核心,在介绍该部分工作原理之前,先简单解释一下MOS的工作原理图。 它一般有耗尽型和增强型两种。本文使用的为增强型MOS MOS管,其内部结构见mos管工作原理图。它可分为NPN型PNP型。NPN型通常称为N沟道型,PNP型也叫P沟道型。由图可看出,对于N沟道的场效应管其源极和漏极接在N型半导体上,同样对于P沟道的场效应管其源极和漏极则接在P型半导体上。我们知道一般三极管是由输入的电流控制输出的电流。但对于场效应管,其输出电流是由输入的电压(或称电场)控制,可以认为输入电流极小或没有输入电流,这使得该器件有很高的输入阻抗,同时这也是我们称之为场效应管的原因。N沟道和P沟道MOS管

半导体物理与器件

mos管工作原理及详解