Xilinx原语的使用方法2

Xilinx公司原语的使用方法2

3.4.7 RAM/ROM组件

RAM/ROM组件可用于例化FIFO、分布式RAM、分布式RAM、块ROM以及块ROM,具体包括12个组件,如表3-16所示。

表3-16 RAM/ROM原语列表

下面主要介绍FIFO、分布式双口RAM以及块双口RAM原语的使用,单口RAM和ROM原语的用法类似,限于篇幅,就不再介绍。

1.RAM16X1S

RAM16X1S是深度为16比特,位宽为1的同步RAM。当写使能信号WE

为低时,写端口的数据操作无效,RAM内部的数据不会改变;当WE为高时,可以在任意地址中写入比特。为了保证数据的稳定性,地址和数据应该在WCLK的上升沿前保持稳定。输出信号O为RAM中由读地址信号所确定的地址中所存数据的值。此外,还可通过属性指定RAM的初始值。

RAM16X1S原语的例化代码模版如下所示:

// RAM16X1S: 16比特1深度同步RAM(16 x 1 posedge write distributed (LUT) RAM)

// 适用芯片:所有芯片

// Xilinx HDL库向导版本,ISE 9.1

RAM16X1S #(

.INIT(16'h0000)

//对RAM的内容进行初始化,这里初始化为全1

) RAM16X1S_inst (

.O(O), // RAM output

.A0(A0), // RAM address[0] input

.A1(A1), // RAM address[1] input

.A2(A2), // RAM address[2] input

.A3(A3), // RAM address[3] input

.D(D), // RAM data input

.WCLK(WCLK), // Write clock input

.WE(WE) // Write enable input

);

// 结束RAM16X1S模块的例化过程

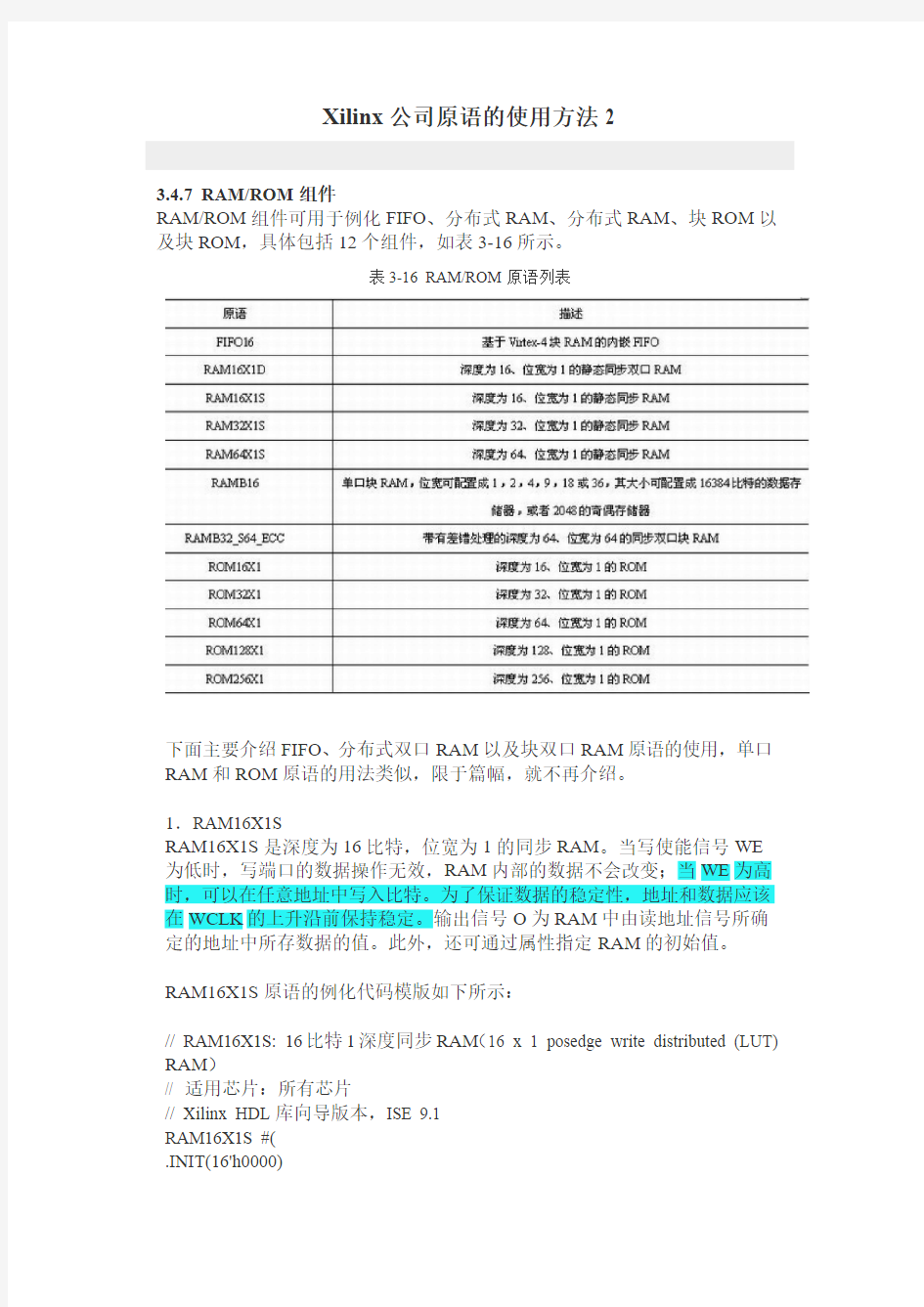

需要注意的是,RAM16X1S原语是Xilinx独有的一类结构,在小数据量存储方面非常节省资源。在综合结果分析时,RAM16X1S原语的RTL结构如图3-45所示。

图3-45 原语RAM16X1S的RTL结构图

2.RAMB16

RAMB16是FPGA芯片中内嵌的双口块RAM,数据位宽可配置成1、2、4、9、18以及36比特,每个块RAM的大小为18 1024比特,所以位宽越大,深度越小。块RAM在FPGA中按照矩阵的方式排列,其数量完全取决于芯片容量的大小。在使用中,可以添加坐标来约束块RAM的位置。例如:LOC = RAMB16_X#Y#;

同样,也可以对块RAM完成初始化。块RAM是以硬核的方式内嵌到FPGA 芯片中,不占用芯片的逻辑资源,是FPGA芯片内部非常宝贵的一种资源。在工作时,要尽量使用芯片的块RAM资源,不仅能保证较高的工作频率,还具有很低的动态功耗。

RAMB16的Verilog例化代码如下所示。

// RAMB16: 块RAM(Virtex-4 16k+2k Parity Paramatizable BlockRAM

// 适用芯片:Virtex-4芯片

// Xilinx HDL库向导版本,ISE 9.1

RAMB16 #(

.DOA_REG(0),

// A端口可选的输出寄存器,可设置为0或1,分别表示输出不寄存/寄存.DOB_REG(0),

// B端口可选的输出寄存器,可设置为0或1,分别表示输出不寄存/寄存.INIT_A(36'h000000000),

// 初始化A端口的输出初始值

.INIT_B(36'h000000000),

// 初始化A端口的输出初始值

.INVERT_CLK_DOA_REG("FALSE"),

// 反转A端口寄存器的时钟,可设置为"TRUE"或"FALSE",分别表示不反转/反转

.INVERT_CLK_DOB_REG("FALSE"),

// 反转B端口寄存器的时钟,可设置为"TRUE"或"FALSE",分别表示不反转/反转

.RAM_EXTENSION_A("NONE"),

// RAM的A端口扩展选项,可设置为"UPPER"、"LOWER"或"NONE",分别表示作为// 高字节、低字节级联,或者不扩展

.RAM_EXTENSION_B("NONE"),

// RAM的B端口扩展选项.READ_WIDTH_A(0),同A端口

.READ_WIDTH_A(0),

// A端口的数据读取宽度,有效值为1, 2, 4, 9, 18, 或36

.READ_WIDTH_B(0),

// B端口的数据读取宽度,有效值为1, 2, 4, 9, 18, 或36

.SIM_COLLISION_CHECK("ALL"),

// 碰撞检测使能信号,可设置为"ALL"、"WARNING_ONLY"、"GENERATE_X_ONLY" // 或者"NONE"

.SRVAL_A(36'h000000000),

// 复位后A端口的输出值

.SRVAL_B(36'h000000000),

//复位后A端口的输出值

.WRITE_MODE_A("WRITE_FIRST"),

// A端口的写模式,可设置为"WRITE_FIRST", "READ_FIRST", 或

"NO_CHANGE"

.WRITE_MODE_B("WRITE_FIRST"),

// B端口的写模式,可设置为"WRITE_FIRST", "READ_FIRST", 或

"NO_CHANGE"

.WRITE_WIDTH_A(2),

// A端口的数据写入宽度,有效值为1, 2, 4, 9, 18, 或36

.WRITE_WIDTH_B(0),

// B端口的数据写入宽度,有效值为1, 2, 4, 9, 18, 或36

// 下列INIT_xx 声明用于指定RAM的初始化内容

.INIT_00(256'h0000000000000000000000000000000000000000000000000000 000000000000),

000000000000),

.INIT_02(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_03(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_04(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_05(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_06(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_07(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_08(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_09(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_0A(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_0B(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_0C(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_0D(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_0E(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_0F(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_10(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_11(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_12(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_13(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_14(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_15(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_16(256'h0000000000000000000000000000000000000000000000000000 000000000000),

000000000000),

.INIT_18(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_19(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_1A(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_1B(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_1C(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_1D(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_1E(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_1F(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_20(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_21(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_22(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_23(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_24(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_25(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_26(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_27(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_28(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_29(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_2A(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_2B(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_2C(256'h0000000000000000000000000000000000000000000000000000 000000000000),

000000000000),

.INIT_2E(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_2F(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_30(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_31(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_32(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_33(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_34(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_35(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_36(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_37(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_38(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_39(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_3A(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_3B(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_3C(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_3D(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_3E(256'h0000000000000000000000000000000000000000000000000000 000000000000),

.INIT_3F(256'h0000000000000000000000000000000000000000000000000000 000000000000),

// 下面的INITP_xx 用于初始化校验比特

.INITP_00(256'h000000000000000000000000000000000000000000000000000 0000000000000),

.INITP_01(256'h000000000000000000000000000000000000000000000000000 0000000000000),

.INITP_02(256'h000000000000000000000000000000000000000000000000000

0000000000000),

.INITP_03(256'h000000000000000000000000000000000000000000000000000 0000000000000),

.INITP_04(256'h000000000000000000000000000000000000000000000000000 0000000000000),

.INITP_05(256'h000000000000000000000000000000000000000000000000000 0000000000000),

.INITP_06(256'h000000000000000000000000000000000000000000000000000 0000000000000),

.INITP_07(256'h000000000000000000000000000000000000000000000000000 0000000000000)

) RAMB16_inst (

.CASCADEOUTA(CASCADEOUTA), // A端口的1比特级联输出

.CASCADEOUTB(CASCADEOUTB), // B端口的1比特级联输出

.DOA(DOA), // A端口的32比特数据输出

.DOB(DOB), // B端口的32比特数据输出

.DOPA(DOPA), // A端口4比特校验数据输出

.DOPB(DOPB), // B端口4比特校验数据输出

.ADDRA(ADDRA), // A端口15比特地址输入

.ADDRB(ADDRB), // B端口15比特地址输入

.CASCADEINA(CASCADEINA), // A端口1比特级联地址输入

.CASCADEINB(CASCADEINB), // B端口1比特级联地址输入

.CLKA(CLKA), //A端口的工作时钟输入

.CLKB(CLKB), // B端口的工作时钟输入

.DIA(DIA), // A端口的32比特写数据

.DIB(DIB), // A端口的32比特写数据

.DIPA(DIPA), //A端口4比特校验输入数据

.DIPB(DIPB), //B端口4比特校验输入数据

.ENA(ENA), //A端口的1比特使能信号

.ENB(ENB), //B端口的1比特使能信号

.REGCEA(REGCEA), //A端口1比特寄存器使能信号

.REGCEB(REGCEB), //B端口1比特寄存器使能信号

.SSRA(SSRA), // A端口1比特复位输入信号

.SSRB(SSRB), // B端口1比特复位输入信号

.WEA(WEA), // A端口4比特写使能输入信号

.WEB(WEB) // B端口4比特写使能输入信号

);

// 结束RAMB16模块的例化过程

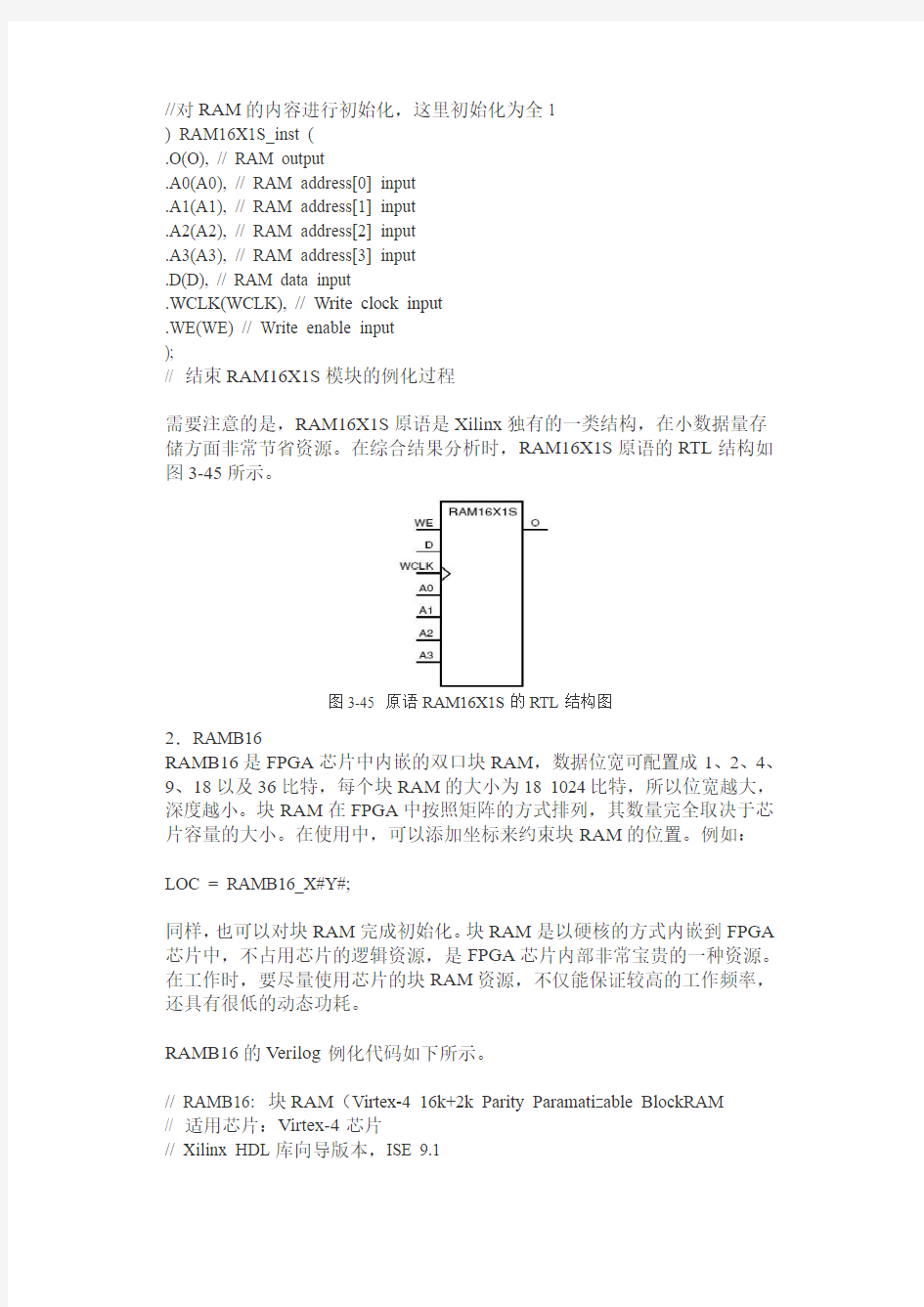

在综合结果分析时,RAMB16的RTL结构如图3-46所示。

图3-46 RAMB16的RTL结构示意图

3.4.8 寄存器和锁存器

寄存器和锁存器是时序电路中常用的基本元件,其原语在表3-17中给出。

表3-17 寄存器和锁存器原语列表

下面只介绍FDCPE原语的使用,其余两个原语的使用方法类似。

1.FDCPE原语

FDCPE指带单数据输入信号D、单输出O、时钟使能信号CE、异步复位PRE 和异步清空信号CLR的D触发器。当PRE信号为高时,输出端O为高;当CLR为高时,输出端O为低;当PRE和CLR都为低、CE信号为高时,输入信号D在时钟上升沿被加载到触发器中,并被送到输出端;当PRE和CLR

都为低、CE信号为低时,输出端保持不变。FDCPE的真值表如表3-18所列。

表3-18 FDCPE原语的真值表

FDCPE原语的Verilog实例化代码如下所示:

// FDCPE: D触发器(Single Data Rate D Flip-Flop )

// 适用芯片:所有FPGA芯片

// Xilinx HDL库向导版本,ISE 9.1

FDCPE #(

.INIT(1'b0)

//初始化寄存器的值,可设置为1'b0或1'b1

) FDCPE_inst (

.Q(Q), // 数据输出端口

.C(C), // 时钟输入端口

.CE(CE), // 时钟使能输入信号

.CLR(CLR), // 异步清空输入信号

.D(D), // 数据输入信号

.PRE(PRE) // 异步复位输入信号

);

// 结束FDCPE模块的例化过程

在综合结果分析时,FDCPE原语的RTL结构如图3-47所示。

图3-47 FDCPE的RTL结构

3.4.9 移位寄存器组件

移位寄存器组件为Xilinx芯片所独有,由于属性的不同,具体有8个,如表3-19所列。

表3-19移位寄存器组件列表

各个移位寄存器原语都是在SRL16的基础上发展起来的,因此,本节主要介绍基本的SRL16原语。

1.SRL16原语

SRL16是基于查找表(LUT)的移位寄存器,在实际应用中既能节省资源,还能保证时序。其输入信号A3、A2、A1以及A0选择移位寄存器的读取地址,当写使能信号高有效时,输入信号将被加载到移位寄存器中。单个移位寄存器的深度可以是固定的,也可以动态调整,最大不能超过16。需要更大深度的移位寄存器时,则需要将多个SRL16拼接起来。单个SRL16的地址信号线与输出的真值表如表3-20所示。

表3-20 SRL16的功能说明表

SRL16本质上是一种基于查找表(LUT)的移位寄存器,因此其位宽(B)和深度(D)需要满足查找表的结构特点,所占用Slice资源M的计算公式为:

其中,R[]函数的意义是取整。从上式可以看出,深度为1的移位寄存器和深度为16的移位寄存器所占用的Slice资源是一样的。和触发器相比,SRL16最大的特点就是占用Slice资源特别少。

只要固定A3~A0的信号电平,即可获得一个固定长度的移位寄存器,其长度范围从1~16,可由公式(M)计算得到。当A3~A0全为0时,其寄存深度为1;当A3~A0全为1时,其寄存深度为16。

Length = (8 x A3) +(4 x A2) + (2 x A1) + A0 +1 (M)

SRL16原语的Verilog实例化代码如下所示:

// SRL16: 16位查找表移位寄存器(16-bit shift register LUT operating on posedge of clock)

// 适用芯片:所有FPGA芯片

// Xilinx HDL库向导版本,ISE 9.1

SRL16 #(

.INIT(16'h0000)

// 初始化移位寄存器的值,可以为16比特任意整数

) SRL16_inst (

.Q(Q), // SRL16的数据输出信号

.A0(A0), // 选择[0]输入

.A1(A1), // 选择[1]输入

.A2(A2), // 选择[2]输入

.A3(A3), // 选择[3]输入

.CLK(CLK), // 时钟输入信号

.D(D) // SRL16的数据输入信号

);

// 结束SRL16模块的例化过程

在综合结果分析时,SRL16原语的RTL级结构如图3-48所示。

图3-48 SRL16的RTL级结构示意图

3.4.10 Slice/CLB组件

Slice/CLB组件涵盖了Xilinx FPGA中所有的逻辑单元,包括各种查找表、复用器以及逻辑操作等21个原语,如表3-21所列。

表3-21 Slice/CLB组件列表

本节主要介绍基本的单输出1比特查找表原语和通用输出2到1复用器原语的使用方法。

1.LUT1原语

FPGA内部的组合逻辑都可以通过LUT结构实现,常用的LUT结构有LUT1、

LUT2、LUT3以及LUT4,其区别在于查找表输入比特宽度的不同。LUT1是其中最简单的一种,常用于实现缓冲器和反相器,是带通用输出的1比特查找表。

LUT1原语的Verilog实例化代码如下所示:

// LUT1: 1比特输入的通用查找表(1-input Look-Up Table with general output)

// 适用芯片:所有FPGA芯片

// Xilinx HDL库向导版本,ISE 9.1

LUT1 #(

.INIT(2'b00)

// 指定LUT的初始化内容

) LUT1_inst (

.O(O), // LUT的通用输出

.I0(I0) // LUT输入信号

);

// 结束LUT1模块的例化过程

在综合结构分析时,LUT1原语的RTL级结构如图3-49所示。

图3-49 LUT1的RTL级结构示意图

2.MUXF7原语

MUXF7是带通用输出的2到1查找表复用器,其控制信号S可以是任何内部信号,当其为低电平时,选择I0;当其为高电平时选择I1。MUXF7需要占用一个完整的CLB资源,和其相关的查找表可组成7功能的查找表和16到1的选择器,可将MUXF6的输出连接到MUXF7的输入端。MUXF7的真值表如表3-22所示。

表3-22 MUXF7的真值表

MUXF7原语的实例化代码如下所示:

// MUXF7: 2到1LUT复用器(CLB MUX to tie two MUXF6's together with general output)

// 适用芯片:Virtex-II/II-Pro 以及Spartan-3/3E

// Xilinx HDL库向导版本,ISE 9.1

MUXF7 MUXF7_inst (

.O(O), // MUX的通用输出信号

.I0(I0),

.I1(I1), // 复用器的输入信号,连接到MUXF6 LO

.S(S) // 复用器的输入选择信号

);

// End of MUXF7_inst instantiation

在综合结构分析时,MUXF7原语的RTL级结构如图3-50所示。

图3-50 MUXF7的RTL及结构示意图

本节给出了典型的Xilinx原语的使用,但更多的原语需要读者在实践中大量应用才能熟练掌握。只有全面掌握了原语,才能对Xilinx FPGA的资源有一个理性认识,从而将工程设计提升到艺术雕刻的高度,这是每一个FPGA开发人员的目标。详细的原语资料可在ISE安装目录下的“doc\usenglish\ books\docs”文件夹中找到,其中Virtex4系列芯片的原语资料文件“v4ldl.pdf”位于“v4ldl”文件中,Virtex5系列芯片的原语资料文件“v5ldl.pdf”位于“v5ldl”文件中,Spartan 3A系列芯片的原语资料文件“s3adl.pdf”位于“s3adl”文件中,Spartan 3E系列芯片的原语资料文件“s3edl.pdf”位于“s3edl”文件中。

3.5 本章小结

本章主要介绍基于Xilinx芯片的Verilog开发技术。首先介绍了典型的硬件设计思维;然后讨论了优秀的通用代码风格和Xilinx专用的代码风格,无论哪种风格都是稳定性、速度以及硬件资源三者优化,只不过前者从FPGA器件共有的特性出发,后者则面向Xilinx公司的FPGA芯片特点;最后,介绍了Xilinx公司FPGA器件的硬件原语,以及典型原语的使用方法。特别需要强调的一点是:对原语的全面掌握是Xilinx FPGA开发人员的基本要求。

微波炉的使用小常识

最佳答案 一、微波炉使用常识 A、微波炉不要摆放在卧室,最好放在平稳、干燥、通风的地方。机体背部、顶部及两侧都应该留出大约10厘米的空隙以确保具有良好的通风环境。 B、微波炉里不能使用金属或者带有金属配件的容器,也不能使用木制或竹制器具。同时普通塑料容器由于遇热容易变形并容易污染食物、危害人体健康,因此也不能使用。这里建议大家最好使用耐热的玻璃或者是耐热陶瓷等专用器皿。 C、像是袋装食物需要在开启后放入容器内再放入微波炉内,而蛋类必须要打碎搅拌均匀后再放入微波炉内,否则可能会引起爆炸等事故发生。 D、切忌不能用微波炉加热牛奶,因为牛奶中的氨基酸经过微波炉加热后,通常会有一部分转变成对人体有害的物质。 E、加热食物一定要盛放在指定容器中,不能直接将食物放在微波炉内的玻璃转盘上。 F、拿取食物时应该使用适当的夹具,不要直接用手拿取以防烫伤。 G、用微波炉加热或解冻食物时间不应过长。如果忘记取出,食物在炉内存放时间超过2小时建议将其丢掉,以免食物中毒。 H、使用微波炉加热食物时要使用保鲜薄膜,这样可以将水汽封住使加热迅速均匀。在取出食物前可以将保鲜膜刺破以免粘到食物上。 I、不要使用微波炉油炸食品,因为高温油飞溅可能会导致明火出现,引起炉内起火。这时千万不要打开微波炉,而应先关闭电源,待火熄灭后再开门降温。 J、要注意微波炉内外的清洁卫生,这样能够更好的延长其使用寿命。 K、建议大家要习惯性检查微波炉门开启是否正常,如果异常就应该立刻停止使用并送到专业部门进行检修。这主要是因为如果微波炉的电磁外泄将会对人体造成永远不能治愈的烧伤。 L、当微波炉处于工作状态时,大家应该远离微波炉。 二、微波炉应该放置在何处 用户应该将微波炉放置在干燥、通风的地方,以更好的避免热气或水进到里面。 在掌握微波煮食的时间时,必须考虑以下的重要因素:

xilinx FPGA SelectIO模块资料

5.1.6 SelectIO模块 Virtex-6每个I/O片(I/O Tile)包含两个IOB、两个ILOGIC、两个OLOGIC 和两个IODELAY,如图5-24 所示。 图5-24 I/O 片结构图 本小节就以下几个方面介绍Virtex-6 的SelectIO 资源。 (1) SelectIO 的电气特性。 (2) SelectIO 的逻辑资源——ILOGIC 资源和OLOGIC 资源。 (3) SelectIO 的高级逻辑资源——ISERDES 资源、OSERDES 资源和Bitslip。 一、SelectIO IO 的电气特性 所有的Virtex-6 FPGA 有高性能的可配置SelectIO 驱动器与接收器,支持非常广泛的接口标准。强大的功能SelectIO 包括输出强度和斜率的可编程控制以及使用数控阻抗(DCI)的片上终端。

IOB 包含输入、输出和三态SelectIO 驱动器。支持单端I/O 标准(LVCMOS、 HSTL、SSTL)和差分I/O 标准(LVDS、HT、LVPECL、BLVDS、差分HSTL 和SSTL)。 注意:差分输入和VREF 相关输入由VCCAUX 供电。 IOB、引脚及内部逻辑的连接如图5-25 所示。 图5-25 IOB、引脚及内部逻辑连接图 IOB 直接连接ILOGIC/OLOGIC 对,该逻辑对包含输入和输出逻辑资源,可实现数据和三态控制。ILOGIC和OLOGIC可分别配置为ISERDES和OSERDES。Xilinx软件库提供了大量与I/O相关的原语,在例化这些原语时,可以指定I/O 标准。与单端I/O相关的原语包括IBUF(输入缓冲器)、IBUFG(时钟输入缓冲器)、OBUF(输出缓冲器)、OBUFT(三态输出缓冲器)和IOBUF(输入/输出缓冲器)。与差分I/O相关的原语包括IBUFDS(输入缓冲器)、IBUFGDS (时钟输入缓冲器)、OBUFDS(输出缓冲器)、OBUFTDS(三态输出缓冲器)、IOBUFDS(输入/输出缓冲器)、IBUFDS_DIFF_OUT(输入缓冲器)和IOBUFDS_DIFF_OUT(输入/输出缓冲器)。 二、SelectIO的逻辑资源 SelectIO的逻辑资源主要是指ILOGIC和OLOGIC资源,它们完成了FPGA引脚到内部逻辑的连接功能,包括组合输入/输出、三态输出控制、寄存器输入/输出、寄存器三态输出控制、DDR输入/输出、DDR输出三态控制、IODELAYE1高分辨率可调整延迟单元及其控制模块。 下面简要介绍ILOGIC和OLOGIC功能。

超级一键网克使用方法

超级一键网克使用方法 进行网克需要的条件: 一键网克软件:超级一键网克,当然其他的网克软件也可以。 一台已经装好系统的机器(操作系统98以上即可,推荐XP)用作服务器, 一台已经装好全部软件并且配置好的机器作为母盘,当然,如果你只对系统盘进行网克的话,这台机器也可以兼做服务器,但是如果你想全盘网克的话,那就需要另外一台机器做服务器了,道理嘛,因为做全盘镜像的时候镜像文件当然不可能放在源盘上,而必须放在另外一块硬盘上,就好象你左手永远不可能摸到左手的手背一样,呵呵。 其它客户机,数量255台以下,当然多于255台也可以,只是下面的IP地址和子网掩码要重新配置,大家参看有关资料。不过我想大家一次网克也不可能会有那么多台机器的,呵呵。 注意事项:首先,这些机器间物理网络要保持畅通(废话!)。另外,如果你的网吧是杂牌军的话,那就不要试了,因为每台机器的配置如果不一样的话,所装的驱动也不一样,否则网克后可能有太多的不可预知的后果,经常蓝屏肯定是家常便饭了,当然也有可能根本就启动不了。以上说的配置主要是显卡和主板(如果你的声卡是集成的话)。硬盘无所谓,但要注意,目标盘的容量一定要大于母盘。当然了,最好是配置完全一样,这样基本上不会出什么问题。

当然,如果你的机器配置不一样的话,也可以进行网克,大家可以把雨林木风ghost版里面的ghost文件提取出来作为镜像,这样也比一台一台装系统要快得多了。不过那应该是分区网克,具体方法你学会了全盘网克那自然不在话下。下面开工。 第一步,制作镜像,如果只制作系统盘的镜像,那么在单机操作就行了。具体操作我想大家都会。下面讲的是制作全盘镜像,当然你不必拆开机器挂两个硬盘了,网克嘛! 1、配置tftpd32 解压超级一键网克到服务器的任意盘,比如E盘,双击TFTPD32.EXE,关闭防火墙,或者在应用规则里设为允许访问网络。最好关掉,否则下面你要点若干次允许。点DHCP server标签,这里有几个地方要填一下,当前目录和server不要填,程序自动判断。IP地址池随便填,但要注意不要跟服务器的IP地址冲突,当然要符

微波炉正确使用方法

微波炉正确使用方法 1、在使用微波沪之前,应检查所用器皿是否适用于微波炉 (1)微波烹调时切勿使用金属网架及其它金属器皿,不应使用带金边、银边的 器皿,微波炉中通常使用陶瓷、耐热玻璃、耐热塑料等器皿。 (2)使用光波微波组合烹调时,切勿在金属网架上放置铝制或其它金属容器。 金属网架不应接近炉腔内壁,以防止打火。 (3)使用保鲜纸遮盖食物烹调时,请将保鲜纸一角摺上,使蒸汽可以排出。煮 好后将保鲜纸小心拆开,避免蒸汽灼伤。 2、烹调前应先放入转盘支撑及玻璃转盘,再将盛好食物的器皿放在玻璃转盘上 进行烹调。 3、烹调少量食物时,要多加观察,防止过热起火。不要用微波炉储存任何食物。 4、当食物在塑料、纸或其它可燃材料制成的简易容器中加热或烹调时,应随时 注意,防止起火。 5、从微波炉内拿出食物和器皿时,应当使用隔热手套,以免高温烫手。 6、使用烧烤、光波烹调时,炉内温度很高,故翻转食物应戴上隔热起火手套, 且切勿触碰内上板。 7、为防止玻璃转盘损坏,请遵守下列事项: (1)烹调完食物,应先待转盘冷却后再进行清洗。 (2)切勿将冰冷食品或冰冷器皿放置在炽热的转盘上。 (3)转盘的最大负载重量不能超过5公斤 8、如果微波炉因碰撞、跌落引起炉门、门封、铰链、外壳等发生损坏,请勿继 续使用,必须由专业维修人员检修后才可使用。 9、使用微波炉烹调食物时应注意: (1)切勿煮带壳蛋,压力会使蛋爆裂,应先将蛋打破,要用牙签刺破蛋黄、蛋 白数次。 (2)已煮好的汤圆、荷包蛋等,马上取出可能会因其内部液体沸腾爆破而溅伤 人体。应打开炉门后略搁置一会儿,再取出食物。 (3)烹调食物时不要把时间设置过长,因为煮食时间不足可继续,时间过长则 无法补救。 (4)烹调食谱所提供的是烹调的大约时间,影响烹调时间的因素有:依个人喜 好的煮食程度、食物的初温、形状的大小、份量和使用器皿的形状、大小以及食物的排列、遮盖、翻搅等。 (5)表面无孔的食物(如:蛋、板栗、土豆、香肠等),请去皮或在外皮上开 一裂缝或叉几个小孔,否则受热膨胀,可能发生爆裂。 (6)一般情况下不可用微波炉煎炸食物,除非使用质量可靠的特制微波煎碟。 (7)光波,烧烤烹调时,不可遮盖食物,因为食物需要直接吸收光波和烧烤的 热能。 10、微波炉停止使用时,应将炉门稍稍敞开,使炉腔内水蒸汽充分散发,有利 于腔体的保养。 11、在操作时也可参考微波炉机身上的《微波炉简明使用手册》。

Xilinx-XADC的使用中文介绍doc资料

Zynq器件XADC的使用(原创) 1.前言 赛灵思的7系列FPGA和Zynq器件创造性地在片上集成了模数转换器和相关的片上传感器(内置温度传感器和功耗传感器),这是相比赛灵思前一代产品来新增加的特性,可在系统设计中免去外置的ADC器件,有力地提高了系统的集成度。本文就这一新模块的使用进行简单介绍,希望对大家有所帮助,当然如有不当之处还请高手指正,以免误导大家,欢迎大家补充。 2.XADC模块介绍 2.1 XADC模块概述 Zynq器件XADC模块包括2个12比特1 MIPS的模数转换器和相关的片上传感器,模数转换器能为系统应用提供通用目的的高精度的模拟接口,下图是XADC模块的框图: XADC模块支持不同的操作模式,如外步触发同步采样模式;可接受不同类型的模拟输入信号,如单端或差分信号;最多能接受17路外部的模拟输入信号。XADC模块也包括一定数量的片上传感器用来测量片上的供电电压和芯片温度,这些测量转换数据存储在一个叫状态寄存器(status registers)的专用寄存器内,可由FPGA内部叫动态配置端口(Dynamic

Reconfiguration Port (DRP))的16位的同步读写端口访问。ADC转换数据也可以由JTAG TAP访问,这种情况下并不需要去直接例化XADC模块,因为这是一个已经存在于FPGA JTAG结构的专用接口,此时因为没有在设计中直接例化XADC模块,XADC模块就工作在一种预先定义好的模式叫缺省模式,缺省模式下XADC模块专用于监视芯片上的供电电压和芯片温度。XADC模块的操作模式是由用户通过DRP或JTAG接口写控制寄存器来选择的,控制寄存器的初始值有可能在设计中例化XADC模块时的块属性(block attributes)指定。 2.2 XADC模块管脚需求 所有的XADC模块专用管脚都位于bank0, 所以都加有_0的后缀。下图表示了XADC的基本输入输出需求: 这有两种推荐配置:图中左边XADC由Vccaux(1.8V)供电,并且用一个外部的1.25V参考源。用外部参考源在精度和热飘移方面可以获得更好的性能,一个磁珠用隔离模拟地和数字地,这可避免较常用的模拟和数字电路共地而把噪声带入模拟电路的缺点;图中右边XADC是用片内的参考源,这时VREFP脚必须按图中所示连接到地。

第4节 Xilinx公司原语的使用方法1

第4节Xilinx公司原语的使用方法1 Xilinx 原语 3.4 Xilinx公司原语的使用方法 原语,其英文名字为Primitive,是Xilinx针对其器件特征开发的一系列常用模块的名字,用户可以将其看成Xilinx公司为用户提供的库函数,类似于C++中的“cout”等关键字,是芯片中的基本元件,代表FPGA中实际拥有的硬件逻辑单元,如LUT,D触发器,RAM 等,相当于软件中的机器语言。在实现过程中的翻译步骤时,要将所有的设计单元都转译为目标器件中的基本元件,否则就是不可实现的。原语在设计中可以直接例化使用,是最直接的代码输入方式,其和HDL语言的关系,类似于汇编语言和C语言的关系。 Xilinx公司提供的原语,涵盖了FPGA开发的常用领域,但只有相应配置的硬件才能执行相应的原语,并不是所有的原语都可以在任何一款芯片上运行。在Verilog中使用原语非常简单,将其作为模块名直接例化即可。本节以Virtex-4平台介绍各类原语,因为该系列的原语类型是最全面的。其它系列芯片原语的使用方法是类似的。 Xilinx公司的原语按照功能分为10类,包括:计算组件、I/O端口组件、寄存器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、Slice/CLB 组件以及G比特收发器组件。下面分别对其进行详细介绍。 3.4.1 计算组件 计算组件值得就是DSP48核,也有人将其称为硬件乘法器,功能描述如表3-6所示。 表3-6 计算组件清单 DSP48 其结构为一个18*18比特的有符号乘法器,且在后面还级联了一个带有可配置流水线的3输入加法器 DSP48核由一个18比特的乘法后面级联一个48比特的加法器,乘法器和加法器的应用位宽分别可以在18、48比特内任意调整。其在乘加模块中有广泛应用,特别是各类滤波器系统中,不仅可以提高系统稳定性,还能够节省逻辑资源且工作在高速模式下。 其在Verilog中的例化模版为: module fpga_v4_dsp48( BCOUT, P, PCOUT, A, B, BCIN, C, CARRYIN,CARRYINSEL, CEA, CEB, CEC, CECARRYIN, CECINSUB, CECTRL, CEM, CEP, CLK, OPMODE, PCIN, RSTA, RSTB, RSTC, RSTCARRYIN, RSTM, RSTP, SUBTRACT); output [17:0]BCOUT; output [47:0] P, PCOUT; //

注射用生长抑素

注射用生长抑素 【药品名称】 通用名称:注射用生长抑素 英文名称:Recombinant Human Interferon α2b Vaginal Effervescent Tablets 【成份】 主要成份为生长抑素,为人工合成的环状十四肽 【适应症】 本品主要用于:严重急性食道静脉曲张出血;严重急性胃或十二指肠溃疡出血,或并发急性糜烂性胃炎或出血性胃炎;胰腺外科手术后并发症的预防和治疗;胰、胆和肠瘘的辅助治疗;糖尿病酮症酸中毒的辅助治疗。 【用法用量】 静脉给药(静脉注射或静脉滴注)。 通过慢速冲击注射(3~5分钟)0.25mg或以每小时0.25mg的速度连续静脉滴注给药(一般是每小时每公斤体重用药量为0.0035mg)。 临使用前,每支冻干剂用1ml生理盐水溶液溶解。 对于连续静脉滴注给药,须用本品3mg配备够使用12小时的药液(溶剂可为生理盐水或5%葡萄糖注射液),输液量调节在每小时0.25mg。 1 严重急性上消化道出血包括食道静脉曲张出血的治疗:首先缓慢静脉推注0.25mg(用1ml生理盐水配制)作为负荷 【不良反应】 少数病例用药后出现恶心、眩晕、面部潮红。当注射速度超过每分钟0.05mg时,病人会发生恶心和呕吐现象。

【禁忌】 对本品过敏者禁用。 【注意事项】 1 由于本品抑制胰岛素及胰高血糖素的分泌,在治疗初期会导致血糖水平短暂的下降; 2 胰岛素依赖型糖尿病患者使用本品后,每隔3-4小时应测试1次血糖浓度,同时给药中,尽可能避免使用葡萄糖。必要的情况下应同时使用胰岛素。 3 在连续给药过程中,应不间断地注入,换药间隔最好不超过3分钟。有可能时,可通过输液泵给药。 4 本品必须在医生指导下使用。 【特殊人群用药】 儿童注意事项: 儿童使用本品的安全性资料尚未建立。 妊娠与哺乳期注意事项: 避免孕妇使用本品,除非无其它安全替代措施。 老人注意事项: 老年患者使用本品的安全性资料尚未建立。 【药物相互作用】 本品可延长环已烯巴比妥导致的睡眠时间,而且加剧戊烯四唑的作用,所以不应与这类药物或产生同样作用的药物同时使用。 由于生长抑素与其他药物的相互作用未建立,所以建议应单独给药。 【药理作用】 生长抑素是人工合成的环状十四氨基酸肽,其与天然生长抑素在化学结构和作用机理上完全

思他宁(注射用生长抑素)

思他宁(注射用生长抑素) 【药品名称】 商品名称:思他宁 通用名称:注射用生长抑素 英文名称:Somatostatin for Injection 【成份】 本品主要成份及其化学名称为:生长抑素醋酸盐 分子式:C76H104N18O19 S2 分子量:1638。 【适应症】 严重急性食道静脉曲张出血。严重急性胃或十二指肠溃疡出血,或并发急性糜烂性胃炎或出血性胃炎。胰、胆和肠瘘的辅助治疗。胰腺术后并发症的预防和治疗。糖尿病酮症酸中毒的辅助治疗。 【用法用量】 药物冻干粉须在使用前用生理盐水溶解。思他宁采用静脉给药,通过慢速冲击注射(3至5分钟)250微克或以每小时250微克的速度连续滴注(约相当于每公斤体重,每小时3.5微克)给药。对于连续滴注给药,须用1支3毫克的思他宁配制足够使用12小时的药液,溶剂既可以是生理盐水,也可以是5%的葡萄糖溶液,输液量应调节为每小时250微克,并建议使用输液注射器。对严重急性上消化道出血(包括食道静脉曲张出血) 的治疗:建议首先缓慢静脉注射250微克思他宁,作为负荷剂量,而后立即进行每小时250微克的静脉点滴给药。当两次输液给药间隔大于3至5分钟时,应重新静脉注射250微克思他宁,以确保给药的连续性。当大出血被止住后(一般在12至24小时内),治疗应继续48 至72小

时,以防止再次出血。对于上述病例,通常的治疗时间是120小时。对胰瘘、胆瘘、肠瘘的辅助治疗:应采用每小时250微克的速度静脉连续点滴给药,直到瘘管闭合(2至20天),这种治疗可作为全胃肠外营养的辅助措施。当瘘管闭合后,思他宁静脉点滴应继续进行1至3天,而后逐渐停药,以防反跳作用。对胰腺外科手术后并发症的预防和治疗:手术开始时,作为辅助治疗,以每小时250微克速度点滴思他宁;手术后,持续点滴给药5天。对糖尿病酮症酸中毒的辅助治疗:对酮症酸中毒的患者,以每小时100至500微克的速度静脉点滴思他宁同时配合胰岛素治疗,3小时内可缓解酮症酸中毒,4小时内可使血糖恢复正常。 【不良反应】 少数病例用药后产生恶心、眩晕、脸红等反应。当滴注思他宁的速度高于每分钟50微克时,病人会发生恶心和呕吐现象。 【禁忌】 已证实对于思他宁药物过敏的病人,不得使用此药。避免孕妇使用本品,除非无其它安全替代措施。 【注意事项】 1 由于本品抑制胰岛素及胰高血糖素的分泌,在治疗初期会引起短暂的血糖水平下降。特别是胰岛素依赖型糖尿病患者,使用本品后每隔3-4小时应测试一次血糖浓度。同时,给药期间应避免给予胰岛素所要求的葡萄糖。在必要情况下,应同时使用胰岛素; 2 本品必须在医生指导下使用。 【特殊人群用药】 妊娠与哺乳期注意事项: 避免孕妇使用本品,除非无其它安全替代措施。

安装系统的几种方法

一、光盘安装 1、安装盘安装 这是最常规的方法,也是最基本的方法,特点是安全、稳定,缺点是速度慢,需要另外安装驱动程序和软件。简单介绍一下步骤,开机进入BIOS,设置从光驱启动(CD-ROM),放入安装盘,重启电脑,选择相应的菜单,就会进入windows安装程序,选择你想安装的分区,然后根据需要对其进行重分区或格式化操作,然后回车,开始安装。期间会碰到输入密钥、时区、键盘类型等信息,一一输入即可,如果用的是无人职守安装盘,等着就行了,重启几次后,就安好了,记得还要安装驱动。 2、ghost盘安装 GHOST意为幽灵,是赛门铁克公司推出的硬盘分区备份恢复软件,具有简单易行、速度快的特点,一般在ghost光盘启动后会有一键恢复到C盘的选项,也可以进入WINPE,在PE环境下运行GHOST,进行分区恢复。打开GHOST后,先点一下OK,然后依次选择local→partition →from image,找到合适的映像文件,然后选择需要恢复的分区,一般是C盘,确定后等上最多七八分钟就可以了,重启后会进入一个安装程序界面,这是在给你的电脑安装驱动、常用软件的过程,再次重启,系统就装好了。 二、U优盘安装 这个方法适用于没有光驱的电脑。要求电脑支持USB启动,当然,只要不是太旧的电脑,一般都支持的。其中制作相应的启动盘是关键。安装前记得进入BIOS,设置相应的启动方式。 1、优盘启动盘安装

可以是DOS启动盘,或者是PE启动盘,另外需要有GHOST 映像或者光盘映像。开机设置启动方式,这个根据启动盘的模式,可以是USB-HDD、USB-ZIP、USB-FDD等,DOS环境下,打开GHOST,然后还原C盘分区,在PE环境下,也可以打开GHOST 还原分区,这两种方法和用ghost盘安装方法是一样的,只是实现途径不一样。在PE下还可以用虚拟光驱加载光盘映像,然后运行相应的安装程序,开始系统安装,这和安装盘安装方法类似。 2、量产U盘为CD-ROM 准备好U盘、光盘镜像和量产工具,一步一步制作好启动盘,然后,进入BIOS,设置为USB-CDROM启动,随后方法就和光盘安装方法一样了,不过速度要比光盘安装快,这个和优盘读写速度快有关。 三、硬盘安装 这个安装方法几乎不需要什么别的硬件,速度也快。需要可以安装到硬盘的pe,光盘镜像。先在硬盘上安装PE,然后重启,进入PE环境,运行虚拟光驱,加载光盘镜像。还是那样,根据光盘镜像的类型,是安装盘就运行相应的安装程序,是ghost盘就运行ghost恢复C盘分区。 还有就是如果要安装双系统,那么用硬盘安装就方便多了,不用刻盘,也不用制作启动优盘,只要先进入已有的系统,加载光盘镜像,然后运行相应的安装程序就可以了。这里如果是安装盘镜像,启动菜单就已经修改好了,如果是ghost盘,那么,还要使用相应的软件修改启动菜单。

三腔二囊管的应用及护理

三腔二囊管的应用及护理 概述 上消化道出血是临床上常见的症状,引起上消化道出血的病因很多,其中以食管、胃、十二指肠、胰或胆管疾病引起的出血占首位,其次是门静脉高压引起的食管、胃底静脉曲张破裂出血,后者出血量大,发病急骤,来势凶猛,一般的止血药物难以凑效,需立即安置三腔二囊管压迫止血。经鼻腔插入三腔二囊管,进入胃腔后充气使管端的气囊膨胀,然后向外牵引,用以压迫胃底的曲张静脉。然后再充气使位于食管下段的气囊膨胀,即可压迫食管的曲张静脉,一般均获得满意效果。三腔二囊管压迫止血是门静脉高压导致的食管胃底静脉曲张破裂出血最方便、高效、安全的方法,因此,迅速成功完成三腔管的置入,使其达到有效的止血目的是抢救成功的关键。 适应证 食管胃底静脉曲张大出血病人药物治疗不理想者用,为内镜及手术治疗赢得时间。 操作前准备 三腔二囊管,石蜡油,手套,听诊器,20或50ml注射器,棉签,胶

布,止血钳,弯盘,温开水适量,开口器,压舌板,纱布,绷带,0.5kg 重的沙袋,牵引架。 应用三腔二囊管的告知程序 (一) 首先由护士告知患者或家属三腔二囊管主要是用于食管、胃底静曲张破裂出血,它是利用膨胀的气囊压迫出血部位以达到止血的目的。 (二) 操作前医生应向家属交代病情,明确插三腔二囊管的必要性,以取得家属的理解和患者配合,同时还应向家属交代因个人健康状况、个体差异以及某些不可预测的因素,在插三腔二囊管的过程中也有可能出现下列情况:1 .鼻咽部损伤。 2.止血效果不理想,甚至无效。 3.气囊破裂。 4.剌激咽喉胃肠后,出现呕吐、窒息。 5.剌激咽喉引起心脑血管意外,如心脏骤停。 (三) 医生和护士在操作过程中,一定会按医疗操作程序,仔细观察和正规操作,最大限度的避免上述并发症的发生。一旦发生上述并发症,将立即采取相应措施,请患者和家属放心。(四) 操作时嘱患者如有出现呕血时,将头偏向一侧,尽量将口中血液吐出,防止发生窒息。 (五) 当三腔二囊管插至咽喉处时,嘱患者做吞咽动作,操作者会配合其吞咽动作,顺利完成操作。(六) 感谢患者、家属的配合。操作步骤1、先用注射器分别向食管囊和胃囊注气,检查充气后是否均匀,置入水中,检查是否漏气。抽尽气囊内的气体,食管囊及胃囊的管口。做好标记,三腔管前端涂以液体石蜡备用。操作者戴手套。

格兰仕微波炉正确使用方法

微波炉正确使用方法 A:使用前要详细阅读《使用手册》。 家用微波炉专为家庭加热及烹调食物而设计,故不适用于其他商业用途。精品文档,你值得期待 B: C:用户在使用微波炉之前,应检查所用器皿是否适用于微波炉。 ⑴微波烹调时切勿使用金属网架及其它金属器皿,不应使用带金边、银边的器皿。微波炉中通常使用陶瓷、耐热玻璃、 耐热塑料等器皿。 ⑵使用光波微波组合烹调时,切勿在金属网架上放置铝制或其它金属容器。金属网架不应接近炉腔内壁,以防止打火。 ⑶使用保鲜纸遮盖食物烹调时,请将保鲜纸一角摺上,使蒸汽可以排出。煮好后将保鲜纸小心拆开,避免蒸汽灼伤。D:烹调前应先放入转盘支撑及玻璃转盘,再将盛好食物的器皿放在玻璃转盘上进行烹调。 E:烹调少量食物时,要多加观察,防止过热起火。不要用微波炉储存任何食物。 F:当食物在塑料、纸或其它可燃材料制成的简易容器中加热或烹调时,应随时注意,防止起火。 G:从微波炉内拿出食物和器皿时,应当使用隔热手套,以免高温烫手。 H:使用烧烤、光波烹调时,炉内温度很高,故翻转食物应戴上隔热起火手套,且切勿触碰内上板。 I:为防止玻璃转盘损坏,请遵守下列事项: ⑴烹调完食物,应先待转盘冷却后再进行清洗。 ⑵切勿将冰冷食品或冰冷器皿放置在炽热的转盘上。 ⑶转盘的最大负载重量不能超过5公斤。

J:如果微波炉因碰撞、跌落引起炉门、门封、铰链、外壳等发生损坏,请勿继续使用, 必须由专业维修人员检修后才可使用。 K:使用微波炉烹调食物时应注意: ⑴切勿煮带壳蛋,压力会使蛋爆裂。应先将蛋打破,要用牙签刺破蛋黄、蛋白数次。 ⑵已煮好的汤圆、荷包蛋等,马上取出可能会因其内部液体沸腾爆破而溅伤人体。应打开炉门后略搁置一会儿,再取 出食物。 ⑶烹调食物时不要把时间设置过长,因为煮食时间不足可继续,时间过长则无法补救。 ⑷烹调食谱所提供的是烹调的大约时间,影响烹调时间的因素有:依个人喜好的煮食程度,食物的初温、形状大小、 份量和使用器皿的形状、大小以及食物的排列、遮盖、翻搅等。烹调时需参阅食谱中的“微波炉烹饪技巧”,再参照以上因素,适当调整烹调时间。 ⑸表面无孔的食物(如:蛋、板栗、土豆、香肠等),请去皮或在外皮上开一裂缝或叉几个小孔,否则受热膨胀,可 能发生爆裂。 ⑹一般情况下不可用微波炉煎炸食物,除非使用质量可靠的特制微波煎碟。具体参阅《格兰仕微波食谱》的有关内容。 ⑺光波、烧烤烹调时,不可遮盖食物,因为食物需要直接吸收光波和烧烤的热能。 L:微波炉停止使用时,应将炉门稍稍敞开,使炉腔内水蒸气充分散发,有利于腔体的保养。 在使用微波炉后先不要马上将微波炉的门关上,等一,二分钟后再关上。因为要先将微波炉 内的热气散去后再关,这样可以减少内部接插件的氧化

使用Xilinx CORE Generator

使用Xilinx CORE Generator心得 初步使用Xilinx CORE Generator: 参考书籍:《Xilinx ISE 5.x 使用详解》EDA先锋工作室 P63-P72:IP核生成工具——CORE Generator 1. 对于如何在工程中加入IP核,是很简单的,我在未看书之前,就可根据提示挑选适当的核,对核进行参数设置,将核加入工程。 2. 接下来是如何使用,在这里,由于我主要使用VHDL语言,仿真工具用ModelSim6.0,综合工具主要使用Synplify7.7,我就只说在这样的环境下如何对该IP核进行元件例化,进行项目配置,并进行仿真与综合。 2.1 元件例化 可使用ISE的Laguage Template,也就是Xilinx 6.2 ISE中工具栏右上角的小灯泡,在COREGEN目录下,你会发现,你所用到的IP核的例化语句已经出现在模板里,拷过去就可以直接用了(当然你可能也要视情况进行必要的改动)。 3. 仿真 这里,最主要的问题是库,由于使用了IP核,所以要把XilinxCroeLib加入ModelSim库中。我的经验是:先在当前工程的目录下创建一个xilinxcorelib库,然后把该库文件剪切到modelsim根目录下,最后在modelsim下,选中该库,点击右键选择Edit,将路径高到modelsim下。然后将xilinx\vhdl\src\xilinxcorelib编译到该库中。此时要注意,由于库文件的关联性,第一次不可能全部编译通过,连续三次后,大多数核就在库中,只有少数几个不能通过编译。 4. 综合 由于综合过程中,提示如下(下面是我在comp.arch.fpga上所发的问题): In my project,there's a xilinx IP core. I want to use the synplify7.7 to synthesize it, but there's a warning when synthesize . The warning is : @W: CD280 :"G:\project\itu656_dec\itu656_Decoder.vhd":29:10:29:19|Unbound component counter_11 mapped to black box @W: CD280 :"G:\project\itu656_dec\itu656_Decoder.vhd":37:10:37:18|Unbound component counter_4 mapped to black box my project nane is itu656_dec : a decoder for itu 656 video The following code has been used in my project: component counter_11 port ( Q: OUT std_logic_VECTOR(10 downto 0); CLK: IN std_logic; CE: IN std_logic; ACLR: IN std_logic); end component; component counter_4

生长抑素

注射用生长抑素 【适应症】 1.严重急性食道静脉曲张出血; 2.严重急性胃或十二指肠溃疡出血,或并发急性糜烂性胃炎或出血性胃炎;3.胰腺外科手术后并发症的预防和治疗; 4.胰、胆和肠瘘的辅助治疗; 5.糖尿病酮症酸中毒的辅助治疗。 【用法与用量】 静脉给药。 通过慢速冲击注射(3~5分钟)0.25mg或以每小时0.25mg的速度连续滴注给药(一般每小时每公斤体重用药量为0.0035mg)。 临使用前,每支冻干剂用1ml生理盐水溶解。 对于连续滴注给药,须用本品3mg配备够使用12小时的药液(溶剂可为生理盐水或5%的葡萄糖注射液),输液量调节在每小时0.25mg。 1.严重急性上消化道出血包括食道静脉曲张出血的治疗:首先缓慢静脉推注0.25mg(用1ml生理盐水配制)作为负荷量,而后立即进行以每小时0.25mg的速度持续静脉滴注给药。当两次输液给药间隔大于3-5分钟的情况下,应重新静脉注射本品0.25mg,以确保给药的连续性。当出血停止后(一般在12-24小时内),继续用药48-72小时,以防再次出血。通常常的治疗时间是120小时。 2.胰瘘、胆瘘和肠瘘的辅助治疗:以每小时0.25mg的速度静脉连续滴注,直到瘘管闭合(2~20天),这种治疗可以用作全胃肠外营养的辅助措施。当瘘管闭合后,应继续用药1~3天,而后逐渐停药,以防反跳作用。 3.胰腺外科手术后并发症的治疗:在手术开始时,以每小时0.25mg的速度静脉滴注,术后持续静滴5天。 4.糖尿病酮症酸中毒的辅助治疗:以每小时0.1~0.5mg的速度静脉滴注,作为胰岛素治疗(10单位冲击后每小时1~4.8单位静滴)的辅助措施,在4小时内可以使血糖恢复正常,在3小时之内缓解酮症酸中毒。 【不良反应】 少数病例用药后出现恶心、眩晕、面部潮红。当注射速度超过每分钟0.05mg时,病人会发生恶心和呕吐现象。 【禁忌症】对本品过敏者禁用。 【注意事项】 (1)由于本品抑制胰岛素及胰高血糖素的分泌,在治疗初期会导致血糖水平短暂的下降;

软盘、光盘、硬盘克隆

软盘、光盘、硬盘克隆一个也不能少 经常玩电脑朋友,肯定常常复制软盘,那么如何才能使复制的软盘与源盘文件完全一样,引导信息、文件分配表(FAT)都完全一样呢?甚至将源盘作成IMG映像保存到硬盘上,在需要时再做成软盘呢? 如何将光盘做成一个文件,以便于存放到硬盘上,或再刻录出与源光盘一模一样的光盘呢? 如何将硬盘的启动分区做成一个文件,在操作系统出现问题时,能够整盘恢复回去,使操作系统恢复正常,而省去了重新安装操作系统和各种驱动程序的烦恼呢? 下面分别进行介绍,不过这需要三款工具的帮忙,它们分别是HD-Copy、WinIso、Ghost, 一、软盘的克隆 使用过DOS的朋友大多都使用过HD-COPY,它是德国人Oliver Fromme编写的一个磁盘对拷程序。功能非常强大,可以用作格式化软盘、软盘扩容、修复坏软盘、保存软盘信息、读取坏软盘、清洗软驱磁头等用处。最大的好处是它能将源盘“克隆”成一个映像(IMG格式),在需要做成软盘时再恢复就可以了。所以从92年问世至今一直都深受人们的喜爱。 HD-COPY的使用非常简单,在DOS下运行HD-Copy,其主界面如图1,菜单中的英文依次为READ(读取)、WRITE(写入)、VERIFY DESTINATION(校验目标盘)、VERIFY SOURCE(校验源盘)、FORMAT DESTINATION(格式化磁盘)、PUT TO FILE(存入映象文件)、GET FROM FILE(读取映象文件)、SPECIAL MENU(特殊菜单)、ABOUT(关于)、Escapr(exit) (退出),菜单栏的右侧是一些开关。 图1

克隆软盘的操作方法是:先启动HD-COPY再插入源盘,选择READ(或按R键)读取源盘信息到缓冲区(缓冲区是程序在内存中划出的一块用作临时数据交换的区域)。结束后再插入目标盘,选择Write(或直接按W)。如果目标盘中以前存有数据,HD-COPY将会问你是否确定覆盖(Y/N),当然是Y,然后程序将执行对拷动作。如果你不想拷贝目标盘,只想将源盘留一个备份(例如借来的软盘)可以在第一步完成后选择PUT TO FILE(按P键),输入你想要存放的路径和文件名。注意的是文件必须是DOS下的8.3格式,就是说文件名不能超过8个英文字母或4个中文字。将来需要的时候可以把你保存的映象文件找来GET FROM FILE(快捷键G)再执行第二步就可以了。 二、光盘的克隆 随着大容量硬盘的普遍采用,人们已经习惯将光盘拷贝成光盘映像文件使用,普遍采用的便是大名鼎鼎的ISO 9660国际标准格式,因此光盘映像文件也简称ISO文件。因为ISO文件保留了光盘中的全部数据信息(包括光盘启动信息),你可以方便地采用常用光盘刻录软件(如Nero Burning-ROM)通过CD-R/RW烧录成光碟,也可以通过虚拟光驱软件(如Daemon-Tools)直接使用。 WinISO 就是一个CD-ROM 映像文件格式转换工具,并且可以直接编辑光盘映像文件!通过WinISO,你可以在映像文件内部添加/删除/重命名/提取文件。你可以将其他格式的映像文件转换为标准的ISO 格式,同时你也可以从你的CD-ROM 中创建ISO 映像文件。将光盘“克隆”成ISO镜像文件的方法如下: 1.启动WinISO之后将欲克隆的光盘放入光驱中,点击菜单“操作”→“从CDROM制作ISO”项,弹出如图2所示的窗口,在其中的“来源CD-ROM”栏选择光盘所在的盘符,在“输出文件”栏设定好存放光盘镜像文件的路径和文件名,同时要在下部选中“ASPI”来制作ISO文件。 图2

Xilinx原语的使用方法1

Xilinx原语的使用方法1 3.4 Xilinx公司原语的使用方法 原语,其英文名字为Primitive,是Xilinx针对其器件特征开发的一系列常用模块的名字,用户可以将其看成Xilinx公司为用户提供的库函数,类似于C++中的“cout”等关键字,是芯片中的基本元件,代表FPGA中实际拥有的硬件逻辑单元,如LUT,D触发器,RAM等,相当于软件中的机器语言。在实现过程中的翻译步骤时,要将所有的设计单元都转译为目标器件中的基本元件,否则就是不可实现的。原语在设计中可以直接例化使用,是最直接的代码输入方式,其和HDL语言的关系,类似于汇编语言和C语言的关系。 Xilinx公司提供的原语,涵盖了FPGA开发的常用领域,但只有相应配置的硬件才能执行相应的原语,并不是所有的原语都可以在任何一款芯片上运行。在Verilog中使用原语非常简单,将其作为模块名直接例化即可。本节以Virtex-4平台介绍各类原语,因为该系列的原语类型是最全面的。其它系列芯片原语的使用方法是类似的。 Xilinx公司的原语按照功能分为10类,包括:计算组件、I/O端口组件、寄存器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM 组件、Slice/CLB组件以及G比特收发器组件。下面分别对其进行详细介绍。 3.4.1 计算组件 计算组件指的就是DSP48核,也有人将其称为硬件乘法器,功能描述如表3-6所示。 表3-6 计算组件清单 DSP48 其结构为一个18*18比特的有符号乘法器,且在后面还级联了一个带有可配置流水线的3输入加法器 DSP48核由一个18比特的乘法后面级联一个48比特的加法器,乘法器和加法器的应用位宽分别可以在18、48比特内任意调整。其在乘加模块中有广泛应用,特别是各类滤波器系统中,不仅可以提高系统稳定性,还能够节省逻辑资源且工作在高速模式下。其在Verilog中的例化模版为: module fpga_v4_dsp48( BCOUT, P, PCOUT, A, B, BCIN, C, CARRYIN,CARRYINSEL, CEA, CEB, CEC, CECARRYIN, CECINSUB, CECTRL, CEM, CEP, CLK, OPMODE, PCIN, RSTA, RSTB, RSTC, RSTCARRYIN, RSTM, RSTP,

超级一键使用方法

进行网克需要的条件: 一键网克软件:超级一键网克,当然其他的网克软件也可以。 一台已经装好系统的机器(操作系统98以上即可,推荐XP)用作服务器, 一台已经装好全部软件并且配置好的机器作为母盘,当然,如果你只对系统盘进行网克的话,这台机器也可以兼做服务器,但是如果你想全盘网克的话,那就需要另外一台机器做服务器了,道理嘛,因为做全盘镜像的时候镜像文件当然不可能放在源盘上,而必须放在另外一块硬盘上,就好象你左手永远不可能摸到左手的手背一样,呵呵。 其它客户机,数量255台以下,当然多于255台也可以,只是下面的IP地址和子网掩码要重新配置,大家参看有关资料。不过我想大家一次网克也不可能会有那么多台机器的,呵呵。 注意事项:首先,这些机器间物理网络要保持畅通(废话!)。另外,如果你的网吧是杂牌军的话,那就不要试了,因为每台机器的配置如果不一样的话,所装的驱动也不一样,否则网克后可能有太多的不可预知的后果,经常蓝屏肯定是家常便饭了,当然也有可能根本就启动不了。以上说的配置主要是显卡和主板(如果你的声卡是集成的话)。硬盘无所谓,但要注意,目标盘的容量一定要大于母盘。当然了,最好是配置完全一样,这样基本上不会出什么问题。 当然,如果你的机器配置不一样的话,也可以进行网克,大家可以把雨林木风ghost版里面的ghost文件提取出来作为镜像,这样也比一台一台装系统要快得多了。不过那应该是分区网克,具体方法你学会了全盘网克那自然不在话下。下面开工。 第一步,制作镜像,如果只制作系统盘的镜像,那么在单机操作就行了。具体操作我想大家都会。下面讲的是制作全盘镜像,当然你不必拆开机器挂两个硬盘了,网克嘛! 1、配置tftpd32

三腔二囊管的使用

三腔二囊管的使用 是利用柔软的气囊压力,直接压在出血的曲张静脉上,以达到止血 2)适应证:食管、胃底静脉曲张破裂出血者. 1、目的及用物准备 (1)目的: ①三腔管是抢救门静脉高压并上消化道大出血的用品。 ②三腔管其中之一胃咸压管为胃减压作用. ③三腔管其中之二胃囊管经充气后可压迫胃底,达到止血作用. ④三腔管其中之三食管囊管经充气后可压迫食管下段,达到止血作用。 (2)用物准备: ①治疗盘、治疗巾:盘内放三腔双囊管、20ml及50ml注射器各1支、止血钳1把、弯盘1个、液体石蜡、纱布数块. ②床边牵引装置有0.5kg的砂袋、滑车牵引固定架、绷带。 2、操作与护理及注意事项 (1)操作与护理: ①病人因消化道大出血,引起精神紧张,所以插三腔管前护士应做好准备工作,说明插管的目的和方法,取得合作。因人施护:有针对性地向病人及家属作解释,并给病人作深呼吸和吞咽示范动作,以便配合。烦躁不安者可先肌注异丙嗪25mg或安定10mg。病房应安静、清洁 ②操作前,用50ml注射器分别向胃气囊管和食气囊管充气,检查是否漏气,并测定充盈后两者气体的容量和气压。 ③将三腔管之前端及气囊涂以液体石蜡油,用注射器抽尽气囊内的气体. ④协助病人半卧位,清洁鼻腔,用地卡因喷雾器进行咽喉部喷雾,使其达到表面麻醉作用。将管经鼻腔徐徐插入,至咽部嘱病人做吞咽动作以通过三腔管。深度约60-65cm时,用20ml注射器抽吸胃减压管,吸出胃内容物,表示管端确已入胃。 ⑤用50ml注射器分别向胃囊管注气150—200ml,囊内压力2。67-5。34kPa。以止血钳夹住胃囊管,随后改用管钳。缓慢向外牵拉三腔管遇有阻力时表示胃气囊已压向胃底贲门部,用胶布将管固定于病人鼻孔外。 ⑥再用 50ml注射器向食囊管注气100-120ml,囊内压力4.67—6kPa,即可压迫食管下段.用止血钳夹住食管囊管,然后改用管夹。胃管囊和食管囊须分别标记。 ⑦用绷带缚住三腔管,附以0。5kg的砂袋,用滑车固定架牵引三腔管。 ⑧冲洗胃减压管,然后连接于胃肠减压器,观察胃内是否继续出血。亦可注入每100ml内含8mg 去甲肾上腺素的冰盐水等。 ⑨出血停止24小时后,可放去食管囊内的气体,放松牵引,继续观察24小时,确无出血时再将胃气囊放气。拔管时将气囊内之余气抽净.嘱病人口服石蜡油20-30ml,再缓慢的拔出管子。(2)注意事项: ①用前应该检查管和囊的质量.橡胶老化或气囊充盈后囊壁不均匀者不宜使用。 ②防止三腔管被牵拉出来,必须先向胃气囊内充气,再向食管囊充气。其充气量太少达不到止血目的;充气量过多,食道易发生压迫性溃疡。注气应从胃气囊开始,再充气管囊,放气顺序相反③为了避免食道与胃底发生压迫性溃疡,食管气囊每隔12小时放气1次,同时将三腔管向内送入少许。若出血不止.30分钟后仍按上法充气压迫. ④观察气囊有无漏气,每隔2—3小时测食管气囊压力1次,胃气囊只要向外牵拉感到有阻力即可断定无漏气。

微波炉实验

微波炉的拆装及检修 实验时间班级姓名 一、实验目的 1、了解微波炉的工作原理,简单结构及正确的使用方法。 2、学习和掌握微波炉的拆装方法。 3、掌握用常用仪表和工具检测微波炉。 二、实验仪表和用具 1、实验用微波炉1只 2、MF500型万用表1只 3、20W电烙铁1只 4、尖嘴钳1只 5、烧杯2只 6、温度计1只 三、实验内容与步骤 1、微波炉的拆装步骤 (1)把微波炉置于工作台上,打开炉门,取出玻璃转盘。 (2)用十字螺丝刀旋出外壳的紧固螺钉,取下外壳,然后用一根万用表表笔短接高压电容器的两极,给高压电容放电。 (3)用螺丝刀旋出位于微波炉右后侧,固定于后壳上的风扇的紧固螺钉,拔去电动机电源插片,取下风扇,再取下扇叶,旋出电动机的固定螺钉,取下电动机。 (4)旋出高压电容器的紧固螺钉,拔出高压电容器极上的电源插片,取下高压电容器,再旋开高压硅堆的外壳,取出其中的高压硅堆。 (5)拔下过热保护器上的电源插片,旋出紧固螺钉,取下过热保护器。 (6)旋出炉灯塑料外壳的紧固螺钉,拔下炉灯电源插片,取下炉灯外壳,再旋下炉灯。(7)拔除磁控管上的电流插片,旋出紧固螺钉,将磁控管取下。 (8)取下高压变压器上的连接件,旋出紧固螺钉,将高压变压器与底座分离。 (9)旋出电路板的紧固螺钉,拔出电路板上的各种电源线插头,取下电路板。注意各种电源线在线路板上的位置,根据电源线的颜色,应做出相应的标记,以防安装时电源线插错,烧毁电路板。 (10)拔出主联锁开关和副联锁开关上的电源插片,用一字螺丝刀轻轻拨开固定联锁开关的塑料卡,取下两只联锁开关,注意,千万不能折断塑料卡,否则,安装联锁开关时,联锁开关无法固定。 (11)旋出炉门的紧固螺钉,轻轻取下炉门,注意不要碰损炉门,以防炉门变形,使微波泄漏。 (12)用一字螺丝刀轻轻拨开控制面板内侧的塑料卡,取下控制面板。旋出控制面板内侧的紧固螺钉。 (13)再把剩下的微波炉支架倒置于台面上,取下底板,旋出转盘电机紧固螺钉,拔除电源插片,取下转盘电机。 (14)微波炉的安装步骤和上述拆卸过程相反,注意各种电源线不能插错,且一定要插紧各种电源线。各种紧固螺钉要旋紧。