STM8低功耗设定及其例程

STM8低功耗设定及其例程

STM8有三种低功耗模式,即等待、活跃停机和停机。具体它们三者有什么区别自己看官方手册去吧,这里只讲停机模式的应用,其他的一笔带过!

一、进入的方式:

等待模式进入用的指令是WFI,而活跃停机和停机用的都是halt(),所不同的是,在执行halt指令之前,如果开启了AWU,则是活跃停机,反之则是停机。还有一点要说明的是,在停机模式下独立看门狗是不能养的,而只能养窗口看门狗。

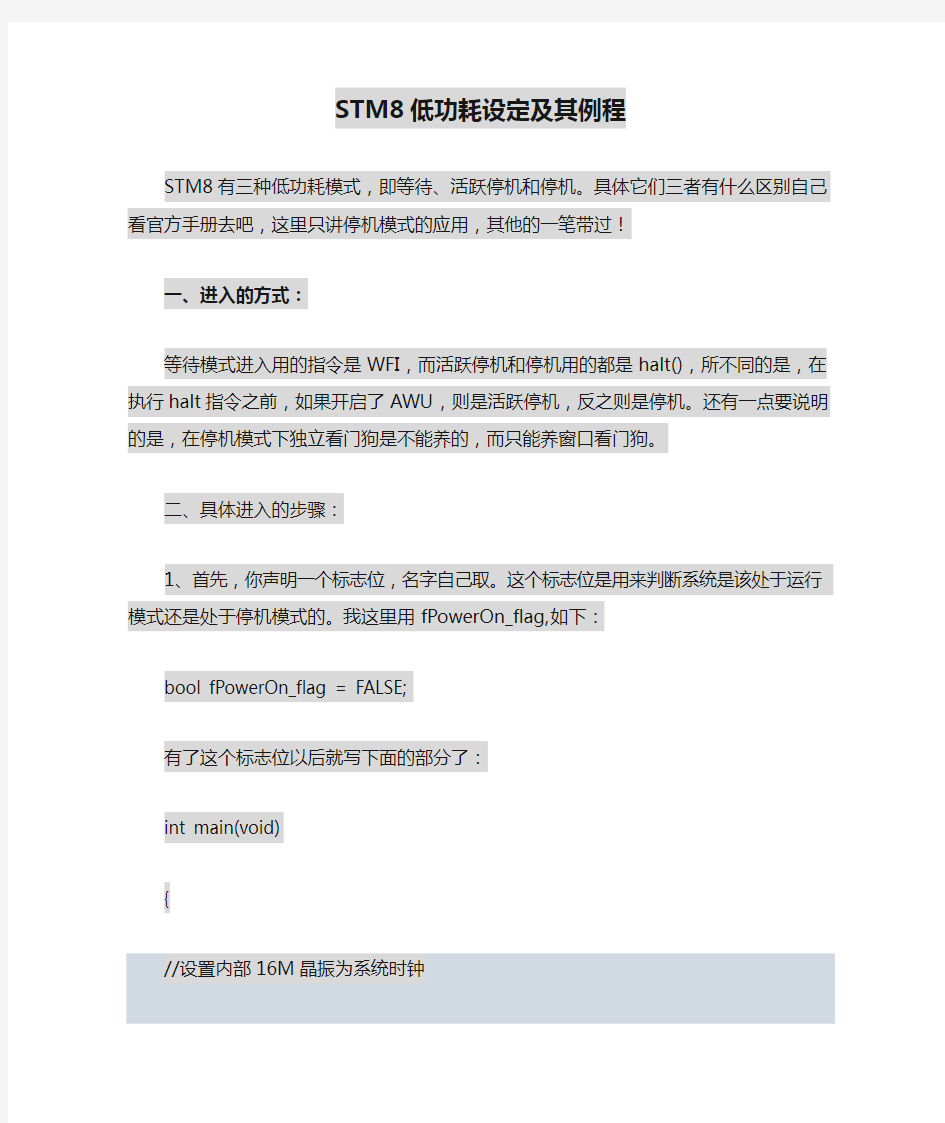

二、具体进入的步骤:

1、首先,你声明一个标志位,名字自己取。这个标志位是用来判断系统是该处于运行模式还是处于停机模式的。我这里用fPowerOn_flag,如下:

bool fPowerOn_flag = FALSE;

有了这个标志位以后就写下面的部分了:

int main(void)

{

//设置内部16M晶振为系统时钟

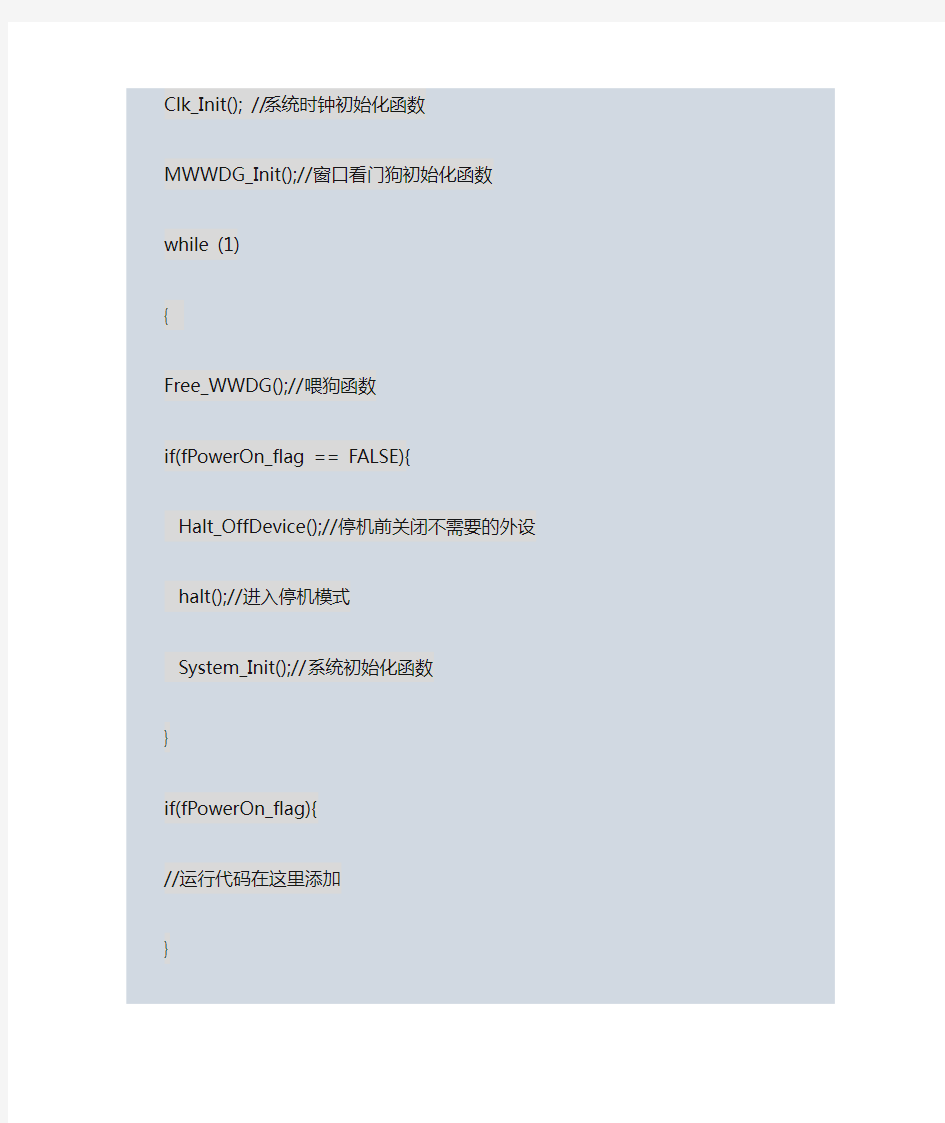

Clk_Init(); //系统时钟初始化函数

MWWDG_Init();//窗口看门狗初始化函数

while (1)

{

Free_WWDG();//喂狗函数

if(fPowerOn_flag == FALSE){

Halt_OffDevice();//停机前关闭不需要的外设

halt();//进入停机模式

System_Init();//系统初始化函数

}

if(fPowerOn_flag){

//运行代码在这里添加

}

}

}

以上就是一个停机模式的模板了,大家参照着用就可以了。系统上电默认是进入停机模式,然后通过按键唤醒进入运行模式。下面为大家讲一下主函数中每个函数的写法和功能吧!

2、各函数说明:

a、时钟初始化函数:

void Clk_Init(void)

{

CLK_DeInit();//复位时钟寄存器

CLK_HSICmd(ENABLE);//使能内部高速时钟

CLK_HSIPrescalerConfig(CLK_PRESCALER_HSIDIV4);//配置内部高速时钟(时钟分频器:4分频),系统时钟4MHz

CLK_ClockSecuritySystemEnable();//开启时钟安全系统

}

这个函数我想不用多讲了,大家都懂的。

b、窗口看门狗函数:

void MWWDG_Init(void)

{

WWDG_Init(COUNTERINIT, WINDOW);//COUNTERINIT = 0x7f,WINDOW = 0x77

}

这个是窗口看门狗初始化函数。

void Free_WWDG(void)

{

INT8U CounterValue;

CounterValue = (INT8U)(WWDG_GetCounter() & 0x7F);

/*

* 判断是否小于所设置的窗口上限值

* 只有小于窗口上限值才能清零

*/

if(CounterValue < WINDOW){

WWDG_SetCounter(COUNTERINIT);

}

}

这个是窗口看门狗喂狗函数,防止看门狗复位。

c、停机前外设设置函数:

void Halt_OffDevice(void)

{

//关闭设备前,设置系统主时钟,和中断

Clk_Init();

//CLK_HSIPrescalerConfig(CLK_PRESCALER_HSIDIV4);

ADC1_DeInit();

TIM1_DeInit();

//停机前关闭不需要的功能模块的时钟

CLK_PeripheralClockConfig(CLK_PERIPHERAL_TIMER3,DISABLE);

CLK_PeripheralClockConfig(CLK_PERIPHERAL_TIMER1,DISABLE);

CLK_PeripheralClockConfig(CLK_PERIPHERAL_ADC,DISABLE);

CLK_PeripheralClockConfig(CLK_PERIPHERAL_TIMER2,DISABLE);

CLK_PeripheralClockConfig(CLK_PERIPHERAL_TIMER4,DISABLE);

CLK_PeripheralClockConfig(CLK_PERIPHERAL_AWU,DISABLE);

CLK_PeripheralClockConfig(CLK_PERIPHERAL_I2C,DISABLE);

CLK_PeripheralClockConfig(CLK_PERIPHERAL_UART2,DISABLE);

GPIO_Init(GPIOA,GPIO_PIN_1|GPIO_PIN_2|GPIO_PIN_3,GPIO_MODE_OUT_PP_LOW_SLOW);

GPIO_Init(GPIOB,GPIO_PIN_HNIB,GPIO_MODE_OUT_PP_LOW_SLOW);

GPIO_Init(GPIOB,GPIO_PIN_2|GPIO_PIN_3,GPIO_MODE_OUT_PP_LOW_SLOW);

GPIO_Init(GPIOC,GPIO_PIN_1|GPIO_PIN_2|GPIO_PIN_3|GPIO_PIN_4,GPIO_MODE_OUT_PP _HIGH_SLOW);

GPIO_Init(GPIOC,GPIO_PIN_5|GPIO_PIN_6|GPIO_PIN_7,GPIO_MODE_OUT_PP_LOW_SLOW);

GPIO_Init(GPIOD,GPIO_PIN_LNIB,GPIO_MODE_OUT_PP_LOW_SLOW);

GPIO_Init(GPIOD,GPIO_PIN_4|GPIO_PIN_5|GPIO_PIN_6,GPIO_MODE_OUT_PP_LOW_SLOW);

GPIO_Init(GPIOE,GPIO_PIN_LNIB,GPIO_MODE_OUT_PP_LOW_SLOW);

GPIO_Init(GPIOE,GPIO_PIN_5|GPIO_PIN_6|GPIO_PIN_7,GPIO_MODE_OUT_PP_LOW_SLOW);

GPIO_Init(GPIOG,GPIO_PIN_0,GPIO_MODE_OUT_PP_LOW_SLOW);

GPIO_Init(GPIOG,GPIO_PIN_1,GPIO_MODE_OUT_PP_HIGH_SLOW);

InPut_Init();

enableInterrupts();

}

这个函数主要就是在停机前设置好系统的时钟,并且关闭一切不必要的外设的时钟,如AD,定时器等等的时钟。并且最重要的是要设置好系统唤醒的条件和使能中断。对于IO口的设置,对于外设是高电平工作的,那么设置成推挽输出低,对于是低电平工作的那么设置成推挽输出高。这里说明一下,浮空输入我不知道可不可以,大家可以试试。

d、唤醒口初始化设置函数:

void InPut_Init(void)

{

//与按键相连的引脚设置为输入模式

GPIO_Init(P_PortD,Power,GPIO_MODE_IN_PU_IT);

//将PD7引脚的TLI中断设置为下降沿中断,TLI是最高优先级中断

EXTI_SetTLISensitivity(EXTI_TLISENSITIVITY_FALL_ONLY);

GPIO_Init(P_PortA,CHARGE_IN,GPIO_MODE_IN_PU_IT);

//将GPIOD端口设置为上升沿触发中断--因为充电器插入时产生一个高电平,拔出时产生一个下降沿

EXTI_SetExtIntSensitivity(EXTI_PORT_GPIOA,EXTI_SENSITIVITY_RISE_FALL);

}

系统可以通过两个IO口里唤醒CPU,一个是按键,设置成最高优先级中断TLI,并且是下降沿中断。还有一个就是充电器插入唤醒中断,这里我的移动电源是要充电的,所以要做充电器的插入拔除检测,因此要设置成上升沿下降沿中断方式。

讲完以上的函数,大部分的功能都讲完了,剩下的就是在stm8s_it.c里面处理中断了。

按键唤醒中断处理:

INTERRUPT_HANDLER(TLI_IRQHandler, 0)

{

/* In order to detect unexpected events during development,

it is recommended to set a breakpoint on the following instruction.

*/

delay_ms(20);//延时消抖

if(!GPIO_ReadInputPin(P_PortD,Power)){

delay_ms(20);

time_count = 0;

if(fPowerOn_flag == FALSE){

fPowerOn_flag = TRUE;

}

else{

if(fExitDCPower_flag == FALSE) fPowerOn_flag = FALSE;

}

}

}

首先是20ms的延时,然后再次检测IO口的电平,如果为低,那么说明按键按下了,再延时20ms。然后处理系统工作的标志位。如果系统在停机模式,那么按下按键以后,系统进入工作模式;反之,系统进入停机模式。这里说明一下,那个else里面的处理要加入一个限制条件,就是在运行模式下再次按下唤醒按键时,要先判断充电器有没有插入,如果没有插入,则系统进入停机模式,如果插入了,系统则不处理,继续保持运行模式对电池充电。

充电器插入唤醒中断处理:

INTERRUPT_HANDLER(EXTI_PORTA_IRQHandler,3)

{

/* In order to detect unexpected events during development,

it is recommended to set a breakpoint on the following instruction.

*/

delay_ms(20);

if(GPIO_ReadInputPin(P_PortA,CHARGE_IN)){

delay_ms(20);

if(fPowerOn_flag == FALSE) fPowerOn_flag = TRUE;

if(fExitDCPower_flag == FALSE) fExitDCPower_flag = TRUE;

}

else{

delay_ms(20);

if(fExitDCPower_flag == TRUE) fExitDCPower_flag = FALSE;

}

这里的话我相信大家也应该看得懂的,就不多言了!

好了,今天就讲到这里了。我想已经讲得够详细了吧,还有什么问题的话可以发邮件给我。我的邮箱是610967340@https://www.360docs.net/doc/e917370819.html,!拜拜,新的一年祝大家身体健康、工作顺利!

集成电路低功耗设计方法研究【文献综述】

毕业设计文献综述 电子信息科学与技术 集成电路低功耗设计方法研究 摘要:随着IC制造工艺达到纳米级,功耗问题已经与面积、速度一样受到人们关注,并成为制约集成电路发展的关键因素之一。同时,由于电路特征尺寸的缩小,之前相比于电路动态功耗可以忽略的静态漏功耗正不断接近前者,给电路低功耗设计提出了新课题,即低漏功耗设计。本文将分析纳米工艺下芯片功耗的组成和对低漏功耗进行研究的重要性,然后介绍目前主要的低功耗设计方法。此外,由于ASIC技术是目前集成电路发展的趋势和技术主流,而标准单元是ASIC设计快速发展的重要支撑,本文在最后提出了标准单元包低漏功耗设计方法,结合电路级的功耗优化技术,从而拓宽ASIC功耗优化空间。 关键字:低功耗,标准单元,ASIC设计 前言: 自1958年德克萨斯仪器公司制造出第一块集成电路以来,集成电路产业一直以惊人的速度发展着,到目前为止,集成电路基本遵循着摩尔定律发展,即集成度几乎每18个月翻一番。 随着制造工艺的发展,IC设计已经进入了纳米级时代:目前国际上能够投入大规模量产的最先进工艺为40nm,国内的工艺水平正将进入65nm;2009年,Intel酷睿i系列创纪录采用了领先的32nm 工艺,并且下一代22nm工艺正在研发中。但伴随电路特征尺寸的减小,电路功耗数值正呈指数上升,集成电路的发展遭遇了功耗瓶颈。功耗问题已经同面积和速度一样受到人们重视,成为衡量IC设计成功与否的重要指标之一。若在设计时不考虑功耗而功利地追求集成度的提高,则可能会使电路某些部分因功耗过大引起温度过高而导致系统工作不稳定或失效。如Intel的1.5GHz Pentium Ⅳ处理器,拥有的晶体管数量高达4200万只,功率接近95瓦,整机生产商不得不为其配上了特大号风扇来维持其正常工作。功耗的增大不仅将导致器件的可靠性降低、芯片的稳定性下降,同时也给芯片的散热和封装带来问题。因此,功耗已经成为阻碍集成电路进一步发展的难题之一,低功耗设计也已成为集成电路的关键设计技术之一。 一、电路功耗的组成 CMOS电路中有两种主要的功耗来源,动态功耗和静态功耗。其中,动态功耗包括负载电容的充放电功耗(交流开关功耗)和短路电流引起的功耗;静态功耗主要是由漏电流引起的功耗,如图1所示。

MRS201低功耗霍尔元件

TMR 超低功耗全极磁开关 概述 是一款集成了隧道磁阻(TMR )传感器和CMOS 技术,为高灵敏度、高速、低功耗、高精度应用而开发的全极磁开关。采用高精度推挽式半桥TMR 磁传感器和CMOS 集成电路,包括TMR 电压发生器、比较器、施密特触发器和CMOS 输出电路,能将变化的磁场信号转化为数字电压信号输出。通过内部电压稳压器来提供温度补偿电源,并允许宽的工作电压范围。以低电压工作、1微安级的供电电流、高响应频率、宽的工作温度范围、优越的抗外磁干扰特性成为众多低功耗、高性能应用的理想选择。采用两种封装形式:SOT23-3和TO-92S 。 功能框图 产品特性 ? 隧道磁电阻 (TMR) 技术 ? 1.5微安超低功耗 ? 高频率响应可达1kHz ? 全极磁开关 ? 高灵敏度,低开关点 ? 宽工作电压范围 ? 卓越的温度稳定性 ? 优越的抗外磁场性能 典型应用 ? 流量计,包括水表、气表和热量表 ? 接近开关 ? 速度检测 ? 线性及旋转位置检测 磁开关MRS201MRS201MRS201MRS201MRS201MRS201

管脚定义 TO-92S SOT23-3 极限参数 性能参数(V CC = 3.0V, T A = 25°C) 注:在以上测试中,电源和地之间需连接一个0.1μF的电容。

磁特性(V CC = 3.0V, T A = 25°C) 电压和温度特性 输出和磁场关系 注:上电时,在工作磁场为零时,输出信号为高电平。 磁场感应方向磁场强度

MRS201应用指南 封装尺寸 SOT23-3封装图: 平行于TMR 传感器敏感方向的磁场超过工作点门限︱B OPS ︱(︱B OPN ︱)时,输出低电平。当平行于TMR 传感器敏感方向的磁场低于释放点︱B RPS ︱(︱B RPN ︱)时,输出高电平。磁场工作点和释放点的差值就是传感器的回差B H 。 为了降低外部噪音,推荐在传感器电源和地之间增加一个滤波电容(靠近传感器)。如应用电路图所示,典型值为0.1μF 。 MRS201

超低功耗电路的设计原则及设计分析

超低功耗电路的设计原则及设计分析 以手机为代表的电池供电电路的兴起,为便携式仪表开创了一个新的纪元。超低功耗电路系统(包括超低功耗的电源、单片机、放大器、液晶显示屏等)已经对电路设计人员形成了极大的诱惑。毫无疑问,超低功耗电路设计已经对低功耗电路提出了挑战,并将扩展成为电子电路中的一个重要应用领域。 虽然超低功耗设计仍然是在CMOS集成电路(IC)基础上发展起来的,但是因为用户众多,数千种专用或通用超低功耗IC不断涌现,使设计人员不再在传统的CMOS型IC上下功夫,转而选择新型超低功耗IC,致使近年来产生了多种超低功耗仪表。电池供电的水表、暖气表和煤气表近几年能够发展起来就是一个证明。目前,电池供电的单片机则是超低功耗IC的代表。 本文将对超低功耗电路设计原则进行分析,并就怎样设计成超低功耗的产品作一些论述,从而证明了这种电路在电路结构和性价比等方面对传统电路极具竞争力。 1 CMOS集成电路的功耗分析 无论是低功耗还是超低功耗IC,主要还是建立在CMOS电路基础上的。虽然超低功耗IC 对单元电路进行了新形式的设计,但作为功耗分析,仍然离不开CMOS电路基本原理。以74系列为代表的TTL集成电路,每门的平均功耗约为10mW;低功耗的TTL集成电路,每门平均功耗只有1mW。74系列高速CMOS电路,每门平均功耗约为10μW;而超低功耗CMOS 通用小规模IC,整片的静态平均功耗却可低于10μW。传统的单片机,休眠电流常在50μA~2mA范围内;而超低功耗的单片机休眠电流可达到1μA以下。 CMOS电路的动态功耗不仅取决于负载,而且就电路内部而言,功耗与电源电压、集成度、输出电平以及工作频率都有密切联系。因此设计超低功耗电路时不得不对全部元件的内外性质做仔细分析。 CHMOS或CMOS电路的功耗特性一般可以表示为: P=PD+PA

集成电路

集成电路设计综述 杨超 (湖南工学院电气与信息工程学院湖南衡阳421000)【摘要】本文介绍了集成电路设计的各个阶段及其基本的特征,把集成电路设计流程划分为三个阶段: 需求分析系统设计、逻辑设计、物理设计, 并通过对每一阶段的叙述, 同时介绍了集成电路设计的方法和基本知识。最后描述了集成电路设计面对的问题和前景,集成电路技术遵循摩尔定律发展进入了纳米尺度, 功耗带来的挑战日益突出, 已经成为制约集成电路发展的瓶颈问题. 微电子技术的发展已经进入了“功耗限制” 的时代, 功耗成为集成电路设计和制备中的核心问题。降低功耗有可能替代原来提高集成度、缩小器件尺寸成为未来集成电路发展的驱动力。低功耗集成电路的实现是一项综合的工程, 需要同时考虑器件、电路和系统的功耗优化, 需要在性能和功耗之间进行折中. 随着集成电路进入纳米尺度, 适于低功耗应用的CMOS 技术平台由于MOSFET 泄漏导致的电流增大、寄生效应严重等问题愈发突出,目前的许多低功耗技术成为了“治标” 的解决方案, 难以从根本上解决集成电路发展中遇到的“功耗限制” 问题, 一定程度上影响了纳米尺度集成电路的可持续发展,本文在深入分析影响集成电路功耗的各个方面的基础上, 介绍了超低功耗集成电路的工艺、器件结构以及设计技术。 【关键词】集成电路设计,低功耗,微电子器件,逻辑设计,物理设计 1、引言 集成电路技术遵循摩尔定律发展进入了纳米尺度, 功耗带来的挑战日益突出, 已经成为制约集成电路发展的瓶颈问题,微电子技术的发展已经进入了“功耗限制”的时代, 功耗成为集成电路设计和制备中的核心问题,降低功耗有可能替代原来提高集成度、缩小器件尺寸成为未来集成电路发展的驱动力,低功耗集成电路的实现是一项综合的工程,需要同时考虑器件、电路和系统的功耗优化, 需要在性能和功耗之间进行折中。随着集成电路进入纳米尺度, 适于低功耗应用的CMOS 技术平台由于MOSFET 泄漏导致的电流增大、寄生效应严重等问题愈发突出,目前的许多低功耗技术成为了“治标” 的解决方案, 难以从根本上解决集成电路发展中遇到的“功耗限制” 问题, 一定程度上影响了纳米尺度集成电路的可持续发展. 本文在深入分析影响集成电路功耗的各个方面的基础上,介绍了超低功耗集成电路的工艺、器件结构以及设计技术,目前这种发展趋势至少可以持续到2026 年, 其器件的特征尺寸将缩小至 6 nm,因此, 在未来的较长一段时期内,硅基集成电路仍将是微电子技术的主流,传统集成电路设计, 以更小的面积、更快的速度完成运算任务是不懈努力的目标. 然而随着硅基集成电路技术发展到纳米尺度,面积与时间已经不再是集成电路设计中需要考虑的唯一目标, 功耗带来的挑战日益突出, 已经成为制约集成电路发展的瓶颈问题。 2、集成电路往低功耗方向发展 近50年来, 硅基集成电路技术一直沿着摩尔定律高速发展,根据2011 年国际半导体技术发展蓝图(ITRS) 的预测, 目前这种发展趋势至少可以持续到2026 年, 其器件的特征尺寸将缩小至 6 nm。 因此, 在未来的较长一段时期内, 硅基集成电路仍将是微电子技术的主流,传统集成电路设计, 以更小的面积、更快的速度完成运算任务是不懈努力的目标. 然而随着硅基集成电路技术发展到纳米尺度,面积与时间已经不再是集成电路设计中需要考虑的唯一目标, 功耗带来的挑战日益突出, 已经成为制约集成电路发展的瓶颈问题,在诸如手持和便携设备等产品中功耗指标甚至成为第一要素,例如, 苹果公司iPhone4S 手机的双核A5 处理器和三星公司Galaxy S3 手机的四核Exynos 4412 处理器均基于ARM 多核、超低功耗架构Cortex-A9,

数字集成电路低功耗设计

数字集成电路低功耗设计 摘要数字IC的低功耗设计是一个系统问题,必须在设计的各个层次上发展适当的技术,综合应用不同的设计策略,才能达到在降低功耗的同时还能维持较高的系统性能的目的。本文系统地总结了当前系统级芯片设计中的低功耗技术,并对功耗估计和分析以及不同设计层次的功耗优化方法分别进行了讨论。 关键词数字集成电路功耗估计功耗分析低功耗设计功耗优化 1 引言 近来,研究人员发现仅仅用时间和面积作为评价系统性能的指标是不够的。功耗是另一个非常重要的考虑指标。直到最近,相对于面积和速度指标而言,对功耗的考虑还被放在第二位。但是,近年来这种考虑方法正在开始改变,对功耗指标重要性的考虑逐渐提高到与面积和速度同等重要的高度。许多因素推动了这个趋势的发生。也许最明显的因素就是便携式电子系统的飞速发展。对于这些便携式电子系统应用,平均功耗已经变成一个最关键的设计指标。例如,用分立器件所搭建的一个便携式多媒体终端,由于没有进行低功耗的优化设计,其消耗的功率是40瓦。用先进的镍-金属-氰化物电池供电,每公斤重可以产生的电能约为65瓦*小时,支持这样的终端运行10小时就需要6公斤重电池,这是无法接受的。甚至用现在比较先进的电池技术如锂离子电池,每公斤重可以产生的电能为100瓦*小时,支持这个多媒体终端运行10小时,也需要4公斤锂离子电池。因此,如果没有低功耗设计,当前和未来的便携式电子设备要么需要非常重的电池组,要么电池的寿命非常短。 即使对于非便携式的设备而言,减小功耗也会起到非常关键的作用。例如,进行过性能优化的微处理器,在时钟频率为200MHz~500MHz的情况下,消耗的功耗典型值大约为40瓦~80瓦。微处理器的速度正在稳步提高,时钟频率已经达到了1GHz。在这样高的时钟频率下,它们消耗大约300瓦的功率是无法接受的,因为封装和散热设备的成本太高了。因而,除非功耗大大降低,否则因功耗而产生的热量必须限制封装和VLSI系统的性能。 动态功耗是IC功耗的主要组成部分,但随着深亚微米工艺的发展,之前微不足道的漏电流功耗呈指数级增大,甚至有超越动态功耗的趋势,这也使得新兴低功耗技术的研究显得更加重要和紧迫。 本文将介绍芯片功耗的主要来源、基本概念及其影响因素;针对这些功耗来源和影响因素,本文将分别考虑IC设计中不同抽象层次对电路功耗的影响,并比较各项低功耗技术的效果和存在的问题;此外,对功耗的优化也进行了详细的介绍。 2 功耗估计 功耗估计是指估计数字电路的平均功耗。理想情况下平均功耗应该包括静态功耗和动态功耗,然而在精心设计的CMOS电路中,容性功率占主导地位,因此平均功耗一般指的是容性功耗。这与模拟为电压降低问题的瞬时功耗或最坏情况功耗的估计有很大不同。在设计的每一个层次上,从低层的电路级、门级,到高层的结构级(RTL级)和行为级,有相应的功耗估计方法。

低功耗集成电路设计课程上机实验报告

低功耗集成电路设计 上机实验报告 课程名称低功耗集成电路设计 任课教师肖立伊 学生黄庆丰 学号 11SG21908

目录 实验一MOS管阈值电压随衬底偏置电压变化的模拟与分析 (1) 1.实验条件 (1) 2.实验过程 (1) 3.产生机理及用途 (1) 实验二MOS管亚阈值漏电流随漏源电压变化的模拟与分析 (3) 1.实验条件 (3) 2.实验过程 (3) 3.产生机理及用途 (3) 实验三晶体管堆叠效应减少漏电流的模拟与分析 (4) 1.实验条件 (4) 2.实验过程 (4) 3.产生机理及用途分析 (5) 实验四电平转换触发器设计 (6) 1.主从电平转换器 (6) 1)设计过程 (6) 2)模拟结果 (7) 2.脉冲预充触发电平转换器 (8) 1)设计过程 (8) 2)模拟结果 (9) 3.电平转换器用途 (10) 实验五偏置电压对6管存储单元功耗影响的模拟与分析 (11) 1.设计过程 (11) 2.功能模拟及功耗分析 (11) 3.降低功耗原理 (11)

实验一MOS管阈值电压随衬底偏置电压变化的模拟与分析 在本实验中,我们采用smic90nm工艺库中的型号为N10的NMOS管进行阈值电压与衬底偏置的分析,其中衬底偏压VB从-1V线性变化至1V。其电路原理图如下: 图 1 实验一仿真原理图 用Spectre进行仿真,我们得到了下图的仿真结果。 图 2阈值电压随衬底电压变化 如所示,在零偏时,器件的阈值电压243.2mV,而随着衬底电压从-1V至1V 的线性变化过程中,器件阈值电压也从320mV降至15mV,由此可见,衬底偏置能够显著改变阈值电压的变化。 3.产生机理及用途 MOS器件能够导电的原因是在栅氧化层下面形成反型层,从而形成导电沟道所致,而在衬底与源极之间施加负向偏压时将使沟道感应结上的压降增大,表面耗尽层的宽度增加,使得空间电荷区的负空间电荷增加,此时只有增加栅压才能维持强反型的条件,因而阈值电压增大,同理,当施加正向电压时,栅压降低,阈值电压下降。 阈值电压并不是一个恒定的参数,它将受到诸多参数的影响。其中,衬底偏

LP0001-超低功耗红外感应控制IC -V2.0

产品规格书 Data Sheet LP0001 【超低功耗红外感应控制IC 】 SHENZHEN LAND HOPE MICRO-ELECTRONICS LTD. 深圳市联德合微电子有限公司 LANDP LANDP LANDP LANDP LANDP LANDP LANDP LANDP LANDP LANDP LANDP LANDP LANDP LANDP LANDP LANDP LANDP LANDP LANDP LANDP

LP0001超低功耗红外感应控制IC 目录 概述 (3) 特点 (3) 产品应用 (3) 引脚定义 (3) 引脚描述 (4) 功能框图 (5) 功能描述 (5) 应用范例 (6) 极限参数 (8) 电气特性 (8) 封装数据 (9) 丝印说明 (9)

LP0001芯片数据手册V2.0 概述 LP0001是一款具有较高性能的传感信号处理集成电路。它配以热释电红外传感器和少量外接元器件构成被动式的热释电红外开关。它能自动快速开启各类白炙灯、荧光灯、蜂鸣器、自动门、电风扇、烘干机和自动洗手池等装置,特别适用于企业、宾馆、商场、库房及家庭的过道等敏感区域,或用于安全区域的自动灯光、照明和报警系统。 特点 工作功耗小,3V工作电源时功耗小于20uA,5V工作电源时功耗小于35uA,非常适合电池供电系统应用; 内设独立的延迟时间定时器和封锁时间定时器,时间可调节范围宽,所调时间长短不随芯片电源电压变化,只与外围选定的电阻电容值有关; 独立的高输入阻抗运算放大器,可与多种传感器匹配,进行信号与处理; 双向鉴幅器,可有效抑制干扰; 内置参考电压,供内部比较器和运放的参考电压; 工作电压范围2V~6V; 采用SOP16和DIP16封装形式; 引脚定义产品应用 红外线报警器; 红外线感应灯; 自动灯光照明系统; 自动门控制系统; 自动烘干机; 语音迎宾器;