基于Verilog的分频器设计

分频器是指使输出信号频率为输入信号频率整数分之一的电子电路。在许多电子设备中如电子钟、频率合成器等,需要各种不同频率的信号协同工作,常用的方法是以稳定度高的晶体振荡器为主振源,通过变换得到所需要的各种频率成分,分频器是一种主要变换手段。早期的分频器多为正弦分频器,随着数字集成电路的发展,脉冲分频器(又称数字分频器)逐渐取代了正弦分频器。下面以Verilog HDL 语言为基础介绍占空比为50%的分频器。

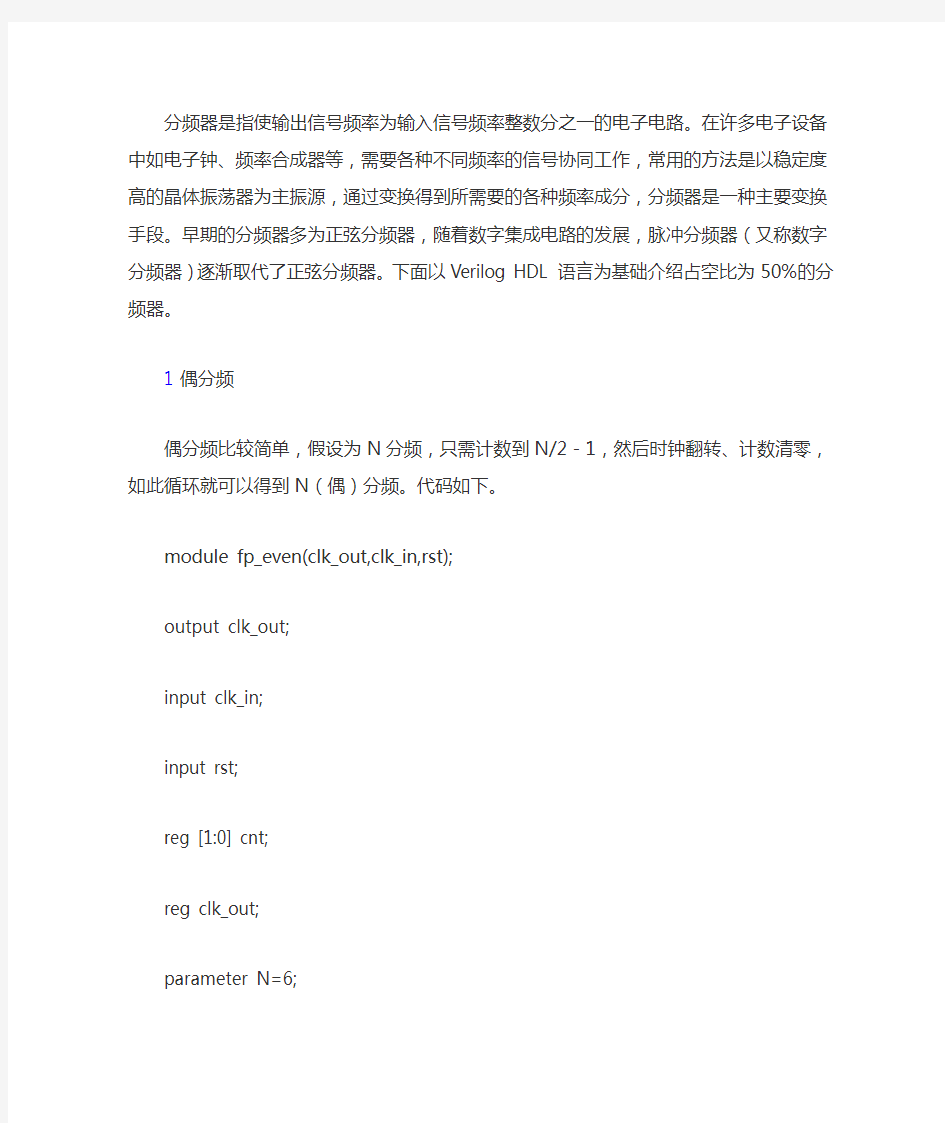

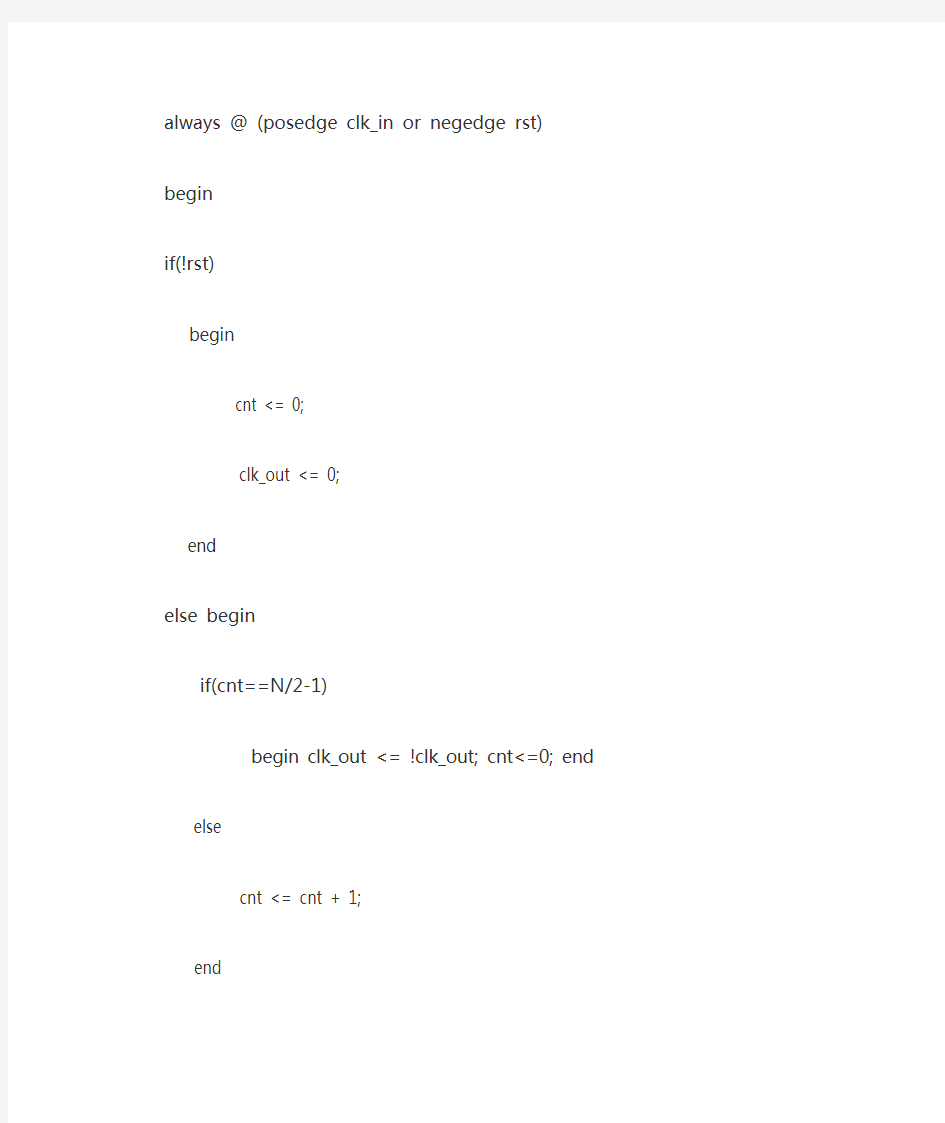

1 偶分频

偶分频比较简单,假设为N分频,只需计数到N/2-1,然后时钟翻转、计数清零,如此循环就可以得到N(偶)分频。代码如下。

module fp_even(clk_out,clk_in,rst);

output clk_out;

input clk_in;

input rst;

reg [1:0] cnt;

reg clk_out;

parameter N=6;

always @ (posedge clk_in or negedge rst)

begin

if(!rst)

begin

cnt <= 0;

clk_out <= 0;

end

else begin

if(cnt==N/2-1)

begin clk_out <= !clk_out; cnt<=0; end

else

cnt <= cnt + 1;

end

end

endmodule

可以通过改变参量N的值和计数变量cnt的位宽实现任意偶分频。

偶分频(N=6)的RTL原理图:

偶分频(N=6)的行为仿真结果:

2奇分频

实现奇数(N)分频,分别用上升沿计数到(N-1)/2,再计数到N-1;用下降沿计数到(N-1)/2,再计数到N-1,得到两个波形,然后把它们相或即可得到N分频。代码如下:

module fp_odd(clk_out,clk_p,clk_n,clk_in,rst);

output clk_out;

output clk_p,clk_n;

input clk_in,rst;

reg [2:0] cnt_p,cnt_n;

reg clk_p,clk_n;

parameter N=5;

always @ (posedge clk_in or negedge rst)

if(!rst) cnt_p <= 0;

else if(cnt_p==N-1) cnt_p <=0; else cnt_p <= cnt_p + 1; end

always @ (posedge clk_in or negedge rst) begin

if(!rst) clk_p <= 0;

else if(cnt_p==(N-1)/2)

clk_p <= !clk_p;

else if(cnt_p==N-1)

clk_p <= !clk_p;

end

always @ (negedge clk_in or negedge rst) begin

if(!rst) cnt_n <= 0;

else if(cnt_n==N-1) cnt_n <=0; else cnt_n <= cnt_n + 1; end

always @ (negedge clk_in or negedge rst) begin

if(!rst) clk_n <= 0;

else if(cnt_n==(N-1)/2)

clk_n <= !clk_n;

else if(cnt_n==N-1)

clk_n <= !clk_n;

assign clk_out = clk_p | clk_n;

endmodule

RTL Schematic:

Simulate Behavioral Model:

同理,可以通过改变参量N的值和计数变量cnt_p和cnt_n的位宽实现任意奇分频。

3任意占空比的任意分频

在verilog程序设计中,我们往往要对一个频率进行任意分频,而且占空比也有一定的要求这样的话,对于程序有一定的要求,现在在前面两个实验的基础上做一个简单的总结,实现对一个频率的任意占空比的任意分频。

比如: FPGA系统时钟是50M Hz,而我们要产生的频率是880Hz,那么,我们需要对系统时钟进行分频。很容易想到用计数的方式来分频:50000000/880 =

56818。显然这个数字不是2的整幂次方,那么我们可以设定一个参数,让它到56818的时候重新计数就可以实现了。程序如下:

module div(clk, clk_div);

input clk;

output clk_div;

reg [15:0] counter;

always @(posedge clk)

if(counter==56817) counter <= 0;

else counter <= counter+1;

assign clk_div = counter[15];

endmodule

分频的应用很广泛,一般的做法是先用高频时钟计数,然后使用计数器的某一位输出作为工作时钟进行其他的逻辑设计,上面的程序就是一个体现。

下面我们来算一下它的占空比:我们清楚地知道,这个输出波形在counter 为0到32767的时候为低,在32768到56817的时候为高,占空比为40%多一些,如果我们需要占空比为50%,那么我们需要再设定一个参数,使它为56817的一半,使达到它的时候波形翻转,就可以实现结果了。程序如下:

module div(clk, clk_div);

input clk;

output clk_div;

reg [14:0] counter;

always @(posedge clk)

if(counter==28408) counter <= 0;

else counter <= counter+1;

reg clk_div;

always @(posedge clk)

if(counter==28408) clk_div <= ~clk_div;

endmodule

继续让我们来看如何实现任意占空比,比如还是由50 M分频产生880Hz,而分频得到的信号的占空比为30%。

56818×30%=17045

module div(clk,reset,clk_div,counter); input clk,reset;

output clk_div;

output [15:0] counter;

reg [15:0] counter;

reg clk_div;

always @(posedge clk)

if(!reset) counter <= 0;

else if(counter==56817) counter <= 0;

else counter <= counter+1;

always @(posedge clk)

if(!reset) clk_div <= 0;

else if(counter<17045) clk_div <= 1;

else clk_div <= 0;

endmodule

RTL级描述:

仿真结果:

4小结

通过以上几个例子对比不难发现,借助计数器来实现任意点空比的任意分频的方法简单,且用verilog语言进行行为描述时,代码简洁、易懂、通用。通过以上的学习,对分频器有了比较深刻的认识,将在以后的学习中会有广泛的应用。

Verilog各种倍分频器设计

module odd_division(clk,rst,count,clk_odd); /*count没必要放在端口中,这里只是为了仿真时观察*/ input clk,rst; output clk_odd; output[3:0] count; reg clk_odd; reg[3:0] count; parameter N = 6; /*6分频* / always @ (posedge clk) if(! rst) begin count <= 1'b0; clk_odd <= 1'b0; end else if ( count < N/2-1) begin count <= count + 1'b1; end else begin count <= 1'b0; clk_odd <= ~clk_odd; end endmodule 奇数倍分频:归类为一般的方法为:对于实现占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数从零开始,到N-1)/2进行输出时钟翻转,然后经过(N+1)/2再次进行翻转得到一个占空比非50%奇数n分频时钟。再者同时进行下降沿触发的模N计数,到和上升沿过(N-1)/2时,输出时钟再次翻转生成占空比非50%的奇数n分频时钟。两个占空比非50%的n分频时钟相或运算,得到占空比为50%的奇数n分频时钟。 module even_division(clk,rst,count1,count2,clk_even); /*count1,count2没必要放在端口中,这

里只是为了仿真时观察*/ input clk,rst; output[3:0] count1,count2; output clk_even; reg[3:0] count1,count2; reg clkA,clkB; wire clk_even,clk_re; parameter N = 5; /*5分频*/ assign clk_re = ~clk; assign clk_even = clkA | clkB; always @(posedge clk) if(! rst) begin count1 <= 1'b0; clkA <= 1'b0; end else if(count1 < (N - 1)) begin count1 <= count1 + 1'b1; /*这里是非阻塞赋值是先执行了下面的IF判断,最后才赋的值。最初看这程序时没注意,想了好半天*/ if(count1 == (N - 1)/2) begin clkA <= ~clkA; end end else begin clkA <= ~clkA;

分频器设计实验报告

竭诚为您提供优质文档/双击可除分频器设计实验报告 篇一:n分频器分析与设计 一、实验目的 掌握74190/74191计数器的功能,设计可编程计数器和n分频器,设计(n-1/2)计数器、分频器。 二、实验原理 分频是对输入信号频率分频。1、cD4017逻辑功能 2、74190/74191逻辑功能 3、集成计数器级联 当所需计数器模数超过所选计数器最大计数状态时,需要采取多片计数器级联。方法分为异步级联和同步级联。4、集成计数器的编程 在集成计数器的时序基础上,外加逻辑门电路等,反馈集成计数器的附加功能端,达到改变计数器时序的目的。可采用复位编程和置数编程两种。5、多片74190/74191计数器级联 可根据具体计数需求和增减需求,选用74190或74191,

选择不同功能、同步或异步设计等。 6、74190/74191计数器编程 由于没有复位端,因此只能使用置数编程,置数端置为0即可异步置数。可根据需求设计n进制加法或减法计数器。 n与译码逻辑功能如下。 7、74191组成(n-1/2)分频器电路如下图: u3 计数器的两个循环中,一个循环在cp的上升沿翻转;另一个是在cp的下降沿翻转,使计数器的进制减少1/2,达到(n-1/2)分频。 三、实验仪器 1、直流稳压电源1台 2、信号发生器1台 3、数字万用表1台 4、实验箱1台 5、示波器1台 四、仿真过程 1、按照cD4017和74191功能表验证其功能。 2、74191组成可编程计数器 (1)构成8421bcD十进制加法计数器,通过实验验证正确性,列出时序表。设计图如下 仿真波形如下 (2)构成8421bcD十进制减法计数器,通过实验验证正确性,列出时序表。设计图如下: 仿真波形如下

VHDL数字系统课程设计报告-5分频器的设计

安康学院HDL数字系统课程设计报告书 课题名称:占空比为1:1的奇数分频器设计 姓名: 学号: 院系: 专业: 指导教师: 时间:

课程设计项目成绩评定表设计项目成绩评定表

课程设计报告书目录 设计报告书目录 一、设计目的 (1) 二、设计思路 (1) 三、设计过程 (1) 3.1、系统方案论证 (1) 3.2、程序代码设计 (2) 四、系统调试与结果 (4) 五、主要元器件与设备 (5) 六、课程设计体会与建议 (5) 6.1、设计体会 (5) 6.2、设计建议 (6) 七、参考文献 (6)

一、设计目的 1、了解EDA软件在电子设计当中的重要作用。 2、熟悉并掌握QuartusⅡ开发软件的基本使用方法。 3、运用ModelSim软件对分频器进行仿真测试。 二、设计思路 对于实现一个占空比为1:1的5倍奇数分频,首先经过上升沿触发进行模5计数,计数选定到2进行输出时钟翻转,然后经过4再次进行翻转得到一个占空非1:1奇数5分频时钟。再者同时进行下降沿触发的模5计数,到和上升沿触发输出时钟翻转选定值相同值时,进行输出时钟翻转,同样经过4时,输出时钟再次翻转得到占空比非1:1的5分频时钟。两个占空比非1:1的5分频时钟进行相或运算,得到占空比为1:1的5分频时钟。 要设计占空比为50%的奇数(n)倍分频器,可以先分别设计从时钟上升沿、下降沿开始的占空比为(n-1)/2n的分频器A,B。将A与B相或结果就是占空比为50%的奇数倍分频器。因为A,B产生的信号的高电平持续时间均比低电平持续时间少一个时钟周期,B相对A来说可以说是延时了半个时钟,那么A与B进行或运算,则结果的高电平持续时间增加了半个时钟周期,而低电平持续时间则减少了半个时钟周期。因此占空比达到50%。 三、设计过程 3.1系统方案论证 奇数倍(2N+1)分频: (1)使用模为2N+1的计数器,让输出时钟在X-1(X在0到2N-1之间)和2N时各翻转一次,则可得到奇数分频器,但是占空比并不是50%(应为 X/(2N+1))。得到占空比为50%的奇数分频器的基本思想是:将得到的上升沿触发计数的奇数分频输出信号CLK1,和得到的下降沿触发计数的相同(时钟翻转值相同)奇数分频输出信号CLK2,进行相或运算。如图1所示. 图 2

用Verilog语言实现任意整数分频器

用Verilog语言实现任意整数分频器 分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相环资源,如赛灵思(Xilinx)的DLL.来进行时钟的分频,倍频以及相移。但是对于时钟要求不高的基本设计,通过语言进行时钟的分频相移仍然非常流行,首先这种方法可以节省芯片内部的锁相环资源,再者,消耗不多的逻辑单元就可以达到对时钟操作的目的。另一方面,通过语言设计进行时钟分频,可以看出设计者对设计语言的理解程度。因此很多招聘单位在招聘时往往要求应聘者写一个分频器(比如奇数分频)以考核应聘人员的设计水平和理解程度。下面讲讲对各种分频系数进行分频的方法:第一,偶数倍分频:偶数倍分频应该是大家都比较熟悉的分频,通过计数器计数是完全可以实现的。如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。以此循环下去。这种方法可以实现任意的偶数分频。电路上只需一个D触发器和一个非门即可实现,Q(n+1)=D,D=~Q(n),clk_out=Q(n+1) . 第二,奇数倍分频:奇数倍分频常常在论坛上有人问起,实际上,奇数倍分频有两种实现方法: 占空比为非50%的三分频时钟,完全可以通过计数器来实现,如进行三分频,通过待分频时钟上升沿触发计数器进行模三计数,当计数器计数到邻近值进行两次翻转,比如可以在计数器计数到1时,输出时钟进行翻转,计数到2时再次进行翻转。即是在计数值在邻近的1和2进行了两次翻转。这样实现的三分频占空比为1/3或者2/3。 module three(clk_in,rst,clk_out); // 三倍频 inputclk_in,rst; output clk_out; reg clk_out; reg [1:0] count; always @(negedgerst or posedgeclk_in) begin if(rst==0) begin count<=0; clk_out<=0; end else begin count<=count+1; if(count==1) clk_out<=~clk_out; else if(count==2) begin clk_out=~clk_out; count<=0; end end end endmodule 仿真图 另一种实现: module div3(CLKIN,CLKOUT,RESETn); //依然是三倍频 inputCLKIN,RESETn;

分频器的设计2014-1-10 10.29.8

武汉理工大学《微机原理与接口技术》课程设计报告书

学

号:

0121105830129

课 程 设 计

题 学 专 班 姓

目 院 业 级 名

分频信号发生器的分析与设计 自动化学院 电气工程及自动化 电气 1107 班 成涛 陈静 教授

指导教师

2014 年

01 月

09 日

武汉理工大学《微机原理与接口技术》课程设计报告书

课程设计任务书

学生姓名: 指导教师: 题 目: 成涛 专业班级: 电气 1107 班 陈静 教授 工作单位: 自动化学院 分频信号发生器的分析与设计

要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰 写等具体要求) 1. 设:有一输入方波信号 f0(<1MHz) 。要求输出信号:f1=f0/N,N 通过键盘 输入。 2. 画出简要的硬件原理图,编写程序。 3. 撰写课程设计说明书。 内容包括:摘要、 目录、 正文、 参考文献、 附录 (程 序清单) 。正文部分包括:设计任务及要求、方案比较及论证、软件设计说明(软 件思想,流程,源程序设计及说明等) 、程序调试说明和结果分析、课程设计收 获及心得体会。

时间安排: 12 月 26 日----- 12 月 28 日 查阅资料及方案设计 12 月 29 日----- 01 月 0 2 日 编程 01 月 03 日-----0 1 月 07 日 调试程序 01 月 08 日----- 01 月 09 日 撰写课程设计报告

指导教师签名: 系主任(或责任教师)签名:

年 年

月 月

日 日

数电课程设计报告数字钟的设计

数电课程设计报告数字钟的设计

数电课程设计报告 第一章设计背景与要求 设计要求 第二章系统概述 2.1设计思想与方案选择 2.2各功能块的组成 2.3工作原理 第三章单元电路设计与分析 3.1各单元电路的选择 3.2设计及工作原理分析 第四章电路的组构与调试 4.1遇到的主要问题 4.2现象记录及原因分析 4.3解决措施及效果 4.4功能的测试方法,步骤,记录的数据 第五章结束语 5.1对设计题目的结论性意见及进一步改进的意向说明5.2总结设计的收获与体会 附图(电路总图及各个模块详图) 参考文献

第一章设计背景与要求 一.设计背景与要求 在公共场所,例如车站、码头,准确的时间显得特别重要,否则很有可能给外出办事即旅行袋来麻烦。数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确度和直观性,且无机械装置,具有更长的使用寿命,因此得到了广泛的使用。数字钟是一种典型的数字电路,包括了组合逻辑电路和时序电路。 设计一个简易数字钟,具有整点报时和校时功能。 (1)以四位LED数码管显示时、分,时为二十四进制。 (2)时、分显示数字之间以小数点间隔,小数点以1Hz频率、50%占空比的亮、灭规律表示秒计时。 (3)整点报时采用蜂鸣器实现。每当整点前控制蜂鸣器以低频鸣响4次,响1s、停1s,直到整点前一秒以高频响1s,整点时结束。 (4)才用两个按键分别控制“校时”或“校分”。按下校时键时,是显示值以0~23循环变化;按下“校分”键时,分显示值以0~59循环变化,但时显示值不能变化。 二.设计要求 电子技术是一门实践性很强的课程,加强工程训练,特别是技能的培养,对于培养学生的素质和能力具有十分重要的作用。在电子信息类本科教学中,课程设计是一个重要的实践环节,它包括选

实验六--Verilog设计分频器计数器电路答案

实验六 Verilog设计分频器/计数器电路 一、实验目的 1、进一步掌握最基本时序电路的实现方法; 2、学习分频器/计数器时序电路程序的编写方法; 3、进一步学习同步和异步时序电路程序的编写方法。 二、实验内容 1、用Verilog设计一个10分频的分频器,要求输入为clock(上升沿有效),reset(低电平复位),输出clockout为4个clock周期的低电平,4个clock周期的高电平),文件命名为fenpinqi10.v。 2、用Verilog设计一异步清零的十进制加法计数器,要求输入为时钟端CLK(上升沿)和异步清除端CLR(高电平复位),输出为进位端C和4位计数输出端Q,文件命名为couter10.v。 3、用Verilog设计8位同步二进制加减法计数器,输入为时钟端CLK(上升沿有效)和异步清除端CLR(低电平有效),加减控制端UPDOWN,当UPDOWN为1时执行加法计数,为0时执行减法计数;输出为进位端C和8位计数输出端Q,文件命名为couter8.v。 4、用VERILOG设计一可变模数计数器,设计要求:令输入信号M1和M0控制计数模,当M1M0=00时为模18加法计数器;M1M0=01时为模4加法计数器;当M1M0=10时为模12加法计数器;M1M0=11时为模6加法计数器,输入clk上升沿有效,文件命名为mcout5.v。 5、VerilogHDL设计有时钟时能的两位十进制计数器,有时钟使能的两位十进制计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;ENA是时钟使能控制输入端,高电平有效,当ENA=1时,时钟CLK才能输入;CLR是复位输入端,高电平有效,异步清零;Q[3..0]是计数器低4位状态输出端,Q[7..0]是高4位状态输出端;COUT是进位输出端。 三、实验步骤 实验一:分频器 1、建立工程

实验一 QUARTUS II入门和分频器设计

实验报告 课程名称EDA技术与VHDL设计 实验项目Quartus II入门 实验仪器计算机、Quartus II 系别信息与通信工程学院 专业电子信息工程 班级/学号电信1201 / 2012010970 学生姓名张宗男 实验日期 成绩 指导教师

实验一 QUARTUS II入门和分频器设计 一、实验目的 1.掌握QUARTUS II工具的基本使用方法; 2.掌握FPGA基本开发流程和DE2开发板的使用方法; 3.学习分频器设计方法。 二、实验内容 1.运用QUARTUS II 开发工具编写简单LED和数码管控制电路并下载到DE2 实验开发板。2.在QUARTUS II 软件中用VHDL语言实现十分频的元器件编译,并用电路进行验证,画出仿真波形。 三、实验环境 1.软件工具:QUARTUS II 软件;开发语言:VHDL; 2.硬件平台:DE2实验开发板。 四、实验过程 1.设计思路 (1)、 18个开关控制18个LED灯,通过低位四个开关的‘1’‘0’控制LED灯上7段灯的显示(2)、 实现10分频IF(count="1001") THEN count<="0000"; clk_temp<=NOT clk_temp; 达到9的时候,把“0000”给到cout,然后clk_temp 信号翻转,从而实现10分频。 2.VHDL源程序 (1)、 LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY e_zhangzongnan IS PORT(SW :IN STD_LOGIC_VECTOR(0 TO 17); HEX0 :OUT STD_LOGIC_VECTOR(0 TO 6);

VHDL非整数分频器设计实验报告

非整数分频器设计 一、 输入文件 输入时钟CLK: IN STD_LOGIC 二、 设计思路 1. 方法一:分频比交错 (1) 确定K 值 先根据学号S N 确定M 和N :为了保证同学们的学号都不相同,取学号的后四位,即N S =1763 ()mod 1920(mod 17)0 17mod 17 S S S N N if N then M else M N =+=== 由以上公式,得N=(1763 mod 19)+20=35 M=(1763 mod 17)=12 然后根据下式计算分频比K 的值: 8()9N M M K N -+= = =8.34285714 (2) 确定交错规律 使在35分频的一个循环内,进行12次9分频和23次8分频,这样,输出F_OUT 平均为F_IN 的8.34285714分频。为使分频输出信号的占空比尽可能均匀,8分频和9分频应‘交替’进 (3) 设计框图:要求同步时序设计

(4)代码 在实体内定义两个进程(PROCESS P1和PROCESS P2),一个进程控制输出8/9分频,一个进程控制35分频周期比例输出。控制器输出FS_CTL信号控制输出是8分频还是9分频,分频器输出C_ENB信号来控制35分频计数器计数。 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; ENTITY DIV IS--定义实体,实体名DIV PORT(F_IN: IN STD_LOGIC;--输入时钟信号 F_OUT: OUT STD_LOGIC--输出时钟信号 ); END DIV; ARCHITECTURE A OF DIV IS SIGNAL CN1: INTEGER RANGE 0 TO 7;--8分频计数器 SIGNAL CN2: INTEGER RANGE 0 TO 8;--9分频计数器 SIGNAL CN: INTEGER RANGE 0 TO 34;--整体计数器 SIGNAL C_ENB: STD_LOGIC;--整体计数器时钟驱动信号 SIGNAL FS_CTL: STD_LOGIC;--控制8、9分频比例信号,高电平8分频,低电平9分频 BEGIN P1:PROCESS(F_IN)--8、9分频计数进程 BEGIN IF (F_IN'EVENT AND F_IN='1') THEN IF(FS_CTL='0') THEN--9分频 IF CN2=8 THEN--计数 CN2<=0; ELSE CN2<=CN2+1; END IF; IF CN2>4 THEN--控制输出,占空比0.5 F_OUT<='1'; ELSE F_OUT<='0'; END IF; IF CN2=8 THEN--控制整体计数器驱动信号 C_ENB<='1'; ELSE C_ENB<='0'; END IF; ELSE IF CN1=7 THEN--8分频计数,同上 CN1<=0; ELSE CN1<=CN1+1; END IF; IF CN1>3 THEN F_OUT<='1'; ELSE F_OUT<='0'; END IF; IF CN1=7 THEN C_ENB<='1'; ELSE C_ENB<='0'; END IF; END IF; END IF; END PROCESS P1; P2:PROCESS(C_ENB)--整体计数进程 BEGIN IF (C_ENB'EVENT AND C_ENB='1') THEN--由驱动信号驱动 IF CN=34 THEN--计数 CN<=0; ELSE CN<=CN+1; END IF; IF (CN=34 OR CN=2 OR CN=5 OR CN=8 OR CN=11 OR CN=14 OR CN=17 OR CN=20 OR CN=23 OR CN=26 OR CN=29 OR CN=32) THEN FS_CTL<='0'; ELSE FS_CTL<='1'; END IF;--8、9分频比例分配 ELSE CN<=CN; END IF; END PROCESS P2; END A;

verilogHDL分频器(奇数分频和偶数分频)

module clk_div( //-----------input----------- iCLK, div, //-----------output---------- oCLK ); //-----------input----------- parameter WIDE=14; input iCLK; input[WIDE-1:0]div; //-----------output----------- output oCLK; wire oCLK_odd; wire oCLK_even; assign oCLK=div[0]?oCLK_odd:oCLK_even; div_odd DUTo (.iCLK(iCLK),.oCLK(oCLK_odd),.div(div)); div_even DUTe (.iCLK(iCLK),.oCLK(oCLK_even),.div(div)); endmodule // odd module div_odd( //--------input-------- iCLK, div, //--------output-------- oCLK ); //--------input-------- parameter WIDE=14; input iCLK; input[WIDE-1:0]div; //--------output-------- output oCLK; reg outCLK;

/* =========================== solve 1 =========================== reg cout; reg[WIDE-1:0] cnt; initial cnt=0; wire inCLK; reg cc; initial cc=0; always @(posedge cout) cc<=~cc; assign inCLK = iCLK^cc; always @(posedge inCLK) begin if(cnt<(div[WIDE-1:1])) begin cnt<=cnt+1; cout<=1'b0; end else begin cnt<=0; cout<=1'b1; end end always @(negedge iCLK) outCLK <= cout; assign oCLK=cc; */ //======================== //solve 2 //======================== reg[WIDE-1:0] cnt_a; initial cnt_a=0; reg[WIDE-1:0] cnt_b; initial cnt_b=0; reg cout_a;

3分频器的设计

三分频器的设计 时钟输入端(clkin)首先反向和不反向分别接到两个D触发器的时钟输入端,两个D触发器的输出接到一个二输入或非门的输入端,或非门的输出反馈到前面两个D触发器的D输入端,并且或非门的输出后面接一二分频器,得到占空比为50%的三分频波形。 图1:图形设计 VHDL程序: library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; entity fen3 is port (clkin : in std_logic; --时钟输入 qout1 : buffer std_logic; qout2 : buffer std_logic; qout3 : buffer std_logic; clkout : out std_logic --占空比为1/2的三分频输出 ); end fen3; architecture behave of fen3 is begin qout3<=qout1 nor qout2; process(clkin) begin if clkin'event and clkin='1' then --在上升沿触发 qout1<=qout3; end if;

end process; process(clkin) begin if clkin'event and clkin='0' then --在下降沿触发 qout2<=qout3; end if; end process; process(qout3) variable tem:std_logic; begin if qout3'event and qout3='1' then --二分频tem:=not tem; end if; clkout<=tem; end process; end behave; 图3:仿真结果

EDA 实验2简单分频时序逻辑电路设计 实验报告

时序电路设计 实验目的: 1.掌握条件语句在简单时序模块设计中的使用。 2.学习在Verilog模块中应用计数器。 实验环境: Windows 7、MAX+PlusⅡ10等。 实验内容: 1.模为60的8421BCD码加法计数器的文本设计及仿真。 2.BCD码—七段数码管显示译码器的文本设计及仿真。 3.用For语句设计和仿真七人投票表决器。 4.1/20分频器的文本设计及仿真。 实验过程: 一、模为60的8421BCD码加法计数器的文本设计及仿真: (1)新建文本:选择菜单File下的New,出现如图5.1所示的对话框,在框中选中“Text Editor file”,按“OK”按钮,即选中了文本编辑方式。 图5.1 新建文本 (2)另存为V erilog编辑文件,命名为“count60.v”如图5.2所示。 (3)在编辑窗口中输入程序,如图5.3所示。

图5.2 另存为.V编辑文件图5.4 设置当前仿真的文本设计 图5.3 模为60的8421BCD码加法计数器的设计代码

(4)设置当前文本:在MAX+PLUS II中,在编译一个项目前,必须确定一个设计文件作为当前项目。按下列步骤确定项目名:在File菜单中选择Project 中的Name选项,将出现Project Name 对话框:在Files 框内,选择当前的设计文件。选择“OK”。如图5.4所示。 (5)打开编译器窗口:在MAX—plusⅡ菜单内选择Compiler 项,即出现如图5.5的编译器窗口。 图5.5 编译器窗口 选择Start即可开始编译,MAX+PLUS II编译器将检查项目是否有错,并对项目进行逻辑综合,然后配置到一个Altera 器件中,同时将产生报告文件、编程文件和用于时间仿真用的输出文件。 (6)建立波形编辑文件:选择菜单File下的New选项,在出现的New对话框中选择“Waveform Editor File”,单击OK后将出现波形编辑器子窗口。 (7)仿真节点插入:选择菜单Node下的Enter Nodes from SNF选项,出现如图5.6所示的选择信号结点对话框。按右上侧的“List”按钮,在左边的列表框选择需要的信号结点,然后按中间的“=>”按钮,单击“OK”,选中的信号将出现在波形编辑器中。 图5.6 仿真节点插入

分频器的verilog hdl语言

分频器的verilog HDL描述(转) 分频器,在许多涉及时序的电路设计中都会用到,在这里,我转载某位高人的文章,关于分频器的设计 偶数倍分频:偶数倍分频应该是大家都比较熟悉的分频,通过计数器计数是完全可以实现的。如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。以此循环下去。这种方法可以实现任意的偶数分频。 module odd_division(clk,rst,count,clk_odd); input clk,rst; output clk_odd; output[3:0] count; reg clk_odd; reg[3:0] count; parameter N = 6; always @ (posedge clk) if(! rst) begin count <= 1'b0; clk_odd <= 1'b0; end else if ( count < N/2-1) begin count <= count + 1'b1; end else begin

clk_odd <= ~clk_odd; end endmodule 奇数倍分频:归类为一般的方法为:对于实现占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数从零开始,到(N-1)/2进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%奇数n分频时钟。再者同时进行下降沿触发的模N 计数,到和上升沿过(N-1)/2时,输出时钟再次翻转生成占空比非50%的奇数n分频时钟。两个占空比非50%的n分频时钟相或运算,得到占空比为50%的奇数n分频时钟。 module even_division(clk,rst,count1,count2,clk_even); input clk,rst; output[3:0] count1,count2; output clk_even; reg[3:0] count1,count2; reg clkA,clkB; wire clk_even; parameter N = 5; assign clk_re = ~clk; assign clk_even = clkA | clkB; always @(posedge clk) if(! rst) begin count1 <= 1'b0; clkA <= 1'b0; end else

分频器的设计

首先讲一下单元: 一般情况下,我们对单元按频率会划分为超高音,高音,中高音,中音,重低音,低音,超低音 超高音:負責22kHz以上的頻率 高音:負責5000Hz~22kHz頻率、 中音:負責1500~5000Hz頻率 低音:負責1500Hz以下頻率 超低音(增加)負責200Hz以下頻率 也有网友提出其她的划分标准 以A音(C调的“哆来咪法嗦啦西”的“啦”音,频率为440赫兹)为基准音,以倍频的形式向下三个八度向上五个八度,把全音域分为八个八度,一个个八度就就是音响上常说的一个倍频程(1oct)。具体的划分就是这样的: 55-110赫兹,110-220赫兹,220-440赫兹,440-880赫兹,880-1760赫兹,1760-3520赫兹,3520-7040赫兹,7040-14080赫兹,共八段(八个八度)。这样就很清晰的瞧出频段的划分了。110赫兹以下-超低频; 110-220赫兹-低频; 220-440赫兹-中低频; 440-880赫兹-低中频; 880-1760赫兹-中频; 1760-3520赫兹-中高频; 3520-7040赫兹-高频; 7040赫兹以上-超高频。 还有两种频段划分方法 以“E”音划分 -20 次低频 20-40 极低频 40-80 低频下段 80-160 低频上段 160-320 中频下段 320-640 中频中段

640-1280 中频上段 1280-2560 高频下段 2560-5120 高频中段 5120-10240 高频上段 10240- 极高频 以“C”划分 -63 极低频 63-125 低频下段 125-250 低频上段 250-500 中频下段 500-1K 中频中段 1K-2K 中频上段 2K-4K 高频下段 4K-8K 高频上段 8K- 极高频 分频器的主要元件:电阻,电感,电容 电阻在分频器中的作用:调整灵敏度 电感:其特性就是阻挡较高频率,只让较低的频率通过电容:其特性与电感刚好相反,也就就是阻挡频率通过

EDA数控分频器的设计报告

数控分频器的设计 1、实验目的: 学习数控分频器的设计、分析和测试方法。 2、实验原理: 数控分频器的功能就是当在输入端给定不同输入数据时,将对输入的时钟信号有不同的分频比,数控分频器就是用计数值可并行预置的加法计数器设计完成的,方法是将计数溢出位与预置数加载输入信号相接即可,详细设计程序如例下文所示。 1) VHDL及语句分析 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY DVF IS --定义实体DVF PORT ( CLK : IN STD_LOGIC; --时钟输入 D : IN STD_LOGIC_VECTOR(7 DOWNTO 0); --7位预置数 FOUT : OUT STD_LOGIC ); --输出的频率 END DVF; ARCHITECTURE one OF DVF IS --定义结构体one SIGNAL FULL : STD_LOGIC; --定义信号full BEGIN P_REG: PROCESS(CLK) --进程P_REG中CNT8从预置数D开始 逐步累加到255后,FULL置1;再将 CNT8置为D,循环以获得一个新的周期 脉冲序列FULL,即产生新的频率V ARIABLE CNT8 : STD_LOGIC_VECTOR(7 DOWNTO 0); BEGIN IF CLK'EVENT AND CLK = '1' THEN IF CNT8 = "11111111" THEN CNT8 := D; FULL<='1'; ELSE CNT8 := CNT8 + 1; FULL <= '0'; END IF; END IF; END PROCESS P_REG ; P_DIV: PROCESS(FULL) --进程P_DIV中,FOUT是占空比为50%的周期

任意分频Verilog实现

1. 偶数倍(2N)分频 使用一模N计数器模块即可实现,即每当模N计数器上升沿从0开始计数至N-1时,输出时钟进行翻转, 同时给计数器一复位信号使之从0开始重新计数,以此循环即可。偶数倍分频原理示意图见图1。 2. 奇数倍(2N+1)分频 (1)占空比为X/(2N+1)或(2N+1-X)/(2N+1)分频,用模(2N+1)计数器模块可以实现。取0至2N-1之间一数值X(0,当计数器时钟上升沿从0开始计数到X值时输出时钟翻转一次,在计数器继续计数达到2N 时,输出时钟再次翻转并对计数器置一复位信号,使之从0开始重新计数,即可实现。 (2)占空比为50%的分频,设计思想如下:基于(1)中占空比为非50%的输出时钟在输入时钟的上升沿 触发翻转;若在同一个输入时钟周期内,此计数器的两次输出时钟翻转分别在与(1)中对应的下降沿触发翻转,输出的时钟与(1)中输出的时钟进行逻辑或,即可得到占空比为50%的奇数倍分频时钟。当然其 输出端再与偶数倍分频器串接则可以实现偶数倍分频。奇数倍分频原理示意图见图2。(这也是许多公司常出的面试题,^_^,是不是很简单?) 3. N-0.5倍分频 采用模N计数器可以实现。具体如下:计数器从0开始上升沿计数,计数达到N-1上升沿时,输出时钟需翻转,由于分频值为N-0.5,所以在时钟翻转后经历0.5个周期时,计数器输出时钟必须进行再次翻转,即当 CLK为下降沿时计数器的输入端应为上升沿脉冲,使计数器计数达到N而复位为0重新开始计数同时输出时钟翻转。这个过程所要做的就是对CLK进行适当的变换,使之送给计数器的触发时钟每经历N-0.5个周期就翻转一次。N-0.5倍:取N=3,分频原理示意图见图3。 对于任意的N+A/B倍分频(N、A、B∈Z,A≦B) 分别设计一个分频值为N和分频值N+1的整数分频器,采用脉冲计数来控制单位时间内两个分频器出现 的次数,从而获得所需要的小数分频值。可以采取如下方法来计算个子出现的频率: 设N出现的频率为a,则N×a+(N+1)×(B-a)=N×B+A 求解a=B-A; 所以N+1出现的频率为 A.例如实现7+2/5分频,取a为3,即7×3+8×2就可以实现。但是由于这种小数分频输出的时钟脉冲抖动很大, 现实中很少使用。 通常实现偶数的分频比较容易,以十分频为例: always @( posedge clk or posedge reset) if(reset) begin k<=0; clk_10<=0; end else if(k==4) begin k<=0;

分频器的设计

分频器的设计 一、课程设计目的 1.学会使用电路设计与仿真软件工具Hspice,熟练地用网表文件来描述模拟电路,并熟悉应用Hspice内部元件库。通过该实验,掌握Hspice的设计方法,加深对课程知识的感性认识,增强电路设计与综合分析能力。 2.分频器大多选用市售成品,但市场上出售的分频器良莠不齐,质量上乘者多在百元以上,非普通用户所能接受。价格在几十元以下的分频器质量难以保证,实际使用表现平庸。自制分频器可以较少的投入换取较大的收获。 二.内容 分频器-概述 分频器是指使输出信号频率为输入信号频率整数分之一的电子电路。在许多电子设备中如电子钟、频率合成器等,需要各种不同频率的信号协同工作,常用的方法是以稳定度高的晶体振荡器为主振源,通过变换得到所需要的各种频率成分,分频器是一种主要变换手段。早期的分频器多为正弦分频器,随着数字集成电路的发展,脉冲分频器(又称数字分频器)逐渐取代了正弦分频器,即使在输入输出信号均为正弦波时也往往采用模数转换-数字分频-数模转换的方法来实现分频。正弦分频器除在输入信噪比低和频率极高的场合已很少使用。

分频器-作用 分频器是音箱中的“大脑”,对音质的好坏至关重要。功放输出的音乐讯号必须经过分频器中的各滤波元件处理,让各单元特定频率的讯号通过。要科学、合理、严谨地设计好音箱之分频器,才能有效地修饰喇叭单元的不同特性,优化组合,使得各单元扬长避短,淋漓尽致地发挥出各自应有的潜能,使各频段的频响变得平滑、声像相位准确,才能使高、中、低音播放出来的音乐层次分明、合拍,明朗、舒适、宽广、自然的音质效果。 在一个扬声器系统里,人们把箱体、分频电路、扬声器单元称为扬声器系统的三大件,而分频电路对扬声器系统能否高质量地还原电声信号起着极其重要的作用。尤其在中、高频部分,分频电路所起到的作用就更为明显。其作用如下: 合理地分割各单元的工作频段; 合理地进行各单元功率分配; 使各单元之间具有恰当的相位关系以减少各单元在工作中出现的声干涉失真; 利用分频电路的特性以弥补单元在某频段里的声缺陷; 将各频段圆滑平顺地对接起来。 分频器-分类 1)功率分频器:位于功率放大器之后,设置在音箱内,通过LC滤波网络,将功率放大器输出的功率音频信号分为低音,中音和高音,分别送至各自扬声器。连接简单,使用方便,但消耗功率,出现音频谷

实验六Verilog设计分频器计数器电路答案

实验六V e r i l o g设计分频器/计数器电路 一、实验目的 1、进一步掌握最基本时序电路的实现方法; 2、学习分频器/计数器时序电路程序的编写方法; 3、进一步学习同步和异步时序电路程序的编写方法。 二、实验内容 1、用Verilog设计一个10分频的分频器,要求输入为clock(上升沿有效),reset(低电平复位),输出clockout为4个clock周期的低电平,4个clock 周期的高电平),文件命名为。 2、用Verilog设计一异步清零的十进制加法计数器,要求输入为时钟端CLK (上升沿)和异步清除端CLR(高电平复位),输出为进位端C和4位计数输出端Q,文件命名为。 3、用Verilog设计8位同步二进制加减法计数器,输入为时钟端CLK(上升沿有效)和异步清除端CLR(低电平有效),加减控制端UPDOWN,当UPDOWN 为1时执行加法计数,为0时执行减法计数;输出为进位端C和8位计数输出端Q,文件命名为。 4、用VERILOG设计一可变模数计数器,设计要求:令输入信号M1和M0控制计数模,当M1M0=00时为模18加法计数器;M1M0=01时为模4加法计数器;当M1M0=10时为模12加法计数器;M1M0=11时为模6加法计数器,输入clk 上升沿有效,文件命名为。 5、VerilogHDL设计有时钟时能的两位十进制计数器,有时钟使能的两位十进制计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;ENA是

时钟使能控制输入端,高电平有效,当ENA=1时,时钟CLK才能输入;CLR 是复位输入端,高电平有效,异步清零;Q[3..0]是计数器低4位状态输出端,Q[7..0]是高4位状态输出端;COUT是进位输出端。 三、实验步骤 实验一:分频器 1、建立工程 2、创建Verilog HDL文件 3、输入10分频器程序代码并保存 4、进行综合编译 5、新建波形文件 6、导入引脚 7、设置信号源并保存 8、生成网表 9、功能仿真 10、仿真结果分析 由仿真结果可以看出clockout输出5个clock周期的低电平和5个clock 的高电平达到10分频的效果,设计正确。 实验二:十进制加法计数器(异步清零) 1、建立工程 2、创建Verilog HDL文件 3、输入加法计数器代码并保存 4、进行综合编译 5、新建波形文件 6、导入引脚 7、设置信号源并保存 8、生成网表 9、功能仿真 10、仿真结果分析

Verilog分频器设计

Verilog分频器设计 module adder(clk,z); output z; reg q; reg z; always@(posedge clk) begin if(q%9==0) z<=q; else q=q+1; end endmodule module counter9(clk,datein,z); output z; input clk; input datein; reg z; reg[3:0] q; always@(posedge clk) begin q<=q+1; if (q==4'b1001) begin q<=4'b0000; z<=datein; end end endmodule

2008-11-04 19:58 分频器是FPGA设计中使用频率非常高的基本单元之一。尽管目前在大部分设计中还广泛使用集成锁相环(如altera的PLL,Xilinx的DLL)来进行时钟的分频、倍频以及相移设计,但是,对于时钟要求不太严格的设计,通过自主设计进行时钟分频的实现方法仍然非常流行。首先这种方法可以节省锁相环资源,再者,这种方式只消耗不多的逻辑单元就可以达到对时钟操作的目的。偶数倍分频:偶数倍分频应该是大家都比较熟悉的分频,通过计数器计数是完全可以实现的。如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。以此循环下去。这种方法可以实现任意的偶数分频。 module odd_division(clk,rst,count,clk_odd); /*count没必要放在端口中,这里只是为了仿真时观察*/ input clk,rst; output clk_odd; output[3:0] count; reg clk_odd; reg[3:0] count; parameter N = 6; /*6分频* / always @ (posedge clk) if(! rst) begin count <= 1'b0; clk_odd <= 1'b0; end else if ( count < N/2-1) begin count <= count + 1'b1; end else begin count <= 1'b0; clk_odd <= ~clk_odd;