Xilinx ISE 13 笔记04 引脚约束的实现

第四引脚约束和时序约束的实现

引脚约束:将顶层设计的逻辑端口和FPGA的物理引脚进行映射,步骤如下:

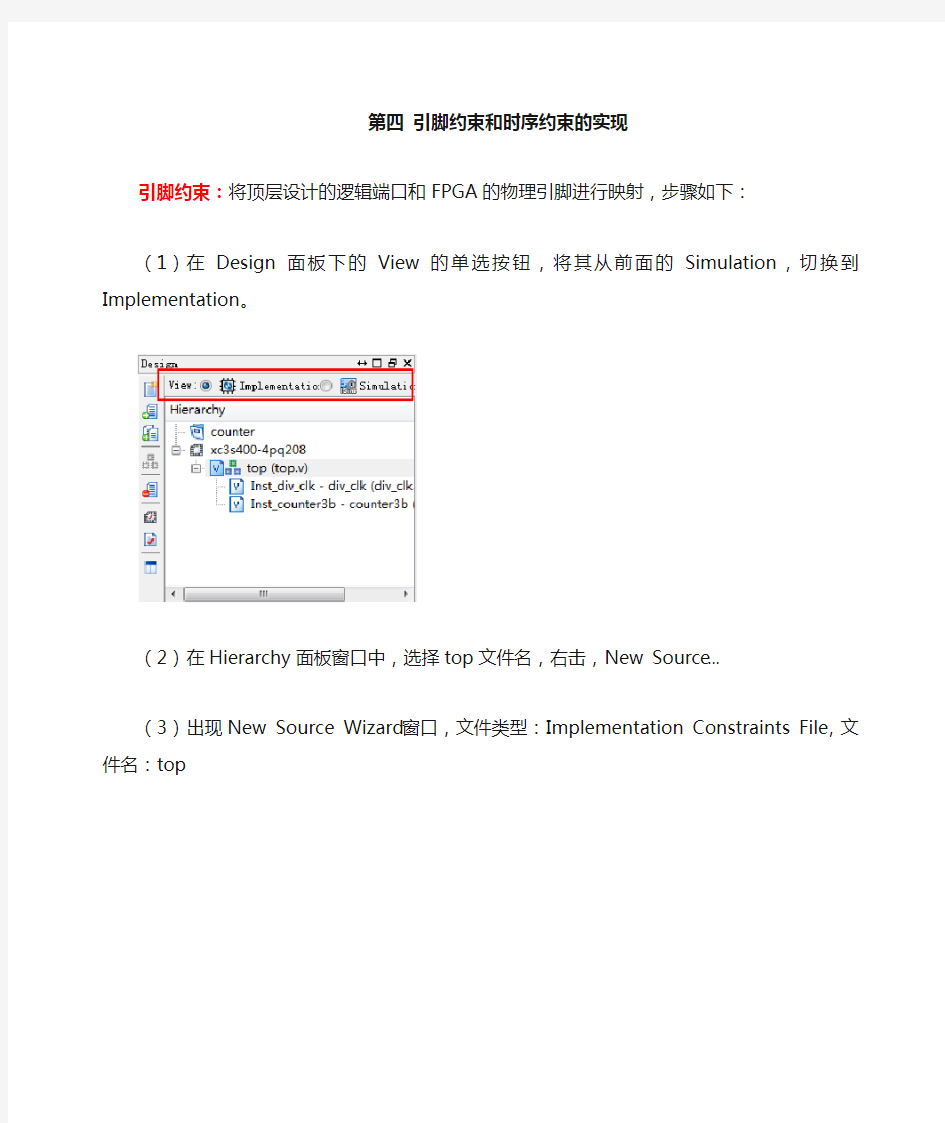

(1)在Design面板下的View的单选按钮,将其从前面的Simulation,切换到Implementation。

(2)在Hierarchy面板窗口中,选择top文件名,右击,New Source…

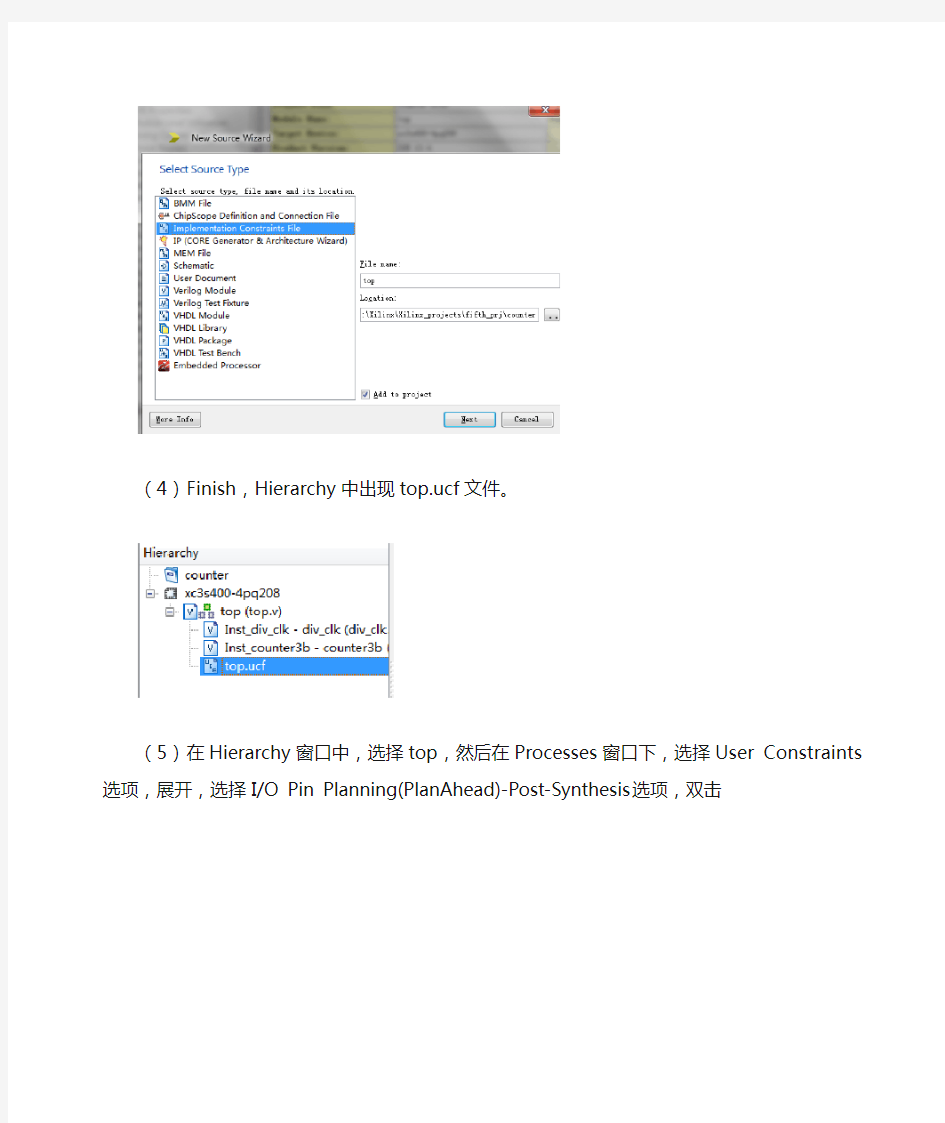

(3)出现New Source Wizard窗口,文件类型:Implementation Constraints File,文件名:top

(4)Finish,Hierarchy中出现top.ucf文件。

(5)在Hierarchy窗口中,选择top,然后在Processes窗口下,选择User Constraints 选项,展开,选择I/O Pin Planning(PlanAhead)-Post-Synthesis选项,双击

(6)出现ISE Project Navigator对话框,由于已经生成.ucf文件,选择Yes

(7)出现对话框,单击OK。

(8)出现PlanAhead工具主界面(第一次等很久…),Close。

下面准备在PlanAhead软件中实现I/O引脚位置的约束,查板子原理图和引脚约束文件。步骤如下:

(1)对应每个信号行,在Site栏下,分别输入FPGA引脚的名字,然后在I/O Std 栏下,输入LVCOMS33,作为设计中所有I/O引脚的标准。

注意:也可以采用下面的方法,约束I/O引脚的位置。如下图,在I/O Ports窗口中选中需要约束的端口,然后用鼠标将其拖拽到Package窗口所显示器件的相应的封装的位置,如此重复,知道为顶层设计的每个端口都分配了FPGA的引脚位置。然后为每个引脚分配I/O Std为LVCMOS33。

当在FPGA映射了相应的位置后,在工具栏选择放大按钮,可以在所分配FPGA 引脚内看到“-||-”符号。

(2)保存,退出PlanAhead工具界面

(3)在Hierarchy窗口中,选择top.ucf文件,然后在Processes窗口中,选择User Constraints,展开,双击Edit Constraints(Text)选项。

时序约束的实现:

这部分内容是可选的,在不是高性能的或者对时序要求很苛刻的地方,不需要进行时序约束的实现。

下面是实现时序约束的步骤:

(1)在Hierarchy窗口选择top模块,然后在Processes面板窗口下,选择User Constraints,展开,双击Create Timing Constraints选项。打开时序约束编辑器界面。

(2)在主界面的Constraint Type 窗口下,选择并展开Timing Constraints,用鼠标单击击Clock Domains选项。

(3)在Unconstrained Clocks窗口中,选择clk,并用鼠标双击该选项。

(4)在Time中输入10ns

(5)选择并展开Timing Constraints,选择outputs。出现如下图

选中counter<0>到counter<2>,右击,选择Create Time Group.

(6)出现下图所示界面,在Time group name的右边输入counter_group作为组的名字,单击OK

(7)当出现对话框时,选择Yes,创建OFFSET。

(8)出现Create Clock to Pad界面,接受默认设置,选择Create按钮。

保存设置,并关闭时序约束器界面

(9)按照前面的步骤,用文本编辑器打开top.ucf文件,在ucf文件中,添加了时序约束。

常用芯片引脚图

.v .. .. 常用芯片引脚 74LS00数据手册 74LS01数据手册 74LS02数据手册 74LS03数据手册 74LS04数据手册 74LS05数据手册 74LS06数据手册 74LS07数据手册 74LS08数据手册 74LS09数据手册 74LS10数据手册 74LS11数据手册

第2页 共8页 74LS12数据手册 74LS13数据手册 74LS14数据手册 74LS15数据手册 74LS16数据手册 74LS17数据手册 74LS19数据手册 74LS20数据手册 74LS21数据手册 74LS22数据手册 74LS23数据手册 74LS26数据手册 74LS27数据手册 74LS28数据手册

.v .. .. 74LS30数据手册 74LS32数据手册 74LS33数据手册 74LS37数据手册 74LS38数据手册 74LS40数据手册 74LS42数据手册 [1].要求0—15时,灭灯输入(BI )必须开路或保持高电平,如果不要灭十进制数零,则动态灭灯输入(RBI )必须开路或为高电平。 [2].将一低电平直接输入BI 端,则不管其他输入为何电平,所有的输出端均输出为低电平。 [3].当动态灭灯输入(RBI )和A,B,C,D 输入为低电平而试灯输入为高电平时,所有输出端都为低电平并且动态灭灯输入(RBO )处于第电平(响应条件)。 [4].]当灭灯输入/动态灭灯输出(BI/RBO )开朗路或保持高电平而试 灯输入为低电平时,所有各段输出均为高电平。 表中1=高电平,0=低电平。BI/RBO 是线与逻辑,作灭灯输入(BI )或动态灭灯(RBO )之用,或者兼为二者之用。

Xilinx FPGA入门连载1:ISE14.6安装

Xilinx FPGA入门连载1:ISE14.6安装 特权同学,版权所有 配套例程和更多资料下载链接: https://www.360docs.net/doc/f79627233.html,/s/1jGjAhEm 1 安装文件拷贝与解压缩 到SP6共享网盘(链接https://www.360docs.net/doc/f79627233.html,/s/1jGjAhEm)下的software文件夹下载ISE14.6的安装包。 随意选中前面的某个压缩包,右键单击选择“解压到当前文件夹”。 随后大约需要5-10分钟,解压才能完成。解压完成后,出现如下文件夹。

2 虚拟光驱或解压缩安装 点击进入文件夹“Xilinx.ISE.Design.Suite.14.6”,如图所示。 若用户PC安装了虚拟光驱,则使用虚拟光驱打开“XILINX_ISE_DS_14.6”进行安装。 假设用户PC没有安装虚拟光驱,则按照我们下面的步骤操作。右键单击“XILINX_ISE_DS_14.6”,选择“解压到XILINX_ISE_DS_14.6”,如图所示。 又是5-10分钟的漫长等待,谁让咱们土得连个虚拟光驱都没有捏! 3 ISE14.6安装 安装前面的步骤解压缩后,如图所示。

在着手开始安装前,建议大家把什么乱起八糟的杀毒软件都关一关,免得后面一大堆郁闷问题。 双击上图的最后一个可执行文件“xsetup”,随后便弹出了最基本的ISE安装界面,如图所示。点击右下角的“Next”进入下一步。 如图所示分别勾选“I accept …”和“I also accept…”两个选项,再点击右下角的“Next”进入下一步。

如图所示,勾选最下方的“I accept…”选项,然后点击右下角的“Next”进入下一步。 入下一步。

Xilinx ISE 使用入门

Xilinx ISE 使用入门 1、ISE的安装 现以ISE 5.2i为例介绍Xilinx ISE Series的安装过程。 1)系统配置要求 ISE 5.2i推荐的系统配置与设计时选用的芯片有关。因为在综合与实现过程中运算量非常大,所以对系统配置要求很高。为了提高综合、仿真、实现过程的速度,对于计算机的CPU的主频、主板和硬盘的工作速度,尤其是内存大小配置都有非常高的要求。在ISE 5.2i 支持的所有Xilinx的FPGA/CPLD中,要求最低的Spartan II和XC9500/XL/XV等系列需要的内存和虚拟内存推荐值均达到128MB,而对于Virtex-II XC2V8000来说,需要的内存和虚拟内存推荐值均高达3GB。 2)ISE 5.2i的安装 以中文版Windows XP操作系统为例加以说明。 (1)启动Windows XP,插入ISE5.2i安装光盘,自动或选择执行Install.exe,安装界面如图4.25所示。 图4.25 ISE5.2i安装界面 (2)单击此时安装界面上的操作选择“下一步”直到出现图示对话框,输入有效的Registration ID。之后单击“下一步”选择安装路径;再之后点击“下一步”,会弹出图4.26的对话框,可以选择器件模型。

图4.26 器件模型选择对话框 (3)点击“下一步”,如图4.27所示,可以选择器件种类。

图4.27 器件种类选择对话框 通过以上步骤后,可根据具体情况来选择,继续“下一步”即可完成安装。 安装完成后,环境变量应作如下描述: 若操作系统是Windows NT/2000/XP,选择开始->控制面板->系统->选项->系统->高级->环境变量,在环境变量中加入: 变量名:Xilinx 变量值:C:Xilinx(即安装路径) 具体设置如图4.28所示。 3 VHDL设计操作指南 首先进入ISE工程管理器(Project Navigator)界面,如图4.30所示。Project Navigator 是ISE所用集成工具的连接纽带,通过使用Project Navigator,设计者可以创建、组织和管理自己的设计。 图4.28 环境变量设置操作图 3)安装第三方软件

74LS系列芯片引脚图资料大全

74系列芯片引脚图资料大全 作者:佚名来源:本站原创点击数:57276 更新时间:2007年07月26日【字体:大中小】 为了方便大家我收集了下列74系列芯片的引脚图资料,如还有需要请上电子论坛https://www.360docs.net/doc/f79627233.html,/b bs/ 反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373

反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│ Y =A+C )│四总线三态门74LS125 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND

xilinx ise安装教程

《Xilinx ISE 14.2 安装指南》 1. 写在前面的话 到了这个年纪,一个人的路,总是孤独的。型号还有FPGA这一爱好,凭着自己的兴趣,不屈不饶的努力学习,不求有多大的成就,但求能给数字界贡献微薄的一份子。曾经无数的跌倒,曾经无数次的失落,曾经无数次的崩溃,尽管失去总比得到的多,这些都不重要,因为,我一直在努力,像松鼠那么努力! 光阴似箭,玩了大约3年的Altera FPGA,把它当做最亲密的伙伴的同时,我竟然开始玩弄Xilinx FPGA了。。。甚是激动。。。也许知己知彼,百战百殆,但对我而言,每一个都将是我学习的对象,也许是我的兴趣,也许是我的使命,这两者必定在我未来扮演重要的角色。尽然开始读研了,一个人的奋斗,没有找到久违的团队感,一度,我感到很孤独!虽然水平不过如此,见识还是那么的肤浅,能力还是不足,但好歹我终于找到了激情的欲望,也许拿到ZedBoard这一刻起,我又能找回方向,填补孤独的心灵了。 允许,还是老样子,我将会一步一步记录我Xilinx FPGA的学习过程,包括我的设计,思想,灵感;我会将此与Altera FPGA对照着来触摸,深化,我希望能让更多的人了解Xilinx,而不是仅仅局限于Altera FPGA。此刻开始,从新回归到菜鸟水平,“巧妇难为无米之炊”,万事开头难,在收集了一大包相关Xilinx的资料后,咱就开始安家吧—Xilinx ISE 14.2安装指南。

2. Xilinx ISE 14.2软件下载 由于偷懒,省的更换系统后又得下载对应版本的软件,在官网直接下载全功能版本,8.2G,支持Windows & Linux,网址及连接如下所示:

74系列芯片引脚图

74系列芯片引脚图、功能、名称、资料大全(含74LS、74HC等),特别推荐为了方便大家,我收集了下列74系列芯片的引脚图资料。 说明:本资料分3部分:(一)、TXT文档,(二)、图片,(三)、功能、名称、资料。 (一)、TXT文档 反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门 LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373

反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘

1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│ Y =A+C )│四总线三态门 74LS125 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND Vcc -G B1 B2 B3 B4 B8 B6 B7 B8 ┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位总线驱动器 74LS245 │20 19 18 17 16 15 14 13 12 11│ )│ DIR=1 A=>B │ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A └┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘ DIR A1 A2 A3 A4 A5 A6 A7 A8 GND

ISE学习教程

1、ISE的安装 现以ISE 5.2i为例介绍Xilinx ISE Series的安装过程。 1)系统配置要求 ISE 5.2i推荐的系统配置与设计时选用的芯片有关。因为在综合与实现过程中运算量非常大,所以对系统配置要求很高。为了提高综合、仿真、实现过程的速度,对于计算机的CPU的主频、主板和硬盘的工作速度,尤其是内存大小配置都有非常高的要求。在ISE 5.2i支持的所有Xilinx的FPGA/CPLD中,要求最低的Spartan II和XC9500/XL/XV等系列需要的内存和虚拟内存推荐值均达到128MB,而对于Virtex-II XC2V8000来说,需要的内存和虚拟内存推荐值均高达3GB。 2)ISE 5.2i的安装 以中文版Windows XP操作系统为例加以说明。 (1)启动Windows XP,插入ISE5.2i安装光盘,自动或选择执行Install.exe,安装界面如图4.25所示。 图4.25 ISE5.2i安装界面 (2)单击此时安装界面上的操作选择“下一步”直到出现图示对话框,输入有效的Registration ID。之后单击“下一步”选择安装路径;再之后点击“下一步”,会弹出图4.26的对话框,可以选择器件模型。

图4.26 器件模型选择对话框 (3)点击“下一步”,如图4.27所示,可以选择器件种类。

图4.27 器件种类选择对话框 通过以上步骤后,可根据具体情况来选择,继续“下一步”即可完成安装。 安装完成后,环境变量应作如下描述: 若操作系统是Windows NT/2000/XP,选择开始->控制面板->系统->选项->系统->高级->环境变量,在环境变量中加入: 变量名:Xilinx 变量值:C:Xilinx(即安装路径) 具体设置如图4.28所示。

ISE安装步骤

从网上下载测试版软件华中科技大学ftp:211.69.207.25下载 ModelSim.SE.v6.0 仿真工具 Xilinx.ISE.v6.3i.Incl.Keymaker- foundation安装软件 Xilinx.ISE.v6.3i.VIRTEX.VIRTEXE.Addon- foundation库文件1 Xilinx.ISE.v6.3i.VIRTEX.VIRTEXE.Addon.Addon- foundation库文件2 SYNPLICITY_SYNPLIFY_PRO_V7.7 foundation器件综合软件 一、ModelSim.SE.v6.0的安装 双击图标进行安装,然后双击keygenerate产生文件license.dat文件。将其拷贝到modelsim安装的文件夹下。单击我的电脑,在右键中修改环境变量。 加入环境变量LM_LICENSE_FILE,变量值为C:/Modeltech_6.0/license.dat 则modelsim安装成功.还需在modelsim安装的文件夹下拷贝已经编译好的一些库文件,为其后面的处理作好准备,三个库文件为XilinxCoreLib_ver、unisims_ver、simprims_ver。 进入ModelSIM安装文件夹,找到一个名为ModelSIM.ini的文件,将其属性由只度改为存档,在[Library]段的最后加上simprims_ver = $MODEL_TECH/../simprims_ver XilinxCoreLib_ver= $MODEL_TECH/../XilinxCoreLib_ver unisims_ver= $MODEL_TECH/../unisims_ver 目的是让ModelSIM运行时可以自动加载编译好的库文件。 二、Xilinx.ISE.v6.3i.Incl.Keymaker的安装 双击其安装软件进行安装,光盘里有两张光盘,和一个ID产生器,安装两个光盘时,要使用同一个ID。 将Xilinx.ISE.v6.3i.VIRTEX.VIRTEXE.AddXilinx .ISE .v6.3i.VIRTEX.VIRTEXE.Addon.Add 分别解压缩,将解压缩得到的文件夹拷贝到Xilinx安装的目录下(第二个文件只需拷贝最後一个文件) ISE6.2的安装,大体一致,记得有选择set/update时全选,不然有些功能无法适用,至于升级,打开edit后,在perference中去掉就可以了。 如果你装了防火墙,如天网、瑞星,第一次启动时,要一直允许ise访问网络,不然会抱错的。 经试验,最好安装在winXP系统下。 三、SYNPLICITY_SYNPLIFY_PRO_V7.7的安装 将其完全解压后进行安装,其中的license要选择使用本机的license,然后用解压后的 license.txt覆盖SYNPLICITY目录下的license,用解压后的覆盖 Synplicity\Synplify_77\bin\mbin目录下的同名文件。 发现环境变量改变为SYNPLICITY_LICENSE_FILE,变量值为C:\Synplicity\license.txt。软件整体安装成功!

Xilinx ISE 使用入门手册

Xilinx ISE使用入门手册1 发布日期:2009-3-613:06:10文章来源:搜电浏览次数:2940 1、ISE的安装 现以ISE5.2i为例介绍Xilinx ISE Series的安装过程。 1)系统配置要求 ISE5.2i推荐的系统配置与设计时选用的芯片有关。因为在综合与实现过程中运算量非常大,所以对系统配置要求很高。为了提高综合、仿真、实现过程的速度,对于计算机的CPU的主频、主板和硬盘的工作速度,尤其是内存大小配置都有非常高的要求。在ISE5.2i 支持的所有Xilinx的FPGA/CPLD中,要求最低的Spartan II和XC9500/XL/XV等系列需要的内存和虚拟内存推荐值均达到128MB,而对于Virtex-II XC2V8000来说,需要的内存和虚拟内存推荐值均高达3GB。 2)ISE5.2i的安装 以中文版Windows XP操作系统为例加以说明。 (1)启动Windows XP,插入ISE5.2i安装光盘,自动或选择执行Install.exe,安装界面如图4.25所示。 图4.25ISE5.2i安装界面

(2)单击此时安装界面上的操作选择“下一步”直到出现图示对话框,输入有效的Registration ID。之后单击“下一步”选择安装路径;再之后点击“下一步”,会弹出图4.26的对话框,可以选择器件模型。 图4.26器件模型选择对话框 (3)点击“下一步”,如图4.27所示,可以选择器件种类。

图4.27器件种类选择对话框 通过以上步骤后,可根据具体情况来选择,继续“下一步”即可完成安装。 安装完成后,环境变量应作如下描述: 若操作系统是Windows NT/2000/XP,选择开始->控制面板->系统->选项->系统->高级->环境变量,在环境变量中加入: 变量名:Xilinx 变量值:C:Xilinx(即安装路径) 具体设置如图4.28所示。

Spartan-14.7平台与ISE软件的入门

Spartan-3平台与ISE软件的入门 一、快速浏览Spartan-3E Starter Kit的用户指南,便于以后进行内容查找。 中文用户指南:Spartan-3E Starter Kit Board User Guide.mht 英文用户指南:Spartan-3E Starter Kit Board User Guide.pdf 二、ISE软件安装。 根据资料自学完成安装(在个人电脑上),ISE推荐版本:14.7。注意需要破解(即提供license)。 三、ISE软件的初次使用。 在Spartan-3E开发板上,使用ISE软件,完成一个最基本工程的建立、编程、仿真、下载实现。 3.1 1)运行ISE Design Suite软件,界面如下

File New Project a)设置顶层文件类型Top-level source type为Schematic(原理图)

b)选择工程的保存位置Location和工作目录Working Directory 为fpgaxunlian c)为工程取名,如:xunlian1 点击Next 进行下述设置

根据观察我们使用的Spartan 3E开发板上的FPGA芯片上的字,可知目标FPGA芯片的属性如下 芯片系列(Family):Spartan3E 芯片型号(Device):XC3S500E 芯片封装(Package):FG320 速度等级(Speed):-4(注:XILINX的FPGA,值越大,速度等级越高) 综合工具(Systhesis Tool)选择ISE自带的XST 仿真工具(Simulator)选择ISE自带的Isim 编程语言(Preferred Language)选择Verilog 然后,点击Next

基于Xilinx-ISE-12.4的FPGA使用例子

基于ISE 12.4的FPGA设计基本流程 关键字:FPGA XILINX ISE 12.4ISE设计流程时序仿真 信息化调查找茬投稿收藏评论好文推荐打印社区分享 ISE是使用XILINX的FPGA的必备的设计工具,它可以完成FPGA开发的全部流程,包括设计输入、仿真、综合、布局布线、生成BIT文件、配置以及在线调试等,功能非常强大。本文主要通过一个最简单的“点亮LED灯”实例介绍了基于ISE 12.4软件的FPGA设计流程,包括设计输入、仿真、约束、下载等。 0 前言 一套完整的FPGA设计流程包括电路设计输入、功能仿真、设计综合、综合后仿真、设计实现、添加约束、布线后仿真和下载、调试等主要步骤。 图1 FPGA设计流程 目前赛灵思公司FPGA设计软件的最新版本是ISE 13,由于笔者暂未用到该版本,本文中以ISE 12.4为例。 ISE 9以后的版本的安装文件都是集成到了一个包当中,安装起来很方便。软件包里面包含四个大的工具,ISE Design Tools、嵌入式设计工具EDK、PlanAhead、Xtreme DSP设计工具System Generator。ISE设计工具中包含ISE Project Navigator、ChipScope Pro 和以下工具: 图2 ISE软件包中部分工具 做一般的FPGA逻辑设计时只需要用到ISE设计工具,下面通过一个最简单的“点亮LED 灯”实例,具体讲解ISE设计工具的使用,并介绍基于ISE的FPGA设计基本流程。 1 创建工程 (1)在桌面快捷方式或开始→所有程序→Xilinx ISE Design Suite 12.4→ISE Design Tools中打开ISE Project Navigator。 (2)单击File→New Project...出现下图所示对话框。

常用实验器件引脚图

常用实验器件引脚图 1. 四2输入正与非门74LS00 Y=AB VCC 4B 4Y 3B 3A 3Y 4A 1A 1B 1Y 2A 2B 2Y GND 2. 四2输入正或非门 74LS02 Y=A+B VCC 4Y 4B 4A 3Y 3B 3A 1Y 1A 1B 2Y 2A 2B GND 3. 六反向器 74LS04 Y=A VCC 6A 6Y 5A 5Y 4A 4Y 1A 1Y 2A 2Y 3A 3Y GND

Y=AB VCC 4B 4A 4Y 3B 3A 3Y 1A 1B 1Y 2A 2B 2Y GND 5. 双4输入正与非门 74LS20 Y=ABCD VCC 2D 2C NC 2B 2A 2Y 1A 1B NC 1C 1D 1Y GND 6. 双与或非门74LS51 2Y=(2A2B)+VCC 1B 1C 1D 1E 1F 1Y 1A 2A 2B 2C 2D 2Y GND (2C2D) 1Y=(1A1B1C)+(1D1E1F)

1Y=A VC C 4B 4A 4Y 3B 3A 3Y 1A 1B 1Y 2A 2B 2Y GND ⊕ B=AB+A B 8. 4位二进制计数器 74LS93 输入NC QA QD GND QB QC 输入NC V NC NC A B R 0(1R 0(2

注:A. 对BCD计数,输出QA连接输入B。 B. 对二五混合进制计数,输出QD连接输入A。 C. 输出QA连接输入B。 D. H=高电平L=低电平X=无关

9. 四2-1线数据选择器/多路开关74LS157 V C C G 4A 4B 4Y 3A 3B 3Y S 1A 1B 1Y 2A 2B 2Y GND 10. 74LS181 B0A0S3S2S1S0CN M GND F0F1F2VCC A1CM+4P A=B B1A2B2 A3B3G F3

ISE12.4教程

0 前言 一套完整的FPGA设计流程包括电路设计输入、功能仿真、设计综合、综合后仿真、设计实现、添加约束、布线后仿真和下载、调试等主要步骤。 图1 FPGA设计流程 目前赛灵思公司FPGA设计软件的最新版本是ISE 13,由于笔者暂未用到该版本,本文中以ISE 12.4为例。 ISE 9以后的版本的安装文件都是集成到了一个包当中,安装起来很方便。软件包里面包含四个大的工具,ISE Design Tools、嵌入式设计工具EDK、PlanAhead、Xtreme DSP设计工具System Generator。ISE设计工具中包含ISE Project Navigator、ChipScope Pro 和以下工具: 图2 ISE软件包中部分工具 做一般的FPGA逻辑设计时只需要用到ISE设计工具,下面通过一个最简单的“点亮LED 灯”实例,具体讲解ISE设计工具的使用,并介绍基于ISE的FPGA设计基本流程。 1 创建工程 (1)在桌面快捷方式或开始→所有程序→Xilinx ISE Design Suite 12.4→ISE Design Tools中打开ISE Project Navigator。 (2)单击File→New Project...出现下图所示对话框。

图3 新建工程对话框 在该界面输入工程名、选择工程存放路径、选择顶层模块类型,其中顶层模块类型有硬件描述语言(HDL)、原理图(Schematic)、SynplifyPro默认生成的网表文件(EDIF)、Xilinx IP Core和XST生成的网表文件(NGC/NGO)这四种选项,这里我们使用Verilog模块作为顶层输入,所以选HDL。 (3)单击Next >进入下一步,弹出下图所示对话框。

ISE教程

光盘放进DVD光驱,等待其自动运行(如果没有自动运行,直接执行光盘目录下的Setup.exe文件程序即可),会弹出图4-1所示的欢迎界面,点击“Next”进入下一页。 图4-1 ISE安装过程的欢迎界面 2.接着进入注册码获取、输入对话框,如图4-2所示。注册码可以通过网站、邮件和传真方式申请注册码。如果已有注册码,输入后单击“Next”按键后继续。

图4-2 ISE9.1安装程序的注册码输入界面 购买了正版软件后,最常用的方法就是通过网站注册获取安装所需的注册码。首先在Xilinx的官方主页 https://www.360docs.net/doc/f79627233.html,上建立自己的帐号,然后点击图4-1中的“Website”按键,登陆帐号,输入CD盒上的产品序列号(序号的格式为:3个字符+9个数字),会自动生成16位的注册码,直接记录下来即可,同时Xilinx网站会将注册码的详细信息发送到帐号所对应的邮箱中。 3.下一个对话框是Xilinx软件的授权声明对话框,选中“I accept the terms of this software license”,单击“Next”后进入安装路径选择界面,如图4-3所示。单击“Browse”按键后选择自定义安装路径,单击“Next”按键继续 图4-3 ISE软件安装路径选择对话框 4.接下来的几个对话框分别是选择安装组件选择,如图4-4所示,用户需要选择自己使用的芯片所对应的模块,这样才能在开发中使用这些模块。在计算机硬盘资源不紧张的情况下,通常选择“Select All”。

图4-4 ISE安装组件选择界面 评论[支持者: 0 人,反对者: 0 人,中立者: 0 人] 查看评论信息 2008-11-26 20:53:00 第3楼 小大 个性首页| QQ 5.随后进入设置环境变量页面,保持默认即可。如果环境变量设置错误,则安装后不能正常启动ISE。选择默认选项,安装完成后的环境变量,其值为安装路径。最后进入安装确认对话框,单击Install按钮,即可按照用户的设置自动安装ISE,如图4-5所示

赛灵思ISE设计流程介绍

The ISE? design flow is shown in the following figure and described in the following sections. Note The following sections provide links to additional Help topics. In the Help Viewer, click the Synchronize TOC button to view all related Help topics. Design Creation During design creation, you create an ISE project and then, create or add source files to that project. ISE projects can contain many types of source files and design modules, including HDL, EDIF/NGC netlist, schematic, intellectual property (IP), embedded processor, and Digital Signal Processing (DSP) modules. For more information, see the following topics: Understanding the ISE Project File Design Entry Overview Working with Source Control Systems Synthesis During synthesis, the synthesis engine compiles the design to transform HDL sources into an architecture-specific design netlist. The ISE software supports the use of Xilinx Synthesis Technology (XST), which is delivered with the ISE software, as well as third party synthesis tools, including Synplify, Synplify Pro, and Precision software. For more information, see the following topics: XST Synthesis Overview Using Synplify or Synplify Pro Software for Synthesis Using Precision Software for Synthesis

74系列元件引脚图

反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS24 5 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373 反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│

Y =A+C )│四总线三态门74LS125 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND Vcc -G B1 B2 B3 B4 B8 B6 B7 B8 ┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位总线驱动器74LS245 │20 19 18 17 16 15 14 13 12 11│ )│ DIR=1 A=>B │1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A └┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘ DIR A1 A2 A3 A4 A5 A6 A7 A8 GND 页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器 正逻辑与门,与非门: Vcc 4B 4A 4Y 3B 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = AB )│ 2输入四正与门74LS08 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1B 1Y 2A 2B 2Y GND Vcc 4B 4A 4Y 3B 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ __ │14 13 12 11 10 9 8│ Y = AB )│ 2输入四正与非门74LS00 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1B 1Y 2A 2B 2Y GND Vcc 1C 1Y 3C 3B 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ ___ │14 13 12 11 10 9 8│ Y = ABC )│ 3输入三正与非门74LS10 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1B 2A 2B 2C 2Y GND

Xilinx_FPGA下载烧写教程

Step1 学习下载配置Xilinx 之FPGA 配合Mars-EDA 的Spartan2 核心板,用图文方式向大家详细讲述如何下载配置Xilinx 的FPGA。 FPGA 下载模式说明 S1 为 FPGA 下载模式选择跳线,M0,M1,M2 默认状态为通过 4.7K 电阻上拉到 3.3V,当用跳线帽短接 S1 的PIN3 和PIN6 将置 M0 为0,同理,短接 PIN2 和PIN5,PIN3 和PIN4 将置 M1,M2 为0。M0,M1,M2 的电平和 FPGA 下载之间的关系参见下图:(Boundary-scan mode)是调试最常用的 JTAG 模式。当采用板载 PROM 时,采用的跳线模式是 Master Serial Mode –短路 PIN1 和PIN6,PIN2 和PIN5 J2 为Slave Serial Mode 的接口。下载模式跳线 S1 短接PIN1 和PIN6,PIN2 和PIN5 即可。 J3 为 JTAG Mode 的接口。下载模式跳线短接 PIN1 和 PIN6 即可。

S2 跳线说明 1.通过 JTAG 方式烧录 FPGA:短接 PIN1 和PIN3。 2.通过 JTAG 方式烧录 PROM:短接 PIN3 和PIN5,PIN2 和PIN4. 3.通过菊花链下载 FPGA 和烧录 PROM:短接 PIN3 和PIN5,PIN4 和PIN6. 下面我们利用 Spartan2 核心板介绍一下通过 JTAG 菊花链方式下载 FPGA 和烧录 PROM. 硬件跳线选择: 1.跳线 S1: 此时要求 M0 M1 M2 = 100, 设置 FPGA 的下载方式为 Boundary-scan mode, 此时将 M1 和M2 的跳线安上。 跳线 S2 : 通过菊花链下载 FPGA 和烧录 PROM:短接 PIN3 和 PIN5,PIN4 和 PIN6. 2.将 Xilinx 下载线和核心板上 JTAG mode 接口 J3 相连,连接到计算机并口。核心板上电。

Xilinx ISE 使用入门手册

Xilinx ISE 使用入门手册 发布日期:2009-3-6 13:06:10文章来源:搜电浏览次数:6414 1、ISE的安装 现以ISE 5.2i为例介绍Xilinx ISE Series的安装过程。 1)系统配置要求 ISE 5.2i推荐的系统配置与设计时选用的芯片有关。因为在综合与实现过程中运算量非常大,所以对系统配置要求很高。为了提高综合、仿真、实现过程的速度,对于计算机的CPU的主频、主板和硬盘的工作速度,尤其是内存大小配置都有非常高的要求。在ISE 5.2i支持的所有Xilinx的FPGA/CPLD中,要求最低的Spartan II和XC9500/XL/XV 等系列需要的内存和虚拟内存推荐值均达到128MB,而对于Virtex-II XC2V8000来说,需要的内存和虚拟内存推荐值均高达3GB。 2)ISE 5.2i的安装 以中文版Windows XP操作系统为例加以说明。 (1)启动Windows XP,插入ISE5.2i安装光盘,自动或选择执行Install.exe,安装界面如图4.25所示。 图4.25 ISE5.2i安装界面 (2)单击此时安装界面上的操作选择“下一步”直到出现图示对话框,输入有效的Registration ID。之后单击“下一步”

选择安装路径;再之后点击“下一步”,会弹出图4.26的对话框,可以选择器件模型。 图4.26 器件模型选择对话框 (3)点击“下一步”,如图4.27所示,可以选择器件种类。

图4.27 器件种类选择对话框 通过以上步骤后,可根据具体情况来选择,继续“下一步”即可完成安装。 安装完成后,环境变量应作如下描述: 若操作系统是Windows NT/2000/XP,选择开始->控制面板->系统->选项->系统->高级->环境变量,在环境变量中加入: 变量名:Xilinx 变量值:C:Xilinx(即安装路径) 具体设置如图4.28所示。

xilinx ISE时序约束笔记-中文

时序约束的两个步骤: 1.路径终点生产groups(顾名思义就是进行分组) 2.指点不同groups之间的时序要求 全局约束使用默认的路径终点groups——即所有的触发器、I/O pads等ISE时序约束笔记2——Global Timing Constraints 问题思考 单一的全局约束可以覆盖多延时路径 如果箭头是待约束路径,那么什么是路径终点呢? 所有的寄存器是否有一些共同点呢? 问题解答 什么是路径终点呢? ——FLOP1,FLOP2,FLOP3,FLOP4,FLOP5。 所有的寄存器是否有一些共同点呢? ——它们共享一个时钟信号,约束这个网络的时序可以同时覆盖约束这些相关寄存器间的延时路径。 周期约束 周期约束覆盖由参考网络钟控的的同步单元之间的路径延时。

周期约束不覆盖的路径有:input pads到output pads之间的路径(纯组合逻辑路径),input pads到同步单元之间的路径,同步单元到output pads之间的路径。 周期约束特性 周期约束使用最准确的时序信息,使其能够自动的计算: 1.源寄存器和目的寄存器之间的时钟偏斜(Clock Skew) 2.负沿钟控的同步单元 3.不等同占空比的时钟 4.时钟的输入抖动(jitter) 假设: 1.CLK信号占空比为50% 2.周期约束为10ns 3.由于FF2将在CLK的下降沿触发,两个触发器之间的路径实际上将被约 束为10ns的50%即5ns

时钟输入抖动(Clock Input Jitter) 时钟输入抖动是源时钟的不确定性(clock uncertainty)之一 时钟的不确定时间必须从以下路径扣除: ——周期约束建立时间路径 ——OFFSET IN约束的建立时间路径 时钟的不确定时间必须添加到以下路径中: ——周期约束保持时间路径 ——OFFSET IN约束保持时间路径 ——OFFSET OUT约束路径 Pad-to-Pad约束 ——不包含任何同步单元的纯组合逻辑电路 ——纯组合逻辑延时路径开始并结束于I/O pads,所以通常会被我们遗漏而未约束 ISE时序约束笔记3——Global Timing Constraints 问题思考 哪些路径是由CLK1进行周期约束? 哪些路径是由pad-to-pad进行约束?

关于Xilinx ISE简单使用方法介绍

关于Xilinx ISE(14.2)简单使用方法介绍 安装ISE软件基本上是一路点击鼠标就是,但必须安装注册表文件,可在网上查找,可能是一个生成注册表文件或注册表文件(license)。功能仿真是在设计输入后进行;时序仿真是在逻辑综合后或布局布线后进行。(系统差不多占20GB硬盘) 1.创建工程文件(New Projiect) File New Projiect 。如输入文件名:Two2One。 设置一些参数,如下图所示:(注意:使用的是BASYS2板) 在上图点击Next键,弹出如下窗口,设置一些参数,如下图所示:(注意:使用的是BASYS2板)

2.创建资源文件(New Source) Project→New Source。如输入文件名:One2Two。 选择模型,如Verilog Module,输入HDL语言; 或输入原理图。 或Project→Add Source,,增加已存在的资源文件(*.v)。实例:二选一电路。 点击Next键,弹出如下窗口,

弹出参数信息窗口:

参数表:

之后保存文件。 文本: module Two2One( input [7:0] x_in, input flag, output [7:0] y_out, ); assign y_out = flag ? x_in : 8'b00000000; endmodule 3.程序语法检查 如下图所示: 或者:

4.创建测试文件(功能仿真数据的建立) Project New Source。如输入文件名:Two2One_tf(*.v)。 选择,如Verilog Test Fxiture,建立用于测试以上资源文件(电路)用的数据文件。建立 不同时间段的输入数据,用于产生相应时段的输出波形。

fpGa_CPLD设计工具xilinxISE使用详解

1.第一章:FPGA/CPLD简介 ●FPGA一般是基于SRAM工艺的,其基于可编程逻辑单元通常是由查找表(LUT, look up table)和寄存器(register)组成。其中内部的查找表通常是4输入的,查找表一般完成纯组合逻辑功能; ●Xilinx可编程逻辑单元叫做slice,它由上下两部分组成,每部分都由一个register 加上一个LUT组成,被称为LC(logic cell,逻辑单元),两个LC之间有一些共用逻辑,可以完成LC之间的配合工作与级连; ●Altera可编程逻辑单元叫做LE(Logic Element,逻辑单元),由一个register加上 一个LUT构成;Lattice的底层逻辑单元叫做PFU(programmable Function unit,可编程功能单元),它由8个LUT和9个register组成。 ●Ram和dpram/spram/伪双口RAM,CAM(content addressable memory)。Fpga中其 实没有专业的rom硬件资源,实现ROM是对RAM赋初置,并且保存此初值 ●CAM,即内容地址储存器,在其每个存储单元都包含了一个内嵌的比较逻辑,写 入cam的数据会和其内部存储的每一个数据进行比较,并返回与端口数据相同的所以内部数据的地址。总结:RAM是一种根据地址读/写数据的存储单元;而CAM 和RAM恰恰相反,它返回的是与端口数据相匹配的内部地址。使用很广,比如路由器中的地址交换表等等 ●Xilinx块ram大小是4kbit和18kbit两种结构。Lattice块ram是9kbit ●分布式ram适合用于多块小容量的ram的设计; ●Dll(delay-locked loop)延迟锁定回环或者pll(phase locked loop)锁相环,可以用 以完成时钟的高精度,地抖动的倍频/分频/占空比调整/移相等功能。Xilinx主要集成的是DLL,叫做CLKDLL,在高端的FPGA中,CLKDLL的增强型模块为DCM (digital clock manager,数字时钟管理模块)。生成的方式有两种:1.在HDL代码和原理图中直接实例化。2.在IP核生成器中配置相关参数,自动生成IP。 ●Cpu和dsp处理模块的硬件主要由一些加/乘/快速进位链,pipelining和mux等结构 组成的,加上用逻辑资源和块ram实现的软核部分组成强大的软件计算中心。比较适合实现FIR滤波器/编码解码器和FFT等运算。 ●Fpga的开发流程:1.电路设计与输入,自顶而下设计,利于模块的划分与复用,可 移植性好,通用性好,设计部因为芯片的工艺和结构的改变而改变,更利于向ASIC 的移植。这通常使用verilog语言来设计。2.功能仿真:电路设计完成后,要用专应的仿真工具对设计进行功能仿真,验证电路是否符合设计的要求。也叫前仿真,优点:能及时发现设计中的错误,加快设计进度,提高设计的可靠性。3.综合优化:(synthesize)是指将hdl语言,原理图等设计输入翻译成由与/或/非门/ram/触发器等基本逻辑单元组成的逻辑连接(网表),并根据目标与要求(约束条件)优化所生成的逻辑连接,输出edf和edn等文件。4.综合后仿真:仿真时,把综合生成的延时文件反标到综合仿真模型中去。5:实现:使用FPGA/CPLD厂商提供的工具软件,根据所选芯片型号,将综合输出的逻辑网表适配到具体的FPGA/CPLD器件上,这个过程叫做实现(implementation)过程。其中xinlinx的实现过程分为翻译(translate)/映射(map)和布局布线(place and route)的三个步骤。因为只有器件开发商最了解器件内部的结构,所以实现步骤必须选用器件开发商提供的工具。 6.时序仿真与验证:布局布线后首先应该做时序仿真,静态时序分析STA(static timing analyzer)7.调试与加载配置iMPACT与BitGen集成起来。 ●增量式综合和增量式布局布线(Incremental design)流程:增量是综合是在综合过 程仅对修改过的模块进行重新编译,保持为改变设计的原有综合结果。增量是布局