wince+S3C6410 SD卡启动

wince+s3c6410 SD卡启动

1. 基于IROM SD/MMC启动方式的原理

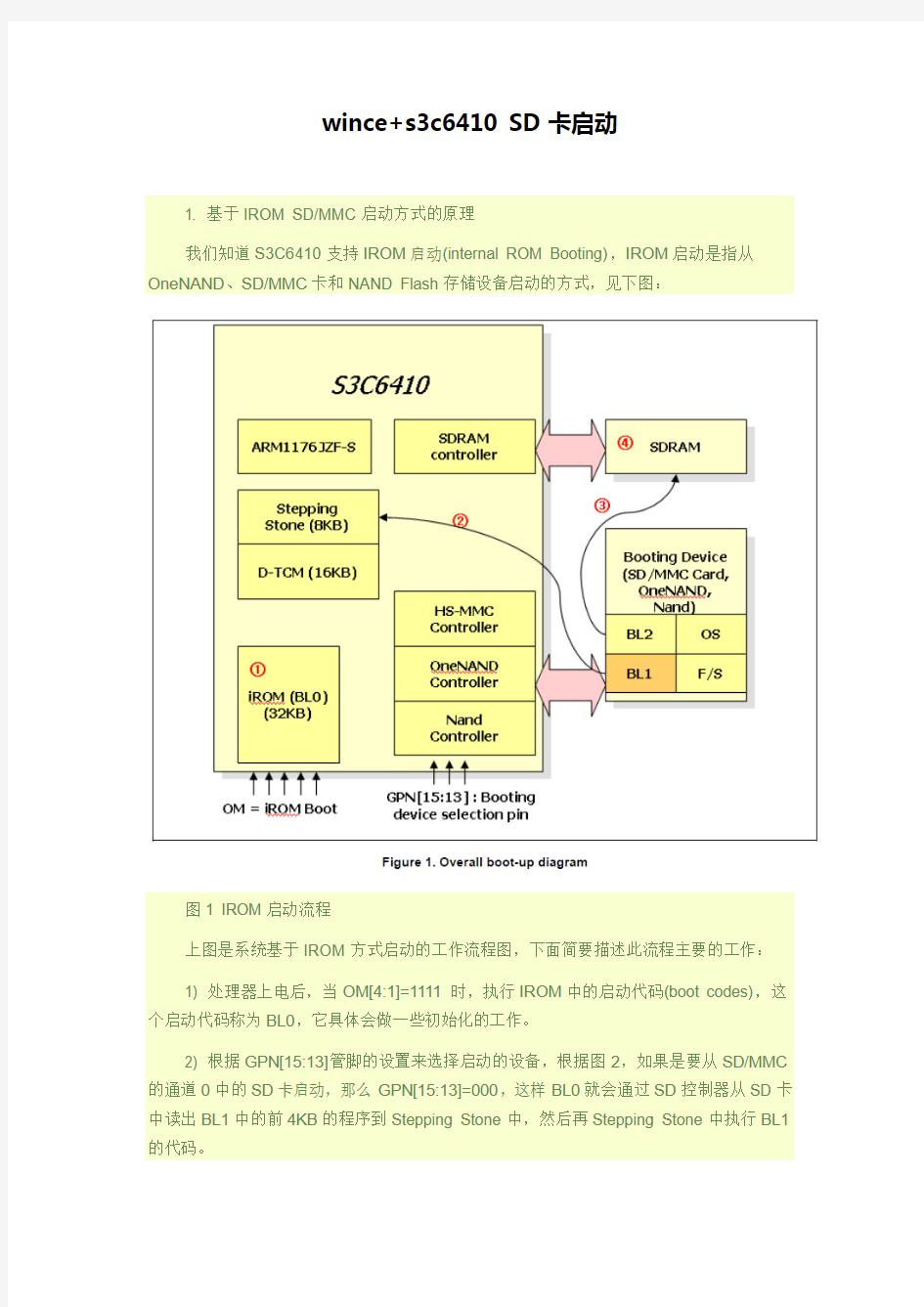

我们知道S3C6410支持IROM启动(internal ROM Booting),IROM启动是指从OneNAND、SD/MMC卡和NAND Flash存储设备启动的方式,见下图:

图1 IROM启动流程

上图是系统基于IROM方式启动的工作流程图,下面简要描述此流程主要的工作:

1) 处理器上电后,当OM[4:1]=1111时,执行IROM中的启动代码(boot codes),这个启动代码称为BL0,它具体会做一些初始化的工作。

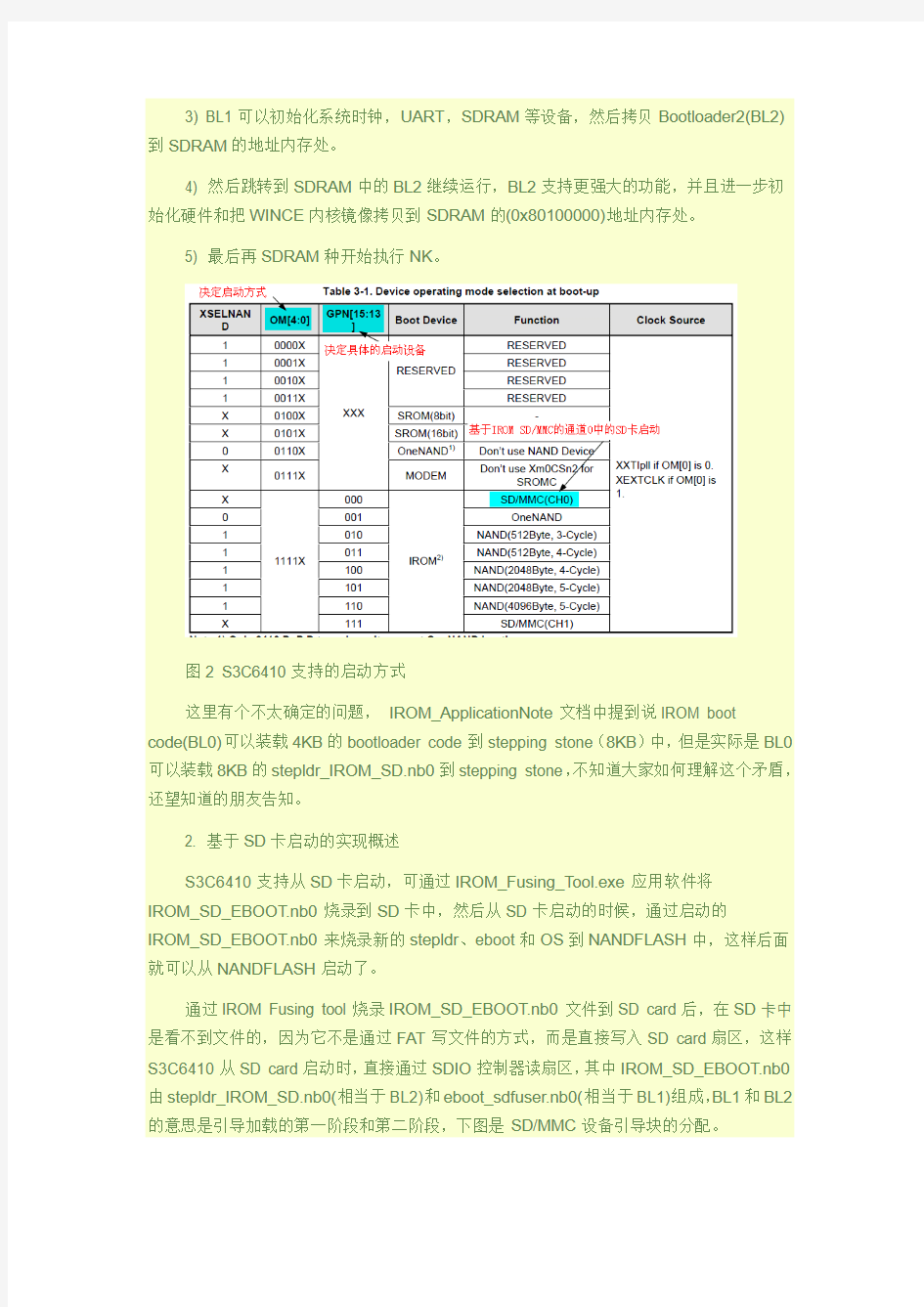

2) 根据GPN[15:13]管脚的设置来选择启动的设备,根据图2,如果是要从SD/MMC 的通道0中的SD卡启动,那么GPN[15:13]=000,这样BL0就会通过SD控制器从SD卡中读出BL1中的前4KB的程序到Stepping Stone中,然后再Stepping Stone中执行BL1的代码。

3) BL1可以初始化系统时钟,UART,SDRAM等设备,然后拷贝Bootloader2(BL2)到SDRAM的地址内存处。

4) 然后跳转到SDRAM中的BL2继续运行,BL2支持更强大的功能,并且进一步初始化硬件和把WINCE内核镜像拷贝到SDRAM的(0x80100000)地址内存处。

5) 最后再SDRAM种开始执行NK。

图2 S3C6410支持的启动方式

这里有个不太确定的问题,IROM_ApplicationNote文档中提到说IROM boot

code(BL0)可以装载4KB的bootloader code到stepping stone(8KB)中,但是实际是BL0可以装载8KB的stepldr_IROM_SD.nb0到stepping stone,不知道大家如何理解这个矛盾,还望知道的朋友告知。

2. 基于SD卡启动的实现概述

S3C6410支持从SD卡启动,可通过IROM_Fusing_Tool.exe应用软件将

IROM_SD_EBOOT.nb0烧录到SD卡中,然后从SD卡启动的时候,通过启动的

IROM_SD_EBOOT.nb0来烧录新的stepldr、eboot和OS到NANDFLASH中,这样后面就可以从NANDFLASH启动了。

通过IROM Fusing tool烧录IROM_SD_EBOOT.nb0文件到SD card后,在SD卡中是看不到文件的,因为它不是通过FAT写文件的方式,而是直接写入SD card扇区,这样S3C6410从SD card启动时,直接通过SDIO控制器读扇区,其中IROM_SD_EBOOT.nb0由stepldr_IROM_SD.nb0(相当于BL2)和eboot_sdfuser.nb0(相当于BL1)组成,BL1和BL2的意思是引导加载的第一阶段和第二阶段,下图是SD/MMC设备引导块的分配。

图3 SD/MMC设备启动块分配图

由上图可知SD卡的最后一个块(block,这里也就是sector,每个sector为512Bytes)因为预留下来,所以我们不能使用,倒数第二个block指定用于SD卡的标签(signature),从[LAST-18]到[LAST-3]这16块用于保存BL1,根据上图并结合BL2的大小可以判断BL2在SD卡中的位置。

3. 烧到IROM_SD_EBOOT.nb0烧录到SD卡

根据上面的描述,我们知道要把IROM_SD_EBOOT.nb0烧录到SD卡中的具体位置,下面先来看IROM Fusing tool.exe的应用界面

图4 IROM_Fusing_tool.exe的界面

在上图选择START的时候,我们来看IROM_Fusing_tool.exe源代码的主要实现部分,下面看第一部分:

图5 IROM_Fusing_tool.exe写动作主要实现部分

为什么从第0x52到0x56这5字节的内容是文件系统的标识符呢?我们通过winhex 工具来查看SD卡的启动区的内容,这些内容是对SD卡进行格式化的时候写进SD卡中的,

如下:

下面继续来看第二部分:

图7 IROM_Fusing_tool.exe写动作主要实现部分

SDHC设备引导块的分配如下:

图8 SDHC设备引导块的分配

4. 启动时从SD卡中读取IROM_SD_EBOOT.nb0并

S3C6410启动后,基于IROM+SD的启动方式,CPU先执行BL0的启动代码,其中BL0在启动过程中会通过SD卡控制器把BL1(也就是stepldr_IROM_SD.nb0,大小为8KB)的内容拷贝到stepping stone中),然后在stepping stone中执行BL1的代码,BL1在执行过程中会调用main函数,如下:

图9 BL1的main函数

到此BL2的内容已经复制到SDRAM指定的内存地址处,并且开始执行了,然后可以通过IROM_SD_EBOOT.nb0的下载功能手动或者自动下载block0、eboot.bin或是NK.bin 到NANDFLASH中了。

4.1 保存SD/MMC卡信息的全局变量

在使用SD/MMC卡作为启动设备的时候,SD/MMC卡的信息必须要保存在指定的区域,见下图:

图10 保存SD/MMC卡的信息的地址及用途定义

4.2 设备复制函数(Device Copy Function)

S3C6410内部包含了引导设备的块赋值函数的ROM代码,所以开发者不需要实现设备复制函数,这些内部的函数可以复制任何设备的数据到SDRAM中,使用者在内部的ROM 代码执行之后可以使用这些函数,因为这些函数是在BL0阶段初始化的。下面是这些设备复制函数的描述表

图11 设备赋值函数说明

Z-Turn Board U-Boot启动流程 zynq

Z-Turn Board使用Xilinx的Zynq 7000系列芯片,即Zynq-7000 Extensible Processing Platform,是一个可扩展处理平台,简单说就是有个FPGA做外设的A9双核处理器。 所以,它的启动流程自然也和FPGA完全不同,而与传统的ARM处理器类似。 Zynq7000支持多种设备启动,包括Jtag、NAND、parallel NOR、Serial NOR (Quad-SPI)以及SD 卡。按手册说明除了Jtag之外的启动方式均支持安全启动,使用AES、SHA256加密后的启动代码(不过在勘误里说到,当前硅片版本的无法正常使用secure configuration功能,所以俺就不介绍它鸟) 还是按照时间顺序来介绍下具体流程吧 1、在器件上电运行后,处理器自动开始Stage-0 Boot,也就是执行片内BootROM中的代码。 2、BootROM会初始化CPU和一些外设,以便读取下一个启动阶段所需的程序代码:FSBL (First Stage Bootloader)。 不过这又有一个问题了,之前说到,Zynq支持多种启动设备,BootROM怎么知道从哪个启动设备里去加载FSBL?这就得靠几个特殊的MIO引脚来选择了,具体见下图。 BootROM会去读取MIO[2..8],从而确定启动设备,将选定设备的头192Kbyte内容,也就是FSBL,复制到OCM中,并将控制器交给FSBL。 3、FSBL启动时可以使用整块256Kb的OCM,当FSBL开始运行后,器件就正式由咱自己控制了。Xilinx提供了一份FSBL代码,如果没什么特殊要求,可以直接使用。按照手册说明,FSBL应该完成以下几件事。 使用XPS提供的代码,继续初始化PS(ARM)。 将bitstream写入PL(配置FPGA),不过这一步也可以以后再做。 将接下来启动用的Second Stage Bootloader(SSBL,一般就是U-Boot一类的东西),或者裸奔程序,复制到内存中 跳到SSBL运行去 4、接下来的步骤就没啥特别了,U-boot开始运行,初始化好Linux启动环境,然后开始运行Linux系统。 双核处理器, Board, 程序, 加密, 上电

zynq的启动方式

Zynq-7000AP SOC器件有效利用了片上CPU来帮忙配置。在没有外部JTAG的情况下,处理系统(PS)与可编程逻辑(PL)都必须依靠PS来完成芯片的初始化配置。 ZYNQ的两种启动模式:从BootROM主动启动,从JTAG被动启动。 ZYNQ的启动配置分多级进行的。配置至少需要两步,但通常按如下三个阶段进行: 阶段0:该阶段简称为BootROM,控制着整个芯片的初始化过程。放在BootROM中的代码是固化的,不可修改的,处理器核在上电或者热启动时自动执行这部分代码。 阶段1:该阶段的启动加载器(FSBL)也可以由用户代码控制。 阶段2:这阶段通常可以是用户的PS端的设计代码,当然也可以是第二阶段的启动加载器(SSBL),这个阶段可以完全由用户控制,是可选的。 ZYNQ外部启动条件: 1、电源要求:在阶段0 BootROM状态时,PS与PL的电源要求如表所示: 在阶段1 FSBL时,PS与PL都是必须上电的,因为PL将在这个阶段进行配置,而PS将负责配置的过程。 2、时钟要求:必须满足时钟 3、复位要求:主要有两个外部复位源将影响BootROM的执行。(电源复位信号,系统复位 信号) 4、启动引脚设置:需要配置好引脚才能正确启动平台。 BootROM 1、BootROM的作用:上电复位以后,PS端即开始进行配置。在不使用JTAG的情况下,ARM 将在片上的BootROM中开始执行代码。BootROM中的代码对NAND、NOR、Quad-SPI、SD与PCAP的基本外设控制器进行初始化,使得ARM核可以访问、使用这些外设。而DDR等其他外设将在阶段1或者之后进行初始化。BootROM中的代码还负责加载阶段1的启动镜像。 PS的启动源是由外部模式引脚的高低电平来选择的,也就是指BootROM将根据外部配置引脚的设置来从不同的外部存储中加载阶段1的启动镜像,当然也支持在线性Flash 上直接运行。 需要注意的是PL的配置并不在BootROM中完成,BootROM只为配置PL做好准备。 FSBL 1、FSBL是在BootROM之后启动的引导程序。由BootROM加载到OCM或者直接在线性Flash 上运行。FSBL主要完成以下工作: 1)根据XPS中的配置,完成PS端的初始化。 2)使用比特流文件对PL进行配置 3)加载第二阶段引导程序(SSBL)或者裸跑程序(直接在ARM上运行无操作系统程序)到内存空间。 4)跳转执行SSBL或者裸跑程序。 注意:FSBL在跳转到SSBL或者裸跑程序前,并不使能MMU。这是因为许多操作系统,

Zynq学习笔记(基本设计流程)

Zynq学习笔记(基本设计流程) Zynq Standalone training 1.从“所有程序\xilinxDesign Tools\Vivado 2013.2\启动Vivado2013.2,创建新工程: LED_Controller,RTL Project,verilog,选择part:family:Zynq-7000;package:clg484. (XC7Z020-1CLG484C) 2.点击Flow Navigator/IP Integrator/Create Block Design,建立一个Zynq的框图设计。设计 名为System 3.在框图的上方处,点击Add IP,(可以在Search中加7过滤),选ZYNQ7 Processing System; 4.双击ZYNQ7 Processing System IP模块,打开PS的配置窗口。 ●配置PS的bank电平,bank0:LVCMOS3.3V,bank1:LVCMOS1.8V ●打开Memory Interfaces,配置QSPI。1-6,8(Feedback Clk)。点“+”可以看配置后 的各个参数。 ●点击I/O Peripherals,配置UART1:MIO48..49,Baud Rate配置在PS-PL Configuratin中。 ●勾选USB0,28-39 ●勾选Ethernet0,改EMIO为MIO :16-27,打开“+”,勾选MDIO:52-53 ●添加SD 0 40-45, CD:47, WP:46 ●点开GPIO,勾选GPIO MIO,设置MIO的Direction:50-51为输入,MIO7只能是输 出,其余为输入输出。若看不到,就向右拉移动条。 5.配置PS时钟:CLKIN=33.3333(常用的)。CPU=66 6.6666;DDR_CLK=533.333. CPU Clock Ratio=6:2:1,均为默认值。 设置外设时钟。 QSPI的模块内部有一个2分配的电路,应此想设置他的工作频率为100M,就需要将输入时钟设为200MHz。 SDIO(即SD卡的时钟),设为50MHz。 Ether0:1000MHz。 PL时钟:勾选FCLK_CLK0时钟并设置相应的时钟:100MHz。 6.配置DDR。Enable DDR(打勾)。DDR3, MT41J128M16HA-15E,32BIT(两片拼 接而成), Internal Vref打勾;填写Train/Board Detail,两种方式:一用户直接写;二通过计算。选择“计算”方式,然后点OK,填写各组信号线在PCB 板上的实际长度和Package的数值,相应的Delay参数就计算好了。

ZYNQ的启动原理和配置

ZYNQ的启动原理和配置 启动过程 设备配置包含用于初始化和配置ps和pl的所有方法及过程。在软件控制下,ps内的DevC 提供用于初始化和配置ps和pl的手段和方法,在zynq中提供两个模块用于控制配置过程:BootROM,一个静态存储块器块,当上电复位和暖复位后,有Cortex-A9的CPU执行这个内置程序; 设备配置单元:用于控制JTAG调试访问和提供连接到AES、HMAC和PCAP模块的接口,用于实现对芯片内的pl的配置及数据的解密。 在ps的控制下,可以实现安全或非安全的配置所有ps和pl。通过zynq提供的JTAG接口,用户可以在外部主机的控制下对zynq进行配置,zynq不支持最开始就配置pl的过程。对zynq的配置过程至少包含两个阶段,但是通常要求3个阶段。 阶段0:该阶段也称为BootROM,该阶段控制初始设备的启动。BootROM是上电复位或暖复位后,处理器所执行的用户不可修改的代码,该代码已经固化到zynq的BootROM中;阶段1:在该阶段,通常执行第一级启动引导程序。但是,它也可以是任何用户控制的代码; 在该阶段,通常执行用户自己编写的软件程序,但是,也可以是第二级的启动引导程序,该阶段完全是在用户的控制下实现的。 zynq的BootROM BootROM特性: 提供3种不同的方法,用于配置PS:两个主模式和一个从模式,即安全、加密的镜像、主模式;非安全的主模式;通过JTAG的非安全从模式; 支持4种不同的外部启动源:Quad-SPI Flash、NAND Flash、NOR Flash、SD; 支持使用AES-256和HMAC(SHA-256)的PS安全配置; 支持Soc调试安全性; 从NOR和QSPI芯片内执行配置过程。

如何在zynq上挂linux_第二章

上一章讲到这么一个网页: https://www.360docs.net/doc/f416356413.html,/resources/tools-software/linux-drivers/platforms/zynq 你打开看看,密密麻麻好多英文啊 还有各种链接 本人时间确实有限,简略讲点要紧的部分吧。 这个网页讲了三大部分 1,u-boot,uImage,和dtb文件的编译 2,BOOT.bin的生成 3,UI界面下载和释放 教程第一章有这么一个图: 其实要启动一个linux, 你需要的就是以下四个文件: BOOT.bin devicetree.dtb uImage 和uramdisk.image.gz

BOOT.bin (来自于编译得来的u-boot文件和网页提供的参考设计) devicetree.dtb (编译得来) uImage (编译得来) 和uramdisk.image.gz (教程第一章里已经讲了怎么来的,xilinx网站之直接下载下来就行) 所以,在linux下要编译的是这几个文件: u-boot uImage devicetree.dtb 然后你就需要一台linux的电脑了 VNC接入工作站也行,虚拟机也行,或者你干脆装一台linux。 有两点注意:我试过14.04版的Ubuntu,在解压缩一个zip包的时候会出错,提示文件名过长。 我也试过一个桌面版的RHEL 6.4,结果里面没装GCC,而GCC在编译过程里是必须有的。(查看装没装GCC的办法之一是进/usr/bin看一下有没gcc文件)最后搞成功的是一台装了GCC的RHEL 6.3桌面版。

现在准备下载一堆东西吧 第一样,交叉编译环境安装包 https://www.360docs.net/doc/f416356413.html,/member/mentor_codebench/xilinx-2011.09-50-arm-xilinx-linux-gnueabi.bin 141M大小,去下载吧。 开个迅雷或者QQ炫风的会员会很快的。 第二样,u-boot编译环境 下载页面: https://https://www.360docs.net/doc/f416356413.html,/Xilinx/u-boot-xlnx 点右边的“Download ZIP”就开始下载,然后你可以指定下载目录。 或者直接下载: https://https://www.360docs.net/doc/f416356413.html,/Xilinx/u-boot-xlnx/archive/master.zip 这个zip包下载下来之后会自动重新命名为u-boot-xlnx-master.zip 放进linux之后解压缩 解压命令unzip -o u-boot-xlnx-master.zip 别忘了把这个补丁文件放进解压后的根目录 https://www.360docs.net/doc/f416356413.html,/_media/resources/tools-software/linux-drivers/platforms/uboot-env.patch

zynq启动流程分析

1.纯PL开发,这个和一般的xilinx的FPGA没有很大的区别。 2.纯PS开发, 典型的就是helloworld工程,这个看到了网友的有两种方式。注:这两个方式后面都有相应的实验。 一种是传统的arm的方式,这个可以参考懒兔子博客。 还一种就是xilinx方法,这个是生成一个elf文件,这个elf文件包括了硬件配置信息(xmp),和裸跑程序(c文件)。 3.PS+PL(不跑操作系统)开发,这个可以参考懒兔子博客二,三笔记,生成的elf文件包括了硬件配置信息(xmp),还有裸跑程序(c文件),另外还有一个.bit文件可以看出和纯PS 开发的区别了。 4.PS+PL(跑操作系统)开发,这个就需要BOOT.BIN,设备树,linux内核镜像,文件系统了。其中BOOT.BIN是由3部分组成的(boot.elf,.bit,.fsbl.elf),boot.elf这个是由交叉编译环境产生的,相当于ssbl吧,.bit文件是PL使用产生,fsbl.elf这个就是fsbl吧。 Zynq启动过程简介 1.在器件上电运行后,处理器自动开始Stage-0 Boot,也就是执行片内BootROM中的代码 2.BootROM会初始化CPU和一些外设,以便读取下一个启动阶段所需的程序代码,FSBL(First Stage Bootloader)。 不过这又有一个问题了----之前说到,Zynq支持多种启动设备,BootROM怎么知道从哪个启动设备里去加载FSBL?这就得靠几个特殊的MIO引脚来选择了: BootROM会去读取MIO[2..8],从而确定启动设备,将选定设备的头192Kbyte内容,也就是FSBL,复制到OCM(On Chip Memory)中,并将控制器交给FSBL。 3,FSBL启动时可以使用整块256Kb的OCM,当FSBL开始运行后,器件就正式由咱自己控制了。Xilinx提供了一份FSBL代码,如果没什么特殊要求,可以直接使用。 按照手册说明,FSBL应该完成以下几件事。 1). 使用XPS提供的代码,继续初始化PS 2). 将bitstream写入PL(配置FPGA),不过这一步也可以以后再做 3). 将接下来启动用的Second Stage Bootloader(SSBL,一般就是U-Boot一类的东西),或者裸奔程序,复制到内存中 4). 跳到SSBL运行去 4,接下来的步骤就没啥特别了,Uboot开始运行,初始化好Linux启动环境,然后开始运行Linux系统。 注明:由于自己zedboard还没有开始玩,现在的理解和以后的理解可能又不一样。很多理解粗浅而鄙陋,恳请大家指正,希望大家一起学习进步

zynq_ubuntu桌面系统的建立

UbuntuontheZynq?-7000SoCFeaturingthe Avnet ZedBoard 这个指南提供了一种集合几个不同的技术在一个平台的方法,使用Avnet ZedBoard,我们拥有800Mhz ARM-9 Cortex 32位双核处理芯片,联合Xilinx FPGA 无与伦比的灵活性实施自定义用户系统。我们使用一个Linux内核作为基础操作系统在处理器内核运行,同时添加一个全性能的桌面架构Ubuntu,在根文件系统中控制。这个桌面允许ZedBoard像个人计算机一样工作,使用USB接口的键盘和鼠标,和一个HDMI接口的显示器。 实验1:FPGA硬件平台 1,在网站:https://www.360docs.net/doc/f416356413.html,/resources/fpga/xilinx/kc705/adv7511下找到 cf_adv7511_zed_edk_14_4_2013_02_05.tar.gz链接,下载得到HDL Reference Design,解压并将cf_adv7511_zed和cf_lib拷贝到目录L:\ubuntu_linux下。 2,打开cf_adv7511_zed文件下的system.xmp文件 3,在XPS下,点击Generate BitStream产生syste.bit文件,将在Zynq_Ubuntu\cf_adv7511_zed\implementation\system.bit 4,在xps下,点击左边的SDK Export Design 图标,勾选上include bitstream and BMM files,点击Export and Launch SDK按钮。选择工作区间为l:\ubuntu_linux\ f_adv7511_zed\SDK\SDK_Workspace,ok 5,在SDK下,新建一个应用工程zynq_fsbl_0 选择Zynq FSBL ,finish。将在Zynq_Ubuntu\cf_adv7511_zed\SDK\SDK_Workspace\zynq_fsbl_ 0\Debug\zynq_fsbl_0.elf 6,在zynq_ubuntu目录下新建一个文件夹bootfile,将system.bit文件和zynq_fsbl_0.elf文件都复制到bootfile文件夹下。

Zynq FSBL代码导读

FSBL代码导读 一、main函数执行之前 FSBL模板的代码是跟ISE的版本有关的,我用的是14.3,内容会比14.2版更多一点,但是基本过程是一样的。 板子上电之后,最先执行的并不是FSBL中的main函数,因为这个时候板子还没有初始化,不具备执行C语言的能力,此时只能执行汇编代码,所执行的代码是由BSP提供的。 我们打开zynq_fsbl_bsp——>ps7_cortexa9_0——>libsrc— —>standalone_v3_07_a——>src文件夹,里面有一个asm_vector.S文件,这个文件 声明了一个代码段,位于地址0处。开机之后,PS自动执行地址0处的指令,其第一句话就是一个跳转:B _boot。如下: 于是就跳转到boot.S中执行_boot标号下的代码了,_boot会对系统做初始化,当它执行完后,PS将具备执行C代码的能力,接着在_boot的代码中,再次执行了一个跳转: _start标号位于xil.crt0.S中,仍然对系统进行设置,我们看到,第一句话就是跳转到_cpu_init去执行cpu初始化。代码部分截图如下: 在_start的末尾,BSP终于完成了自己的工作,PS将跳转到main函数开始执行。如下:

二、main函数执行过程 终于系统进入了FSBL阶段。我们打开zynq_fsbl——>src文件夹,然后打开main函数: Main函数首先是一些宏定义,接下来就是执行ps7_int()函数。SDK是一个很智能的工具,图中的灰色阴影部分是SDK判断出了PEEP_CODE这个宏没有定义,所以用灰颜色提示读者这段代码不用执行。 ps7_init函数位于ps7_init.c文件中。这个C文件是由XPS根据用户的配置自动生成的。我们进入ps7_init函数看一下,这个函数很短: 根据代码,很明显可以猜到,ps7_init函数其实执行了mio,pll,clock,ddr和某些外设的初始化。 我们接着看FSBL的main函数,根据XPS自动生成的ps7_init.c执行完初始化之后,FSBL将根据启动状态寄存器判断是采用的哪种启动模式。有四种启动模式,分别是QSPI,NOR,JTAG,SD卡等模式。每种模式都有一段独立的代码,举个例子,我们看SD卡模式的执行代码:

基于ZYNQ的小型密码机及数据加密方法与制作流程

图片简介: 本技术涉及信息安全技术领域,尤其涉及一种基于ZYNQ的小型密码机及数据加密方法。所述密码机采用ZYNQ可编程器件中的ARM处理器运行嵌入式Linux系统,上层应用进行业务数据的处理;采用ZYNQ可编程器件中的FPGA实现各种不同的国密算法;采用专用处理器进行密钥的管理和权限控制;板上提供千兆以太网、USB接口、串口、DDR等板载资源,可实现一个完整的密码机功能。相对于普通加密机具有硬件系统简单、成本和功耗低、高性能等优点。 技术要求 1.一种基于ZYNQ的小型密码机,其特征在于,包括ZYNQ主处理器(1)、 专用处理器(4)和密钥存储器(5),所述ZYNQ主处理器(1)包括ARM处 理器(2)和FPGA(3),所述ARM处理器(2)与FPGA(3)通过片内高速 总线连接,所述FPGA(3)与专用处理器(4)通过总线复用连接,所述专用 处理器(4)与密钥存储器(5)连接; 所述ARM处理器(2),其运行嵌入式Linux系统进行业务的调度和管 理,用于根据接收到的业务请求包进行相应运算,并将经运算的业务请求包 发送给FPGA; 所述FPGA(3),用于根据业务请求包向专用处理器(4)进行密钥权限 验证,当验证通过时通过预定加密算法对业务数据进行加密处理,将加密处 理的业务数据通过ARM处理器(2)返回给请求方;

所述专用处理器(4),用于实现信息密钥的管理和权限控制,根据业 务请求包进行权限验证; 所述密钥存储器(5),用于以密文形式存储密钥。 2.根据权利要求1所述一种基于ZYNQ的小型密码机,其特征在于, 所述ARM处理器(2)当收到业务请求包时,运行于Linux上的应用程序对 业务请求包进行解析,将业务数据和相应的命令码按照约定好的顺序进行组合,发送至FPGA,数据传输完成后向FPGA内部寄存器写入完成标识;ARM 处理器(2)在收到FPGA发送的中断后读取FPGA内的运算结果,组织数据, 将结果返回给请求方。 3.根据权利要求2所述一种基于ZYNQ的小型密码机,其特征在于, 所述FPGA(3)其内部例化一个双口RAM,第一接口通过片内高速总线与ARM 处理器(2)互联,第二接口专用处理器(4)互联;当逻辑检测到内部寄存 器被ARM处理器写入完成标识后,发送中断给专用处理器(4),表明FPGA 内部有待处理数据,请求相应的权限进行操作,当接收到处理器(4)反馈 的权限验证通过时,调用相应的算法进行运算,将运算结果写入到双口RAM 中,产生中断通知ARM处理器已经完成运算。 4.根据权利要求3所述一种基于ZYNQ的小型密码机,其特征在于,所 述专用处理器(4)接收到FPGA发送的中断后读取FPGA内双口RAM的数据,根据相应的命令码判断是否为合法数据,是否有权限进行运算,如果为合法数据且有权限则通知FPGA启动算法运算,否则返回错误码。 5.根据权利要求3任一项所述一种基于ZYNQ的小型密码机,其特征在 于,还包括算法专用芯片(6),所述FPGA的第二接口通过总线复用与算法 专用芯片(6)和专用处理器(4)互联,所述算法专用芯片(6)和专用处 理器(4)均可通过复用总线对FPGA的双口RAM进行数据读写,所述算法专 用芯片(6)实现SM1加密算法,并与FPGA中的加密算法配合对业务数据进 行加密。

XilinxVivadozynq7000入门笔记剖析

IP Integrator flow 1.创建RTL工程 2.创建IP Integrator Block Design 3.添加zynq 处理器 ip中搜索zynq,添加zynq7 Processing System,其中的BFM版本为先前的IP处理器版本。鼠标右键点击FIXED_IO和DDR接口,选择make external,连接到芯片外部。但此时处理是完全未经过配置的,双击处理器进行配置。 自动添加的外部接口:(参考ug585文档) FIXED_IO, 是专用的内部固化的外设IO,作用? 54个MIO口, DDR_VRN,DDR_VRP: DDR DCI voltage reference pins, refer to UG933, Zynq-7000 AP SoC PCB Design and Pin Planning Guide. PS_SRSTB: Debug system reset, active Low. Forces the system to enter a reset sequence. PS_CLK: System reference clock PS_PORB: Power on reset, active low DDR接口,处理器ddr内存寻址接口; M_AXI_GP0_ACLK, M_AXI_GP0,在PS-PL Configuration中可取消对GP Master AXI Tnterface的选择 FCLK_CLK0:PL Pabric Clocks,不使用可在Clock Configuration 中disable。 FCLK_RESET0_N:时钟复位使能,可在General中disable 。 4.配置processing System, 配置处理器内部控制模块的详细功能与特性查看:Soc Technical Reference manual https://www.360docs.net/doc/f416356413.html,/support/documentation/user_guides/ug585-Zynq-7000-TRM.pdf 通用配置: (1)MIO配置:Bank0与Bank1分区的IO对应FPGA处理器可配置的IO,由硬件决定电平还是芯片已经指定电平?由硬件决定。 UART1映射到MIO[48:49] zedboard Bank 0 IO Voltage:LVCMOS 3.3V zedboard Bank 1 IO Voltage:LVCMOS 1.8V zedboard PS与PL电源部分是完全独立,但是无论什么时候有PL电源供电就必须有PS电源供电。

Zynq7000启动流程介绍

Zynq7000启动流程介绍 打了半天。。。一不小心碰到鼠标后退键,啥都木了。。。再来吧 一开始呢,我以为Zynq7000是一个加上了双核A9处理器的FPGA芯片。但是看了资料后,才发现,其实不是这么回事 Zynq7000就如同他的名字一样,Zynq-7000 Extensible Processing Platform,是一个可扩展处理平台,简单说就是有个FPGA做外设的A9双核处理器。 所以,它的启动流程自然也和FPGA完全不同,而与传统的ARM处理器类似。 Zynq7000支持从多种设备启动,包括Jtag, NAND, parallel NOR, Serial NOR (Quad-SPI), 以及SD卡。按手册说明除了Jtag之外的启动方式均支持安全启动,使用AES、SHA256加密后的启动代码(不过在勘误里说到,当前硅片版本的无法正常使用secure configuration功能,所以俺就不介绍它鸟) 还是按照时间顺序来介绍下具体流程吧 1.在器件上电运行后,处理器自动开始Stage-0 Boot,也就是执行片内BootROM中的代码 2.BootROM会初始化CPU和一些外设,以便读取下一个启动阶段所需的程序代码,FSBL(First Stage Bootloader)。 不过这又有一个问题了----之前说到,Zynq支持多种启动设备,BootROM怎么知道从哪个启动设备里去加载FSBL?这就得靠几个特殊的MIO引脚来选择了,具体见下图 BootROM会去读取MIO[2..8],从而确定启动设备,将选定设备的头192Kbyte内容,也就是FSBL,复制到OCM中,并将控制器交给FSBL,。 3,FSBL启动时可以使用整块256Kb的OCM,当FSBL开始运行后,器件就正式由咱自己控制了。Xilinx 提供了一份FSBL代码,如果没什么特殊要求,可以直接使用。 按照手册说明,FSBL应该完成以下几件事。 1). 使用XPS提供的代码,继续初始化PS

一文教你如何玩转Zynq平台

一文教你如何玩转Zynq平台 经过这几年的市场磨砺,Zynq-7000 FPGA SoC器件平台在开发者中的认知度和接受度越来越高,这种“ARM处理器+可编程逻辑”的创新架构,可以帮助开发者在设计中找到高性能与灵活性的完美平衡,对此大家也心知肚明。 但是在实际的应用中,想要玩转Zynq这种“异构”平台,并非信手拈来这样简单。其中很大的一个原因就是以往的开发工具都是彼此分立且松散连接的,设计和实现效率不高,因此需要一种全新的设计方法和开发工具来支持Zynq的应用开发。 Xilinx推出的Vivado设计套件恰好能够满足这一需求。Vivado是一种以IP和系统为中心、支持7系列以及更新系列器件的(包括7系列FPGA、Zynq-7000 AP SoC、UltraScale / UltraScale Plus FPGA、Zynq US+ MPSoC等)全新集成开发环境,可解决用户在系统级集成和实现过程中常见的生产力瓶颈问题。Vivado目前最新的HLx版本可为设计团队提供实现基于C的设计、重用优化、IP子系统复用、集成自动化以及设计收敛加速所需的工具和方法,结合UltraFast高层次生产力设计方法,可帮助设计人员以高层次抽象形式开展工作,加速高层次设计、验证和实现。 图1,Zynq全可编程平台设计开发流程 在近日举办的安富利MiniZed Speedway培训活动中,一个重要的议程就是:如何帮助开发者使用Vivado设计套件创建一个符合用户设计需求的Zynq-7000硬件平台。 与传统的处理器不同,Zynq平台的处理器系统(PS)包含一系列常用的外设资源(如I2C、UART、CAN、GPIO、SPI、USB 2.0、Ethernet MAC、SDIO等)以及多端口DRAM Controller (可支持DDR2、DDR3/3L或LPDDR2颗粒组成一个16-bit或32-bit的存储器系统)。而且,PS通过专用的端口可以直接和可编程逻辑(PL)进行通信和数据共享,使用PL可以创建用户自定义IP,扩展PS的外设和处理能力。虽然说PS可以在没有任何PL编程的情况下使用,但是为了充分利用PL中的软IP资源,或者完成PS特定的外设与PL器件引脚间的连接布线,对PL的编程还是必要的。这也是Zynq平台硬件设计不同于和优于传

Zynq开发流程的捷径SDSoC

Zynq开发流程的捷径SDSoC 之前我们已经向大家介绍了全可编程的Zynq SoC平台应用开发所需的一系列神器,如Vivado、Xilinx SDK、PetaLinux等。那么这是否意味着在Zynq开发的过程中就会是一马平川呢? 让我们先来看看一个典型的Zynq SoC开发流程(如图1):开发者首先需要对软硬件进行分区,即确定系统哪些部分放入PL(可编程逻辑)中进行硬件加速,哪些部分在PS(处理器系统)中用软件实现;接下来,要完成软/硬件之间的连接,包括使用怎样的DataMover、PS与PL之间的接口如何配置等;之后要完成配套的软件驱动和应用程序的开发。 整个流程通常需要一个完整团队的通力合作,并不简单。而且,开发工作本身就是一个探索性的过程,很多情况下上述所有设计工作完成之后人们才发现,系统在吞吐量、延迟或面积等方面还需要进一步的优化,这就意味着软硬件区分硬件架构搭建驱动和应用软件开发整个流程要重新来过。如此经过多次迭代,才能获得一个令人满意的设计方案。而因此却可能造成开发周期的不可控,严重拖延TIme-To-Market。这无疑是一个很大的挑战。 图1,传统的Zynq SoC开发流程 那么Zynq开发流程,有没有捷径可走呢?Xilinx给出的答案是:有!这个捷径就是SDSoC。SDSoC是Xilinx推出的一个基于简便易用的Eclipse集成设计环境(IDE)的工具套件,它支持Zynq-7000全可编程SoC和Zynq UltraScale+ MPSoC,以及MicroBlaze处理器,可以为开发者提供类似嵌入式C/C++/OpenCL 应用的开发体验。 如果感觉上面的描述比较抽象,那就让我们来看看使用SDSoC对Zynq开发流程的影响和改变(如图2)。应用SDSoC之后,工具可以自动搭建软硬件之间的通讯部分,包括DataMover、软件驱动程序和硬件连接接口,还可以将整个开发过程抽象到C/C++的应用层面,让开发者以C/C++为起点来进行算法开发。 在进行系统软件/硬件划分时,用户仅需在图形化界面中用鼠标单击指定那些需要进行硬件加速的模块即可。而在将设计应用到Zynq系统上之后,如果发现性能不达标,可以使

基于ZYNQ芯片的外设驱动技术方案

一、BootLoader的移植制作 (2) 1、生成uboot.elf文件 (3) 2、system.bit生成 (5) 3、创建fsbl (8) 4、生成BOOT.BIN (9) 二、配置并编译linux内核 (10) 1、修改设备树内容 (10) 2、配置编译linux内核 (12) 三、Linux设备驱动移植 (14) 1、Linux设备驱动模型 (14) 2、Linux设备驱动移植 (15)

在嵌入式操作系统中,BootLoader是在操作系统内核运行之前运行。可以初始化硬件设备、建立内存空间映射图,从而将系统的软硬件环境带到一个合适状态,以便为最终调用操作系统内核准备好正确的环境。在嵌入式系统中,通常并没有像BIOS那样的固件程序(注,有的嵌入式CPU也会内嵌一段短小的启动程序),因此整个系统的加载启动任务就完全由BootLoader来完成。在一个基于zynq的嵌入式Linux系统中,系统在上电或复位时通常都从地址0x00000000处开始执行,而在这个地址处安排的通常就是系统的BootLoader程序。 想要在zynq芯片上顺利启动Linux并且驱动相关模块正常工作,首先需要正确移植BootLoader。作为初始化硬件平台的一段Bare Metal代码,Bootloader的移植也并入了我们的工作。所以综合起来说,我们的工作主要分为了三个部分:Bootloader的移植以及Linux内核和设备驱动的移植。 在进行移植工作之前,首先要做的是要在宿主机上面搭建好我们目标板的开发平台,以及下载好uboot源代码,Linux内核源代码以及相关驱动源代码。(有的模块的驱动源代码在Linux内核源代码中已经包含进去了,那么就不用单独下载。需要下载的驱动源代码只是针对标准Linux内核中不支持的部件而言。) 一、BootLoader的移植制作 每一种操作系统都需要有自己的引导程序,最为人们所知的就是Windows 的BIOS。缺失了这一部分,系统将无法正常启动。对比与Windows的BIOS,android系统拥有自己的专属的BootLoader,它主要负责初始化系统平台的硬件设备,建立内存空间的映射关系。在它完成初始化工作之后,继续负责把内核镜像和yaffs2格式的文件系统从SD卡载入到RAM中,完成Linux内核和文件系统的加载并设置内核的启动参数,紧接着启动内核。等到内核真正启动了之后,BootLoader就杀死自己,把CPU让出给内核使用。之后内核根据硬件环境做出系统初始化设置,并将CPU转让给yaffs2文件系统运行管理。至此,Linux系统成功的启动起来。下图1为bootloader的启动过程。

Miz-7020-uboot笔记

u-boot启动过程中如下流程:

start.S代码分析: start.S中一个比较重要的全局变量_TEXT_BASE定义如下: .globl_TEXT_BASE _TEXT_BASE: .word CONFIG_SYS_TEXT_BASE 其中CONFIG_SYS_TEXT_BASE定义在zynq_common.h中,而zynq_zed.h 包含了该头文件, #define CONFIG_SYS_TEXT_BASE 0x04000000 _TEXT_BASE的地址为0x04000000,也就是DDR的起始地址。 .globl _bss_start_ofs _bss_start_ofs: .word __bss_start - _start 上述代码定义bss起始地址偏移量,其中__bss_start的值在u-boot.lds 中获取,start在start.S中启动的第一个函数。 .global _image_copy_end_ofs _image_copy_end_ofs: .word __image_copy_end - _start 上述代码定义_image_copy_end_ofs起始地址偏移量 .globl _bss_end_ofs _bss_end_ofs: .word__bss_end__ - _start 上述代码定义bss结束地址偏移量

.globl _end_ofs _end_ofs: .word _end - _start 上述代码定义全部代码偏移量,其中_end的值在u-boot.lds中获取。/* IRQ stack memory (calculated at run-time) */ .globl IRQ_STACK_START IRQ_STACK_START: .word0x0badc0de 上述代码设置IRQ堆栈。 /* IRQ stack memory (calculated at run-time) */ .globl FIQ_STACK_START FIQ_STACK_START: .word0x0badc0de 上述代码设置FIQ堆栈。 /* IRQ stack memory (calculated at run-time) + 8 bytes */ .globl IRQ_STACK_START_IN IRQ_STACK_START_IN: .word0x0badc0de bl cpu_init_cp15 bl cpu_init_crit

详细解读Zynq的三种启动方式(JTAG,SD,QSPI)

详细解读Zynq的三种启动方式(JTAG,SD,QSPI) 本文介绍zynq上三种方式启动文件的生成和注意事项,包括只用片上RAM (OCM)和使用DDR3两种情况。 JTAG方式 JTAG方式是调试中最常用的方式,在SDK中在Project Explorer窗口工程上右键-Debug As-Debug ConfiguraTIons可以看到以下窗口 首次打开左边窗口中Xilinx C/C++ applicaTIon(GDB)下没有子项,这时双击Xilinx C/C++ applicaTIon(GDB)即可新建一个调试;这时右边窗口会自动填充如上图,若没有则手动填入;在右边ApplicaTIon窗口指定要下载调试的.elf文件;在右边STDIO Connection可以指定标准输入输出串口,即printf打印串口,若这里选择开发板上uart的com口,则调试时printf的信息打印到调试时Console窗口,同时也可从Console窗口输入数据,以此将数据通过串口发送到开发板上以上设置完成后点击Debug即可开始调试;若以上在Project Explorer窗口工程上右键-Run As-Run Configurations;配置与此类似,最后点击run即可开始运行,只是不是调试而是直接上板运行。 只用OCM 只用OCM指不使用DDR3的方式,与使用DDR3的方式略有不同。这里不用FSBL来加载PL部分的.bit文件和第二阶段启动程序(裸机程序),而直接用BootROM加载裸机程序到OCM,即将裸机程序当做FSBL来运行,当然还要以下处理才可以:包含进头文件:#include ps7_init.h在裸机程序main函数开始处调用:ps7_init()从design_1_wrapper_hw_platform_1目录复制ps7_init.c和ps7_init.h文件到裸机程序所在的src目录中 注意:这里样调用ps7_init()只适用于只用OCM的情况,经测试打开DDR3后再这样调用会在ps7_init()中初始化失败,调试发现在初始化PLL时失败(原因未知)。

ZYNQ实验手册

Lab1 zybo standalone控制GPIO和传感器 一、实验目的 学会使用zybo进行SDK编程,点亮LED,驱动DS18B20传感器测量温度,使用Uart进行输出。 二、实验原理介绍 本次实验将使用已经预先生成完的Bitstream文件,该硬件比特中包含了5路GPIO(分别接在LED0、LED1、SW0、SW1和JC7)、Uart和4路PWM。 三、实验步奏 (1)打开SDK,将工程目录选到ZYNQ_Workshop文件夹下,点击OK。 (2)选择file->Import->General->Existing Projects into Workspace,点击Next; 将路径选择到ZYNQ_Workshop\Led.sdk,点击Finish。

(3)SDK工程被打开,包含了Lab1、Lab1_bsp和system_wrapper_hw_platform_0三个工程,其中Lab1为应用程序,Lab1_bsp为自动生成的Board Support Package, system_wrapper_hw_platform_0为导出到SDK的硬件工程。

(4)实验的应用程序主程序在Lab1->src下的helloworld.c中。 (5)程序相当简单,在Gpio初始化设置后,在while(1)循环中对LED进行控制后,读取ds18b20传感器数据,并通过串口输出温度值。 (6)下载硬件比特。选择菜单栏的Xilinx Tools->Program FPGA选项。

在弹出的对话框中确认下载的硬件比特后,点击Program。 (7)等待完成后LD10会亮起,表示FPGA硬件工程已经被下载了。下一步进行软件下载,先选择菜单栏Project->Build All(或者使用Ctrl+B快捷键),工程开始build。

z-turn开发笔记

Z-turn开发笔记 1、Zynq启动配置 1.1 时钟要求 器件启动时拥有了稳定的电压后,还必须保证PS_PORT_B引脚拉高前,PS_CLK已经有稳定的时钟输入,通常PS_CLK采用33.3Mhz和50MHz的时钟。 ZYBO:50MHz Z-turn: 33.3MH 1.2复位要求 PS_POR_B:这个复位保持PS在复位状态,直到所有PS的供电达到了所有的要求。在PS上电之前,必须为低。PS_POR_B由供电器件“Power-Good”信号提供。 PS_SRST_B:这个复位用于强制系统复位。它能被连接或者拉高,当在PS供电斜坡阶段,该信号为高。 1.3模式引脚配置 五个模式引脚,mode[4:0]用于表示启动源,用于JTAG模式和PLL旁路选择。两个电压模式引脚vmode[1:0],用于表示复用I/O组的电压模式。使用20K欧的上拉或者下拉电阻连接mode[4:0]和vmode[1:0]信号。 当ROM运行时,vmode信号用来设置各个MIO_PIN寄存器,为所有的MIO 引脚设置合适的LVCMOS18或者LVCMOS33 I/O标准。当完成BootROM后,在需要的时候,FSBL可以将I/O的标准从LVCMOS修改为HSTL或者LVTTL。Vmode[0]引脚用于设置第0组。。。。。 当PS_POR_B复位信号从低到高变化时,对mode和vmode信号采样三个PS_CLK时钟。当在上电复位采样时,将采样的模式值保存到SLCR内的BOOT_MODE寄存器中。vmode的值保存在GPIOB_DRVR_BIAS_CTRL。 模式引脚是MIO[6:2],vmode引脚是MIO[8:7],引脚使用如下: MIO[2]表示JTAG模式; MIO[5:3]选择启动模式; MIO[6]是能PLL; MIO[8:7]配置I/O组电压。