基于DDS的数字移相信号发生器

光电与通信工程学院《EDA》课程设计报告

课设名称:基于DDS的数字移相信号发生器年级专业及班级:

姓名:

学号:

组别:

指导教师:

厦门理工学院光电与通信工程学院

2014年6月

一、课程设计目的

1、进一步熟悉QuartusⅡ的软件使用方法;

2、熟悉利用VHDL设计数字系统并学习LPM ROM的使用方法;

3、学习FPGA硬件资源的使用和控制方法;

4、掌握DDS基本原理,学习利用此原理进行信号发生器的设计。

二、设计任务

1、完成8位输出数据宽度的频率可调的移相正弦信号发生器。

2、完成8位输出数据宽度的频率可调的移相三角波、方波信号发生器。

3、以上三种波形使用一个按键依次切换。

4、波形发生器实现幅度可调。

5、在显示某种波形时,将相关波形的特征值存入存储器中。(信号发生器的原始

数据存储在外部存储器里,由FPGA进行读取)

6、完成两路相位相差90度的频率幅度可调的移相信号发生器。(包括正弦波、

方波、三角波)

注意:以上前5点为基本要求,第6点为提高要求。

三、实验设备

EDA最小系统板一块或EDA6000实验箱一台、PC机一台、示波器一台

四、DDS工作原理

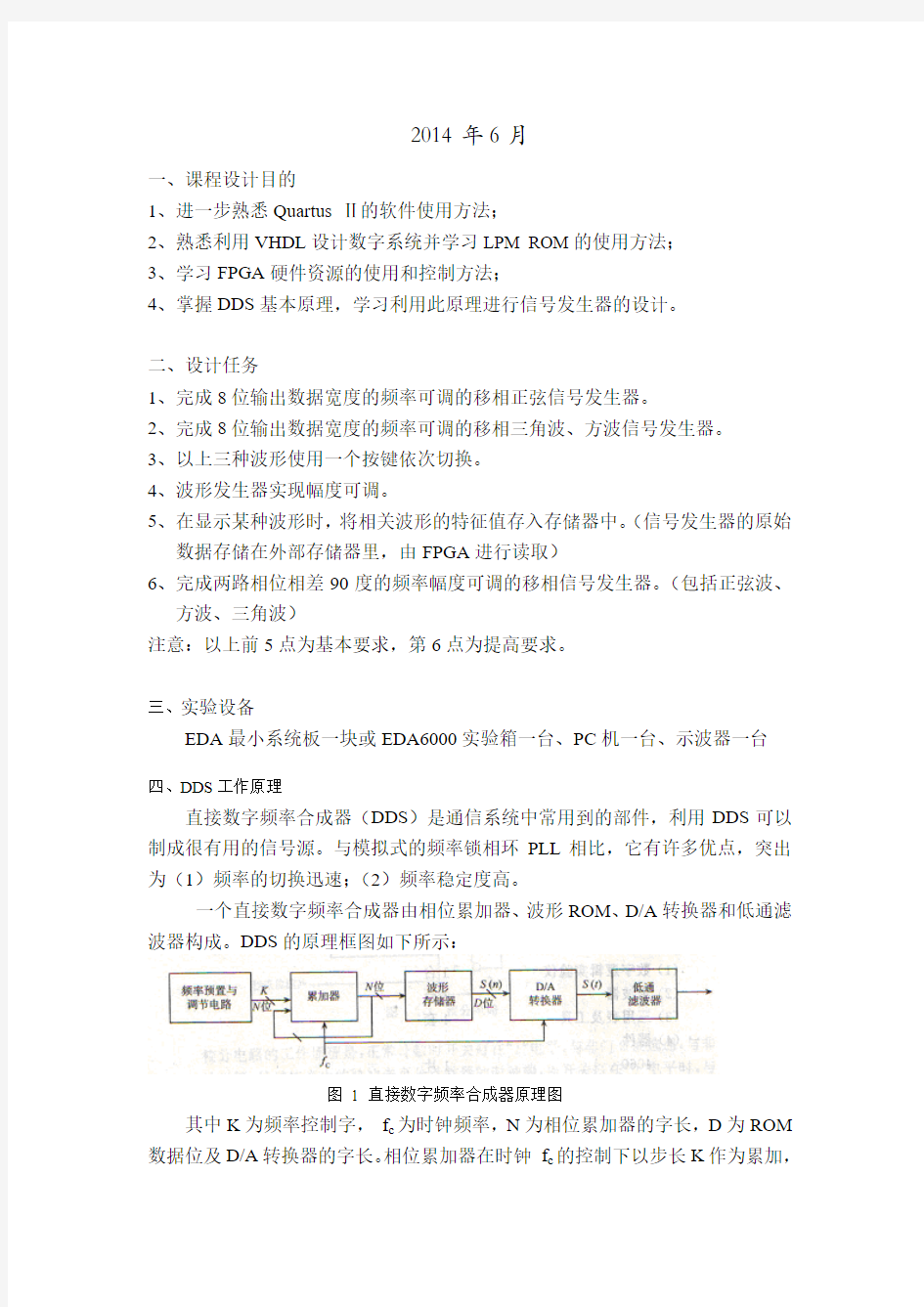

直接数字频率合成器(DDS)是通信系统中常用到的部件,利用DDS可以制成很有用的信号源。与模拟式的频率锁相环PLL相比,它有许多优点,突出为(1)频率的切换迅速;(2)频率稳定度高。

一个直接数字频率合成器由相位累加器、波形ROM、D/A转换器和低通滤波器构成。DDS的原理框图如下所示:

图1 直接数字频率合成器原理图

其中K为频率控制字,f c为时钟频率,N为相位累加器的字长,D为ROM 数据位及D/A转换器的字长。相位累加器在时钟f c的控制下以步长K作为累加,

输出N位二进制码作为波形ROM的地址,对波形ROM进行寻址,波形ROM 输出的幅码S(n)经D/A转换器变成梯形波S(t),再经低通滤波器平滑后就可以得到合成的信号波形了。合成的信号波形形状取决于波形ROM中存放的幅码,因此用DDS可以产生任意波形。本设计中直接利用D/A转换器得到输出波形,省略了低通滤波器这一环节。

1、频率预置与调节电路

不变量K被称为相位增量,也叫频率控制字。DDS方程为:f0= f c K/2n,f0为输出频率,f c为时钟频率。当K=1时,DDS输出最低频率(也既频率分辩率)为f c /2n

DDS的最大输出频率由Nyguist 采样定理决定,即f c /2,也就是说K的最大值为2n-1.因此,只要N足够大,DDS可以得到很细的频率间隔。要改变DDS的输出频率,只要改变频率控制字K即可。

2、累加器

相位累加器的原理图如下图

图2 相位累加器原理图

相位累加器由N为加法器与N位寄存器级联构成。每来一个时钟脉冲f c,加法器将频率控制字与寄存器输出的累加相位数据相加,再把相加后的结果送至寄存器的数据输入端,寄存器将加法器在上一个时钟作用后所产生的下数据反馈到加法器的输入端;以使加法器在下一个时钟作用下继续频率控制字进行相加。这样,相位累加器在时钟的作用下,进行相位累加,当相位累加器累加满量时,就产生一次溢出,完成一个周期性的动作,这个周期应为u k= 2n / GCD(2N ;k),其中GCD表示最大公约数。

3、波形存储器

用相位累加器输出的数据作为波形存储器的取样地址进行波形的相位——幅值转换,即可在给定的时间上确定输出的波形的抽样幅值。N位的寻址ROM 相当于把00--- 3600 的正弦信号离散成具有2n样值的序列,若波形ROM有D位数据位,则2n个样值的幅值以D位二进制数值固化在ROM 中,按照地址的不同可以输出相宜相位的正弦信号的幅值。相位----幅值变换原理图如下所示。

图3 相位-幅度变换原理图

4、D/A转换器

D/A转换器的作用是把已经合成的正弦波的数字量转换成模拟量,正弦幅度量化序列S(n)经D/A转换后变成了包络为正弦波的阶梯波S(t),S(t)的周期需要注意的是,频率合成器对D/A转换器的分辨率有一定的要求,为T=uk*T c.

。

D/A转换器的分辨率越高,合成的正弦波S(t)台阶数就越多,输出波形的精度也就越高。

五、DDS的逻辑电路图

六、结果波形

七、程序

加法器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY SUM IS

PORT(K : IN STD_LOGIC_VECTOR( 2 DOWNTO 0);

CLK : IN STD_LOGIC;

RST : IN STD_LOGIC;

WR : OUT STD_LOGIC;

CS : OUT STD_LOGIC;

OPT : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); ONT : OUT STD_LOGIC_VECTOR(14 DOWNTO 0));

END ENTITY SUM;

ARCHITECTURE BEHA V OF SUM IS

SIGNAL TEM : STD_LOGIC_VECTOR(10 DOWNTO 0); BEGIN

PROCESS(CLK ,RST)

BEGIN

IF RST = '1' THEN

TEM<= "00000000000";

ELSIF CLK'EVENT AND CLK='1' THEN

TEM <= TEM + K +1;

END IF;

END PROCESS;

OPT <= TEM(10 DOWNTO 3) ;WR <= '0'; CS <= '0';

END ARCHITECTURE BEHA V;

寄存器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY ADDRESS IS

PORT ( D :IN STD_LOGIC_VECTOR(9 DOWNTO 0);

CLK :IN STD_LOGIC;

Q :OUT STD_LOGIC_VECTOR(14 DOWNTO 0)); END ENTITY ADDRESS;

ARCHITECTURE GOD OF ADDRESS IS

BEGIN

PROCESS (CLK)

BEGIN

IF CLK'EVENT AND CLK='1' THEN

Q<= "00000" & D;

END IF;

END PROCESS;

END GOD;

控制器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CONTROL IS

PORT(WRI : OUT BIT;

CLK : IN STD_LOGIC;

WRRD: IN STD_LOGIC;

RD : OUT BIT;

A: IN STD_LOGIC_VECTOR(14 DOWNTO 0);

AA: OUT STD_LOGIC_VECTOR(14 DOWNTO 0);

QQIO : INOUT STD_LOGIC_VECTOR(7 DOWNTO 0);

QQ : IN STD_LOGIC_VECTOR(7 DOWNTO 0));

END ENTITY CONTROL;

ARCHITECTURE BEHA V1 OF CONTROL IS

SIGNAL FLAG:BIT;

BEGIN

PROCESS(CLK)

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF FLAG='1' THEN

AA <= A;

WRI<=FLAG;RD<=NOT FLAG;

QQIO<= QQ;

elsIF FLAG='0' THEN

AA <= A;

WRI<=FLAG;RD<=NOT FLAG;

END IF;

END IF;

END PROCESS;

PROCESS(WRRD)

BEGIN

IF WRRD'EVENT AND WRRD='1' THEN

FLAG<=NOT FLAG;

END IF;

END PROCESS;

END ARCHITECTURE BEHAv1;

三角波信号发生器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY REG IS

PORT ( D :IN STD_LOGIC_VECTOR(7 DOWNTO 0);

SCW: IN STD_LOGIC;

CLK :IN STD_LOGIC;

Q :OUT STD_LOGIC_VECTOR(9 DOWNTO 0)); END ENTITY REG;

ARCHITECTURE BEHA V OF REG IS

SIGNAL AD :STD_LOGIC_VECTOR(9 DOWNTO 0); SIGNAL FLAG:STD_LOGIC_VECTOR(1 DOWNTO 0); BEGIN

PROCESS(SCW)

BEGIN

IF SCW'EVENT AND SCW='1' THEN

FLAG <= FLAG + 1;

END IF;

END PROCESS;

PROCESS(FLAG)

BEGIN

CASE FLAG IS

WHEN "00"=>AD<="0000000000";

WHEN "01"=>AD<="010*******";

WHEN "10"=>AD<="1000000000";

WHEN OTHERS=>NULL;

END CASE;

END PROCESS;

PROCESS (CLK)

BEGIN

IF CLK'EVENT AND CLK='1' THEN

Q<=D + AD;

END IF;

END PROCESS;

END ARCHITECTURE BEHA V;

波形选择器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY CHOOSE IS

PORT(

SCW:IN STD_LOGIC_VECTOR(1 DOWNTO 0);

D1: IN STD_LOGIC_VECTOR(7 DOWNTO 0);

D2: IN STD_LOGIC_VECTOR(7 DOWNTO 0);

D3: IN STD_LOGIC_VECTOR(7 DOWNTO 0);

Q :OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END CHOOSE;

ARCHITECTURE BEHA V OF CHOOSE IS

BEGIN

PROCESS(SCW)

BEGIN

CASE SCW IS

WHEN "00"=>Q<=D1;

WHEN "01"=>Q<=D2;

WHEN "10"=>Q<=D3;

WHEN OTHERS=>NULL;

END CASE;

END PROCESS;

END BEHA V;

调幅

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY AM IS

PORT(SCA : IN STD_LOGIC_VECTOR(1 DOWNTO 0);

K : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

Q : OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END AM;

ARCHITECTURE BEHA V OF AM IS

BEGIN

PROCESS(SCA)

BEGIN

CASE SCA IS

WHEN "00" => Q <= K;

WHEN "01" => Q <= '0' & K(7 DOWNTO 1);

WHEN "10" => Q <= "00" & K(7 DOWNTO 2);

WHEN "11" => Q <= "000" & K(7 DOWNTO 3);

END CASE;

END PROCESS;

END BEHA V;

八、心得体会