第4章锁相环的原理和应用10教程文件

锁相环原理

锁相环原理一、锁相环是什么?锁相环是一种利用相位同步产生电压,去调谐压控振荡器以产生目标频率的负反馈控制系统。

锁相环就是通过负反馈控制系统,让压控振荡器的固有振荡频率fo 和输入的参考信号fi 的相位保持在误差允许范围内,从而让振荡频率fo达到和参考信号fi 同步相位频率的目的。

一般来说,参考信号fi 的信号特性更好,通过锁相系统提高振荡频率fo的信号特性,同时还可以将参考信号fi 转化为你想要的任意(最好整数倍)频率信号。

二、基本理论1.工作原理最基础的锁相环系统主要包含三个基本模块:鉴相器(Phase Detector:PD)、环路滤波器(L00P Filter:LF)其实也就是低通滤波器,和压控振荡器(Voltage Controlled Oscillator:VCO)。

有了这三个模块的话,最基本的锁相环就可以运行了。

但我们实际使用过程中,锁相环系统还会加一些分频器、倍频器、混频器等模块。

(这一点可以类比STM32的最小系统和我们实际使用STM32的开发板)我们从锁相系统开始运行的那一刻进行分析,这个时候鉴相器有两个输入信号,一个是输入的参考信号Vin,另一个是压控振荡器的固有振荡信号Vout。

这个时候由于两个信号的频率不相同,会因为频差而产生相位差,如果不对压控振荡器进行任何操作,那么相位差会不断累积,从而跨越2Π角度,从零重新开始测相位,如图3所示。

这便是测量死区,明明相位在不断变大,但鉴相器只能测出0~2Π的范围,测出的相位差最大便是2Π,这样就导致了鉴相器的输出电压只能在一定的范围内波动。

理想状态是让这两个信号的相位差一直保持在2Π的范围内,不进入测量死区。

那么在系统刚开始的时候,鉴相器测出两个信号的相位差,将相位差时间信号转化为误差电压信号输出(具体转化过程见鉴相器讲解)。

通过环路滤波器转化为压控电压加到压控振荡器上,使压控振荡器的输出频率Vout逐步同步于输入信号Vin,直到两个信号的频率逐渐同步,相位差也在测量误差范围内,那么整个系统就稳定下来了。

锁相环的组成和原理及应用

锁相环的组成和原理及应用一.锁相环的基本组成许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环路是一种反馈控制电路,简称锁相环(PLL)。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

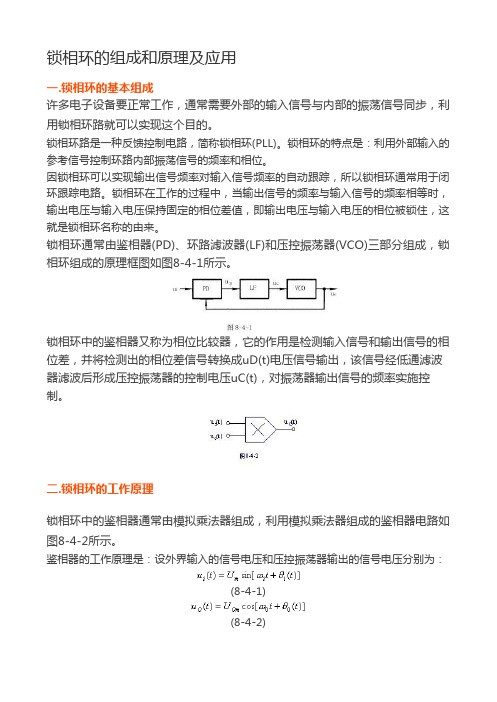

锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,锁相环组成的原理框图如图8-4-1所示。

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压uC(t),对振荡器输出信号的频率实施控制。

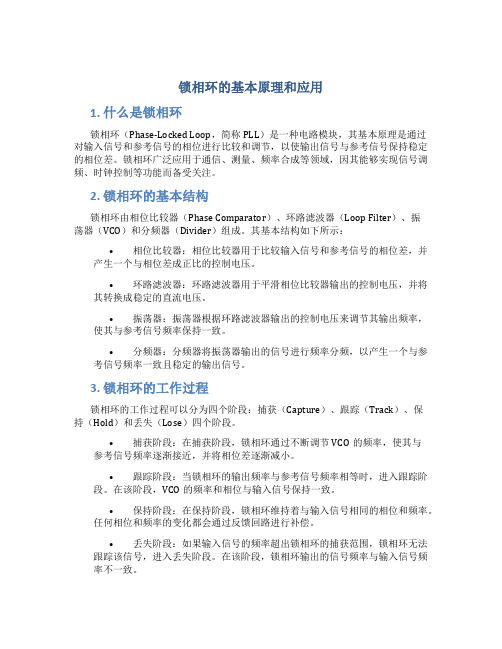

二.锁相环的工作原理锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图8-4-2所示。

鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为:(8-4-1)(8-4-2)式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。

则模拟乘法器的输出电压uD为:用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压uC(t)。

即uC(t)为:(8-4-3)式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为:即(8-4-4)则,瞬时相位差θd为(8-4-5)对两边求微分,可得频差的关系式为(8-4-6)上式等于零,说明锁相环进入相位锁定的状态,此时输出和输入信号的频率和相位保持恒定不变的状态,uc(t)为恒定值。

锁相环工作原理

锁相环工作原理锁相环是一种用于控制信号频率和相位的电路。

它在许多应用中被广泛使用,例如通信系统、雷达、无线电和音频设备等。

锁相环能够将输入信号的频率和相位与参考信号进行比较,并通过反馈控制的方式来调整输出信号,使其与参考信号保持同步。

锁相环的基本组成部分包括相位比较器、低通滤波器、电压控制振荡器(VCO)和分频器。

下面将详细介绍每个部分的工作原理。

1. 相位比较器(Phase Detector):相位比较器是锁相环的核心部分,它用于比较输入信号和参考信号的相位差。

常见的相位比较器有边沿比较器和乘法器。

当输入信号和参考信号的相位差为零时,相位比较器输出的电压为零。

如果相位差不为零,相位比较器会输出一个电压,该电压的大小和相位差的大小成正比。

2. 低通滤波器(Low Pass Filter):相位比较器输出的电压信号经过低通滤波器进行滤波,以去除高频噪声和杂散信号。

低通滤波器通常采用RC滤波器或者数字滤波器,其作用是平滑输出信号,并提供稳定的直流电压。

3. 电压控制振荡器(Voltage Controlled Oscillator,VCO):VCO是锁相环的可变频率源,其输出频率可以通过控制输入的电压进行调节。

VCO的频率范围通常较宽,可以根据需要选择。

VCO的输出信号经过分频器后与输入信号进行比较,通过调整VCO的频率来实现输入信号与参考信号的同步。

4. 分频器(Divider):分频器用于将VCO的输出信号分频,得到一个与输入信号频率相匹配的信号。

分频器通常采用可编程分频器,可以根据需要选择分频比。

分频器的作用是将VCO的高频输出信号转换为与输入信号频率相匹配的信号,以便与输入信号进行比较。

锁相环的工作原理如下:1. 输入信号和参考信号经过相位比较器进行比较,得到相位差信号。

2. 相位差信号经过低通滤波器滤波,得到一个稳定的直流电压。

3. 直流电压作为控制信号输入到VCO中,调节VCO的频率。

4. VCO的输出信号经过分频器分频,得到一个与输入信号频率相匹配的信号。

锁相环工作原理

锁相环工作原理锁相环是一种用于频率合成和频率测量的电子系统,它可以将输入信号的频率与参考信号的频率进行比较,并通过反馈控制来使两者保持同步。

锁相环广泛应用于通信系统、雷达、测量仪器等领域。

一、锁相环的基本组成1. 相位比较器(Phase Detector):相位比较器是锁相环的核心部件,用于比较输入信号和参考信号之间的相位差。

常见的相位比较器有乘法器、异或门等。

2. 低通滤波器(Low Pass Filter):相位比较器输出的信号经过低通滤波器进行滤波,以去除高频噪声和杂散信号,得到平滑的控制电压。

3. 电压控制振荡器(Voltage Controlled Oscillator,VCO):VCO是锁相环的另一个重要组成部分,它根据控制电压的大小来调节输出频率。

VCO的频率范围应包含输入信号和参考信号的频率。

4. 分频器(Divider):分频器将VCO的输出信号进行分频,得到与参考信号频率相同或相近的信号,用于与输入信号进行相位比较。

5. 反馈环(Feedback Loop):反馈环将分频器的输出信号反馈到相位比较器,形成闭环控制系统。

通过不断调节VCO的频率,使输入信号和参考信号的相位差尽可能小,从而实现锁相环的工作。

二、锁相环的工作原理锁相环的工作原理可以分为两个阶段:捕获(Acquisition)和跟踪(Tracking)。

1. 捕获阶段:在捕获阶段,锁相环的目标是将输入信号的频率和相位与参考信号进行同步。

首先,相位比较器将输入信号和参考信号进行相位比较,产生一个误差信号。

该误差信号经过低通滤波器后,作为控制电压输入到VCO中。

VCO的输出信号经过分频器后与参考信号进行相位比较,不断调节VCO的频率和相位,直到输入信号和参考信号的相位差趋近于零。

2. 跟踪阶段:在捕获阶段完成后,锁相环进入跟踪阶段。

在跟踪阶段,输入信号的频率和相位可能会发生变化,锁相环需要通过反馈控制来保持输入信号和参考信号的同步。

锁相环的基本原理和应用

锁相环的基本原理和应用1. 什么是锁相环锁相环(Phase-Locked Loop,简称PLL)是一种电路模块,其基本原理是通过对输入信号和参考信号的相位进行比较和调节,以使输出信号与参考信号保持稳定的相位差。

锁相环广泛应用于通信、测量、频率合成等领域,因其能够实现信号调频、时钟控制等功能而备受关注。

2. 锁相环的基本结构锁相环由相位比较器(Phase Comparator)、环路滤波器(Loop Filter)、振荡器(VCO)和分频器(Divider)组成。

其基本结构如下所示:•相位比较器:相位比较器用于比较输入信号和参考信号的相位差,并产生一个与相位差成正比的控制电压。

•环路滤波器:环路滤波器用于平滑相位比较器输出的控制电压,并将其转换成稳定的直流电压。

•振荡器:振荡器根据环路滤波器输出的控制电压来调节其输出频率,使其与参考信号频率保持一致。

•分频器:分频器将振荡器输出的信号进行频率分频,以产生一个与参考信号频率一致且稳定的输出信号。

3. 锁相环的工作过程锁相环的工作过程可以分为四个阶段:捕获(Capture)、跟踪(Track)、保持(Hold)和丢失(Lose)四个阶段。

•捕获阶段:在捕获阶段,锁相环通过不断调节VCO的频率,使其与参考信号频率逐渐接近,并将相位差逐渐减小。

•跟踪阶段:当锁相环的输出频率与参考信号频率相等时,进入跟踪阶段。

在该阶段,VCO的频率和相位与输入信号保持一致。

•保持阶段:在保持阶段,锁相环维持着与输入信号相同的相位和频率。

任何相位和频率的变化都会通过反馈回路进行补偿。

•丢失阶段:如果输入信号的频率超出锁相环的捕获范围,锁相环无法跟踪该信号,进入丢失阶段。

在该阶段,锁相环输出的信号频率与输入信号频率不一致。

4. 锁相环的应用锁相环在各个领域有着广泛的应用,下面列举几个常见的应用:•频率合成器:锁相环可以将稳定的参考频率合成为其他频率,广泛用于通信、雷达、测量等领域。

锁相环技术原理及其应用

锁相环技术原理及其应用一、锁相环技术原理1.1 基本概念锁相环(Phase-Locked Loop,PLL)是一种调节电路,能够通过控制其输出信号相位与参考信号相位之间的差值,使输出信号频率与参考信号频率一致,并且其输出信号相位与参考信号精确同步。

锁相环可以用于频率合成、时钟恢复、数字信号处理、射频通信等领域。

1.2 工作原理锁相环主要由相位比较器、低通滤波器、时钟发生器、可变增益放大器和电压控制振荡器等组成。

其中,相位比较器的作用是将参考信号和反馈信号进行比较,然后得到相位误差信号。

低通滤波器的作用是将相位误差信号进行平滑处理,得到直流误差信号。

时钟发生器的作用是产生参考信号。

可变增益放大器的作用是将误差信号放大后作为电压控制振荡器的控制电压。

电压控制振荡器的作用是产生锁相环输出信号,并且通过调节电压来控制输出信号的频率和相位。

1.3 稳定性分析锁相环的稳定性与参考信号的稳定性和相位比较器的带宽以及低通滤波器的截止频率等因素有关。

稳定性分析主要是评估锁相环输出信号的频率精度和相位噪声。

二、锁相环技术应用2.1 频率合成频率合成是利用锁相环技术将一个较低频率信号转换为高频率信号。

其中,参考信号是一个较低频率信号,产生参考信号的时钟发生器经过倍频器将参考信号的频率增加到所需的合成频率,然后经过相位比较器和滤波器控制电压控制振荡器的输出频率。

频率合成广泛应用于通信、广播、雷达、卫星导航等领域。

2.2 时钟恢复时钟恢复是一种将时钟信号从数据信号中恢复出来的技术。

锁相环可以通过将数据信号作为反馈信号,将时钟信号从数据信号中恢复出来。

时钟恢复广泛应用于数字通信和数字音频领域。

2.3 数字信号处理锁相环可以通过将输入信号与锁相环输出信号相比较,将输入信号变换的频率和相位误差降到很小,从而使输入信号的相位和频率与输入信号一致。

锁相环广泛应用于数字信号处理,例如数字滤波器、数字混频器、数字降噪器等。

2.4 射频通信锁相环在射频通信中的应用非常广泛,主要用于频率合成、时钟恢复等领域。

锁相环原理及使用

•

•

谢谢!欢迎提问。

2、另外19款PLL

步进:25kHz,带宽1.5kHz,相位裕量:45°

3、ADF4154小数分频锁相源

fREF=12.8MHz,带宽8kHz,相位裕量:45°

4、ADF4001参考时钟源 步进:40kHz,VC-TCXO10MHz

环路滤波器

• 在选定参考信号、鉴相器以及VCO 的前提下,那么环路滤波器的设计 对信号的指标就起着关键的作用。 本公司通用的环路滤波器为无源三 阶环,并在滤波器后加一个1μH的 电感以防止其它高频信号的串扰。 环路滤波器利用ADIsimPLL软件, 采用相位裕量设计法,只要给定环 路带宽和相位裕量就能设计环路滤 波器。环路带宽一般取1/10-1/20 fRES,相位裕量30º ,一般取 -60º 45º 。 需要说明的是,不应刻意拔高环路 滤波器的作用。环路带宽和相位裕 量只要在合理的范围之内,它是不 会影响锁定的,但是会对锁定时间、 相噪和杂散造成一定的影响。

从原理上来说,PLL主要由以下六个部分组 成:参考晶振,R分频器,鉴相器(电荷泵), 环路滤波器,VCO,N分频器。

fREF

XTAL ÷R PD VCO

fout

÷N

fout

定义:

fREF :晶振参考频率 fout :输出频率 fRES :频率步进

那么, 鉴相频率 fPFD=fREF/R=fout/N (1) ---------------------------------------------------------------------------------------------对于整数分频锁相源: fRES=fPFD (2) N=P*B+A (B≥A) (3) 其中:P为前置分频器分频比 A、B为计数器 ---------------------------------------------------------------------------------------------对于小数分频锁相源: fRES=fPFD/MOD (4) N=INT+FRAC/MOD (5) 其中:MOD为模,即分频比N小数部分的分母 FRAC为分频比N小数部分的分子 INT为分频比N的整数部分

锁相环的原理范文

锁相环的原理范文锁相环(Phase-Locked Loop,PLL)是一种广泛应用于电子通信、数字信号处理、时钟系统等领域的控制系统。

它的主要功能是将输入信号的相位和频率与参考信号进行比较,并通过反馈回路来控制输出信号的相位和频率,使得输出信号与参考信号保持同步。

锁相环通常由三个主要部分组成:相位比较器、环路滤波器和振荡器。

相位比较器是锁相环的核心部件之一,它用于将参考信号和输出信号的相位进行比较,并产生一个误差信号。

常见的相位比较器有两种类型:正弦相位比较器和数字相位比较器。

1.正弦相位比较器:在其中一个时间点上,正弦相位比较器通过对输入信号和参考信号进行正弦函数运算,得到一个差值信号。

这个差值信号产生的幅度与输入信号和参考信号之间的相位误差有关。

2.数字相位比较器:数字相位比较器将输入信号和参考信号分别转换为数字形式,并进行逐位比较。

根据比较结果,数字相位比较器产生一个误差信号,表示输入信号和参考信号之间的相位差。

相位比较器产生的误差信号被送入环路滤波器。

环路滤波器的作用是对误差信号进行滤波和放大,以产生控制信号。

常见的环路滤波器有积分环路滤波器和低通滤波器。

1.积分环路滤波器:积分环路滤波器将误差信号进行积分运算,以消除高频噪声和抑制低频误差。

积分环路滤波器的输出是一个连续的直流信号,用于控制振荡器的频率。

2.低通滤波器:低通滤波器用于滤除误差信号中的高频噪声,只保留低频成分。

低通滤波器的输出用于调节振荡器的相位。

振荡器是锁相环的另一个重要组成部分。

它根据控制信号产生输出信号,并将输出信号反馈给相位比较器,与参考信号进行比较。

根据比较结果,振荡器调整输出信号的频率和相位,使其逐渐与参考信号同步。

根据不同的应用场景,锁相环还可以加入除频器(频率分频器)、数字-模拟转换器等辅助功能,以实现更复杂的控制任务。

总结起来,锁相环通过相位比较器对输入信号和参考信号的相位进行比较,然后通过滤波器将误差信号转换成控制信号,最后通过振荡器产生同步相位的输出信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

7

123

2020/6/28

4.3.锁相环的应用 4.3.1 频率倍乘

基本的PLL据图示于图1,输出信号频率 锁定于输入频率的平均值,因此,输入频

率与输出频率相同。而图2所示电路为又 一种锁相环,其输出频率精确等于输入频

率的十倍。因此,电路的作用又如频率倍

乘器。

8

123

2020/6/28

fr 相位比较器

4.3.3.2 VCO的应用

V CC

W

VCO VCC

9

4 Fo

基本振荡器条件 VCOin = VDD :

50 0K

8

(S ET FR EQ )

5

6 7 11

12

C1

R1 R2

0. 1U

10 0K

R ES2

Fmax= 1 / R1( C1+32pf ) R1 ( 10k -- 1M ) VCOin = VSS:

fo 并将其与外加参考频率fr作比较,产生 一个与相位差对应的误差电压输出至低通

滤波器。

3

123

2020/6/28

误差电压经LPF滤波后馈入VCO 的控制 输入端,这样就可使fo和fr之间的任何频 率差减少相位差逐步恒定。这时,环路就 称为被锁定了,即锁定状态。

4

123

2020/6/28

如果VCO 的频率在开始时低于输入参 考频率,相应比较器的输出偏正。此正输 出电压经滤波后加至VCO,强制VCO 的 频率增加,直至 VCO的频率和相应与输 人参考信号的频率与相应精确相同为止。

相位差在0—180 范围内变化时,V的脉冲宽度t p也随着改变,由于V的周期是t,占空比D(D =tp/t)出随着改变。V经低通滤波器后即可 得到平均值电乐Vd。Vd与相位差成正比。

20

123

2020/6/28

相位差=0 时 Vd=0; 相位差=45 时,Vd=Vdd/4 相位差=90 时,Vd=Vdd/2 相位差=180 时,Vd=Vdd

fig 1 V --C

Fmin = 1 / R2( C1+32pf )

15

123

2020/6/28

键控移频 ( FSK )

V CC

R1

VCO VCC

9

4 Fo

50 0K

8

(S ET FR EQ )

5

6 7 11

C1

R2

0. 1U

10 0K

U1

U2

N OT

R3

N OT

PO T2

123

C2

C AP fig 2 FS K

16 2020/6/28

4.3.3.3 调频信号( FM )的解调

载频 = 10kHz 调制信号 = 400 Hz ( 音频 ) 解调输出 Pin10

17

123

2020/6/28

解调

1

2

3

4

FM

C 14

C AP

PhaseCompartor I

2 R?

3

10 0k

C1

10 00 p

6

7

9

C 0. 1u

8 5 11

12

R1 R2 4. 7M

50 K

123

O PA MP

10 Uo

Rl 10 k

fig 2 F -- V

Ti tle

Si ze

N

A 4 19

20DFi2alte0e:: /6/28

15 E:

4.4. PLL锁相环电路分析

4.4.1 4046比较器I和II的特点

比较器I的特点是:两个输入信号的电平状态相 异时( 一个是高电平,一个是低电平),输山信号 V为高电平:反之为低电平。当两个输入信号的

第4章锁相环的原理和应用10

4.1.锁相环的组成

图1是基本锁相环电路的框图。PLL是由

相位比较器(有时称为相位检波器)、低

通滤波器(LPF)和线性压控振荡器

(VCO)三部分组成。

fr

误差

fo

相位比较器

低通滤波器

线性压控振荡器

反馈

123

图1

2 2020/6/28

4.2.锁相环的原理

相位比较器将来自压控振荡的输出频率

误差

fo

低通滤波器

线性压控振荡器

计数器10

图2

在图2的框图中,一个“计数器10”除十分频器 插接在反馈环的VCO输出端和相应比较器的输入 端之间。因此,相应比较器锁定在除十计数器的 输出频率上,而不是 VCO的输出频率上。

9

123

2020/6/28

这样,锁定条件就变为VCO的频率(fo)必须是输 入参考信号频率(fr)的十倍,而电路的作用.就是 倍频系数为10的频率倍乘器。电路也可以倍乘任 何数,不只是乘以十,只要在PLL反馈环中插入 具有相应分频比的计数器即可。

12

123

2020/6/28

4.3.3 CD4046 及其应用

4046 PLL锁相环电路: 一个小功率线性压控振荡器(VCO) 一个源极跟随器 一个齐纳二极管 二个相位比较器 4046 PLL锁相环电路组成框图如下:

13

123

2020/6/28

4.3.3.1. CD4046.pdf

14

123

2020/6/28

10

123

2020/6/28

4.3.2 频率合成

PLL电路还可以用做精确的可编程频率合成器 ( 见图3) 相位比较器的参考输入频率fr是频率精确 固定的1kHZ信号,此信号是由1MHZ晶体振荡器 的输出被除1000计数器分频得到的。

计数器 1000

fr 相位比较器

误差

fo

低通滤波器

压控振荡器

振荡器 1 MHZ

123

可编程计数器 图3

11 2020/6/28

象频率倍乘电路那样,在反馈环中有一个计数 器插接在VCO的输出端和相位比较器的输人端之 间。但此电路是外部可编程的,所以,它具有 100X至 1000 X之间的任何整数分频比。

由于此电路具有这一特点,故能产生或合成在 100kHZ至 1MHZ之间的稳定、精确频率,步距为 1kHZ。在图3中的VCO电路至少应具有10至1的频 率延伸范围,以复盖所需的频段。此外,频率步 距对应于1kHZ的外接输入频率。

5

123

2020/6/28

如果VCO的频率增加到高于输入参考频 率,则发生与上述相反的过程。相应比较 器的输出减少,使VCO 的频率降低,以 锁定到与输入参考相同的频率上。

6

123

2020/6/28

低通滤波器将相位检波器的输出滤波后 转换成平滑的直流控制电压,是锁相环电 路的重要组成部分。由于滤波器有一定的 时间常数,所以PLL的锁定不是瞬时的, 因而VCO的输出频率锁定在参考电压fo的 平均值上,而不是锁定到即时值。这一特 性利于将带噪ຫໍສະໝຸດ 的输入参考频率形成纯净 的输出频率。

VCO

85

4

R1 10 0K

O PA MP

10 Uo

Rl 10 k

fig 1 F M -- V

18

123

2020/6/28

频率 – 电压转换 ( F – V )

PhaseCompartor II

Fin

C1 14

C AP

13 R 4 10 0k

C1

.0 1u

6

7

9 VCO

4

R5 10 k

C2 51 00 p