WT588C语音芯片技术详解说明

WT588C语音芯片技术详解说明

1、产品特点

可以重复烧写语音;

WT588C-16S容量可以选择4Mb、8Mb、16Mb、32Mb、64Mb、128Mb;

PWM和DAC两种音频输出方式;

内部集成时钟振荡器;

二线最多可以加载255段语音;

触发防抖时间:50us(串口)和10ms(按键);

支持播放不同采样率的语音文件、WAV音频格式;

支持BUSY状态输出功能;

工作电压:DC2.4~5.0V。

2、芯片选型

WT588C16-16S内置容量16Mbit,可以任意更换语音。

WT588C-16S外接SPI-flash,可以任意更换语音。

芯片控制方式有:两线串口。

芯片输出方式有:PWM输出(直接推动喇叭)、DAC输出(外接功放使用)。下文有相应的参考电路。

3、应用范围

汽车(防盗报警器、倒车雷达、GPS导航仪、电子狗、中控锁);

智能家居系统;

家庭防盗报警器;

医疗器械人声提示;

家电(电磁炉、电饭煲、微波炉);

娱乐设备(游戏机、游乐机);

学习模型(早教机、儿童有声读物);

智能交通设备(收费站、停车场);

通信设备(电话交换机、电话机);

工业控制领域(电梯、工业设备);

高级玩具。

4、管脚图

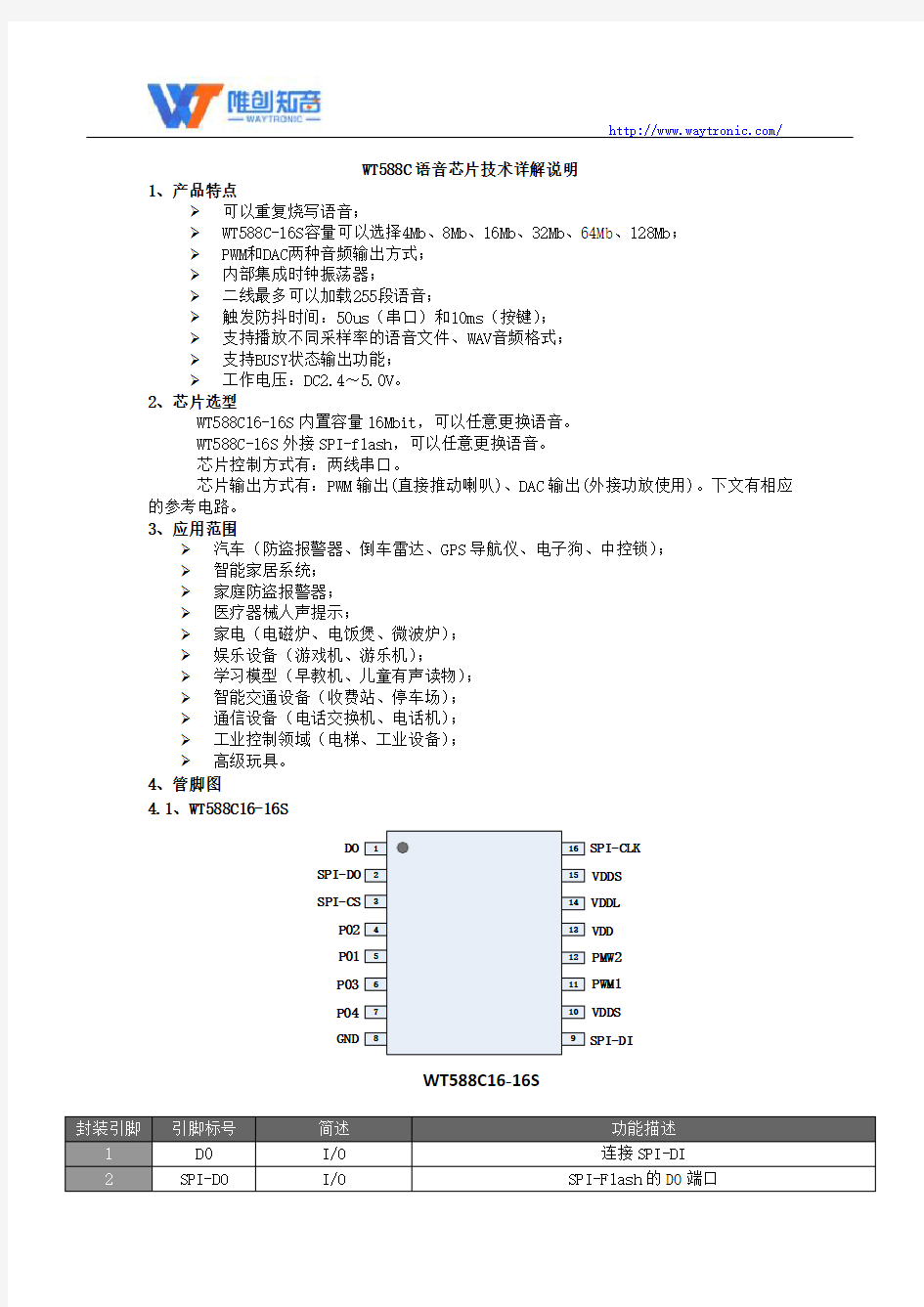

4.1、WT588C16-16S

DO SPI-DO SPI-CS

P02

P01

P03

P04

GND

PWM1

PMW2

SPI-DI

VDDS

VDD

SPI-CLK

VDDL

VDDS WT588C16-16S

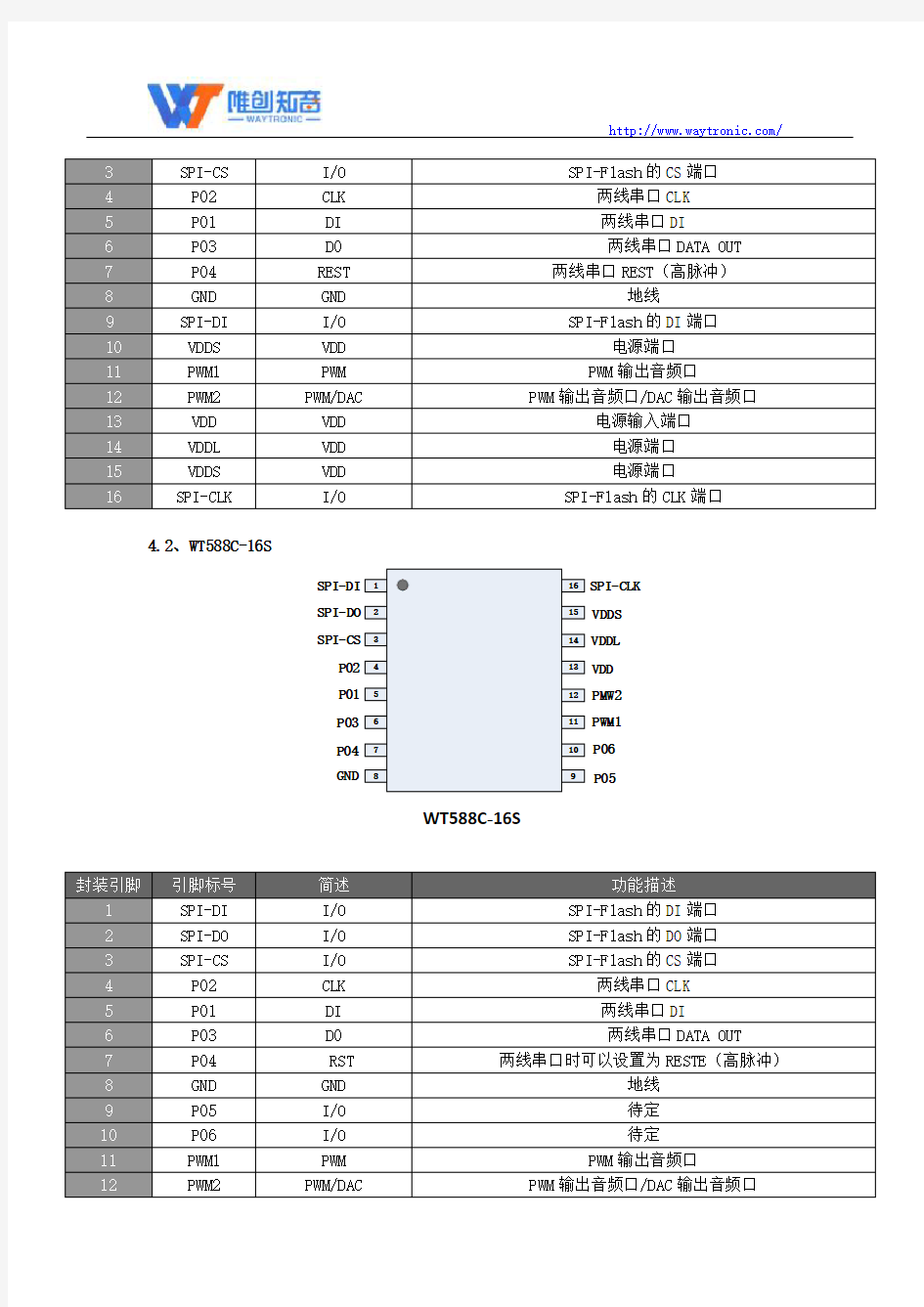

4.2、WT588C-16S

SPI-DI SPI-DO SPI-CS

P02

P01

P03

P04

GND

PWM1

PMW2

P05

P06

VDD

SPI-CLK

VDDL

VDDS WT588C-16S

5、电气参数

环境温度25℃,工作电压DC3V

6、两线串口控制模式

6.1、发送地址命令

两线串口控制模式由DI及CLK发送数据信号控制语音地址,同时由DO返回相关操作数据。在发送DI前先将CLK拉高100us以唤醒芯片工作,继而发送周期为200us的CLK信号跟DI,在接收到DI数据100us后DO返回DI所发送的数据。整个数据需要发送24bit,数据发送完成后200us,开始播放地址语音。

时钟周期的工作范围为50us~4000us。

备注:

在上电时,若CLK管脚有高脉冲或者高电平,则进入烧写模式,芯片无法正常工作,须给P04(RESET)一个10ms以上的高脉冲。使用51系列MCU的客户需注意!此类MCU复位后IO默认输出高电平,所以会导致WT588C芯片进入烧写模式。

因此、第一次发指令的时候、可以先给P04复位脚一个高脉冲复位一下芯片,然后发指令、CLK发送完后,建议把CLK拉低。

6.2、读取芯片工作状态

发送16bit 的数据0×2200,可以通过读取DO 返回的数据,知道芯片的当前状态。由DO 返回的D7数据,0代表语音停止,1代表芯片正在播放语音。

注意:两线串口模式下不会自动进入休眠状态,需要低功耗可通过休眠指令让芯片进入休眠状态。

6.4、语音地址

WT588C 在两线串口模式下最多可加载256段语音,注意由于语音总地址不一样,单片机发送给语音芯片的控制指令不一样。

当语音总地址小于100段时;地址所对应的命令如下: (语音地址总个数为1~100) 可以发现规律、每个地址码按照20H 累加。

CLK DI DO D15 D14 D13 D12 D11

D6 D5

D4 D3 D2 100us 100us GroupN D1 VOICE D7 D0 D15 D14

D13 D12

D11

D6 D5 D4 D3 D2 D1 D7 D0

200us

当语音总地址大于100段时;地址所对应的命令码如下:

客户发送的是命令码就行了、比如说客户要播放第5个地址的语音。即只需要发送指令0×1800E8即可。

7、应用电路

7.1、WT588C16-16S两线串口模式(PWM输出)

备注:VDD电压范围可以选2.8~5.2V

芯片I/O口电压3.3V

7.2、WT588C16-16S两线串口模式(DAC输出)

备注:VDD电压范围可以选2.8~5.2V

芯片I/O口电压3.3V

7.3、WT588C-16S两线串口模式(PWM输出)

备注: VDD电压范围2.8~5.2V

芯片I/O口电压3.3V

7.4、WT588C-16S两线串口模式(DAC输出)

备注: VDD电压范围2.8~5.2V

芯片I/O口电压3.3V

7.5、WT588C16-16S内置FLASH下载电路

备注:1.PWM1要接上VDD

2.VDDS要接上VDD

3.芯片I/O口电压3.3V

8、程序范例

8.1、两线串口控制程序范例

//MCU: STC10F04

//晶振: 22.1184MHz

#include “STC8051.h”/* STC8051 definitions */ #include

sbit WT_CLK = P2 ^ 0;

sbit WT_DI = P2 ^ 2;

sbit WT_DO = P2 ^ 3;

sbit LED_OUT = P4 ^ 6; //指示灯

sbit KEY1 = P3 ^ 7;

sbit KEY2 = P3 ^ 6;

sbit KEY3 = P3 ^ 5;

sbit KEY4 = P3 ^ 4;

unsigned char VoiceAddr = 0; //存储语音地址

/*--------------------------------------

;模块名称: Delay_10us

;功能: 延时函数,STC10F04 10us @22.1184MHz ;入参: unsigned int n 延时次数

;出参: 无

;-------------------------------------*/

void Delay_10us(unsigned int n)

{

unsigned char i;

for (; n > 0; n--)

{

for (i = 40; i > 0; i--)

{

_nop_();

}

}

}

/*--------------------------------------

;模块名称: Delay_1ms

;功能: 延时函数,STC10F04 1ms @22.1184MHz ;入参: unsigned int z 延时次数

;出参: 无

;-------------------------------------*/

void Delay_1ms(unsigned int z)

{

unsigned int i, j;

for (i = z; i > 0; i--)

{

for (j = 1700; j > 0; j--) ;

}

}

/*--------------------------------------

;模块名称:WTH_2L

;功能:WTH二线串口通信函数,高位在前,发送24位数据;入参:发送的24位数据

;出参:芯片返回的数据

;-------------------------------------*/

unsigned long int WTH_2L(unsigned long int dat)

{

unsigned char i;

unsigned long int return_dat;

WT_CLK = 1;

Delay_100us(2);

for (i = 0; i < 24; i++)

{

WT_CLK = 1;

if (dat & 0x800000) WT_DI = 1;

else WT_DI = 0;

dat <<= 1;

Delay_10us(5); //50us

if (WT_DO) return_dat |= 0x01;

else return_dat &= ~(0x01);

return_dat <<= 1;

Delay_10us(5); //50us

WT_CLK = 0;

Delay_10us(10); //100us

}

Delay_10us(5); //50us

if (WT_DO) return_dat |= 0x01;

else return_dat &= ~(0x01);

return_dat &= 0x7ffffe; //屏蔽前后无用的数据

return return_dat;

}

/*--------------------------------------

;模块名称: Play_voice

;功能:WTH二线串口通信,WTH芯片播放语音

;入参:播放的地址0~255

;出参:0:播放失败;1:播放成功

;-------------------------------------*/

unsigned char Play_voice(unsigned char addr)

{

unsigned long int dat;

dat = 0x1800c8 + (addr << 5);

if (WTH_2L(dat) == dat) return 1; //播放成功

return 0; //播放失败

}

/*--------------------------------------

;模块名称:WTH_Check_sate

;功能:WTH二线串口通信,查询WTH芯片状态,高位在前发送16位数据;入参:无

;出参:0:芯片未处于播放状态;1:芯片正在播放状态

;-------------------------------------*/

unsigned char WTH_Check_sate(void)

{

unsigned char i;

unsigned long int dat = 0x2200;

unsigned long int return_dat;

WT_CLK = 1;

Delay_100us(2);

for (i = 0; i < 16; i++)

{

WT_CLK = 1;

if (dat & 0x8000) WT_DI = 1;

else WT_DI = 0;

dat <<= 1;

Delay_10us(5); //等待50us后才读取DO数据

if (WT_DO) return_dat |= 0x01;

else return_dat &= ~(0x01);

return_dat <<= 1;

Delay_10us(5); //50us

WT_CLK = 0;

Delay_10us(10); //100us

}

if (WT_DO) return_dat |= 0x01;

return_dat &= 0xffff;

if (return_dat & 0x80) //只判断第9位数据

return 1; //正在播放

return 0; //未播放

}

void Main(void)

{

unsigned long int temp;

P2M0 = 0x00;

P2M1 = (1 << 3); //P22(DO)为高阻输入,其他为普通IO

WT_CLK = 0;

WT_DI = 0;

//如果是51系列单片机,请在在此时才给WTH芯片上电初始化。

P01 = 1; //打开WTH的电源控制

WTH_2L(0xa0140); //芯片初始化

while (1)

{

if (P3 != 0xff)

{

if (KEY1 == 0)

{

Delay_1ms(20);

if (KEY1 == 0)

{

if (Play_voice(VoiceAddr)); //每按一次播放下一曲

if (VoiceAddr < 255)

{

VoiceAddr++;

}

}

while (KEY1 == 0);

}

if (KEY2 == 0)

{

Delay_1ms(20);

if (KEY2 == 0)

{

Play_voice(VoiceAddr); //每按一次播放上一曲

if (VoiceAddr)

{

VoiceAddr--;

}

}

while (KEY2 == 0);

}

if (KEY3 == 0)

{

Delay_1ms(20);

if (KEY3 == 0)

{

WTH_2L(0x1800c8); //手动播放某一指定地址,方便用于调试

}

while (KEY3 == 0);

}

if (KEY4 == 0)

{

Delay_1ms(20);

if (KEY4 == 0)

{

WTH_2L(0xa0140); //手动对芯片重新初始化,方便用于调试

}

while (KEY4 == 0);

}

}

Delay_1ms(30);

if (WTH_Check_sate()) //检测芯片的状态

LED_OUT1 = 1; //正在播放语音

else LED_OUT1 = 0; //未播放语音

}

}

9、封装尺寸图

9.1、WT588C-16S/WT588C16-16S封装尺寸图

单位:mm

成绩录入和学分管理及综合实践等使用方法

1.1.1 原始成绩录入 学生成绩登记,可分为成绩录入和成绩导入两种方式,成绩导入系统提供了模板供参考,本节介绍如何进行成绩录入。 以下以维护“高二(01)班”“2008-2009第二学期模块终结性考试”中的“英语写作”模块为例,操作示范如下图: 操作步骤: 1.在左侧“成绩管理”标签页中找到“原始成绩录入”功能项; 2.右侧维护区选定考试名称“2008-2009第二学期模块终结性考试”、模块名称“英 语写作”; 3. 4. 5.在左侧班级列表中找到目标班级“高二(01)班”; 右侧维护区显示该班级的学生信息,在成绩一列中依次输入学生成绩信息;成绩输入完成后,单击页面下方的“保存”,完成学生成绩信息的录入。 1.1.2 成绩统计 如果需要考查学生学习成绩走势、班级成绩对比、年级成绩走势等成绩综合统计报表,则需进行成绩统计。 以下以统计“高二年级”“2008-2009第二学期模块终结性考试”中的“英语写作”统计为例,操作示范如下图:

操作步骤: 1.在左侧“成绩管理”标签页中找到“单科成绩统计”功能项; 2.右侧维护区选定考试名称“2008-2009第二学期模块终结性考试”、年级“高二”、 班级类型“普通班”、学科名称“英语写作”; 3. 4. 5.选定统计方法,按“分数线”统计; 设定A、B、C、D、E 等的分数线; 单击下方“统计”完成成绩,并保存,保存成绩统计结果。 1.1.3 补考处理 对达不到及格分数的学生要进行补考处理。首先生成模块的补考名单,在补考过后需要维护补考学生的补考成绩。以“英语写作”模块高二年级补考学生为例示范操作如下:

操作步骤: 1.在左侧“成绩管理”标签页中找到“补考处理”功能项,选择维护区上方的“补 考名单生成”项; 2.右侧维护区选定考试名称“2008-2009第二学期模块终结性考试”、模块“英语写 作”,点击页面下方的“生成名单”; 3.在跳出的“生成名单”——对话框,单击“确定”; 4.进入“补考名单打印”项,查看右上方的打印预览,并打印名单; 5.补考结束后,进入“补考成绩维护”项; 6.维护考生的补考成绩,点击页面下方的“保存”后,再点击“替换”,完成补考成 绩的更新。 1.1.4 重修处理 对补考后仍然不及格的学生一般要求进行重修处理,该模块操作与补考处理类似。请参考补考处理。 1.1.5 成绩查询 学科教师、班主任、教务处、校长等关注分析学生成绩时,可查看系统提供的成绩统计报表,系统提供原始成绩查询、年级成绩表、年级分析表、模块分析表等各项综合统计

max7219资料及电路图

MAX7219是MAXIM公司生产的串行输入/输出共阴极数码管显示驱动芯片,一片MAX7219可驱动8个7段(包括小数点共8段)数字LED、LED条线图形显示器、或64个分立的LED发光二级管。该芯片具有10MHz传输率的三线串行接口可与任何微处理器相连,只需一个外接电阻即可设置所有LED的段电流。。它的操作很简单,MCU只需通过模拟SPI三线接口就可以将相关的指令写入MAX7219的内部指令和数据寄存器,同时它还允许用户选择多种译码方式和译码位。此外它还支持多片7219串联方式,这样MCU就可以通过3根线(即串行数据线、串行时钟线和芯片选通线)控制更多的数码管显示。MAX7219的外部引脚分配如图1所示及内部结构如图2所示。 图1 MAX7219的外部引脚分配

图2 MAX7219的内部引脚分配 各引脚的功能为: DIN:串行数据输入端 DOUT:串行数据输出端,用于级连扩展 LOAD:装载数据输入 CLK:串行时钟输入 DIG0~DIG7:8位LED位选线,从共阴极LED中吸入电流 SEG A~SEG G DP 7段驱动和小数点驱动 ISET:通过一个10k电阻和Vcc相连,设置段电流 MAX7219有下列几组寄存器:(如图3) MAX7219内部的寄存器如图3,主要有:译码控制寄存器、亮度控制寄存器、扫描界限寄存器、关断模式寄存器、测试控制寄存器。编程时只有正确操作这些寄存器,MAX7219才可工作。

图 3 MAX7219内部的相关寄存器 分别介绍如下: (1)译码控制寄存器(X9H) 如图4所示,MAX7219有两种译码方式:B译码方式和不译码方式。当选择不译码时,8个数据为分别一一对应7个段和小数点位;B译码方式是BCD译码,直接送数据就可以显示。实际应用中可以按位设置选择B译码或是不译码方式。 图4 MAX7219的译码控制寄存器 (2)扫描界限寄存器(XBH)

芯片常用封装及尺寸说明

A、常用芯片封装介绍 来源:互联网作者: 关键字:芯片封装 1、BGA 封装(ball grid array) 球形触点陈列,表面贴装型封装之一。在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配 LSI 芯片,然后用模压树脂或灌封方法进行密封。也称为凸点陈列载体(PAC)。引脚可超过200,是多引脚 LSI 用的一种封装。封装本体也可做得比 QFP(四侧引脚扁平封装)小。例如,引脚中心距为 1.5mm 的360 引脚 BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚 QFP 为 40mm 见方。而且 BGA 不用担心 QFP 那样的引脚变形问题。该封装是美国 Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。最初,BGA 的引脚(凸点)中心距为 1.5mm,引脚数为225。现在也有一些 LSI 厂家正在开发500 引脚的 BGA。 BGA 的问题是回流焊后的外观检查。 现在尚不清楚是否有效的外观检查方法。有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。美国 Motorola 公司把用模压树脂密封的封装称为 OMPAC,而把灌封方法密封的封装称为 GPAC(见 OMPAC 和 GPAC)。 2、BQFP 封装(quad flat package with bumper) 带缓冲垫的四侧引脚扁平封装。QFP 封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形。美国半导体厂家主要在微处理器和 ASIC 等电路中采用此封装。引脚中心距0.635mm,引脚数从84 到196 左右(见 QFP)。

MAX7219

多功能LED译码显示驱动IC PS7219 1 引言 PS7219是由力源公司自行研制、开发的一款新型多功能8位LED显示驱动IC。接口采用三线SPI方式,用户只需简单修改内部相关的控制或数字RAM,便可很容易地实现多位LED显示。在性能上PS7219与MAXIM 公司的MAX7219完全兼容,并增加了位闪等功能。 PS7219具有多个级联特性,为大屏幕LED显示提供了方便。在理论上,只需三根用户I/O口控制线,便可以实现无穷多的LED级联显示。在实际应用中,已实现了149片PS7219级联,可以控制1192位LED 显示。 2 PS7219特点与引脚说明 PS7219的特点: ★ 串行接口(16位控制字); ★ 8位共阴级LED显示驱动; ★ 显示位数1~8,可数字调节; ★ 按位进行BCD译码/不译码数字制; ★ 16级亮度数字控制; ★ 上电LED全熄; ★ 提供位闪功能; ★ 多个PS7219级联可实现任意多的LED显示;★ 宽24脚双列直插模块封装。 PS7219引脚图如图1所示。 引脚功能说明见表1。 3 PS7219内部结构 如图2 所示,PS7219由六部分组成。 图2 PS7219内部组成框图 图1 PS7219引脚排列

3.1 串行输入缓冲部分 主要功能是与外部控制信号接口,将控制命令串 行读入,并进行串并转换,供控制器读取。 3.2 控制器 是整个IC的核心部分。它先将输入缓冲部分的控制字读入处理,根据其地址值送到相应的控制RAM或数字RAM,同时将数据送入串行同步输出部分,以便在下一个控制字输入周期,将其串行输出。 3.3 控制RAM数据RAM 这两部分一起控制LED译码显示部分,实现不同功能及字符的显示。 控制RAM包括:空操作寄存器,译码模式控制寄存器,亮度控制寄存器,掉电控制寄存器,闪烁控制寄存器,测试控制寄存器和扫描界线寄存器。 数据RAM包括:数据1—8寄存器。 3.4 LED译码显示 根据控制RAM和数据RAM的不同值,来实现相应的显示功能。 3.5 内部时钟电路 为控制器提供频率为24MHz的基准时钟,为LED译码显示电路提供频率为1.5kHz的扫描时钟。 4 使用及实例 4.1 使用注意事项 (1)PS7219上电后,内部RAM清零。显示前应先将亮度寄存器、译码模式寄存器及数据寄存器赋值。 (2)PS7219应连接共阴式LED显示器,没有用的LED显示器位选引脚可以悬空不接。 (3)其显示采用扫描方式,使用普通LED亮度可能不足,可选用高亮型号或超高亮型号。对于尺寸大于0.8英寸的LED,应使用适当的驱动电路。 (4)PS7219的RST复位端应可靠地接到复位电路上去。上电复位信号宽度要求大于100ms,典型复位门限为4.65V。 (5)级联时,如果驱动的LED个数不足8的倍数,可把两片驱动器的扫描界线设置为相同的值。 例如,若需11个LED,则两片PS7219分别联接6和5个,并把两片PS7219的显示位数都设置为6。这样,便不会造成两片PS7219驱动的LED亮度有所差异。 (6)当PS7219级联个数大于8个时,需要增加CLK、LOAD信号的驱动能力。可选用如SN74HC245类似的驱动IC。其具体做法见下面将要举的一实例。 4.2 应用举例 (1)单片应用单片PS7219驱动8位LED的原理图如图3所示。

新系统成绩录入方法说明

新系统成绩录入方法说明 各学院: 目前,我校采用新教务系统录入学生成绩。同老系统相比,新系统成绩评定更灵活。针对一门课程,教师可以通过课堂成绩、实践成绩和实验成绩三个维度对学生进行成绩评定。每个维度,教师又可以设置平时成绩、期中成绩和期末成绩三个选项。由此实现对学生成绩的多维评定。具体录入方法如下: 一、系统登录 方式1:登录学校门户后,点击应用直通车中的”新教务系统”,如下图 方式2:进入教务处主页https://www.360docs.net/doc/1318706967.html,/,点击教师服务中的“新综合教务”。选择“统一身份认证登录方式”,输入学校门户的账号和密码即可登录系统。外聘教师用教务登录方式,使用教务号和密码(密码与教务号相同)。 进入系统后,点击页面右侧“常用快捷入口”下的“成绩录入”,进入成

绩录入功能,页面显示教师本学期需录入成绩的课程。 二、成绩系数录入 点击课程里列表录入系数列的按钮,进入系数录入界面。 1.总成绩由”课堂成绩”、“实践成绩”和“实验成绩”三部分构成,每个部分又分为“平时成绩”、“期中成绩”和“期末成绩”。教师根据课程性质先确定各部分权重,再进一步确定每个部分平时、期中和期末的权重。 2.在“总成绩”行分别输入“课堂成绩”、“实践成绩”和“实验成绩”系数,三者之和应为1。 3.分别在“课堂成绩”、“实践成绩”和“实验成绩”三行输入“平时成绩”、“期中成绩”和“期末成绩”系数,三者之和应为1。 系数输入完成后,点击右上角“保存”按钮,系数保存后方可录入成绩。 4.成绩系数录入示例: (1)只有课堂成绩,且课堂成绩中平时成绩占30%,期末占70%,则成绩系数如下:

集成电路芯片封装技术

集成电路芯片封装技术(书) 第1章 1、封装定义:(狭义)利用膜技术及细微加工技术,将芯片及其他要素在框架或基板上布置、 粘帖固定及连接,引出接线端子并通过可塑性绝缘介质灌封固定,构 成整体立体结构的工艺 (广义)将封装体与基板连接固定,装配成完整的系统或电子设备,并确保整个系统综合性能的工程 2、集成电路的工艺流程:芯片设计(上)芯片制造(中)封装测试(占50%)(下)(填空) 3、芯片封装实现的功能:传递电能传递电路信号提供散热途径结构保护与支持 4、封装工程的技术层次(论述题):P4图 晶圆Wafer -> 第零层次Die/Chip -> 第一层次Module -> 第二层次Card ->第三层次Board -> 第四层次Gate 第一层次该层次又称芯片层次的封装,是指把集成电路芯片与封装基板或引脚架之间的粘贴固定、电路连线与封装保护的工艺,使之成为易于取放输送,并可与下一层组装进行链接的模块 第二层次将数个第一层次完成的封装与其他电子元器件组成一个电路卡的工艺 第三层次将数个第二层次完成的封装组装成的电路卡组合成在一个主电路板上使之成为一个部件或子系统的工艺 第四层次将数个子系统组装成为一个完整电子产品的工艺过程 5、封装的分类与特点: 按照封装中组合集成电路芯片的数目——单芯片封装(SCP)多芯片封装(MCP) 按照密封材料——高分子材料封装陶瓷材料封装 按照器件与电路板互连方式——引脚插入型(PTH)表面贴装型(SMT) 6、DCA(名词解释):芯片直接粘贴,即舍弃有引脚架的第一层次封装,直接将IC芯片粘贴到基板上再进行电路互连 7、TSV硅通孔互连封装 HIC混合集成电路封装 DIP双列直插式引线封装

教务管理系统教师用户成绩录入简要使用说明

各位老师: 本学期我校教务管理系统进行升级,使用界面有所变化。我们重新编印教师用户成绩录入简要使用说明,由此造成的不便,敬请谅解。 教务管理系统教师用户成绩录入简要使用说明 一、系统登录 打开IE浏览器,在教务处网页上找到右上角的综合教务管理系统,点击进入登录页面(图1)。选择教师用户,输入用户名及密码,进入教师管理界面(图2)。 成绩录入结束后,请各老师不要忘记关闭开启的窗口,以防他人进入,造成不良后果! 图1登录页面 用户名:输入教师用户名(教师用户名跟原来的一样)。 用户密码:初始密码由教学秘书提供,第一次登录本系统,请修改并保管好密码。 图2教师管理界面图3密码修改界面 二、密码修改 为防止登录信息泄密,请各位教师尽快更改原始密码,点击“信息维护”->“密码修改”,修改自己的原始系统密码和课程原始密码(图3)(第一次登录后,立即修改系统密码)。 三、成绩录入 1、点击“成绩录入”->选择本学期对应的任教课程(图4),进入网上成绩录入系统; (如发现任教课程有误,请速跟教学秘书联系。) 2、输入课程密码(如图5);(初始密码由教学秘书提供) 图4本学期任教课程图5输入课程密码界面 3、按“确定”按钮,进入学生成绩录入界面,在左上角输入各部分成绩比例及右上角选择记分制方式和总评记分方式后(图6),录入成绩按“保存”,全部完成后并检查无误后

按“提交”按钮(图6)。注意:按“提交”按钮后,成绩不能更改。 图6成绩录入界面 按“输出打印”按钮可将该班成绩输出打印。 选择班级及“格式二”,打印并签名后交院系存档。选择班级及“试卷分析”,可制作试卷册用。 成绩提交后教师不能再修改成绩,若需修改,请在开学初一周内,按有关文件向教务处学务科提出申请。 以上为教师成绩录入使用,更详细的说明请参阅教务处网站上《教务管理系统教师网上操作手册.doc》 附注:1、根据《龙岩学院考试管理办法》规定,考查课的成绩评定采用五级记分制(优秀、良好、中等、及格、不及格),一般期末测验成绩占总成绩的60%,平时成绩点总成绩的40%。考试课程学期成绩必须是平时成绩和期未成绩的综合评定,应以期未考试成绩为主(约占60%-80%),适当参考平时作业、提问、平时测验等成绩(约占20%-40%)。 2、计算机成绩的计分方式为:省高校计算机考试占该课程学期总评成绩的60%,平时考核成绩占总评成绩的40%. 3、若期末成绩被判为零分或教师当前录入的成绩为缓考、重修、补考等非正常考试的成绩时,必须在备注栏中选择相对应的选项。

MAX7219抗干扰

在强干扰环境下,如大功率电机的起停或高压发生过程中,干扰源可能通过供电电源或3根信号线串入显示电路而造成显示器的不稳定,从而出现笔段跳跃、显示不全、甚至全暗或全亮的现象. 4.对显示电路单独供电,并在Max7219的电源V+和GND之间接并接一个0.1uF去耦电容和一个10uF/16V电解电容,以有效提高其工作可靠性。 5. 在硬件上采用TVS管吸收瞬态功率,采用磁珠消除高频脉冲;在软件上采用不断刷新显示缓冲区的办法来保证显示的正确性,实际使用效果明显。 max7219(级联)显示问题 悬赏分:0 |解决时间:2008-10-2 22:46 |提问者:sangfuhuan 我用了两个max7219(级联),即显示4个四位, 但是,显示一会其中一对就开始灭了,或是其中一对出现乱码,好像是随机的,只是灭的时间! 难道说级联要注意什么吗? 还是---? 谢谢! 问题补充: 你好!我还想问你关于7219的问题,真是麻烦你了! 你说的加电容我已经加过了,但是你说的CLK,LOAD引脚窜入了干扰信号是啥意思呢?“加入抗干扰的驱动程序,定期重新配置7219 ”是啥意思呢?就是定期重新配置7219吗? 还有就是当我加了电容后小郭很明显!基本都好了,就是最近一上电一会就开始灭了,我怀疑是不是7219模块又问了?还是7219有问题了?你有什么意见呢?还有就是级联的时候,在程序中,在分别给凉快传数据时需要延时吗?在手册里

说是“串行数据输出端口,从DIN 输入的数据在16.5 个时钟周期后在此端有效”是什么意思呢? 非常感谢你!!! 我以前项目中用过4个max7219级联,用得比较稳定。 你这个现象是因为CLK,LOAD引脚窜入了干扰信号,而7219是边沿触发,容易受到干扰。 解决方法: 1、可以在靠近7219芯片的地方,给CLK,DIN加101 - 104的滤波电容,效果比较明显。 2、在程序中,加入抗干扰的驱动程序,定期重新配置7219 3、可以选用完全兼容的max7221代替

芯片封装的主要步骤

芯片封装的主要步骤 板上芯片(Chip On Board, COB)工艺过程首先是在基底表面用导热环氧树脂(一般用掺银颗粒的环氧树脂)覆盖硅片安放点,然后将硅片直接安放在基底表面,热处理至硅片牢固地固定在基底为止,随后再用丝焊的方法在硅片和基底之间直接建立电气连接。 裸芯片技术主要有两种形式:一种是COB技术,另一种是倒装片技术(Flip Chip)。板上芯片封装(COB),半导体芯片交接贴装在印刷线路板上,芯片与基板的电气连接用引线缝合方法实现,芯片与基板的电气连接用引线缝合方法实现,并用树脂覆盖以确保可靠性。虽然COB是最简单的裸芯片贴装技术,但它的封装密度远不如TAB和倒片焊技术。 COB主要的焊接方法: (1)热压焊 利用加热和加压力使金属丝与焊区压焊在一起。其原理是通过加热和加压力,使焊区(如AI)发生塑性形变同时破坏压焊界面上的氧化层,从而使原子间产生吸引力达到“键合”的目的,此外,两金属界面不平整加热加压时可使上下的金属相互镶嵌。此技术一般用为玻璃板上芯片COG。 (2)超声焊 超声焊是利用超声波发生器产生的能量,通过换能器在超高频的磁场感应下,迅速伸缩产生弹性振动,使劈刀相应振动,同时在劈刀上施加一定的压力,于是劈刀在这两种力的共同作用下,带动AI丝在被焊区的金属化层如(AI膜)表面迅速摩擦,使AI丝和AI膜表面产生塑性变形,这种形变也破坏了AI层界面的氧化层,使两个纯净的金属表面紧密接触达到原子间的结合,从而形成焊接。主要焊接材料为铝线焊头,一般为楔形。 (3)金丝焊 球焊在引线键合中是最具代表性的焊接技术,因为现在的半导体封装二、三极管封装都采用AU线球焊。而且它操作方便、灵活、焊点牢固(直径为25UM的AU丝的焊接强度一般为0.07~0.09N/点),又无方向性,焊接速度可高达15点/秒以上。金丝焊也叫热(压)(超)声焊主要键合材料为金(AU)线焊头为球形故为球焊。 COB封装流程 第一步:扩晶。采用扩张机将厂商提供的整张LED晶片薄膜均匀扩张,使附着在薄膜表面紧密排列的LED晶粒拉开,便于刺晶。 第二步:背胶。将扩好晶的扩晶环放在已刮好银浆层的背胶机面上,背上银浆。点银浆。

半导体集成电路封装技术试题汇总(李可为版)

半导体集成电路封装技术试题汇总 第一章集成电路芯片封装技术 1. (P1)封装概念:狭义:集成电路芯片封装是利用(膜技术)及(微细加工技术),将芯片及其他要素在框架或基板上布置、粘贴固定及连接,引出接线端子并通过可塑性绝缘介质灌封固定,构成整体结构的工艺。 广义:将封装体与基板连接固定,装配成完整的系统或电子设备,并确保整个系统综合性能的工程。 2.集成电路封装的目的:在于保护芯片不受或者少受外界环境的影响,并为之提供一个良好的工作条件,以使集成电路具有稳定、正常的功能。 3.芯片封装所实现的功能:①传递电能,②传递电路信号,③提供散热途径,④结构保护与支持。 4.在选择具体的封装形式时主要考虑四种主要设计参数:性能,尺寸,重量,可靠性和成本目标。 5.封装工程的技术的技术层次? 第一层次,又称为芯片层次的封装,是指把集成电路芯片与封装基板或引脚架之间的粘贴固定电路连线与封装保护的工艺,使之成为易于取放输送,并可与下一层次的组装进行连接的模块元件。第二层次,将数个第一层次完成的封装与其他电子元器件组成一个电子卡的工艺。第三层次,将数个第二层次完成的封装组成的电路卡组合成在一个主电路版上使之成为一个部件或子系统的工艺。第四层次,将数个子系统组装成为一个完整电子厂品的工艺过程。 6.封装的分类?

按照封装中组合集成电路芯片的数目,芯片封装可分为:单芯片封装与多芯片封装两大类,按照密封的材料区分,可分为高分子材料和陶瓷为主的种类,按照器件与电路板互连方式,封装可区分为引脚插入型和表面贴装型两大类。依据引脚分布形态区分,封装元器件有单边引脚,双边引脚,四边引脚,底部引脚四种。常见的单边引脚有单列式封装与交叉引脚式封装,双边引脚元器件有双列式封装小型化封装,四边引脚有四边扁平封装,底部引脚有金属罐式与点阵列式封装。 7.芯片封装所使用的材料有金属陶瓷玻璃高分子 8.集成电路的发展主要表现在以下几个方面? 1芯片尺寸变得越来越大2工作频率越来越高3发热量日趋增大4引脚越来越多 对封装的要求:1小型化2适应高发热3集成度提高,同时适应大芯片要求4高密度化5适应多引脚6适应高温环境7适应高可靠性 9.有关名词: SIP :单列式封装 SQP:小型化封装 MCP:金属鑵式封装 DIP:双列式封装 CSP:芯片尺寸封装 QFP:四边扁平封装 PGA:点阵式封装 BGA:球栅阵列式封装 LCCC:无引线陶瓷芯片载体 第二章封装工艺流程 1.封装工艺流程一般可以分为两个部分,用塑料封装之前的工艺步骤成为前段操作,在成型之后的工艺步骤成为后段操作

教务管理系统-成绩管理-操作手册

成都依能科技股份有限公司 技术文档 文档修订记录 *变化类型:创建、增加、修改、删除、审核 版权声明和保密须知: 本文件出现的任何文字叙述、文档格式、照片、插图、方法、过程等内容,除特别声明外,版权均归属成都依能科技股份有限公司所有,受到有关产权及版权法保护。 Copyright? 2013.All rights reserved 成都依能科技股份有限公司

教务管理系统操作手册 成绩管理 应用场景: 为了提高老师成绩录入和统计分析效率,传统成绩录入会浪费很多纸张,领导学生教师查看成绩非常不便,系统中提供报表可快速分析班级的成绩情况。 流程图 可以简化为四步:成绩录入基础设置,教师成绩录入,审核发布,生成统计表 操作步骤: 1.成绩分制维护 系统提供自定义成绩分制以满足学校多种分制情况。 “教务管理系统”->“课程成绩全局配置”->“成绩分制维护”->“添加”

2.成绩全局规则配置 设置好所有的分制后,就需要设置学校的学生培养模式,即学分制或者学年制。 “教务管理系统”->“课程成绩全局配置”->“成绩全局规则配置”->“学分录入配置” 若学校采用学分制管理,则勾选“学分制”;若不是,则勾选“学年制”。

若采用学分制,则图中所示项目含义为: “是否允许修改课程基础学分”:是否允许老师在录成绩时修改该门课程的学分,建议设置为“不允许”,以免影响后续统计; “是否允许修改课程获得学分”:是否允许老师在录成绩时修改单个学生所获得的学分; “学分有效数字保留”:如果学分全为整数,则选择“整数”;若有小数,例如“1.5分”之类的情况,则选择“1位小数”; “课程学分计算公式”:“按总评成绩计算”适用于学生所获得学分只参考总评成绩,与期中、平时等其他成绩无关的情况(可设置总评成绩对应的学分比例,如下图);“按成绩构成项成绩计算”适用于学生所获得学分并不参考总评成绩,而是按照期中、平时、期末等其他成绩构成项目达标情况来组合成最终学分的情况。

MAX7219工作原理简介

MAX7219工作原理简介 MAX7219是一个采用3线串行接口的8位共阴极7段LED显示驱动器。本文分析了MAX7219各个寄存器的功能,并结合MAX7219的工作时序,给出了MAX7219在Motorola MC68HC908单片机系统中的一个应用实例。关键词: MCU;MAX7219;LED Motorola MC68HC908 MAX7219工作时序及其寄存器 MAX7219是一个高性能的多位LED显示驱动器,可同时驱动8位共阴极LED或64个独立的LED。其内部结构框图如图1所示,主要包括移位寄存器、控制寄存器、译码器、数位与段驱动器以及亮度调节和多路扫描电路等。 MAX7219 采用串行接口方式,只需LOAD、DIN、CLK三个管脚便可实现数据传送。DIN管脚上的16位串行数据包不受LOAD状态的影响,在每个CLK的上升沿被移入到内部16位移位寄存器中。然后,在LOAD的上升沿数据被锁存到数字或控制寄存器中。LOAD必须在第16个时钟上降沿或之后,但在下一个时钟上升沿之前变高,否则数据将会丢失。DIN端的数据通过移位寄存器传送,并在16.5个时钟周期后出现在DOUT端,随CLK 的下降沿输出。 MAX7219的操作时序如图2所示。 MAX7219的串行数据标记为D15~D0,其中低8位表示显示数据本身,最高的4位D15~D12未使用,寻址内部寄存器的地址位占用D11~D8,选择14个内部寄存器,见表1。 图1 MAX7219内部结构框图 图2 MAX7219的数据传送时序 MAX7219 内部具有14个可寻址数字和控制寄存器。其中的8个数字寄存器由一个片内8×8双端口SRAM实现。它们可直接寻址,因此可对单个数进行更新并且通常只要 V+超过2V数据就可保留下去。除8个数位寄存器之外,还有无操作、译码方式、亮度调整、扫描位数、睡眠模式和显示器测试6个控制寄存器。 无操作寄存器用于多片MAX7219级联,在不改变显示或不影响任意控制寄存器条件下,它允许数据从DIN传送到DOUT。 睡眠模式控制寄存器用于节省电源消耗,延长显示器的使用寿命。当睡眠模式控制寄存器控制字节中的最低位D0=0时,为睡眠模式;D0=1时,为正常操作模式。上电时所有的控制寄存器都复位,显示器都熄灭,芯片

MAX7219共阴极LED驱动器程序

MAX7219共阴极LED数码管显示驱动 (一)、MAX7219 MAX7219是一种串入、并出的共阴极LED数码管显示驱动器,每片可驱动8位LED数码管显示,与单片机的接口只需3根线,内带BCD译码器,及显示测试、移位、锁存器等,输出电流达40mA,外围只需一只亮度调整电阻。 MAX7219引脚图 1、引脚功能说明 DIN:串行数据输入端,CLK的上升沿时数据被载入内部16位移位寄存器中 CLK:串行时钟输入端,最高工作频率可达10MHz LOAD:片选端,低电平接收DIN端的数据,高电平时数据被所存 DIG0~7:LED的位控制端 A~DP:LED的端控制端 DOUT:串行数据输出端,用于芯片的级联 ISET:硬件亮度调整端,在该引脚与VCC之间跨接一个电阻,LED的亮度即可通过该电阻来调节,流过LED的段驱动平均电流为流过此电阻电流的100倍,此电阻值范围为:10~80K之间。 2、内部寄存器说明 A、译码方式选择寄存器地址:09H 赋值:FFH 表示使用MAX7219内部的BCD译码器 00H 表示不使用MAX7219内部的BCD译码器

B、亮度调节寄存器地址:0AH 赋值:00H~0FH 可改变MAX7219所驱动的LED的亮度,其变化范围在1/32~31/32之间 C、扫描位数设定寄存器地址:0BH 赋值:00H 所有位不显示 01H~07H 依次对应于1~8位及前面位全部显示(即需显示的位应为“1”) D、待机模式开关寄存器地址:0CH 赋值:00H LED全灭 01H LED正常显示 E、显示器测试寄存器地址:0FH 赋值:00H LED为正常显示状态 01H LED测试状态,即LED全亮 F、8位LED显示数据寄存器地址:01H~08H 对这些寄存器赋值(即需显示的内容),就会在对应的1~8位LED数码管上显示出来 3、使用注意事项 由于电源中杂波或附近的电磁等干扰信号,使MAX7219在上电后不显示或乱显示;为了消除这种现象 应在MAX7219的VCC端与地之间接一只104pf的瓷片电容,在LOAD端于地之间接一只10K的电阻。最号还在电源与MAX7219的VCC端之间串一只去高频的电感。 而在电源方面,最好使用变压器供电,而不要用开关电源供电。 加在DIN引脚上的串行数据必须在LOAD脚为低电平时,以每2字节一次,在SCK脚信号的每个上升沿移入1位数据,且高位在前低位在后,然后在LOAD信号的上升沿MAX7219所存数据。 LED数码管引脚图如下:

集成电路封装工艺

集成电路封装工艺 摘要 集成电路封装的目的,在于保护芯片不受或少受外界环境的影响,并为之提供一个发挥集成电路芯片功能的良好环境,以使之稳定,可靠,正常的完成电路功能.但是集成电路芯片封装只能限制而不能提高芯片的功能. 关键词: 电子封装封装类型封装技术器件失效 Integrated Circuit Packaging Process Abstract The purpose of IC package, is to protect the chip from the outside or less environmental impa ct, and provide a functional integrated circuit chip to play a good environment to make it stable an d reliable, the completion of the normal circuit functions. However, IC chip package and not only restricted to enhance the function of the chip. 引言 电子封装是一个富于挑战、引人入胜的领域。它是集成电路芯片生产完成后不可缺少的一道工序,是器件到系统的桥梁。封装这一生产环节对微电子产品的质量和竞争力都有极大的影响。按目前国际上流行的看法认为,在微电子器件的总体成本中,设计占了三分之一,芯片生产占了三分之一,而封装和测试也占了三分之一,真可谓三分天下有其一。封装研究在全球范围的发展是如此迅猛,而它所面临的挑战和机遇也是自电子产品问世以来所从未遇到过的;封装所涉及的问题之多之广,也是其它许多领域中少见的,它需要从材料到工艺、从无机到聚合物、从大型生产设备到计算力学等等许许多多似乎毫不关连的专家的协同努力,是一门综合性非常强的新型高科技学科。 1.电子封装 什么是电子封装(electronic packaging)? 封装最初的定义是:保护电路芯片免受周围环境的影响(包括物理、化学的影响)。所以,在最初的微电子封装中,是用金属罐(metal can) 作为外壳,用与外界完全隔离的、气密的方法,来保护脆弱的电子元件。但是,随着集成电路技术的发展,尤其是芯片钝化层技术的不断改进,封装的功能也在慢慢异化。通常认为,封装主要有四大功能,即功率分配、信号分配、散热及包装保护,它的作用是从集成电路器件到系统之间的连接,包括电学连接和物理连接。目前,集成电路芯片的I/O线越来越多,它们的电源供应和信号传送都是要通过封装来实现与系统的连接;芯片的速度越来越快,功率也越来越大,使得芯片的散热问题日趋严重;由于芯片钝化层质量的提高,封装用以保护电路功能的作用其重要性正在下降。 2.部分封装的介绍 金属封装是半导体器件封装的最原始的形式,它将分立器件或集成电路置于一个金属容器中,用镍作封盖并镀上金。金属圆形外壳采用由可伐合金材料冲制成的金属底座,借助封接玻璃,在氮气保护气氛下将可伐合金引线按照规定的布线方式熔装在金属底座上,经过引线端头的切平和磨光后,再镀镍、金等惰性金属给与保护。在底座中心进行芯片安装和在

集成电路芯片封装技术试卷

《微电子封装技术》试卷 一、填空题(每空2分,共40分) 1.狭义的集成电路芯片封装是指利用精细加工技术及,将芯片及其它要素在框架或基板上,经过布置、粘贴及固定等形成整体立体结构的工艺。 2.通常情况下,厚膜浆料的制备开始于粉末状的物质,为了确保厚膜浆料达到规定的要求,可用颗粒、固体粉末百分比含量、三个参数来表征厚膜浆料。 3.利用厚膜技术可以制作厚膜电阻,其工艺为将玻璃颗粒与颗粒相混合,然后在足够的温度/时间下进行烧结以使两者烧结在一起。 4.芯片封装常用的材料包括金属、陶瓷、玻璃、高分子等,其中封装能提供最好的封装气密性。 5.塑料封装的成型技术包括喷射成型技术、、预成型技术。 6.常见的电路板包括硬式印制电路板、、金属夹层电路板、射出成型电路板四种类型。 7. 在元器件与电路板完成焊接后,电路板表面会存在一些污染,包括非极性/非离子污染、、离子污染、不溶解/粒状污染4大类。 8. 陶瓷封装最常用的材料是氧化铝,用于陶瓷封装的无机浆料一般在其中添加玻璃粉,其目的是调整氧化铝的介电系数、,降低烧结温度。 9. 转移铸膜为塑料封装最常使用的密封工艺技术,在实施此工艺过程中最常发生的封装缺陷是现象。 10. 芯片完成封装后要进行检测,一般情况下要进行质量和两方面的检测。 11. BGA封装的最大优点是可最大限度地节约基板上的空间,BGA可分为四种类型:塑料球栅阵列、、陶瓷圆柱栅格阵列、载带球栅阵列。 12. 为了获得最佳的共晶贴装,通常在IC芯片背面镀上一层金的薄膜或在基板的芯片承载架上先植入。 13. 常见的芯片互连技术包括载带自动键合、、倒装芯片键合三种。 14. 用于制造薄膜的技术包括蒸发、溅射、电镀、。 15. 厚膜制造工艺包括丝网印刷、干燥、烧结,厚膜浆料的组分包括可挥发性组分和不挥发性组分,其中实施厚膜浆料干燥工艺的目的是去除浆料中的绝大部分。 16. 根据封装元器件的引脚分布形态,可将封装元器件分为单边引脚、双边引脚、与底部引脚四种。 17. 载带自动键合与倒装芯片键合共同的关键技术是芯片的制作工艺,这些工艺包括蒸发/溅射、电镀、置球、化学镀、激光法、移植法、叠层制作法等。 18. 厚膜浆料必须具备的两个特性,一是用于丝网印刷的浆料为具有非牛顿流变能力的粘性流体;二是由两种不同的多组分相组成,即和载体相。 19. 烧结为陶瓷基板成型的关键步骤,在烧结过程中,最常发生的现象为生胚片的现

教务系统成绩录入(教师操作及注意事项说明)

教务系统成绩录入(教师操作及注意事项说明) 一、教师使用的功能 (一)成绩录入;(二)信息维护;(三)信息查询;(四)公用信息;(五)系统维护 二、登录系统 (一)打开IE浏览器,输入成绩录入网址:https://www.360docs.net/doc/1318706967.html,,登录界面“丽水学院正方教务管理系统”,输入“用户名”和“密码”(用户名和初始密码均为职工号),选择“教师”,再点击“登录”。 (二)登录系统后,进入教师个人界面,此界面分为[返回首页] 、[成绩录入]、[信息维护]、[信息查询]、[公用信息] 5个菜单。 切记:请您务必 ..自己的初始密码 ....!!!!!! ..在[信息维护]下面的“密码修改”修改 三、成绩录入(截止时间:2012年1月11日前,届时教务处将关闭成绩录入系统) 步骤1.选择[成绩录入],查看本学期任教课程,选择并点击课程名称,显示“请输入课程密码(即为职工号)”,点击“确定”(不要直接回车)。显示“注:成绩录到一半时,请勿切换记分制,否则将导致未保存数据丢失。!!!”,点击“确定”(提示成绩录入截止时间为2012年1月11日),进入“教师成绩录入”界面。 步骤3.在成绩录入界面左上方,教师输入“平时”、“期中”、“期末”、“实验”所占的比例,不占比例的请输入0。(平时成绩比例参照《丽水学院关于课程平时成绩评定实施办法》) 步骤4.教师按百分制录入各项成绩(其中“总评成绩”可不录入,点击“保存”系统将自动生 成)(若.遇学生情况不清楚时,请到 ......“.如.缓考、作弊、旷 ....... ......核实后再录入 .....胡园园老师处 ............16212 考、取消考试资格、 ....中录入 ..”. ...总评成绩 ...“.缓考 .....”.。.则录入 .........降级、跟 ....班重修学生 ...其他成绩 ....后,在 等文字 ..)。⑴“总评成绩”栏中的成绩,可以在您点击“保存”后,系统根据您录入的各项百分制...标注 成绩和各项成绩所占的比例,自动进入总评成绩的计算并保存所有已录入成绩的记录;⑵若您已在总评栏中录入了成绩的话,系统将不再进行总评成绩的计算。 “保存”后,若需要修改平时、期中等成绩,应先点击右下方“清空总评”,取消原来已计算的总评成绩,否则系统不会自动重新计算总评成绩。 步骤5.点击“保存”后,无论您是否要进行修改,系统将会在3天内自动将成绩“提交”。为了确保安全性,建议在核对录入成绩准确无误的情况下,点击“提交”,进入成绩录入状态的锁定。 步骤6.“提交”后若要进行成绩修改,必须填写《成绩更改审批表》,由分院主管教学副院长(朱银法老师,16213)及教务处领导(胡锋吉老师,行政楼205)签字后,再送交行政楼207马亚平老师进行成绩修改,故勿轻易点击“提交”。 四、成绩录入完毕送交所有相关材料(附:任课教师送交期末试卷相关材料清单)

集成电路芯片封装技术复习题

¥ 一、填空题 1、将芯片及其他要素在框架或基板上布置,粘贴固定以及连接,引出接线端子并且通过可塑性绝缘介质灌封固定的过程为狭义封装 ;在次基础之上,将封装体与装配成完整的系统或者设备,这个过程称之为广义封装。 2、芯片封装所实现的功能有传递电能;传递电路信号;提供散热途径;结构保护与支持。 3、芯片封装工艺的流程为硅片减薄与切割、芯片贴装、芯片互连、成型技术、去飞边毛刺、切筋成形、上焊锡、打码。 4、芯片贴装的主要方法有共晶粘贴法、焊接粘贴法、导电胶粘贴发、玻璃胶粘贴法。 5、金属凸点制作工艺中,多金属分层为黏着层、扩散阻挡层、表层金保护层。 6、成型技术有多种,包括了转移成型技术、喷射成型技术、预成型技术、其中最主要的是转移成型技术。 ' 7、在焊接材料中,形成焊点完成电路电气连接的物质叫做焊料;用于去除焊盘表面氧化物,提高可焊性的物质叫做助焊剂;在SMT中常用的可印刷焊接材料叫做锡膏。 8、气密性封装主要包括了金属气密性封装、陶瓷气密性封装、玻璃气密性封装。 9、薄膜工艺主要有溅射工艺、蒸发工艺、电镀工艺、

光刻工艺。 10、集成电路封装的层次分为四级分别为模块元件(Module)、电路卡工艺(Card)、主电路板(Board)、完整电子产品。 11、在芯片的减薄过程中,主要方法有磨削、研磨、干式抛光、化学机械平坦工艺、电化学腐蚀、湿法腐蚀、等离子增强化学腐蚀等。 12、芯片的互连技术可以分为打线键合技术、载带自动键合技术、倒装芯片键合技术。 ^ 13、DBG切割方法进行芯片处理时,首先进行在硅片正面切割一定深度切口再进行背面磨削。 14、膜技术包括了薄膜技术和厚膜技术,制作较厚薄膜时常采用丝网印刷和浆料干燥烧结的方法。 15、芯片的表面组装过程中,焊料的涂覆方法有点涂、 丝网印刷、钢模板印刷三种。 16、涂封技术一般包括了顺形涂封和封胶涂封。 二、名词解释 1、芯片的引线键合技术(3种) ] 是将细金属线或金属带按顺序打在芯片与引脚架或封装基板的焊垫上而形成电路互连,包括超声波键合、热压键合、热超声波键合。 2、陶瓷封装

学生成绩管理系统用户操作手册

学生成绩管理系统用户操作手册 1、引言 1.1编写目的 编写用户操作说明手册的目的是使用户能够更为清楚,便捷的使用学生成绩管理 系统软件,减少用户研究该系统使用方法的时间,能够更快的掌握该软件的使用。 1.2参考资料 《软件工程理论与实践》肖汉主编科学出版社2006年7月出版 2、软件概述 该软件用于各大高校的学生成绩管理,实现了学生成绩管理的计算机智能化,主要功能针对学生成绩记录的添加,查询,删除,修改,保存。 3、运行环境 基本配置:? 服务器:Pentium 4 1.2GHz,256M内存,Windows2000Advanced Server。 客户机: Pentium 41GHz,256M内存,Windows XP Professional。 4、使用说明: 4.1 操作简要说明 这个程序的使用方法是先选择功能1创建链表,输入学生的学号、班级、姓名和成绩等数据,系统自动计算总成绩和平均成绩,或选择功能8输入完整的文件名载入已有的文件,选择功能2插入新的记录到动态链表中,然后即可按学号在动态链表中进行查寻和显示(功能4)、修改(功能5)、删除(功能6)某一学生的数据。如果要保存新输入、新插入或新修改的数据,可返回主菜单选择功能7,然后直接输入文件名,文件名可以没有后缀名(如data)或可以是任意后缀名(如data.txt或data.bin),则将在程序当前目录中建立一个二进制文件,或者输入绝对路径(如D:\1.txt)则系统将在你输入的路径下保存文件。 4.2操作说明及步骤: ⑴提示输入密码.JPG ⑵输错三次密码则自动退出系统.jpg

⑶正确输入密码则进入系统界面.jpg

芯片封装种类

1、BGA(ball grid array) 球形触点陈列,表面贴装型封装之一。在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。也称为凸点陈列载体(PAC)。引脚可超过200,是多引脚LSI 用的一种封装。封装本体也可做得比QFP(四侧引脚扁平封装)小。例如,引脚中心距为1.5mm 的360 引脚BGA 仅为 31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP 为40mm 见方。而且BGA 不用担心QFP 那样的引脚变形问题。该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。最初,BGA 的引脚(凸点)中心距为1.5mm,引脚数为225。现在也有一些LSI 厂家正在开发500 引脚的BGA。BGA 的问题是回流焊后的外观检查。现在尚不清楚是否有效的外观检查方法。有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。美国Motorola 公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC 和GPAC)。 2、BQFP(quad flat package with bumper) 带缓冲垫的四侧引脚扁平封装。QFP 封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形。美国半导体厂家主要在微处理器和ASIC 等电路中采用此封装。引脚中心距0.635mm,引脚数从84 到196 左右(见QFP)。 3、碰焊PGA(butt joint pin grid array) 表面贴装型PGA 的别称(见表面贴装型PGA)。 4、C-(ceramic) 表示陶瓷封装的记号。例如,CDIP 表示的是陶瓷DIP。是在实际中经常使用的记号。 5、Cerdip 用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。带有玻璃窗口的Cerdip 用于紫外线擦除型EPROM 以及内部带有EPROM 的微机电路等。引脚中心距2.54mm,引脚数从8 到42。在日本,此封装表示为DIP-G(G 即玻璃密封的意思)。 6、Cerquad 表面贴装型封装之一,即用下密封的陶瓷QFP,用于封装DSP 等的逻辑LSI 电路。带有窗口的Cerquad 用于封装EPROM 电路。散热性比塑料QFP 好,在自然空冷条件下可容许1. 5~2W 的功率。但封装成本比塑料QFP 高3~5 倍。引脚中心距有1.27mm、0.8mm、0.65mm、0.5mm、0.4mm 等多种规格。引脚数从32 到368。 7、CLCC(ceramic leaded chip carrier) 带引脚的陶瓷芯片载体,表面贴装型封装之一,引脚从封装的四个侧面引出,呈丁字形。带有窗口的用于封装紫外线擦除型EPROM 以及带有EPROM 的微机电路等。此封装也称为QFJ、QFJ-G(见QFJ)。 8、COB(chip on board) 板上芯片封装,是裸芯片贴装技术之一,半导体芯片交接贴装在印刷线路板上,芯片与基板的电气连接用引线缝合方法实现,芯片与基板的电气连接用引线缝合方法实现,并用树脂覆盖以确保可靠性。虽然COB 是最简单的裸芯片贴装技术,但它的封装密度远不如TAB 和倒片焊技术。 9、DFP(dual flat package) 双侧引脚扁平封装。是SOP 的别称(见SOP)。以前曾有此称法,现在已基本上不用。10、DIC(dual in-line ceramic package) 陶瓷DIP(含玻璃密封)的别称(见DIP). 11、DIL(dual in-line)