可调时分秒电子钟

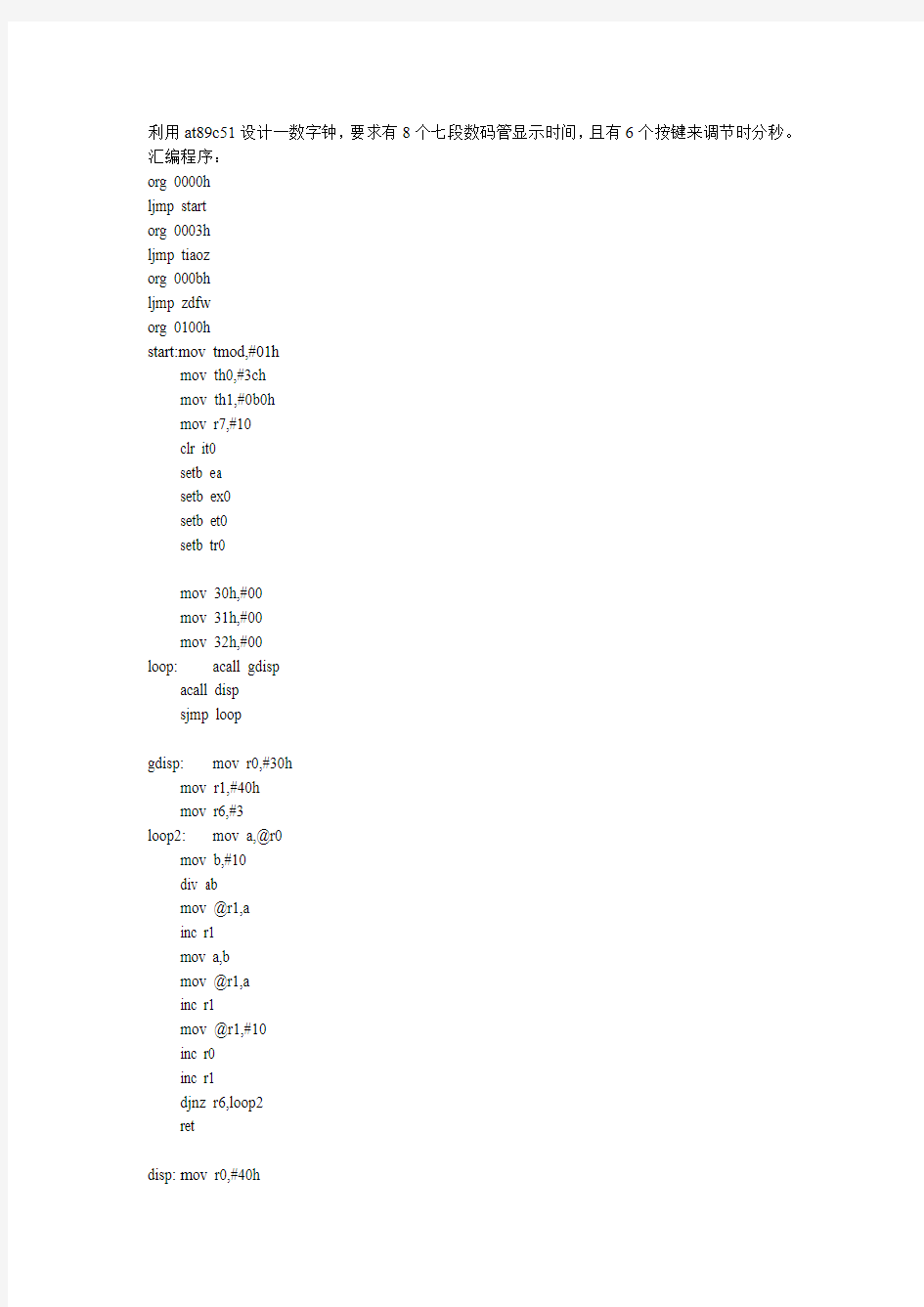

利用at89c51设计一数字钟,要求有8个七段数码管显示时间,且有6个按键来调节时分秒。汇编程序:

org 0000h

ljmp start

org 0003h

ljmp tiaoz

org 000bh

ljmp zdfw

org 0100h

start:mov tmod,#01h

mov th0,#3ch

mov th1,#0b0h

mov r7,#10

clr it0

setb ea

setb ex0

setb et0

setb tr0

mov 30h,#00

mov 31h,#00

mov 32h,#00

loop: acall gdisp

acall disp

sjmp loop

gdisp: mov r0,#30h

mov r1,#40h

mov r6,#3

loop2: mov a,@r0

mov b,#10

div ab

mov @r1,a

inc r1

mov a,b

mov @r1,a

inc r1

mov @r1,#10

inc r0

inc r1

djnz r6,loop2

ret

disp: m ov r0,#40h

mov dptr,#stab

mov r3,#8

loop3: mov a,r2

mov p2,a

mov a,@r0

movc a,@a+dptr

mov p0,a

acall delay

mov a,r2

rl a

mov r2,a

inc r0

djnz r3,loop3

ret

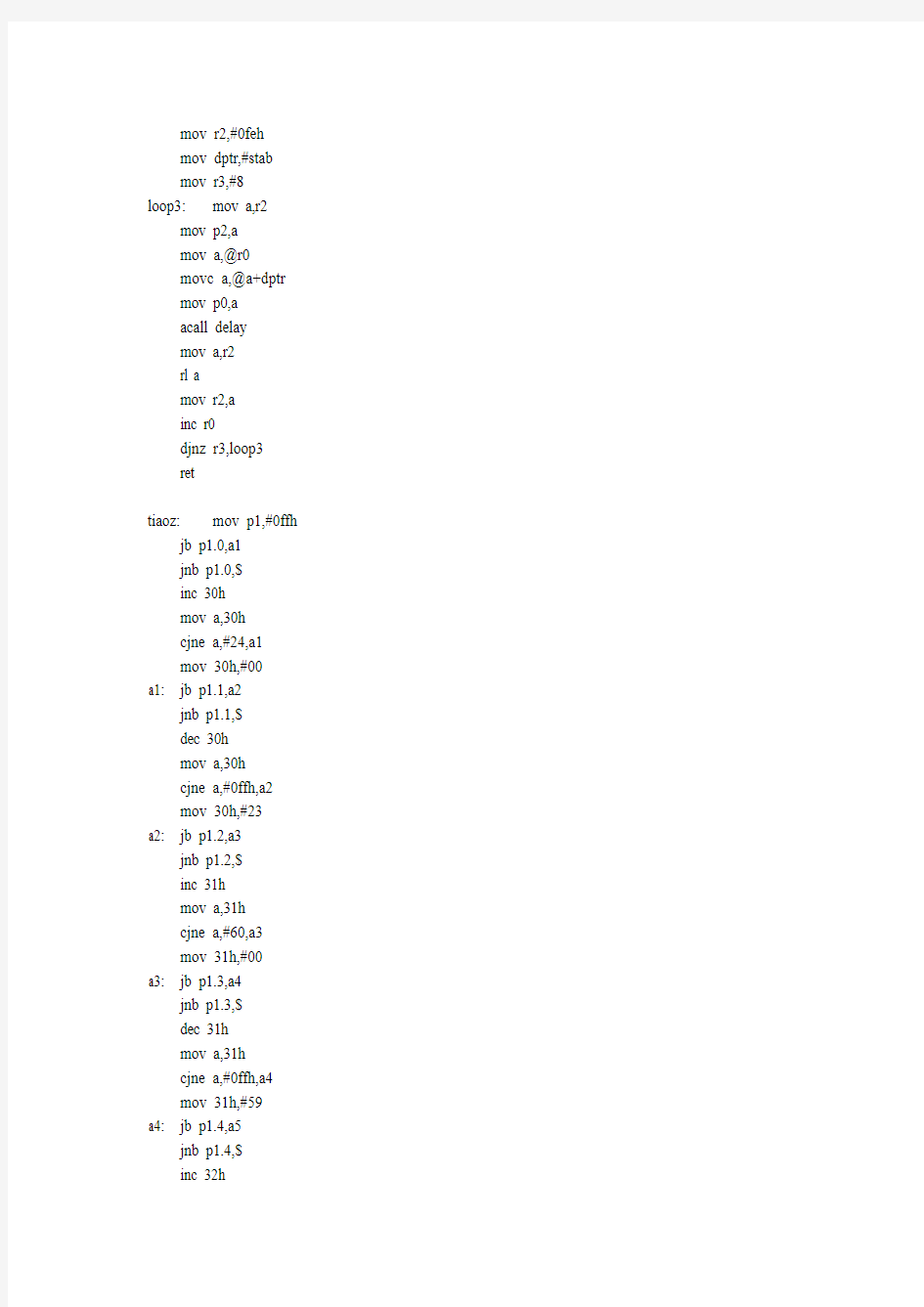

tiaoz: mov p1,#0ffh jb p1.0,a1

jnb p1.0,$

inc 30h

mov a,30h

cjne a,#24,a1

mov 30h,#00

a1: jb p1.1,a2

jnb p1.1,$

dec 30h

mov a,30h

cjne a,#0ffh,a2

mov 30h,#23

a2: jb p1.2,a3

jnb p1.2,$

inc 31h

mov a,31h

cjne a,#60,a3

mov 31h,#00

a3: jb p1.3,a4

jnb p1.3,$

dec 31h

mov a,31h

cjne a,#0ffh,a4

mov 31h,#59

a4: jb p1.4,a5

jnb p1.4,$

inc 32h

cjne a,#60,a5

mov 32h,#00

a5: jb p1.5,a6

jnb p1.5,$

dec 32h

mov a,32h

cjne a,#0ffh,a6

mov 32h,#59

a6: reti

zdfw: mov th0,#3ch

mov th1,#0b0h

djnz r7,endi

mov r7,#10

inc 32h

mov a,32h

cjne a,#60,endi

mov 32h,#00

inc 31h

mov a,31h

cjne a,#60,endi

mov 31h,#00

inc 30h

mov a,30h

cjne a,#24,endi

mov 30h,#00

endi:reti

delay: mov r5,#5

c1: mov r4,#200

c2: djnz r4,c2

djnz r5,c1

ret

stab: db 3fh,06h,5bh,4fh,66h db 6dh,7dh,07h,7fh,6fh

db 40h

end

proteus电路图:

数字电子时钟设计

电子技术课程设计 数字电子时钟的设计 摘要: 设计一个周期为24小时,显示满刻度为23时59分59秒,具有校时功能和报时功能的电子钟。本系统的设计电路由时钟译码显示电路模块、脉冲逻辑电路模块、时钟脉冲模块、整电报时模块、校时模

块等部分组成。计数器采用异步双十进制计数器74LS90,发生器使用石英振荡器,分频器4060CD及双D触发器74LS74D,整电报时电路用门电路及扬声器构成。 一、设计的任务与要求 电子技术课程设计的主要任务是通过解决一,两个实际问题,巩固和加深在“模拟电子技术基础”和“数字电子技术基础”课程中所学的理论知识和实验技能,基本掌握常用电子电路的一般设计方法,提高电子电路的设计和实验能力,为以后从事生产和科研工作打下一定的基础。电子技术课程设计的主要内容包括理论设计、仿真实验、安装与调试及写出设计总结报告。衡量课程设计完成好坏的标准是:理论设计正确无误;产品工作稳定可靠,能达到所需要的性能指标。 本次课程设计的题目是“多功能数字电子钟电路设计”。要求学生运用数字电路,模拟电路等课程所学知识完成一个实际电子器件设计。 二、设计目的 1、让学生掌握组合逻辑电路、时序逻辑电路及数字逻辑电路系统 的设计、安装、测试方法; 2、进一步巩固所学的理论知识,提高运用所学知识分析和解决实 际问题的能力; 3、提高电路布局﹑布线及检查和排除故障的能力; 4、培养书写综合实验报告的能力。

三、原理方框图如下 1、图中晶体振荡电路由石英32.768KHZ及集成芯。 2、图中分频器4060BD芯片及D触发器构成分频器。 3、计数器由二——五——十73LS90芯片构成。 4、图中DCD_HEX显示器用七段数码显示器且本身带有译码器。 5、图中校时电路和报时电路用门电路构成。 四、单元电路的设计和元器件的选择 1、十进制计数电路的设计 74LS90集成芯片是二—五—十进制计数器,所以将INB与QA 相连;R0(1)、R0(2)、R9(1)、R9(2)接地(低电平);INA

利用CPLD设计可调时数字钟

利用C P L D设计可调时 数字钟 The Standardization Office was revised on the afternoon of December 13, 2020

数字电路课程设计 题目:利用CPLD 设计可调时数字钟 学院电子信息工程学院 专业 学号 姓名 教师 装 订 线

基于CPLD数字时钟设计 摘要 本次课程设计是用数字电路知识以及MaxplusⅡ软件进行的制作,首先理解电路原理图,然后进行了焊接,本次焊接增加自己的动手能力。然后对数字电路书又进行了复习,最后应用MaxplusⅡ软件进行了编程。 电路通过使用数字元件,来构成完成二十四小时的数字钟设计,并且将译码器和数据选择器配合使用来完成动态的显示输出。此外,外部控制开关用来控制电路,使得该电路可以完成保持、清零、快速校对时间等一系列的功能。本系统的难点在于EDA系统作图及最后系统优化的应用。尤其是小数点的显示控制,用一个或门,通过1Hz来控制第三个数码管的点显示,再通过一个与非门来控制第五个数码管的点显示,第五个数码管的点在整个脉冲阶段显示,而第三个数码管的点只有在低电平时显示,以达到结果是第五个数码显示管的点常亮,而第三个数码管的点以1Hz的频率闪烁。 制作中经常遇到各种问题,如第一次用的七段译码器显示六和九时,显示的不是很好,就重新自己做的译码器,让其显示的比较完美,而且也出现了制作的程序太大问题,最后不断的修改终于成功了。 关键词:数字电路MaxplusⅡ七段译码器

目录 设计要求.............................................. 设计原理.............................................. 电源电路........................................... 显示电路........................................... 二各模块说明........................................ 设计思路及步骤........................................ 总体框图.............................................. 各模块说明............................................ 段译码显示电路..................................... 时间计数器电路..................................... 数据选择器电路..................................... 译码器电路......................................... 比较器电路......................................... 按键消抖电路....................................... 数字钟电路总图........................................ 三课程总结............................................ 遇到的问题及其解决办法................................ 收获与体会............................................

用LCD设计的可调式电子钟

单片机应用 课程设计说明书 用1602LCD设计的可调式电子钟专业自动化 学生姓名 班级自动化142 学号 14100 指导教师蒋 完成日期 20年1 月23 日

目录 1 概述.......................................................................................... 错误!未指定书签。 2 课题研究背景与意义...................................................................... 错误!未指定书签。 2.1 课题研究背景....................................................................... 错误!未指定书签。 2.2 课题研究意义....................................................................... 错误!未指定书签。 3 系统方案设计与主要设计工作 ..................................................... 错误!未指定书签。 3.1 设计任务............................................................................... 错误!未指定书签。 3.2 功能要求说明....................................................................... 错误!未指定书签。4设计课题总体方案........................................................................... 错误!未指定书签。 4.1硬件设计方案........................................................................ 错误!未指定书签。 4.2系统软件设计........................................................................ 错误!未指定书签。 5. 软件仿真及实物设计调试 ........................................................... 错误!未指定书签。 5.1PROTUES仿真软件介绍 ......................................................... 错误!未指定书签。 5.2仿真运行结果说明 ............................................................... 错误!未指定书签。 5.3实物设计结果与调试 ........................................................... 错误!未指定书签。6课程设计实验总结........................................................................... 错误!未指定书签。参考文献.............................................................................................. 错误!未指定书签。附录.............................................................................................. 错误!未指定书签。 附录1:程序清单........................................................................ 错误!未指定书签。 附录2:系统电路原理图 ........................................................... 错误!未指定书签。 附录3:元器件清单.................................................................... 错误!未指定书签。

整点报时可调式数字电子时钟的设计

用EDA软件实现整点报时数字式可调电子时钟的设计 一、设计目的 了解常见中规模数字集成电路的使用方法,包括计数器、显示译码器、多谐振荡器的工作原理及使用方法。通过组装具有整点报时数字可调电子时钟,了解这类电路的使用技巧及调整方法。通过对电路板的实际布线焊接检测调试,提高电子技术硬件的基本能力。 二、系统组成 1、先用Multisim实现如下系统: 本组合电路包括时基多谐振荡器、计数器、十进制译码显示器、发光数码管等部分组成。各部分组成框图如下: 系统组成图 2、仿真通过 三、单元电路组成原理与参数选择 1、多谐振荡器:这里采用最常见的时基电路555组成的周期为1秒的振荡器。555集成电路的原理及应用可以参见教材,此不重复。通常选择适当的定时电阻和电容元件使振荡刚好为1秒钟。多谐振荡器的电路图和NE555的芯片引脚图如下:

2、十进制计数器: 本系统采用的是十进制计数器7490。本系统秒钟是用两个7490构成60进制组成。分钟也是用两个7490构成60进制组成时钟采用两个7490构成24进制计数器组成。将三个计数器级连起来就构成了电子时钟。7490的芯片图和真值表如下:(5脚接电源VCC,10脚接地其中1脚和12脚相连)。 X 0 0 X COUNT 下面介绍秒钟和分钟连接方法如下图(如果是秒钟14脚则接多谐振荡器555电路的第3脚,如果是分钟14脚则接秒钟的7408(与门)芯片的第3脚。

下面介绍时钟的接法(14脚接分钟的7408的第3脚): 3、7448实现多位数字码显示译(如果是选用共阳极七段数码管则选择7447) 7448为七段译码显示器,其功能可详细参见数字电路书。它实现的功能是把7490输出 的(QA、QB、QC、QD)实现译码驱动七段共阴极数码显示它的接法如下:

时钟可调时间可报时程序

///////////////////////////////////////////////////////// // 工程名称:可调时报时电子钟 // 使用描述: // K1 按一次进入时间调整模块调完后,再按一次恢复时间 // K2 非时间调整模式下,按键报时时间调整模块下,按键选择调整秒分时 // K3 时间调整模块下,时间值增加 // K4 时间调整模块下,时间值减小 // 硬件连接:IOA0~IOA7接SEG IOA8~IOA15接1*8KEY // IOB0~IOB7接DIG 2*4KEY.D_dp接高电平 // 维护记录:2012-8-15 增加时间调整功能,增加报时功能 // /////////////////////////////////////////////////////////// #include "spce061a.h" #include "Sound.h" #include "Clock_Speech.h" //定义各种宏 #define P_IOA_Data (volatile unsigned int *)0x7000 #define P_IOA_Buffer (volatile unsigned int *)0x7001 #define P_IOA_Dir (volatile unsigned int *)0x7002 #define P_IOA_Attrib (volatile unsigned int *)0x7003 #define P_IOB_Data (volatile unsigned int *)0x7005 #define P_IOB_Buffer (volatile unsigned int *)0x7006 #define P_IOB_Dir (volatile unsigned int *)0x7007 #define P_IOB_Attrib (volatile unsigned int *)0x7008 #define P_Watchdog_Clear (volatile unsigned int *)0x7012 #define P_INT_Ctrl (volatile unsigned int *)0x7010 #define P_INT_Clear (volatile unsigned int *)0x7011 #define uint unsigned int #define KEY_ALL 0xff00 int DispTbl[10] = { 0x003F,0x0006,0x005B,0x004F,0x0066, 0x006D,0x007D,0x0007,0x007F,0x006F}; uint sec=0,min=0,hour=0; uint Start_End_Flag=0; uint Adjust_Wei=4; uint flag=1;

数字电子钟设计说明..

数字电子钟课程设计 一、设计任务与要求 (1)设计一个能显示时、分、秒的数字电子钟,显示时间从00: 00: 00到23: 59: 59; (2)设计的电路包括产生时钟信号,时、分、秒的计时电路和显示电路(3)电 路能实现校正 (5)整点报时 二、单元电路设计与参数计算 1. 振荡器 石英晶体振荡器的特点是振荡频率准确、电路结构简单、频率易调整。它还具有压电效应,在晶体某一方向加一电场,则在与此垂直的方向产生机械振动,有 了机械振动,就会在相应的垂直面上产生电场,从而机械振动和电场互为因果,这种循环过程一直持续到晶体的机械强度限止时,才达到最后稳定。这用压电谐振的频率即为晶体振荡器的固有频率。 2. 分频器 由于振荡器产生的频率很高,要得到秒脉冲需要分频,本实验采用一片74LS90 和两片74LS160实现,得到需要的秒脉冲信号。

3. 计数器 秒脉冲信号经过计数器,分别得到“秒”个位、十位、“分”个位、十位以及 “时”个位、十位的计时。“秒” “分”计数器为六十进制,小时为二十四进制。 (1)六十进制计数 由分频器来的秒脉冲信号,首先送到“秒”计数器进行累加计数,秒计数器应完 成一分钟之内秒数目的累加,并达到 60秒时产生一个进位信号。本作品选用一 片74LS161和一片74LS160采取同步置数的方式组成六十进制的计数器。 (2)二十四进制计数 “24翻1”小时计数器按照“ 00— 01—02,, 22—23— 00—01”规律计数。与生 活中计数规律相同。二十四进制计数同样选用74LS161和74LS160计数芯片。但 清零方式采用的是异步清零方式。 MMgM 加 EHagij Z 1 进位信号 脉冲

基于单片机的可调电子钟的设计说明

编号: 基础工程设计 题目:基于单片机设计的可调电子时钟院(系):信息与通信学院 专业:微电子科学与工程 学生姓名:卢镜 学号:1300240119 指导教师:宋保林

2016 年 1 月 6 日 摘要 本人设计的是一个以单片机STC89C52为核心部件的电子钟,结合LCD液晶显示屏。可以在液晶屏上显示时间和字符,并可任意调整时间。本来想用数码管来显示,但是想到数码管仅能显示数字,所以采用了液晶显示屏。它不仅能显示数字,还能显示字符。它的计时周期为24小时,显满刻度为“23时59分59秒”。 文中详细论述了可调电子钟设计原理、使用的各芯片的介绍,阐明了本实例所使用的设计方案、详细的电路图以及程序。本文编写的主导思想是软硬件相结合,以硬件为基础,来进行各功能模块的编写。本系统以单片机的C语言进行软件设计,并着重介绍了所应用的各硬件接口技术和各个接口模块的功能及工作过程,其次,详细阐述了程序的各个模块和实现过程,并且还进行了软件仿真调试和硬件调试。 关键词:单片机STC89C52 ;可调电子钟;液晶显示;仿真

目录 摘要 (1) 前言 (3) 第一章设计说明 (5) 1.1 设计目的和内容 (5) 1.2 设计方案选择 (5) 1.3 设计总体框图 (7) 第二章系统主要硬件设计 (5) 2.1 单片机主控模块 (7)

2.1.1 STC89C52芯片简介 (7) 2.1.2 封装和引脚说明 (8) 2.2 液晶显示模块 (7) 2.2.1 LCD1602模块简介 (11) 2.2.2 LCD1602的控制指令及操作流程 (12) 2.3时钟电路及按键电路 (9) 2.3.1时钟电路 (9) 2.3.2按键电路 (10) 第三章系统软件设计 (10) 3.1 系统程序流程图 (10) 3.2系统程序设计电子时钟清单 (11) 第四章系统调试 (12) 4.1软件调试 (12) 4.2源代码 (14) 4.3硬件调试 (20) 4.3.1原理图 (20) 4.3.2 PCB图 (20) 4.3.3用跳线修改电路 (21) 结语 (21) 谢辞 (22) 参考文献 (23) 附录Ⅰ (24)

数字电子时钟逻辑电路设计

《数字逻辑》 课程设计报告 设计题目:数字电子钟 组员:冯燕升、吴永涛、卓小林、蔡卿指导老师:麦山 日期:2013/12/27

摘要数字电子钟是一种用数字显示秒、分、时的计时装置,本次数字时钟电路设计采用GAL系列芯片来分别实现时、分、秒的24进制和60进制的循环电路,并支持手动校正的功能。 关键词数字电子钟;计数器;GAL 1设计任务及其工作原理 用集成电路设计一台能自动显示时、分、秒的数字电子钟,只要将开关置于手动位置,可分别对秒、分、时进行手动脉冲输入调整或连续脉冲输入的校正。 1.1工作原理 本数字电子钟的设计是根据时、分、秒各个部分的的功能的不同,分别用GAL16V8D 设计成六十进制计数器,个位设计成十进制计数器,十位设计成六进制进制计数器(计数从00到59时清零并向前进位)。分部分的设计与秒部分的设计完全相同;用GAL22V10D设计时的个位,设计成二进制计数器,十位设计为四进制计数器,当时钟计数到23时59分59秒时,使计数器的小时部分清零,进而实现整体循环计时的功能。 2电路的组成 2.1 计数器部分:利用GAL22V10和GAL16V8D芯片分别组成二十四进制计数器和六十进制计数器,它们采用同步连接,利用外接标准脉冲信号进行计数。 2.2 显示部分:将三片GAL芯片对应的引脚分别接到实验箱上的七段共阴数码显示管上,根据脉冲的个数显示时间。 3.3 分频器:由于实验箱上提供的时钟脉冲的时间间隔太小,所以使用GAL16V8D和CD4040芯片设计一个分频器,使连续输出脉冲信号时间间隔为0.5s 3设计步骤及方法 3.1 分和秒部分的设计: 分和秒部分的设计是采用GAL16V8D芯片来设计的60进制计数器,具体设计如图1示:

电子时钟课程设计_数电课程设计数字电子时钟的实现

电子时钟课程设计_数电课程设计数字电子 时钟的实现 课程设计报告设计题目:数字电子时钟的设计与实现班级: 学号: 姓名: 指导教师: 设计时间: 摘要钟表的数字化给人们生产生活带来了极大的方便,大大的扩展了原先钟表的报时。诸如,定时报警、按时自动打铃、时间程序自动控制等,这些,都是以钟表数字化为基础的。功能数字钟是一种用数字电路实现时、分、秒、计时的装置,与机械时钟相比具有更高的准确性和直观性,且无机械装置,具有更长的使用寿命,因此得到了广泛的使用。从原理上讲,数字钟是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。 因此,此次设计与制作数字钟就是为了了解数字钟的原理,从而学会制作数字钟,而且通过数字钟的制作进一步的了解各种在制作中用到的中小规模集成电路的作用及使用方法。通过此次课程设计可以进一步学习与各种组合逻辑电路与时序电路的原理与使用方法。通过仿真过程也进一步学会了Multisim 7的使用方法与注意事项。

本次所要设计的数字电子表可以满足使用者的一些特殊要求,输 出方式灵活,如可以随意设置时、分、秒的输出,定点报时。由于集 成电路技术的发展,,使数字电子钟具有体积小、耗电省、计时准确、 性能稳定、维护方便等优点。 关键词:数字钟,组合逻辑电路,时序电路,集成电路目 录摘要 (1) 第1章概述 (3) 第2章课程设计任务及要求 (4) 2.1设计任务 (4) 2.2设计要求 (4) 第3章系统设计 (6) 3.1方案论证 (6) 3.2系统设计 (6) 3.2.1 结构框图及说明 (6) 3.2.2 系统原理图及工作原理 (7) 3.3单元电路设计 (8) 3.3.1 单元电路工作原理 (8) 3.3.2 元件参数选择···································14 第 4章软件仿真 (15) 4.1仿真电路图 (15) 4.2仿真过程 (16)

数字电子钟设计报告

《电子线路课程设计报告》 系别:自动化 专业班级:自动化0803 学生姓名:冯刚 指导教师:朱定华 (课程设计时间:2010年05月31日——2010年06月12日) 华中科技大学武昌分校

目录 1.课程设计目的 (3) 2.课程设计题目描述和要求 (3) 3.课程设计报告内容.....................................................................3-9 3.1实验名称 (3) 3.2实验目的 (3) 3.3实验器材及主要器件 (3) 3.4数字电子钟基本原理 (4) 3.5数字电子钟单元电路设计、参数计算和器件选择..............................4-8 3.6数字电子钟电路图 (8) 3.7数字电子钟的组装与调试............................................................8-9 4.总结 (9) 参考文献 (10)

1.课程设计目的 ※掌握组合逻辑电路、时序逻辑电路及数字逻辑电路系统的设计、安装、测试方法; ※进一步巩固所学的理论知识,提高运用所学知识分析和解决实际问题的能力;※提高电路布局﹑布线及检查和排除故障的能力; ※培养书写综合实验报告的能力。 2.课程设计题目描述和要求 (1)设计一个有“时”、“分”、“秒”(12小时59分59秒)显示,且有校时功能的电子钟; (2)用中小规模集成电路组成电子钟,并在实验箱上进行组装、调试; (3)画出框图和逻辑电路图,写出设计、实验总结报告; (4)选做:整点报时。在59分51秒、53秒、55秒、57秒输出500Hz音频信号,在59分59秒时输出1000Hz信号,音频持续1s,在1000Hz荧屏结束时刻为整点。 3.课程设计报告内容 3.1实验名称 数字电子钟 3.2实验目的 ·掌握数字电子钟的设计、组装与调试方法; ·熟悉集成电路的使用方法。 3.3实验器材及主要器件 (1)74LS48(6片)(2)74LS90(5片)(3)74LS191(1片)(4)74LS00(5片)(5)74LS04(3片)(6)74LS74(1片)(7)74LS2O(2片) (8)555集成芯片(1片) (9)共阴七段显示器(6片)(10)电阻、电容、导线等(若干)

多功能数字钟电路设计

多功能数字钟电路设计 一、数字电子钟设计摘要 (2) 二、数字电子钟方案框图 (2) 三、单元电路设计及相关元器件的选择 (3) 1.6进制计数器电路的设计 (3) 2.10进制计数器电路的设计 (4) 3.60进制计数器电路的设计 (4) 4.时间计数器电路的设计 (5) 5.校正电路的设计 (6) 6.时钟电路的设计 (7) 7.整点报时电路设计 (8) 8. 译码驱动及单元显示电路 (9) 四、系统电路总图及原理 (9) 五、经验体会 (10) 六、参考文献 (10) 附录A:系统电路原理图 附录B:元器件清单

一、数字电子钟设计摘要 数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。数字钟从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。 此次设计数字钟就是为了了解数字钟的原理,从而学会制作数字钟。而且通过数字钟的制作进一步的了解各种在制作中用到的中小规模集成电路的作用及实用方法。且由于数字钟包括组合逻辑电路和时叙电路。通过它可以进一步学习与掌握各种组合逻辑电路与时序电路的原理与使用方法。 二、数字电子钟方案框图 图1 数字电子钟方案框图

三、单元电路设计和元器件的选择 1. 6进制计数器电路的设计 现要设计一个6进制的计数器,采用一片中规模集成电路74LS90N芯片,先接成十进制,再转换成6进制,利用“反馈清零”的方法即可实现6进制计数,如图2所示。 图2

2. 10进制电路设计 图3 3. 60 进数器电路的设计 “秒”计数器与“分”计数器都是六十进制,它由一级十进制计数器和一级六进制计数器连接而成,如图4所示,采用两片中规模集成电路74LS90N串接起来构成“秒”“分”计数器。

51单片机简易可调的数码管电子钟程序

#include

数字电子时钟课程设计

数字电子技术基础课程设计报告 班级:姓名: 学号: 一、设计目的 1掌握专业基础知识的综合能力。 2完成设计电路的原理设计、故障排除。 3逐步建立电子系统的研发、设计能力,为毕业设计打好基础。 4让学生掌握组合逻辑电路、时序逻辑电路及数字逻辑电路系统的设计、安装、测试方法。 5进一步巩固所学的理论知识,提高运用所学知识分析和解决实际问题的能力。 6培养书写综合实验报告的能力。 二、设计仪器 1 LM555CH 2 74LS161N 74LS160N 74LS290 3 74LS00 74LS08 4 电源电阻电容二极管接地等 三数字电子钟的基本功能及用途 现在数字钟已成为人们日常生活中:必不可少的必需品,广泛用于个人家庭以及车站、码头、剧场、办公室等公共场所,给人们的生活、学习、工作、娱乐带来极大的方便。由于数字集成电路技术的发展和采用了先进的石英技术,使数字钟具有走时准确、性

能稳定、集成电路有体积小、功耗小、功能多、携带方便等优点,,因此在许多电子设备中被广泛使用。 电子钟是人们日常生活中常用的计时工具,而数字式电子钟又有其体积小、重量轻、走时准确、结构简单、耗电量少等优点而在生活中被广泛应用,因此本次设计就用数字集成电路和一些简单的逻辑门电路来设计一个数字式电子钟,使其完成时间及星期的显示功能。 多功能数字钟采用数字电路实现对“时”、“分”、“秒”数字显示的计时装置。具有时间显示、走时准确、显示直观、精度、稳定等优点。电路装置十分小巧,安装使用也方便。同时在日期中,它以其小巧,价格低廉,走时精度高,使用方便,功能多,便于集成化而受广大消费的喜爱。 四设计原理及方框图 数字钟实际上是一个对标准频率进行计数的计数电路,标准的1HZ时间信号必须做到准确稳定。由图可见:本数字钟电路主要由震荡器、、时分秒计数器、译码显示器构成。它们的工作原理是:由震荡器产生的高频脉冲信号作为数字钟的时间基准,送入秒计数

基于proteus的数字电子钟的仿真设计

题目:基于Proteus的数字电子钟的设计 与仿真 课程名称:单片机系统设计与Proteus仿真 学生姓名:马珂 学生学号: 1305010323 系别:电子工程学院 专业:通信工程 年级: 13级 任课教师:徐锋 电子工程学院 2015年5月

目录 一、设计目的与要求 (3) 二、设计内容与方案制定 (3) 三、设计步骤 (3) 1.硬件电路设计 (3) 1.1.硬件电路组成框图 (3) 1.2.各单元电路及工作原理 (4) 1.3.绘制原理图 (5) 1.4.元件清单列表 (6) 2.程序设计 (6) 2.1程序流程 (6) 2.2汇编程序 (7) 四、调试与仿真 (12) 五、心得体会 (14) 六、参考文献: (14)

基于Proteus的数字电子钟的设计与仿真 一、设计目的与要求 设计目的:通过课程设计,培养学生运用已学知识解决实际问题的能力、查阅资料的能力、自学能力和独立分析问题、解决问题的能力和能通过独立思考。 设计要求:设计一个时、分可调的数字电子钟、开机显示“9-58-00”。 二、设计内容与方案制定 具有校时功能,按键控制电路其中时键、分键两个键分别控制时、分时间的调整。按分键分加1;按时键时加1。 以AT89C51单片机进行实现秒、分、时上的正常显示和进位,其中显示功能由单片机控制共阴极数码管来实现,数码管进行动态显示。 三、设计步骤 1、硬件电路设计 1.1.硬件电路组成框图 1.2.各单元电路及工作原理 (1)晶振电路 单片机的时钟产生方法有两种:内部时钟方式和外部时钟方式。本系统中

AT89C51单片机采用内部时钟方式。采用外接晶体和电容组成的并联谐振回路。其电路图如下: (2)键盘控制电路 键盘可实现对时间的校对,用两个按键来实现。按时键来调节小时的时间,按分键来调节分针的时间。其电路连接图如下: (3)显示电路 LED显示器是现在最常用的显示器之一发光二极管(LED)分段式显示器由7条线段围成8字型,每一段包含一个发光二极管。外加正向电压时二极管导通,发出清晰的光。只要按规律控制各发光段亮、灭,就可以显示各种字形或符号。显示电路显示模块需要实时显示当前的时间,即时、分、秒,因此需要6个数码管,采用动态显示方式显示时间,其硬件连接方式如下图所示。

数字电子钟设计方案

一、设计方案 1、总体设计方案说明及系统框图: 数字钟是计时周期为24小时,显示满刻度为23时59分59秒,另外应有校时功能和报时功能。一个基本的数字钟电路主要由译码显示器、“时”,“分”,“秒”计数器、校时电路、报时电路和振荡器组成。干电路系统由秒信号发生器、“时、分、秒”计数器、译码器及显示器、校时电路、整点报时电路组成。秒信号产生器是整个系统的时基信号,它直接决定计时系统的精度,一般用石英晶体振荡器加分频器来实现。将标准秒信号送入“秒计数器”,“秒计数器”采用60进制计数器,每累计60秒发现胡一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。“分计数器”也采用60进制计数器,每累计60分钟,发出一个“时脉冲”信号,该信号将被送到“时计数器”。“时计数器”采用24进制计时器,可实现对一天24小时的累计。译码显示电路将“时”、“分”、“秒”计数器的输出状态菁七段显示译码器译码,通过LED显示器显示出来。整点报时电路时根据计时系统的输出状态产生一脉冲信号,控制信号灯亮灭周期。由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的1HZ时间信号必须做到准确稳定。通常使用石英晶体振荡器电路构成数字钟。校时电路时用来对“时”、“分”、“秒”显示数字进行校对调整的。数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。数字电子钟的总体框图如下图所示。 系统框图: 2、单元电路设计方案: 1)振荡器和分频器 振荡器的作用是产生时间标准信号。数字钟的精度就是主要取决于时间标准信 的频率和稳定度。所以,在实验中采用脉冲信号作为时间标准信号源。 2)计数器 根据计数周期分别组成两个60进制(秒、分)和一个24进制(时)的计数器。把它们适当连接构成秒、分、时的计数,(分计数器中分的个位和十位计数单元的状态转换和秒计数器

自制可调式数字时钟完整版

《综合设计实训I》可调式数字时钟 姓名: 学号: 班级: 实训地点: 指导教师: 通信与电子学院编制 年月日

一、设计要求 数字时钟是采用数字电路实现对年,月,日,时,分,秒数字显示的计时装置,广泛用于个人,家庭,车站,码头,办公室等公共场所,成为人们日常生活中的必需品。 1,、设计时可以利用单片机内部定时器,也可以利用外部实时时钟芯片。(I/O,I2C总线) 2、有年,月,日,时,分,秒功能,而且要能够校正前面五项。 3、显示时可以用8位数码管,也可以用LCD液晶屏。(年只需显示后2位) 4、可选功能:闹钟功能。 二、设计方案 1、芯片分析 AT89C51引脚图 管脚说明: VCC:供电电压。 GND:接地。 P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。当P0口的管脚第一次写1时,被定义为高阻输入。P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。在FIASH编程时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高。 P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。P1口管脚写入1后,被内部上拉为高,可用作输

入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。在FLASH编程和校验时,P1口作为第八位地址接收。 P2口:P2口为一个内部上拉电阻的8位双向I/O口,P2口缓冲器可接收,输出4个TTL门电流,当P2口被写“1”时,其管脚被内部上拉电阻拉高,且作为输入。并因此作为输入时,P2口的管脚被外部拉低,将输出电流。这是由于内部上拉的缘故。P2口当用于外部程序存储器或16位地址外部数据存储器进行存取时,P2口输出地址的高八位。在给出地址“1”时,它利用内部上拉优势,当对外部八位地址数据存储器进行读写时,P2口输出其特殊功能寄存器的内容。P2口在FLASH编程和校验时接收高八位地址信号和控制信号。 P3口:P3口管脚是8个带内部上拉电阻的双向I/O口,可接收输出4 个TTL门电流。当P3口写入“1”后,它们被内部上拉为高电平,并用作输入。作为输入,由于外部下拉为低电平,P3口将输出电流(ILL)这是由于上拉的缘故。 P3口也可作为AT89C51的一些特殊功能口,如下表所示: 口管脚备选功能 P3.0 RXD(串行输入口) P3.1 TXD(串行输出口) P3.2 /INT0(外部中断0) P3.3 /INT1(外部中断1) P3.4 T0(记时器0外部输入) P3.5 T1(记时器1外部输入) P3.6 /WR(外部数据存储器写选通) P3.7 /RD(外部数据存储器读选通) P3口同时为闪烁编程和编程校验接收一些控制信号。 RST:复位输入。当振荡器复位器件时,要保持RST脚两个机器周期的高电平时间。 ALE/PROG:当访问外部存储器时,地址锁存允许的输出电平用于锁存地址的地位字节。在FLASH编程期间,此引脚用于输入编程脉冲。在平时,ALE端以不变的频率周期输出正脉冲信号,此频率为振荡器频率的1/6。因此它可用作对外部输出的脉冲或用于定时目的。然而要注意的是:每当用作外部数据存储器时,将跳过一个ALE脉冲。如想禁止ALE的输出可在SFR8EH地址上置0。此时,ALE只有在执行MOVX,MOVC指令是ALE才起作用。另外,该引脚被略微拉高。如果微处理器在外部执行状态ALE禁止,置位无效。 /PSEN:外部程序存储器的选通信号。在由外部程序存储器取指期间,每个机器周期两次/PSEN有效。但在访问外部数据存储器时,这两次有效的/PSEN信号将不出现。

数字电子钟设计

数字电子钟设计 Revised by Jack on December 14,2020

院部名称 专业电气工程及其自动化 班级 学生姓名 学号 课程设计地点 C105 课程设计学时1周 指导教师 金陵科技学院教务处制 目录

第1章绪论 相关背景知识 电子课程设计是电子技术学习中非常重要的一个环节,是将理论知识和实践能力相统一的一个环节,是真正锻炼学生能力的一个环节。 电子钟是一种高精度的计时工具,它采用了集成电路和石英技术,因此走时精度高,稳定性能好,使用方便,且不需要经常调校。电子钟根据显示方式不同,分为指针式电子钟和数字式电子钟。指针式电子钟采用机械传动带动指针显示;而数字式电子钟则是采用译码电路驱动数码显示器件,以数字形式显示。这些译码显示器件,利用集成技术可以做的非常小巧,也可以另加一定的驱动电路,推动霓红灯或白炽灯显示系统,制做成大型电子钟表。因此,数字式电子钟用途非常广泛。 课程设计目的 1、学习基本理论在实践中综合运用的初步经验,掌握数字电路系统设计的基本方法、设计步骤,进一步熟悉和掌握常用数字电路元器件的应用。 2、学习和练习在面包板上接线的方法、技术、注意事项。

3、学习数字电路实物制作、调试、测试、故障查找和排除的方法、技巧。 4、培养细致、认真做实验的习惯。 5、培养实践技能,提高分析和解决实际问题的能力。 课程设计任务 1.准确计时,以数字形式显示时、分、秒的时间。 2.小时计时采用24进制的计时方式,分、秒采用60进制的计时方式。 3.具有快速校准时、分、秒的功能。 第2章数字电子钟基本原理 总原理框图 数字电子钟的电路组成方框图如图所示。它包括秒发生器电路、计数电路、译码显示电路、校时电路等四个部分组成。其中秒发生器电路、校时电路、二部分尤为重要。由秒发生器电路产生周期为一秒的方波,然后与校时电路共同控制计数电路,正常计时时,由秒发生器电路触发计数电路计数。再通过译码器驱动数码管显示时间。当数码管显示时间与标准时间有偏差时,打开校时电路,进行调节。 图数字电子钟框图

设计报告可调电子时钟

《单片机实训》设计报告 题目:可调电子时钟的设计 学院: 专业: 班级: 姓名: 学号: 指导老师:

一、实验内容 利用CPU的定时器和实验仪上提供的数码显示电路,设计一个可调电子时钟。显示格式如下:XX XX XX ,由左向右分别为:时、分、秒。同时还可以通过键盘(开关)对电子时钟的时间进行加减,达到可调。 二、实验内目的 1、掌握定时器的使用和编程方法; 2、掌握中断处理程序的编程方法; 3、掌握数码显示电路的驱动程序编程方法; 4、掌握键盘电路的程序编程方法; 5、掌握模块子程序的编程方法; 6、掌握硬件的线路的设计及连线方法。 三、实验说明 设计定时器每50ms中断一次,在中断服务程序中,对中断次数进行计数,50ms 计数20次,就是1秒,然后再对秒计数得到分的值,对分计数得到小时的值,分别将各值送到相应的段地址端口和位地址端口,通过数码管显示结果,达到电子时钟的效果。在电子时钟的基础上,程序增加了键盘程序,对电子时钟进行可调(对秒/分/时进行加/减,此功能的增加使电子时钟功能更强、更实用。 四、硬件电路设计原理图 图1 总电路图 R3 图2 键盘控制电路

图3 显示部分电路图 五、软件设计 (一) 程序设计框图

(二) LED数码管字型表

(三)实验程序设计 步骤1、用定时器编写延迟子程序; 2、编写BCD码转换子程序; 3、编写学号显示子程序; 4、编写从0~9秒用数码管显示子程序; 5、据时分秒的要求,编写定时器0中断服务子程序; 6、结合以上子程序,与主程序相组合成电子时钟程序; 7、编写键盘控制加子程序; 8、编写键盘控制减子程序; 9、组合以上子程序,与主程序相组合成可调电子时钟程序; ORG 0000H ;程序入口 AJMP START ;指向主程序 ORG 000BH ;定时器中断入口 AJMP INT1 ;指向中断服务程序 ; INT1: MOV TH0,#9EH MOV TL0,#58H DJNZ R7,EXITINT ;20次未到继续记数 MOV R7,#20 INC 20H MOV R2,20H CJNE R2,#60,EXITINT ;60秒未到继续记数 MOV 20H,#0 INC 21H MOV R2,21H CJNE R2,#60,EXITINT ;60分未到继续记数 MOV 21H,#0 INC 22H MOV R2,22H CJNE R2,#24,EXITINT ;24小时未到继续记数 MOV 22H,#0 EXITINT:RETI START: MOV 20H,#0 MOV 21H,#0 MOV 22H,#0 MOV R7,#20 MOV TMOD,#11H ;设定时器0和1均为方式1 MOV TH0,#9EH ;置定时器0初值为250 ms MOV TL0,#58H MOV TH1,#3CH ;置50ms计数循环初值(定时器1) MOV TL1,#0B0H SETB EA ;CPU开中断