数电实验报告模板

河 北 科 技 大 学

实 验 报 告

级 专业 班 学号 年 月 日

姓 名 同组人 指导教师 吕文哲 任文霞 实验名称 实验二 基本门电路逻辑功能的测试 成 绩 实验类型 验证型 批阅教师

一、实验目的

(1)掌握常用门电路的逻辑功能,熟悉其外形及引脚排列图。 (2)熟悉三态门的逻辑功能及用途。

(3)掌握TTL 、CMOS 电路逻辑功能的测试方法。

二、实验仪器与元器件

(1)直流稳压电源 1台 (2)集成电路

74LS00 四2输入与非门 1片 74LS86 四2输入异或门 1片 74S64 4-2-3-2输入与或非门 1片 74LS125 四总线缓冲门(TS ) 1片 CD4011 四2输入与非门

1片

三、实验内容及步骤

1.常用集成门电路逻辑功能的测试

在数字实验板上找到双列直插式集成芯片74LS00和74LS86。按图进行连线。测试各电路的逻辑功能,并将输出结果记入表中。

门电路测试结果

2.测试与或非门74S64的逻辑功能

在实验板上找到芯片74S64,实现Y AB CD =+的逻辑功能。

Y Y &

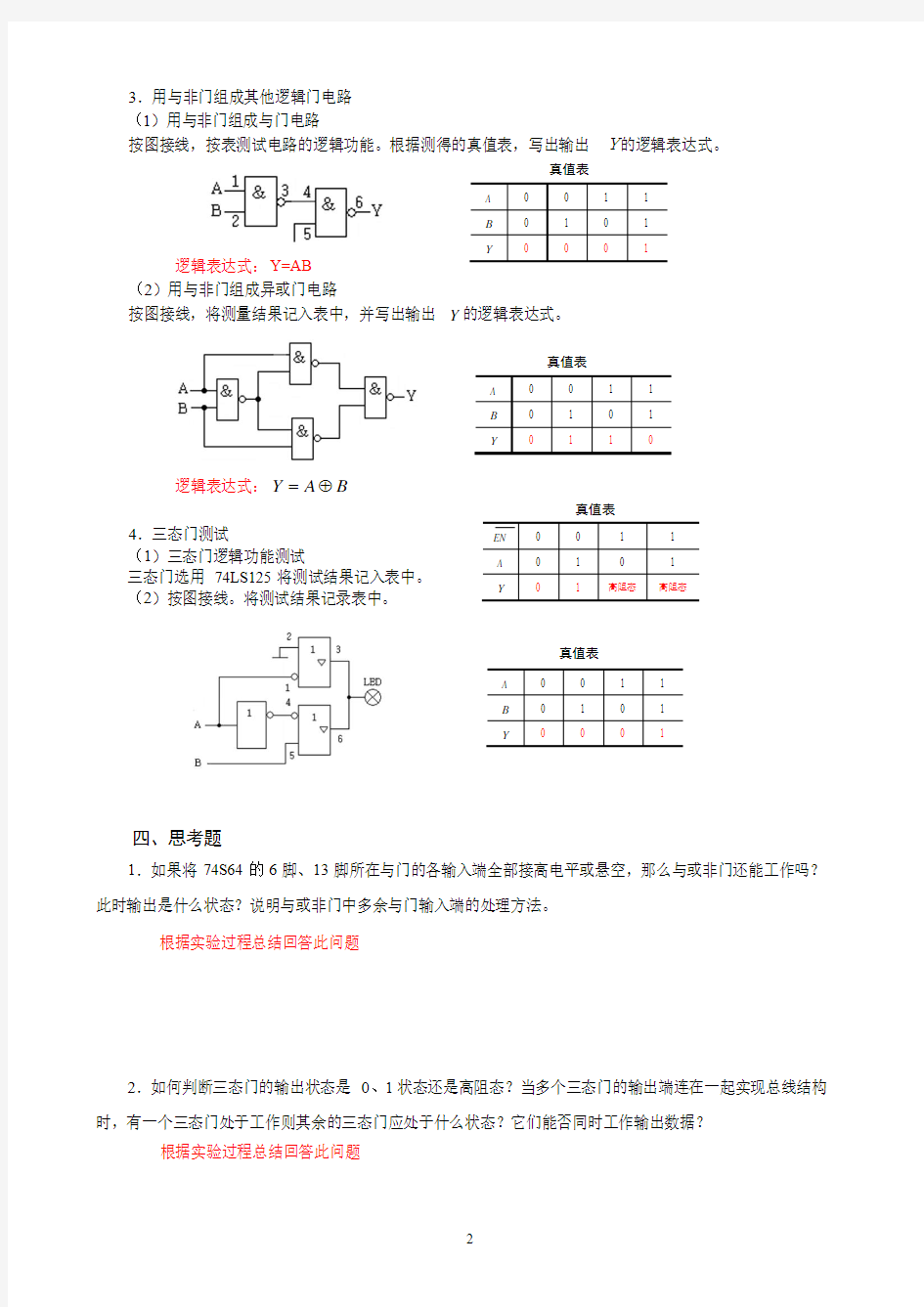

3.用与非门组成其他逻辑门电路 (1)用与非门组成与门电路

按图接线,按表测试电路的逻辑功能。根据测得的真值表,写出输出Y的逻辑表达式。

真值表

逻辑表达式:Y=AB (2)用与非门组成异或门电路

按图接线,将测量结果记入表中,并写出输出Y 的逻辑表达式。

真值表

逻辑表达式:B A Y ⊕=

真值表

4.三态门测试

(1)三态门逻辑功能测试

三态门选用 74LS125将测试结果记入表中。 (2)按图接线。将测试结果记录表中。

真值表

四、思考题

1.如果将74S64的6脚、13脚所在与门的各输入端全部接高电平或悬空,那么与或非门还能工作吗?此时输出是什么状态?说明与或非门中多余与门输入端的处理方法。

根据实验过程总结回答此问题

2.如何判断三态门的输出状态是0、1状态还是高阻态?当多个三态门的输出端连在一起实现总线结构时,有一个三态门处于工作则其余的三态门应处于什么状态?它们能否同时工作输出数据?

根据实验过程总结回答此问题

河北科技大学

实验报告

级专业班学号年月日

姓名同组人指导教师吕文哲任文霞实验名称实验三示波器的使用及门电路测试成绩

实验类型综合型批阅教师

一、实验目的

(1)熟悉双踪示波器的面板结构,学习其使用方法。

(2)进一步学习数字实验板的使用方法。

(3)进一步掌握TTL与非门的特性和测试方法。

二、实验仪器与元器件

(1)直流稳压电源1台

(2)信号发生器1台

(3)6502型示波器1台

(4)集成电路74LS00 四2输入与非门1片

三、实验内容及步骤

1.信号发生器的使用

信号发生器选择不同的按键,可以产生TTL/CMOS标准电平的数字信号,信号从“数字输出”端引出。

通过改变信号发生器的输出频率,观察发光二极管的变化情况。当信号的输出频率较高时,需要用示波器来观察。

2.示波器的使用

(1)示波器的自检

在示波器上读测“校准信号”(方波0.5V、1kHz)电压的峰-峰值、周期和频率,将结果记入表中,并与给定的标准信号值进行比较。

校准信号数据记录2

校准信号数据记录1

(2)TTL数字信号高、低电平值、幅值及频率的测量

先将信号发生器输出的TTL信号频率调为10kHz,再用示波器对其进行测试。

1)高、低电平及幅度值的测量,读出高电平、低电平的电压值,将结果记入表中。

2)频率的测量,使波形在示波器显示两个完整周期,读出波形一个周期所占的格数d,计算周期值T和f。将结果记入表中。

电压峰-峰值、周期和频率测量数据

3.观测与非门对脉冲的控制作用

实验电路如图所示,选择74LS00中的一个门按图接线。

当控制端分别为高电平“1”或低电平“0”时,用示波器双踪观测输入信号与输出信号的波形,并将观察到的波形记录下来。

控制端为高电平“1”

CH1波形

CH2波形

控制端为低电平“0” CH1波形

CH2波形

根据测试结果分析,当控制端为高电平时允许脉冲信号通过,低电平时不允许信号通过。

四、思考题

示波器显示波形不稳定(向左或向右移动)时,应调节哪些旋钮使其稳定下来?

CH2 1

河 北 科 技 大 学

实 验 报 告

级 专业 班 学号 年 月 日

姓 名 同组人 指导教师 吕文哲 任文霞 实验名称 实验五 组合逻辑电路设计 成 绩 实验类型 设计型 批阅教师

一、实验目的

(1)熟悉组合逻辑电路的设计方法,验证电路的逻辑功能。 (2)熟悉集成电路74LS253和74LS138的使用方法。 (3)培养查阅手册及独立完成设计任务的能力。

二、实验仪器与元器件

(1)直流稳压电源 1台 (2)集成电路

74LS253 双数据选择器(TS ) 1片 74LS20 双4输入与非门 1片 74LS00 四2输入与非门 1片 74LS138 3-8线译码器

1片

三、实验任务及要求

1.设计一个控制发电机运行的逻辑电路

有两个发电机组M和N给三个车间供电,N组的发电能力是M组的两倍。如果一个车间开工,只需启动M 组既能满足要求;如果两个车间开工,则需启动N 组就可满足要求;如果三个车间同时开工,则需要同时启动M组和N组,才能满足要求。

(1)设A 、B 、C 为输入变量,分别代表三个车间的开工情况,变量为“1”表示开工,变量为“0”表示不开工。设M 、N 为输出变量,分别代表发电机组的启动情况,“1”代表启动,“0”代表不启动。

(2)真值表 真值表 (3)逻辑表达式

写出逻辑表达式的变换过程

(4)画出逻辑电路图,测试电路的逻辑功能。 用铅笔和直尺画出逻辑电路图

2.设计一个全减器电路

全减器电路中,设A i 为被减数,B i 为减数,C i-1为来自低位的借位。输出为两数之差D i 和向高位的借位C i 。用74LS138和与非门74LS20实现该电路。

(1)真值表 真值表 (2)逻辑表达式 写出逻辑表达式及相应变换过程

(3)画出逻辑电路图,测试电路的逻辑功能。 用铅笔和直尺画出逻辑电路图

3.设计一个用三个开关控制一个灯的逻辑电路

电路要求任何一个开关都能控制灯的亮灭。用74LS138和74LS20实现。测试电路的逻辑功能。

(1)设A 、B 、C 为输入变量,分别代表三个开关,变量为“1”表示开关闭合,变量为“0”表示开关断开。设Y 为输出变量,代表灯的工作情况,“1”代表灯亮,“0”代表灯不亮。

真值表

(2)真值表

(3)逻辑表达式 写出逻辑表达式及相应变换过程

(4)画出逻辑电路图,测试电路的逻辑功能。

用铅笔和直尺画出逻辑电路图

河 北 科 技 大 学

实 验 报 告

级 专业 班 学号 年 月 日

姓 名 同组人 指导教师 吕文哲 任文霞 实验名称 实验六 触发器逻辑功能的测试 成 绩 实验类型 验证型 批阅教师

一、实验目的

(1)掌握基本RS 触发器、D 触发器和JK 触发器的逻辑功能及测试方法。 (2)掌握触发器之间的功能转换方法。

二、实验仪器与元器件

(1)直流稳压电源 1台 (2)6502型示波器 1台 (3)集成电路

74LS00 四2输入与非门 1片 74LS74 双D 型上升沿触发器 1片 74LS112 双JK 型下降沿触发器

1片

五、实验内容及步骤

1.由TTL 与非门构成基本RS 触发器

电路如图所示,按表测量相应Q 和Q 的结果,分析触发器功能。

基本RS 触发器

2.集成D 触发器逻辑功能测试

电路如图所示,按表测量相应Q 和Q 的结果,分析触发器功能。

D触发器逻辑功能测试

注:×—表示任意状态。—单次脉冲的上升沿。—单次脉冲的下降沿。(4)根据测试结果,写出D触发器的特性方程。

3.集成JK触发器逻辑功能测试

电路如图所示,按表测量相应Q和Q的结果,分析触发器功能。

JK触发器逻辑功能测试

(4)根据测试结果,写出JK触发器的特性方程。

4.触发器逻辑功能的转换

(1)将D触发器转换成T 型触发器

电路如图所示,绘出完整的CP、Q和Q的波形。

(2)将JK触发器转换成T触发器

电路如图所示,画出完整的CP和Q的波形。

四、思考题

说明触发器的异步置位端和异步复位端与其它输入信号的关系。

河北科技大学

实验报告

级专业班学号年月日

姓名同组人指导教师吕文哲任文霞实验名称实验九集成同步计数器的应用电路设计成绩

实验类型设计型批阅教师

一、实验目的

(1)掌握中规模集成同步计数器74LS160的逻辑功能和使用方法。

(2)学习CD4511译码器、共阴数码显示器的使用方法。

二、实验仪器与元器件

(1)直流稳压电源1台

(2)集成电路

74LS00 四2输入与非门1片

74LS20 双4输入与非门1片

74LS160 4位十进制同步计数器2片

CD4511 BCD七段译码/驱动/锁存器2片

LED 共阴数码显示器2片

三、实验内容及步骤

1.74LS160逻辑功能测试

表4-9-1 74LS160的逻辑功能表

2.74LS160的应用

(1)用两片74LS160和门电路74LS00构成24进制计数器(用复位法),显示数字为00-23的循环。

1)并行进位型

用铅笔和直尺画出逻辑电路图

2)串行进位型

用铅笔和直尺画出逻辑电路图

(2)用74LS160和74LS20设计一个计数电路(用置数法),要求计数显示为1-7。

用铅笔和直尺画出逻辑电路图

河北科技大学

实验报告

级专业班学号年月日

姓名同组人指导教师吕文哲任文霞实验名称实验十一555定时器的应用成绩

实验类型综合型批阅教师

一、实验目的

(1)熟悉555集成定时器的内部结构及工作原理。

(2)掌握用定时器构成多谐振荡电路、单稳态电路和施密特触发电路的工作原理。

(3)进一步学习用示波器测量波形的周期、脉宽和幅值等。

二、实验仪器与元器件

(1)直流稳压电源1台

(2)信号发生器1台

(3)6502型示波器1台

(4)集成电路

555集成定时器1片

(5)阻容元件

电阻、电容若干

三、实验内容及步骤

1.多谐振荡器

电路如图所示:v C、v O的波形:

多谐振荡器的测量结果

2.单稳态触发器

电路如图所示:v C及v o的波形:

计算值:t w=

测量值:t w=

测量电压实验报告

测量电压实验报告 篇一:基于Labview的电压测量仿真实验报告 仿真实验一基于Labview的电压测量仿真实验 一、实验目的 1、了解电压测量原理; 2、通过该仿真实验熟悉虚拟仪器技术——LABVIEW的简单编程方法; 3、通过本次实验了解交流电压测量的各种基本概念。 二、实验仪器 微机一台、LABVIEW8.5软件三、实验原理 实验仿真程序如下(正弦波、三角波、锯齿波、方波(占空比30%、50%、60%): 四、实验内容及步骤 (1)自己编写LABVIEW仿真信号源实验程序,要求可以产生方波(占空比 可调)、正弦波、三角波、锯齿波等多种波形,而且要求各种波形的参数可调、可控。 (2)编写程序对各种波形的有效值、全波平均值、峰

值等进行测量,在全波平均值测量时要注意程序编写过程。同时记录各种关键的实验程序和实验波形并说明。 实验所得波形如下:(正弦波、三角波、锯齿波、方波(占空比30%、50%、60%): 正弦波: 三角波: 锯齿波: 方波(占空比30%): 方波(占空比50%): 方波(占空比60%): (3)对各种波形的电压进行测量,并列表记录。如下表: 五、实验小结 由各波形不同参数列表可知,电压量值可以用峰值、有效值和平均值表征。被测电压是非正弦波的,必须根据电压表读数和电压表所采用的检波方法进行必要地波形换算,才能得到有关参数。 篇二:万用表测交流电压实验报告1

万用表测交流电压实验报告 篇三:STM32 ADC电压测试实验报告 STM32 ADC电压测试实验报告 一、实验目的 1.了解STM32的基本工作原理 2. 通过实践来加深对ARM芯片级程序开发的理解 3.利用STM32的ADC1通道0来采样外部电压值值,并在TFTLCD模块上显示出来 二、实验原理 STM32拥有1~3个ADC,这些ADC可以独立使用,也可以使用双重模式(提高采样率)。STM32的ADC是12位逐次逼近型的模拟数字转换器。它有18个通道,可测量16个外部和2个内部信号源。各通道的A/D转换可以单次、连续、扫描或间断模式执行。ADC的结果可以左对齐或右对齐方式存储在16位数据寄存器中 接下来,我们介绍一下执行规则通道的单次转换,需要用到的ADC寄存器。第一个要介绍的是ADC控制寄存器(ADC_CR1和ADC_CR2)。ADC_CR1的各位描述如下: ADC_CR1的SCAN位,该位用于设置扫描模式,由软件

数电实验报告 实验二 组合逻辑电路的设计

实验二组合逻辑电路的设计 一、实验目的 1.掌握组合逻辑电路的设计方法及功能测试方法。 2.熟悉组合电路的特点。 二、实验仪器及材料 a) TDS-4数电实验箱、双踪示波器、数字万用表。 b) 参考元件:74LS86、74LS00。 三、预习要求及思考题 1.预习要求: 1)所用中规模集成组件的功能、外部引线排列及使用方法。 2) 组合逻辑电路的功能特点和结构特点. 3) 中规模集成组件一般分析及设计方法. 4)用multisim软件对实验进行仿真并分析实验是否成功。 2.思考题 在进行组合逻辑电路设计时,什么是最佳设计方案 四、实验原理 1.本实验所用到的集成电路的引脚功能图见附录 2.用集成电路进行组合逻辑电路设计的一般步骤是: 1)根据设计要求,定义输入逻辑变量和输出逻辑变量,然后列出真值表; 2)利用卡络图或公式法得出最简逻辑表达式,并根据设计要求所指定的门电路或选定的门电路,将最简逻辑表达式变换为与所指定门电路相应的形式; 3)画出逻辑图; 4)用逻辑门或组件构成实际电路,最后测试验证其逻辑功能。 五、实验内容 1.用四2输入异或门(74LS86)和四2输入与非门(74LS00)设计一个一位全加器。 1)列出真值表,如下表2-1。其中A i、B i、C i分别为一个加数、另一个加数、低位向本位的进位;S i、C i+1分别为本位和、本位向高位的进位。 A i B i C i S i C i+1 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 10 1 1 1 00 1 1 1 1 1 1 2)由表2-1全加器真值表写出函数表达式。

数电实验报告

数字逻辑与数字电路实验报告 实验名称简易迷宫游戏

一、设计课题的任务要求 题目:简易迷宫游戏 设计并实现一个简易迷宫游戏机。 【基本要求】: 1、用8×8 点阵进行游戏显示。 2、迷宫游戏如图1 所示,采用双色点阵显示,其中红色LED 为迷宫墙壁,绿色LED表示人物。通过BTN0~BTN3 四个按键控制迷宫中的人物进行上下左右移动,使人物从起始点出发,走到迷宫的出口,游戏结束。 3、普通计时模式:通过按键BTN7 启动游戏,必须在30 秒内找到出口,否则游戏失败。用两个数码管进行倒计时显示。游戏胜利或者失败均要在8×8 点阵上有相应的画面出现。 4、迷宫中的人物在行走过程中,如果碰到墙壁,保持原地不动。 【提高要求】: 1、多种迷宫地图可以选择。 2、在计时的基础上增加计步的功能,每按一次控制按键步数加1,碰壁不计算步数,计步结果用数码管显示。 3、为游戏增加提示音乐,在不同时间段采用不同频率的信号控制蜂鸣器发声报警。 4、增加其他游戏模式。 5、自拟其它功能。 二、系统设计(包括设计思路、总体框图、分块设计) 设计思路: 依据题目要求,在实验中需要使用到8*8双色点阵输出迷宫图案,使用数码管输出计步步数和倒计时时间,使用蜂鸣器发出警报。由于实验要求需要使用到大量的按键输入。所以需要在输入输出模块中需要按键消抖模块。实验的输出模块共有点阵输出模块,数码管输出模块,蜂鸣器输出模块,在数码管和点阵输出中需要使用到扫描输出的概念。在游戏进行中需要实时判断并且记录人的位置,需要进行记时,计步,所以在整个系统中需要使用状态机进行当前状态转换,控制整个程序。所以在核心实现模块中包括行走模块,状态输出模块,计步模块,计时模块。 输入部分:消抖模块 时钟部分:多级分频器 控制部分:倒计时器,计步器,行走模块,状态机

数电实验报告

选课时间段: 序号(座位号): 杭州电子科技大学 实验报告 课程名称: 数字原理与系统设计实验 实验名称: 组合电路时序分析与自动化设计 指导教师: 学生姓名 学生学号 学生班级 所学专业 实验日期

实验一、设计8位串行进位加法器电路设计: 一位全加器: 八位串行进位加法器:

仿真波形:

实验二、设计5人表决电路 代码: module BJDL45(A,B,C,D,E,YES,NO); input A,B,C,D,E; output YES,NO; reg YES,NO; always@ (A,B,C,D,E,YES,NO) case ({A,B,C,D,E}) 5'B00000:{YES,NO}<=2'B01; 5'B00001:{YES,NO}<=2'B01; 5'B00010:{YES,NO}<=2'B01; 5'B00011:{YES,NO}<=2'B01; 5'B00100:{YES,NO}<=2'B01; 5'B00101:{YES,NO}<=2'B01; 5'B00110:{YES,NO}<=2'B01; 5'B00111:{YES,NO}<=2'B10; 5'B01000:{YES,NO}<=2'B01; 5'B01001:{YES,NO}<=2'B01; 5'B01010:{YES,NO}<=2'B01; 5'B01011:{YES,NO}<=2'B10; 5'B01100:{YES,NO}<=2'B01; 5'B01101:{YES,NO}<=2'B10; 5'B01110:{YES,NO}<=2'B10; 5'B01111:{YES,NO}<=2'B10; 5'B10000:{YES,NO}<=2'B01; 5'B10001:{YES,NO}<=2'B01; 5'B10010:{YES,NO}<=2'B01; 5'B10011:{YES,NO}<=2'B10; 5'B10100:{YES,NO}<=2'B01; 5'B10101:{YES,NO}<=2'B10; 5'B10110:{YES,NO}<=2'B10; 5'B10111:{YES,NO}<=2'B10; 5'B11000:{YES,NO}<=2'B01; 5'B11001:{YES,NO}<=2'B10; 5'B11010:{YES,NO}<=2'B10; 5'B11011:{YES,NO}<=2'B10; 5'B11100:{YES,NO}<=2'B10; 5'B11101:{YES,NO}<=2'B10; 5'B11110:{YES,NO}<=2'B10; 5'B11111:{YES,NO}<=2'B10; default: {YES,NO}<=2'B10; endcase

数电实验报告一

姓名:谭国榕班级:12电子卓越学号:201241301132 实验一逻辑门电路的研究 一、任务 1.熟悉实验室环境及实验仪器、设备的使用方法。 2.掌握识别常用数字集成电路的型号、管脚排列等能力。 3.熟悉74 LS系列、CMOS 4000B系列芯片的典型参数、输入输出特性。 4.掌握常规数字集成电路的测试方法。 二、实验设备及芯片 双踪示波器(DF4321C)1台 信号发生器(DF1641B1)1台 数字万用表(UT58B)一台 数电实验箱1个(自制) 芯片2个:74LS04 CD4069 。 三、实验内容 1.查阅芯片的PDF文件资料,分清管脚名与逻辑功能的对应关系及对应的真值表。74LS04:

CD4069: 2.静态测试 验证6非门74LS04、4069逻辑功能是否正常,并用数字万用表测量空载输出的逻辑电平值(含高、低电平)。 结论:由表格可以看出,CD4069输出的高电平比74LS04高,输出的低电平比74LS04低,所以CD4069的噪声容限相对于74LS04来说较大,故其抗干扰能力强。 3.动态测试 测逻辑门的传输延迟时间:将74LS04、4069中的6个非门分别串接起来,将函数发生器的输出调为方波,对称,幅度:0-5V,单极性,加至第一个门的输入端,并用示波器的通道1观察;用示波器的通道2观察最后一个非门的输出信号,对比输入输出波形以及信号延迟时间。

调节方波信号:

74LS04输出延迟特性: CD4069输出延迟特性:

输出延迟时间的实验数据表: 结论:74LS04的输出延迟比CD4069的输出延迟要短,说明前者的工作速度比后者快。 4.观察电压传输特性 用函数发生器的输出单极性的三角波,幅度控制在5伏,用示波器的X-Y 方式测量TTL 、 CMOS 逻辑门的传输特性,记录波形并对TTL 、CMOS 两种类型电路的高电平输出电压、低电平输出电压以及噪声容限等作相应比较。 (1) 调节函数发生器的输出:单极性三角波,对称,幅度:5V ,频率:500Hz ,从函数发生 器的下部50Ω输出端输出信号; 如图: (2) 扫描方式改为X-Y ,CH1、CH2 接地,调光标使其处于左下角附近; (3) CH1 用 2.0V/DIV (DC ),接函数发生器输出(即非门的输入);CH2 用 0.2V/DIV (DC ),接非门输出。 (4) 记录示波器波形(如图)。

数电实验报告1-数电实验报告实验一

实验一门电路逻辑功能及测试 一、实验目得 1、熟悉门电路逻辑功能。 2、熟悉数字电路学习机及示波器使用方法。 二、实验仪器及材料 1、双踪示波器 2、器件 74LS00 二输入端四与非门2片 74LS20 四输入端双与非门1片 74LS86二输入端四异或门1片 74LS04 六反相器1片 三、预习要求 1、复习门电路工作原理相应逻辑表达示。 2、熟悉所有集成电路得引线位置及各引线用途。 3、了解双踪示波器使用方法。 四、实验内容 实验前按学习机使用说明先检查学习机就是否正常,然后选择实验用得集成电路,按自己设计得实验接线图接好连线,特别注意Vcc及地线不能接错。线接好后经实验指导教师检查无误方可通电。试验中改动接线须先断开电源,接好线后在通电实验。 1、测试门电路逻辑功能。 (1)选用双输入与非门74LS20一只,插入面包板,按图 连接电路,输入端接S1~S4(电平开关输入插口),输 出端接电平显示发光二极管(D1~D8任意一个)。 (2)将电平开关按表1、1置位,分别测出电压及逻辑状态。(表1、1)

2、异或门逻辑功能测试 (1)选二输入四异或门电路74LS86,按图接线,输入端1﹑2﹑4﹑5接电平开关,输出端A﹑B﹑Y接电平显示发光二极管。 (2)将电平开关按表1、2置位,将结果填入表中。 表1、2 3、逻辑电路得逻辑关系

(1)选用四二输入与非门74LS00一只,插入面包板,实验电路自拟。将输入输出逻辑关系分 别填入表1、3﹑表1、4。 (2)写出上面两个电路得逻辑表达式。 表1、3 Y=A ⊕B 表1、4 Y=A ⊕B Z=AB 4、逻辑门传输延迟时间得测量 用六反相器(非门)按图1、5接线,输80KHz 连续脉冲,用双踪示波器测输入,输出相位差,计算每个门得平均传输延迟时间得tpd 值 : tpd =0、2μs/6=1/30μs 5、利用与非门控制输出。 选用四二输入与非门74LS00一只,插入面包板,输入接任一电平开关,用示波器观察S对输出脉冲得控制作用: 一端接高有效得脉冲信号,另一端接控制信号。只有控制信号端为高电平时,脉冲信号才能通过。这就就是与非门对脉冲得控制作用。 6.用与非门组成其她门电路并测试验证 (1)组成或非门。 用一片二输入端与非门组成或非门 Y = A+ B = A ? B 画出电路图,测试并填表1、5 中。 表1、5 图如下: (2)组成异或门 ① 将异或门表达式转化为与非门表达式。 A ⊕B={[(AA)'B]'[A( B B)']}' ② 画出逻辑电路图。 ③ 测试并填表1、6。表1、6

经典编辑南京航空航天大学结构强度的电测法实验报告(含数据)

《结构强度的电测方法》实验报告 学院:航空宇航学院 专业: 学号: 姓名: 组员: 指导教师: 日期:

结构强度电测法实验 一实验目的 1.掌握电阻应变测试原理及方法 2.掌握电阻应变片的安装工艺 3.掌握电阻应变片电桥线路的连接及电阻应变仪的使用 4.测定矩形截面受纯剪切内力作用时的剪切应力分布规律及许用载荷 5.测定特定的弹性元件在对称载荷作用方式下的最大许用载荷 6.测定特定的框架结构在指定外力作用下的危险点应力及最大许用载荷 7.给出测试结果并给出不确定度分析 二实验仪器、设备名称及型号 本实验主要实验仪器和设备有:TS3861静态电阻应变仪、压力试验机、2个待测弹性元件及1个钢架、电阻应变片、导线、电烙铁、丙酮、砂纸、502胶、绝缘胶带、镊子等。 TS3861静态电阻应变仪面板如图1所示。 图1 TS3861静态电阻应变仪面板示意图 其中:(1)CH为通道指示,其下面的两个按扭为通道选择键。 (2) 为读数应变显示窗,其下面的三个按键“自动”、“初值”、“测量”的作用为:“自动”按键在手动测量时无用;“初值”按键为在有初始值的情况下的测量;若先按“初值”再按“测量”按键,为将现通道设置为在“0”初始值的情况下的测量,即“置零”。 (3)根据应变片的阻值选择“应变片电阻Ω”的数字。 (4)根据应变片的灵敏系数选择“灵敏系数K”的数字。

三实验原理及实验方法 1、应变片原理 电阻片分丝式和箔式两大类。丝绕式电阻片是用0.003mm-0.01mm的合金丝绕成栅状制成的;箔式应变片则是用0.003mm-0.01mm厚的箔材经化学腐蚀制成栅状的,其主体敏感栅实际上是一个电阻。金属丝的电阻随机械变形而发生变化的现象称为应变-电性能。电阻片在感受构件的应变时(称做工作片),其电阻同时发生变化。实验表明,构件被测量部位的应变Δl/l与电阻变化率ΔR/R成正比关系,即: 比例系数Ks称为电阻片的灵敏系数。由于电阻片的敏感栅不是一根直丝, 所以K s 不能直接计算,需要在标准应变梁上通过抽样标定来确定。K s 的数值一般 约在2.0 左右,这里取K=2.048。 2、电阻应变仪原理 电阻应变仪是将电阻片感受到应变转化为电阻变化,再把电阻变化通过适当桥路和放大器转为电压变化,并显示出来。电阻应变仪按其测量对象可分为静态电阻应变仪和动态电阻应变仪。动态应变仪有电压和电流输出,提供相关记录仪记录,例如X-Y记录仪、光线示波器和磁带记录仪等等。也有一些应变仪兼有静态应变数值显示和动态电压输出,使用起来比较方便。由于电阻应变仪是一种专用仪器,其显示部分直接显示应变值。通过应变可以计算出载荷、应力和变形,为核算构件的强度提供依据,因此应变仪应用十分广泛应变仪测量电路是一个电桥电路(见图2)它的四个桥臂R1,R2,R3,R4顺序连接在A、B、C、D 之间。电桥AC对角接电源E;BD对角为电桥输出电压U DB。当四个电阻皆由电阻应变片组成,且四枚电阻片阻值和灵敏系数相等时,桥路有如下关系:

数字电路实验报告

数字电路实验报告 姓名:张珂 班级:10级8班 学号:2010302540224

实验一:组合逻辑电路分析一.实验用集成电路引脚图 1.74LS00集成电路 2.74LS20集成电路 二、实验内容 1、组合逻辑电路分析 逻辑原理图如下:

U1A 74LS00N U2B 74LS00N U3C 74LS00N X1 2.5 V J1 Key = Space J2 Key = Space J3 Key = Space J4 Key = Space VCC 5V GND 图1.1组合逻辑电路分析 电路图说明:ABCD 按逻辑开关“1”表示高电平,“0”表示低电平; 逻辑指示灯:灯亮表示“1”,灯不亮表示“0”。 真值表如下: A B C D Y 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 1 1 1 0 1 0 0 0 0 1 0 1 0 0 1 1 0 0 0 1 1 1 1 1 0 0 0 0 1 0 0 1 0 1 0 1 0 0 1 0 1 1 1 1 1 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 1 表1.1 组合逻辑电路分析真值表 实验分析: 由实验逻辑电路图可知:输出X1=AB CD =AB+CD ,同样,由真值表也能推出此方程,说明此逻辑电路具有与或功能。 2、密码锁问题: 密码锁的开锁条件是:拨对密码,钥匙插入锁眼将电源接通,当两个条件同时满足时,开锁信号为“1”,将锁打开;否则,报警信号为“1”,则接通警铃。

试分析下图中密码锁的密码ABCD 是什么? 密码锁逻辑原理图如下: U1A 74LS00N U2B 74LS00N U3C 74LS00N U4D 74LS00N U5D 74LS00N U6A 74LS00N U7A 74LS00N U8A 74LS20D GND VCC 5V J1 Key = Space J2 Key = Space J3 Key = Space J4 Key = Space VCC 5V X1 2.5 V X2 2.5 V 图 2 密码锁电路分析 实验真值表记录如下: 实验真值表 A B C D X1 X2 0 0 0 0 0 1 0 0 0 1 0 1 0 0 1 0 0 1 0 0 1 1 0 1 0 1 0 0 0 1 0 1 0 1 0 1 0 1 1 0 0 1 0 1 1 1 0 1 1 0 0 0 0 1 1 0 0 1 1 0 1 0 1 0 0 1 1 0 1 1 0 1 1 1 0 0 0 1 1 1 0 1 0 1 1 1 1 0 0 1 1 1 1 1 0 1 表1.2 密码锁电路分析真值表 实验分析: 由真值表(表1.2)可知:当ABCD 为1001时,灯X1亮,灯X2灭;其他情况下,灯X1灭,灯X2亮。由此可见,该密码锁的密码ABCD 为1001.因而,可以得到:X1=ABCD ,X2=1X 。

数电实验报告模板

河 北 科 技 大 学 实 验 报 告 级 专业 班 学号 年 月 日 姓 名 同组人 指导教师 吕文哲 任文霞 实验名称 实验二 基本门电路逻辑功能的测试 成 绩 实验类型 验证型 批阅教师 一、实验目的 (1)掌握常用门电路的逻辑功能,熟悉其外形及引脚排列图。 (2)熟悉三态门的逻辑功能及用途。 (3)掌握TTL 、CMOS 电路逻辑功能的测试方法。 二、实验仪器与元器件 (1)直流稳压电源 1台 (2)集成电路 74LS00 四2输入与非门 1片 74LS86 四2输入异或门 1片 74S64 4-2-3-2输入与或非门 1片 74LS125 四总线缓冲门(TS ) 1片 CD4011 四2输入与非门 1片 三、实验内容及步骤 1.常用集成门电路逻辑功能的测试 在数字实验板上找到双列直插式集成芯片74LS00和74LS86。按图进行连线。测试各电路的逻辑功能,并将输出结果记入表中。 门电路测试结果 2.测试与或非门74S64的逻辑功能 在实验板上找到芯片74S64,实现Y AB CD =+的逻辑功能。 Y Y &

3.用与非门组成其他逻辑门电路 (1)用与非门组成与门电路 按图接线,按表测试电路的逻辑功能。根据测得的真值表,写出输出Y的逻辑表达式。 真值表 逻辑表达式:Y=AB (2)用与非门组成异或门电路 按图接线,将测量结果记入表中,并写出输出Y 的逻辑表达式。 真值表 逻辑表达式:B A Y ⊕= 真值表 4.三态门测试 (1)三态门逻辑功能测试 三态门选用 74LS125将测试结果记入表中。 (2)按图接线。将测试结果记录表中。 真值表 四、思考题 1.如果将74S64的6脚、13脚所在与门的各输入端全部接高电平或悬空,那么与或非门还能工作吗?此时输出是什么状态?说明与或非门中多余与门输入端的处理方法。 根据实验过程总结回答此问题 2.如何判断三态门的输出状态是0、1状态还是高阻态?当多个三态门的输出端连在一起实现总线结构时,有一个三态门处于工作则其余的三态门应处于什么状态?它们能否同时工作输出数据? 根据实验过程总结回答此问题

电测实验报告解析

《电子测量技术》实验报告 电气工程学院 姓名:李晓峰 学号:12281035 班级:电气1307班

实验一示波器波形参数测量 一、实验目的 通过示波器的波形参数测量,进一步巩固加强示波器的波形显示原理的掌握,熟悉示波器的使用技巧。 1.熟练掌握用示波器测量电压信号峰峰值,有效值及其直流分量。 2.熟练掌握用示波器测量电压信号周期及频率。 3.熟练掌握用示波器在单踪方式和双踪方式下测量两信号的相位差。 二、实验设备 1.信号发生器,示波器。 示波器——SS7802A a、主要参数: SS-7802模拟示波器·具有能够选择场方式、线路的TV/视频同步功能·附有光标和读出功能·5位数计数器规格及性能·显像管:6英寸、方型8*10p(1p=10mm)约16kV·垂直灵敏度:2mV/p~5V/p(1-2-5档)(通道1、通道2)精度:±2%·频率范围:20MHz·时间轴扫描A·100ns/p~500ms/p·TV/视频同步:能够选择场方式、能够选择ODD、EVEN、BOTH、扫描线路 b、主要功能描述 示波器操作板如图所示:

包括如下五个操作控制区域: 水平控制区 【?POSITION?】:将【?POSITION?】向右旋转,波形右移。 FINE 指示灯亮时,旋转【?POSITION?】可作微调。 MAG×10 :扫描速率提高10倍,波形将基于中心位置向左右放大。 ALTCHOP :选择ALT(交替,两个或多个信号交替扫描)或CHOP (断续,两个或多个信号交替扫描)。 垂直控制区 INPUT:输入连接器(CH1、CH2),连接输入信号。 EXTINPUT :用外触发信号做触发源。外信号通过前面板的EXTINPUT接入。 【VOLTS/DIV】:调节【VOLTS/DIV】选择偏转因数。按下【VOLTS/DIV】;偏转因数显示“”符号。在该屏幕下,可执行微调程序。 【▲POSITION▼】:垂直位移,向右旋转,波形上移。

数电实验-实验报告-实验六

实验一 TTL与非门的参数测试 一、实验目的 ·掌握用基本逻辑门电路进行组合逻辑电路的设计方法。 ·通过实验,验证设计的正确性。 二、实验原理 1.组合逻辑电路的分析: 所谓组合逻辑电路分析,即通过分析电路,说明电路的逻辑。 通常采用的分析方法是从电路的输入到输出,根据逻辑符号的功能逐级列出逻辑函数表达式,最好得到表示输出与输入之间的关系的逻辑函数式。然后利用卡诺图或公式化简法将得到的函数化简或变换,是逻辑关系简单明了。为了使电路的逻辑功能更加直观,有时还可以把逻辑函数式转化为真值表的形式。 2.逻辑组合电路的设计: 根据给出的实际逻辑问题,求出实现这一逻辑功能的最简单电路,陈伟组合逻辑电路的设计。 3.SSI设计:设计步骤如下: ①逻辑抽象;分析时间的因果关系,确定输入和输出变量。 ②定义逻辑状态的含义:以二值逻辑0、1表示两种状态。 ③列出真值表 ④写出逻辑表达式,并进行化简,根据选定器件进行转换。 ⑤画出逻辑电路的连接图。 ⑥实验仿真,结果验证。 三、实验仪器及器件 数字万用表1台

多功能电路实验箱1台 四、实验内容 1.设计5421BCD 码转换为8421BCD 码(用双输入端与非门实现)。 四位自然二进制码 5421BCD码 B3 B2 B1 B0 D3 D2 D1 D0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 0 0 1 0 0 0 1 1 0 0 1 1 0 1 0 0 0 1 0 0 0 1 0 1 0 1 0 1 0 1 1 0 0 1 1 0 0 1 1 1 0 1 1 1 1 0 0 0 1 0 1 1 1 0 0 1 1 1 1 0 1 0 伪码 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 根据5421BCD 码与8421BCD 码真值表可得 2.设A 、B 、C 、D 代表四位二进制变量,函数X=8A-4B+2C+D ,试设计一个组合逻辑电路,判断当函数值介于4 深 圳 大 学 实 验 报 告 课程名称: 实验项目名称: 学院: 专业: 指导教师: 报告人: 学号: 班级: 实验时间: 实验报告提交时间: 教务部制 强看线敷设线盒处检测处电气课与相互过度工作资料试试过了解试高中试技,并且作,并差动保要保护 实验目的与要求: 方法、步骤: 、管路敷设技术通过管线不仅可以解决吊顶层配置不规范高中资料试卷问题,而且可保障各类管路习题到位。在管路敷设过程中,要加强看护关于管路高中资料试卷连接管口处理高中资料试卷弯扁度固定盒位置保护层防腐跨接地线弯曲半径标等,要求技术交底。管线敷设技术中包含线槽、管架等多项方式,为解决高中语文电气课件中管壁薄、接口不严等问题,合理利用管线敷设技术。线缆敷设原则:在分线盒处,当不同电压回路交叉时,应采用金属隔板进行隔开处理;同一线槽内强电回路须同时切断习题电源,线缆敷设完毕,要进行检查和检测处理。、电气课件中调试对全部高中资料试卷电气设备,在安装过程中以及安装结束后进行 高中资料试卷调整试验;通电检查所有设备高中资料试卷相互作用与相互关系,根据生产工艺高中资料试卷要求,对电气设备进行空载与带负荷下高中资料试卷调控试验;对设备进行调整使其在正常工况下与过度工作下都可以正常工作;对于继电保护进行整核对定值,审核与校对图纸,编写复杂设备与装置高中资料试卷调试方案,编写重要设备高中资料试卷试验方案以及系统启动方案;对整套启动过程中高中资料试卷电气设备进行调试工作并且进行过关运行高中资料试卷技术指导。对于调试过程中高中资料试卷技术问题,作为调试人员,需要在事前掌握图纸资料、设备制造厂家出具高中资料试卷试验报告与相关技术资料,并且了解现场设备高中资料试卷布置情况与有关高中资料试卷电气系统接线等情况 ,然后根据规范与规程规定,制定设备调试高中资料试卷方案。 、电气设备调试高中资料试卷技术电力保护装置调试技术,电力保护高中资料试卷配置技术是指机组在进行继电保护高中资料试卷总体配置时,需要在最大限度内来确保机组高中资料试卷安全,并且尽可能地缩小故障高中资料试卷破坏范围,或者对某些异常高中资料试卷工况进行自动处理,尤其要避免错误高中资料试卷保护装置动作,并且拒绝动作,来避免不必要高中资料试卷突然停机。因此,电力高中资料试卷保护装置调试技术,要求电力保护装置做到准确灵活。对于差动保护装置高中资料试卷调试技术是指发电机一变压器组在发生内部故障时,需要进行外部电源高中资料试卷切除从而采用高中资料试卷主要保护装置。 接地电阻测量实验报告范文 为了了解接地装置的接地电阻值是否合格、保证安全运行,同时根据配电设备维护规程的有关规定,我部于20xx年3月1日上午8:00 对乐民原料部弓角田煤矿各变配电点的接地及其各变压器对地绝缘情况进 行测量试验。试验过程及试验结果分析报告如下: 一、试验前的准备: 1、制订试验方案: 前期,我们组织机电队人员一起到现场查看接地装置,查找接地极的适合试验的位置,制订、讨论、修改试验方案,提出试验中的注意事项。 2、试验方法: 接地电阻表本身备有三根测量用的软导线,可接在E、P、C三个接线端子上。接在E端子上的导线连接到被测的接地体上,P端子为电压极,C端子为电流极(P、C都称为辅助接地极),根据具体情况,我们准备采用两种方式测量:(1)、将辅助接地极用直线式或三角线式,分别插入远离接地体的土壤中;(2)、用大于25cm×25cm的铁板作为辅助电极平铺在水泥地面上,然后在铁板下面倒些水,铁板的布放位置与辅助接地极的要求相同。两种方法我们都采取接地体和连接设备不 断开的方式测量,接地电阻电阻表将倍率开关转换到需要的量程上,用手摇发电机手柄,以每分钟0转/分以上的速度转时,使电阻表上的仪表指针趋于平衡,读取刻盘上的数值乘以倍率即为实测的接地电阻值。 3、试验工具: 我们准备好ZC29B-2型接地电阻测试仪、ZC110D-10(0~2500MΩ)型摇表、万用表、铜塑软导线(BVR 1.5mm2)、测电笔、接地极棒和接地板等试验用具及棉纱等辅助材料。 二、试验过程: 1、3月1日上午,现场试验人员进行简单碰头,并进行分工:由帅锐进行测量、值班人员蔡富贵和彭余坤配合操作、陈应沫记录、班长方兴华负责监护; 2、8:45试验开始; 3、测量辅助接地极间及与测量接地体间的距离; 4、采取第一种方法,将接地极棒插入到土壤中并按照图纸接好线; 5、将测量接地体连接处与连接端子牢靠连接; 6、将导线与接地电阻表接好; 7、校正接地电阻表; 8、测量并记录数据;(试验数据见附表) 9、采取第二种方法,测量并记录数据; 10、整个试验过程结束。 恒鼎实业弓角田煤矿春季预防性试验设备外壳接地测试记录 恒鼎实业弓角田煤矿春季预防性试验变压器绝缘测试记录 使用仪器: ZC29B-2型接地电阻测试仪 测量数据表: 测量数据单位(MΩ) 数字电子技术仿真 实验报告 班级: 姓名: 学号: 实验一组合逻辑电路设计与分析 一、实验目的 1.掌握组合逻辑电路的特点; 2.利用逻辑转换仪对组合逻辑电路进行分析与设计。 二、实验原理 组合逻辑电路是一种重要的、也是基本的数字逻辑电路,其特点是:任意时刻电路的输出仅取决于同一时刻输入信号的取值组合。 对于给定的逻辑电路图,我们可以先由此推导出逻辑表达式,化简后,由所得最简表达式列出真值表,在此基础上分析确定电路的功能,这也即是逻辑电路的分析过程。 对于组合逻辑电路的设计,一般遵循下面原则,由所给题目抽象出便于分析设计的问题,通过这些问题,分析推导出真值表,由此归纳出其逻辑表达式,再对其化简变换,最终得到所需逻辑图,完成了组合逻辑电路的设计过程。 逻辑转换仪是在Multisim软件中常用的数字逻辑电路设计和分析的仪器,使用方便、简洁。 三、实验电路及步骤 1.利用逻辑转换仪对已知逻辑电路进行分析。 (1)按图1-1连接电路。 图1-1 待分析的逻辑电路 (2)通过逻辑转换仪,得到下图1-2所示结果。 由图可看到,所得表达式为:输出为Y, D'+ABCD CD'+ABC' AB' + D C' BCD'+AB' A' + D BC' A'+ CD B' D'+A' C' B' A' Y 图1-5 经分析得到的真值表和表达式 (3)分析电路。观察真值表,我们发现:当输入变量A、B、C、D中1的个数为奇数时,输出为0;当其为偶数时,输出为1。因此,我们说,这是一个四输入的奇偶校验电路。 2.根据要求,利用逻辑转换仪进行逻辑电路的设计。 问题提出:有一火灾报警系统,设有烟感、温感和紫外线三种类型不同的火灾推测器。为了防止误报警,只有当其中有两种或两种以上的探测器发出火灾探测信号时,报警系统才会产生报警控制信号,试设计报警控制信号的电路。 具体步骤如下: (1)分析问题:探测器发出的火灾探测信号有两种情况,一是有火灾报警(可用“1”表示),一是没有火灾报警(可用“0”来表示),当有两种或两种以上报警器发出报警时,我们定义此时确有警报情况(用“1”表示),其余以“0”表示。由此,借助于逻辑转换仪面板,我们绘出如图1-3所示真值表。 图1-3 经分析得到的真值表 数字电路实验报告 实验一 组合逻辑电路分析 一.试验用集成电路引脚图 74LS00集成电路 74LS20集成电路 四2输入与非门 双4输入与非门 二.实验内容 1.实验一 2.实验二 密码锁的开锁条件是:拨对密码,钥匙插入锁眼将电源接通,当两个条件同时满足时,开锁信号为“1”,将锁打开。否则,报警信号为“1”,则接通警铃。试分析密码锁的密码 X1 2.5 V A B C D 示灯:灯亮表示“1”,灯灭表示“0” ABCD 按逻辑开关,“1”表示高电平,“0”表示低电平 ABCD是什么? ABCD 接逻辑电平开关。 最简表达式为:X1=AB’C’D 密码为: 1001 A B C D X1 X2 A B C D X1 X2 0 0 0 0 0 1 1 0 0 0 0 1 0 0 0 1 0 1 1 0 0 1 1 0 0 0 1 0 0 1 1 0 1 0 0 1 0 0 1 1 0 1 1 0 1 1 0 1 0 1 0 0 0 1 1 1 0 0 0 1 0 1 0 1 0 1 1 1 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 1 0 1 1 1 1 1 1 1 1 1 三.实验体会: 1.分析组合逻辑电路时,可以通过逻辑表达式,电路图和真值表之间的相互转换来到达实验所要求的目的。 2.这次试验比较简单,熟悉了一些简单的组合逻辑电路和芯片 ,和使用仿真软件来设计和构造逻辑电路来求解。 实验二 组合逻辑实验(一) 半加器和全加器 一.实验目的 1. 熟悉用门电路设计组合电路的原理和方法步骤 二.预习内容 1. 复习用门电路设计组合逻辑电路的原理和方法步骤。 2. 复习二进制数的运算。 3. 用“与非门”设计半加器的逻辑图。 4. 完成用“异或门”、“与或非”门、“与 非”门设计全加器的逻辑图。 5. 完成用“异或”门设计的3变量判奇 电路的原理图。 三.元 件参考 U1A 74LS00D U1B 74LS00D U1C 74LS00D U1D 74LS00D U2A 74LS00D U2B 74LS00D U2C 74LS00D U3A 74LS20D X1 2.5 V X2 2.5 V VCC 5V A B C D 网络高等教育《电力系统继电保护》实验报告 学习中心:奥鹏学习中心 层次:专科起点本科 专业:电气工程及其自动化 年级: 学号: 学生: 实验一电磁型电流继电器和电压继电器实验 一、实验目的 1. 熟悉DL型电流继电器和DY型电压继电器的的实际结构,工 作原理、基本特性; 2. 学习动作电流、动作电压参数的整定方法。 二、实验电路 1.过流继电器实验接线图 过流继电器实验接线图 2.低压继电器实验接线图 低压继电器实验接线图 三、预习题 1.过流继电器线圈采用_串联_接法时,电流动作值可由转动刻度盘上的指针所对应的电流值读出;低压继电器线圈采用__并联 _接法时,电压动作值可由转动刻度盘上的指针所对应的电压值读出。(串联,并联) 2. 动作电流(压),返回电流(压)和返回系数的定义是什么? 答:1.使继电器返回的最小电压称为返回电压;使继电器动作的最大电压称为动作电压;返回电压与动作电压之比称为返回系数。 2.使继电器动作的最小电流称为动作电流;使继电器返回的最大电流称为返回电流;返回电流与动作电流之比称为返回系数。 四、实验容 1.电流继电器的动作电流和返回电流测试 表一过流继电器实验结果记录表 2.低压继电器的动作电压和返回电压测试 表二低压继电器实验结果记录表 五、实验仪器设备 六、问题与思考 1.电流继电器的返回系数为什么恒小于1? 答:由于摩擦力矩和剩余力矩的存在,使得返回量小于动作量。根据返回力矩的定义,返回系数恒小于1. 2.返回系数在设计继电保护装置中有何重要用途? 答:返回系数是确保保护选择性的重要指标,让不该动作的继电器及时返回,使正常运行的部分系数不被切除。 3. 实验的体会和建议 电流保护的动作电流是按躲开最大负荷电流整定的,一般能保护相邻线路。在下一条相邻线路或其他线路短路时,电流继电器将启动,但当外部故障切除后,母线上的电动机自启动,有比较大的启动电流,此时要求电流继电器必须可靠返回,否则会出现误跳闸。所以过电流保护在整定计算时必须考虑返回系数和自起动系数,以保证在上述情况下,保护能在大的启动电流情况下可靠返回。电流速断的保护的动作电流是按躲开线路末端最大短路电流整定的,一般只能保护线路首端。在下一条相邻线路短路时,电流继电器不启动,当外部故障切除后,不存在大的启动电流情况下可靠返回问题 数电实验报告 《数字电子技术》 实验报告 姓名:*** 班级:****888 学号:2014*******8 指导老师:**** 编制时间:2016.06.10 北京联合大学 实验一基本集成逻辑门电路功能分析一、实验目的 1.理解TTL和CMOS普通门电路的参数含义。 2.掌握TTL和CMOS普通门电路的使用方法。 3.掌握分析普通门电路逻辑功能的一般方法。 4.理解TTL和CMOS普通门电路参数的一般分析方法。 二、实验元器件 双四输入与非门 74LS00×1片 六反相器 74LS04×1片 电阻 300Ω×1只 三、实验内容 (一) TTL 双四输入与非门74LS00功能分析 (1)逻辑功能分析 参考图1.1连接电路。一只74LS00芯片中含有四个相同的2输入与非门,可以随意选用,此处选用的是第一个门电路。检查电路无误时方可通电。 图1.1 与非门逻辑功能测试电路 变换单刀双掷开关J1和J2的状态,用直流电压表测试电路的输出电压,将测试结果记入表1.1中。 表1.1 输入 输出 U 1/V U 2/V 实测值 逻辑值 0 0 5 5 0 5 5 5 5 5 5 U1A 7400N J2Key = A J1 Key = B VCC 5V 0.000 V +- 5 5 0 0 (2)电压传输特性分析 依照图1.3编辑电路。在0~5V 间逐步调整输入的直流电压,将随之变化的输出电压记入表1.2中。 图1.3 分析与非门电压传输特性仿真电路 表1.2 U I /V U O /V U I /V U O /V U I /V U O /V U I /V U O /V 5.0 0 3.8 0 2.6 0 1.4 5 4.8 0 3.6 0 2.4 5 1.2 5 4.6 0 3.4 0 2.2 5 1.0 5 4.4 0 3.2 0 2.0 5 0.8 5 4.2 0 3.0 0 1.8 5 0.4 5 4.0 0 2.8 1.6 5 5 5.000 V +-VSS U1A 7400N V2 1.8 V 实验一门电路逻辑功能及测试 一、实验目的 1、熟悉门电路逻辑功能。 2、熟悉数字电路学习机及示波器使用方法。 二、实验仪器及材料 1、双踪示波器 2、器件 74LS00 二输入端四与非门 2片 74LS20 四输入端双与非门 1片 74LS86 二输入端四异或门 1片 74LS04 六反相器 1片 三、预习要求 1、复习门电路工作原理相应逻辑表达示。 2、熟悉所有集成电路的引线位置及各引线用途。 3、了解双踪示波器使用方法。 四、实验内容 实验前按学习机使用说明先检查学习机是否正常,然后选择实验用的集成电路,按自己设计的实验接线图接好连线,特别注意Vcc及地线不能接错。线接好后经实验指导教师检查无误方可通电。试验中改动接线须先断开电源,接好线后在通电实验。 1、测试门电路逻辑功能。 (1)选用双输入与非门74LS20一只,插入面包板,按图 连接电路,输入端接S1~S4(电平开关输入插口),输 出端接电平显示发光二极管(D1~D8任意一个)。 (2)将电平开关按表1.1置位,分别测出电压及逻辑状态。(表1.1) 2、异或门逻辑功能测试 (1)选二输入四异或门电路74LS86,按图接线,输入端1﹑2﹑4﹑5接电平开关,输出端A﹑B﹑Y接电平显示发光二极管。 (2)将电平开关按表1.2置位,将结果填入表中。 表 1.2 3、逻辑电路的逻辑关系 (1)选用四二输入与非门74LS00一只,插入面包板,实验电路自拟。将输入输出逻辑关系分别填入表1.3﹑表1.4。 (2)写出上面两个电路的逻辑表达式。 表1.3 Y=A ⊕B 表1.4 Y=A ⊕B Z=AB 4、逻辑门传输延迟时间的测量 用六反相器(非门)按图1.5接线,输80KHz 连续脉冲,用双踪示波器测输入,输出相位差,计算每个门的平均传输延迟时间的tpd 值 : tp d=0.2μs/6=1/30μs 5、利用与非门控制输出。 选用四二输入与非门74LS00一只,插入面包板,输入接任一电平开关,用示波器观察S 对输出脉冲的控制作用: 一端接高有效的脉冲信号,另一端接控制信号。只有控制信号端为高电平时,脉冲信号才能通过。这就是与非门对脉冲的控制作用。 6.用与非门组成其他门电路并测试验证 (1)组成或非门。 用一片二输入端与非门组成或非门 Y = A + B = A ? B 画出电路图,测试并填表1.5 中。 表1.5 图如下: (2)组成异或门 ① 将异或门表达式转化为与非门表达式。 A ⊕B={[(AA)'B]'[A(BB)']}' ② 画出逻辑电路图。 ③ 测试并填表1.6。 表1.6 输入 输出 A B Y 0 1 0 1 0 1 0 0 1 1 A B Y 0 0 0 0 1 1 1 0 1 1 1深大实验报告模板

接地电阻测量实验报告范文.doc

数电仿真实验报告

数电实验实验报告

电力系统继电保护实验实验报告

数电实验报告

数电实验报告1-数电实验报告实验一