CADENCE 差分对

Title: Differential Pairs in Performance Option Product: Allegro PCB Editor with Performance

Option

Summary: Working with Differential Pairs.

Author/Date: Beate Wilke / 15.04.2009

Table of Contents

1Differential Pairs (2)

1.1Before you start (2)

1.2Definitions (2)

1.2.1Type (3)

1.2.2Objects (3)

1.2.3Uncoupled Length (3)

1.2.4Phase Tolerance (4)

1.2.5Min Line Spacing (4)

1.2.6Coupling Parameters (4)

1.3Calculating differential impedance (6)

1.4Creating an Electrical Constraint Set for one Layer (7)

1.5Creating an Electrical Constraint Set for all Layers (8)

1.6Defining Differential Pairs (10)

1.7Assigning Electrical Constraint Set to Differential Pair (12)

1 Differential Pairs

1.1 Before you start

This Application Note is based on the Application Note “Start with electrical constraining”. It’s important to check and set all necessary settings before you start with electrical constraints. If you do not have the Application Note “Start with electrical constraining”, please contact FlowCAD Hotline – support@flowcad.de.

1.2 Definitions

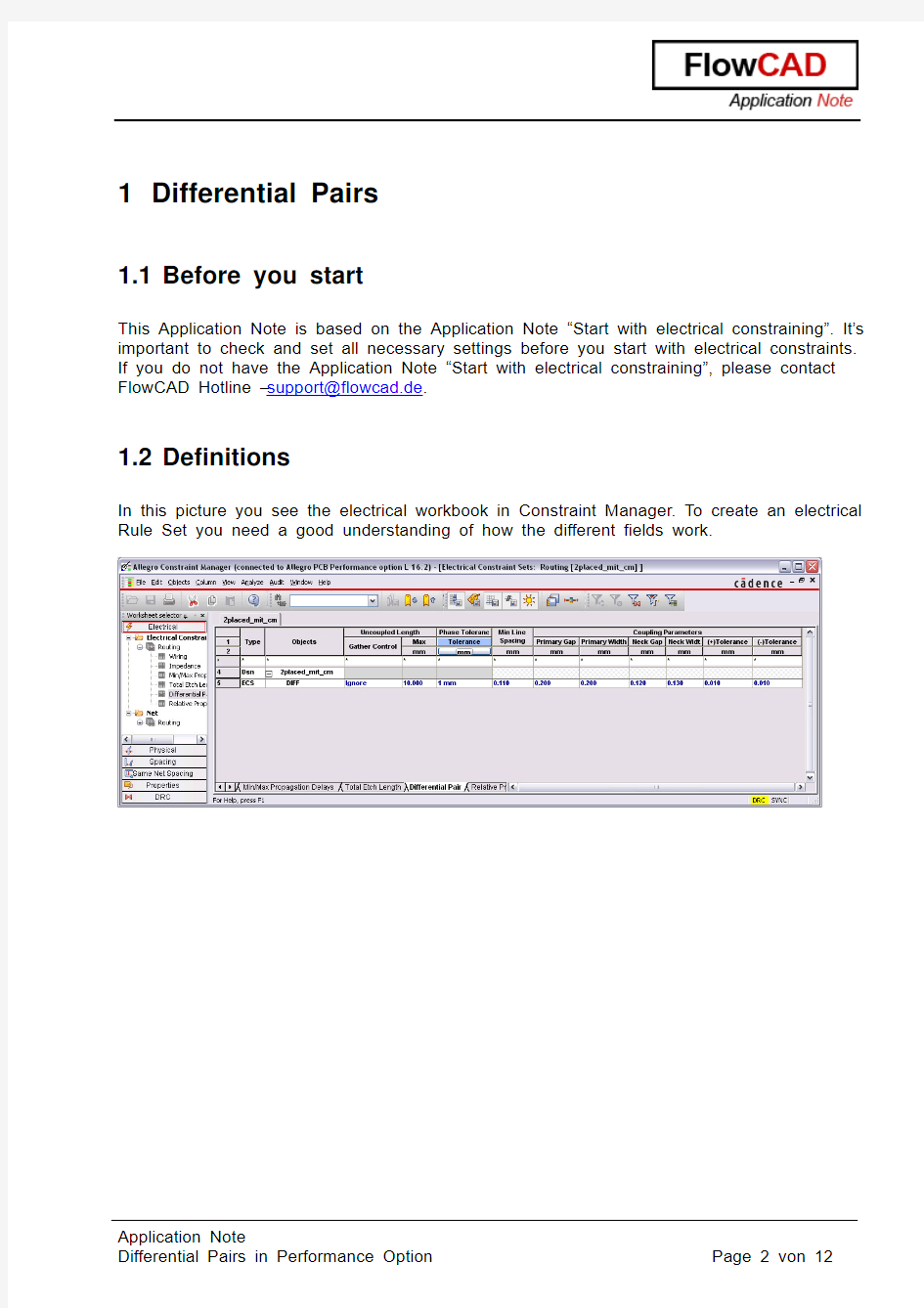

In this picture you see the electrical workbook in Constraint Manager. To create an electrical Rule Set you need a good understanding of how the different fields work.

1.2.1 Type

The field Type shows the Type of the following element. Here is a list of all possible Types:

Dsn Design

DsnI Design Instance Lyr Layer

PrtD Part Definition PrtI Part Instance GtI Gate Instance Bus Bus

MGrp Match Group DPr Differential Pair Xnet Extended Net Net Net PPr Pin Pair NCls Net Class

NCC Net Class-Class Rgn Region

RCls Region Class

RCC Region Class-Class Rslt Result

PCS Physical Constraint Set SCS Spacing Constraint Set SNSC Same Net Spacing Constraint Set

ECS Electrical Constraint Set RBnd Ratsnest Bundle RPPr

Ratsnest Bundle pin pairMember

1.2.2 Objects

The “Object” field stores the Name. If the Type is DSN the Object field includes the board file name. If the Type is ECS the Object includes the name of the Electrical Constraint Set.

1.2.3 Uncoupled Length

Uncoupled Length contains the settings for the total etches length which is not routed using Primary or Neck Gap.

Gather Control:

Gather Control defines if the last cline segments before entering a pad or via are added to the uncoupled length.

The possible settings are “Ignore” or “Include”. Ignore - The uncoupled length for pad entry is not added (ignored) for the uncoupled

length.

Include - Includes the uncoupled length for pad entry to the uncoupled length.

Max uncoupled length:

It’s almost impossible to route a differential pair without any uncoupled length. The Max value defines the maximum total amount of uncoupled length of one differential pair.

1.2.4 Phase Tolerance

Enter the maximum Phase Tolerance in mm or ns for the differential pair. If you have critical nets, the same length or delay is very important for the signal quality.

To optimise same length or delay, you can tune the shorter signal.

1.2.5 Min Line Spacing

The Value is Primary or Neck Gap minus (-) Tolerance, use the smaller value. You need to set this value if it’s smaller than the spacing rules. Min Line Spacing in a differential pair rule overwrites the rules from spacing constraints. Otherwise you would get spacing errors.

1.2.6 Coupling Parameters

1.2.6.1 Primary Gap

Primary Gap is the primary or standard value for the distance between the 2 clines of a differential pair.

1.2.6.2 Primary Width

Primary Width is the primary or standard width for the clines of a differential pair.

1.2.6.3 Neck Gap and Neck Width

If you have to route within a smaller pattern, e.g. inside a BGA footprint you can use the Neck Routing Mode (select Add Connect -> right mouse button -> Neck Mode). Neck Gap and Neck Width are the values for the Neck Routing Mode.

If you use Neck Mode, please remember to set Min Line Width to the right value.

1.2.6.4 (+) and (-) Tolerance

When routing at 45 degrees or using arc clines the tool needs a tolerance for primary and neck gap.

For horizontal and vertical lines the gap matches the gap value of 0.4 exactly.

For all other lines the gap is slightly different. In this example it’s 0.4064 instead of 0.4.

1.3 Calculating differential impedance

You can use the Cross Section to calculate the impedance. Please see Application Note “Start with electrical constraining” chapter 1.

In the Constraint Manager go to Electrical Workbook -> Electrical Constraint Set -> Differential Pair.

Select Min Line Spacing or a Coupling Parameter -> right mouse button -> change.

Select Calculator. The Calculator window opens. Enable the radio button to the value you want to calculate. Change the other value followed by the tab key until you get the right result.

1.4 Creating an Electrical Constraint Set for one Layer

In Constraint Manager go to Electrical Workbook -> Electrical Constraint Set -> Differential Pair.

Select any of the Objects fields -> right mouse button -> Create -> Electrical Cset.

Type in the name of your constraint set and select OK. Fill in all necessary values. We recommend filling in all values. If you don’t want to use Neck Mode, fill in the same values as for Primary Gap and Width.

1.5 Creating an Electrical Constraint Set for all Layers When you route the differential pair on different layers, you need to use different values for Width and Gap. Otherwise you will get different impedances on the different layers. Please see the following Cross Section.

In the next Cross Section all impedances are the same because the values for Width and Gap have been changed.

You need to use a physical rule set to set the different values. In the example below you see the different values for Width and Gap we calculated with Cross Section.

In the electrical Cset leave all Coupling Parameters and Min Line Width blank.

1.6 Defining Differential Pairs

In Constraint Manager go to Electrical Workbook -> Net -> Differential Pair. Select 2 single nets which you want to define as differential pair, click the right mouse button -> Create -> Differential Pair. Then enter the name of the pair and select OK.

If you have several differential pairs in your design, do the following: Go to Electrical Workbook -> Net -> Differential Pair -> select the Object field with Type DSN -> right mouse button -> Create -> Differential pair.

Create Differential Pair window opens. Select Auto Setup.

Fill in the Filter values for + and -. If you wish, you can also fill in the Prefix.

Auto Setup automatically lists all differential pairs and creates pair names. Select Create. Close log file, Differential Pairs Automatic Setup window and Create Differential Pair window. In Constraint Manager you will find all differential pairs.

1.7 Assigning Electrical Constraint Set to Differential Pair In the column on the right hand side of the Objects column with the differential pair names you can reference the differential pair Cset you created previously. To reference a single pair to a Cset, only click in the field. You automatically get a choice box with all available Csets. To reference many pairs, select several fields. In the first row you automatically get a choice box with all available Csets.

采用折叠式结构的两级全差分运算放大器的设计

目录 1. 设计指标 (1) 2. 运算放大器主体结构的选择 (1) 3. 共模反馈电路(CMFB)的选择 (1) 4. 运算放大器设计策略 (2) 5. 手工设计过程 (2) 5.1 运算放大器参数的确定 (2) 5.1.1 补偿电容Cc和调零电阻的确定 (2) 5.1.2 确定输入级尾电流I0的大小和M0的宽长比 (3) 5.1.3 确定M1和M2的宽长比 (3) 5.1.4确定M5、M6的宽长比 (3) 5.1.5 确定M7、M8、M9和M10宽长比 (3) 5.1.6 确定M3和M4宽长比 (3) 5.1.7 确定M11、M12、M13和M14的宽长比 (4) 5.1.8 确定偏置电压 (4) 5.2 CMFB参数的确定 (4) 6. HSPICE仿真 (5) 6.1 直流参数仿真 (5) 6.1.1共模输入电压范围(ICMR) (5) 6.1.2 输出电压范围测试 (6) 6.2 交流参数仿真 (6) 6.2.1 开环增益、增益带宽积、相位裕度、增益裕度的仿真 (6) 6.2.2 共模抑制比(CMRR)的仿真 (7) 6.2.3电源抑制比(PSRR)的仿真 (8) 6.2.4输出阻抗仿真 (9) 6.3瞬态参数仿真 (10) 6.3.1 转换速率(SR) (10) 6.3.2 输入正弦信号的仿真 (11) 7. 设计总结 (11) 附录(整体电路的网表文件) (12)

采用折叠式结构的两级全差分运算放大器的设计 1. 设计指标 5000/ 2.5 2.551010/21~22v DD SS L out dias A V V V V V V GB MHz C pF SR V s V V ICMR V P mW μ>==?== >=±=?≤的范围 2. 运算放大器主体结构的选择 图1 折叠式共源共栅两级运算放大器 运算放大器有很多种结构,按照不同的标准有不同的分类。从电路结构来看, 有套筒 式共源共栅、折叠式共源共栅、增益提高式和一般的两级运算放大器等。本设计采用的是如图1所示的折叠式共源共栅两级运算放大器,采用折叠式结构可以获得很高的共模输入电压范围,与套筒式的结构相比,可以获得更大的输出电压摆幅。 由于折叠式共源共栅放大器输出电压增益没有套筒式结构电压增益那么高,因此为了得到更高的增益,本设计采用了两级运放结构,第一级由M0-M10构成折叠式共源共栅结构,第二级由M11-M14构成共源级结构,既可以提高电压的增益,又可以获得比第一级更高的输出电压摆幅。 为了保证运放在闭环状态下能稳定的工作,本设计通过米勒补偿电容Cc 和调零电阻Rz 对运放进行补偿,提高相位裕量! 另外,本文设计的是全差分运算放大器,与单端输出的运算放大器相比较,可以获得更高的共模抑制比,避免镜像极点及输出电压摆幅。 3. 共模反馈电路(CMFB )的选择 由于采用的是高增益的全差分结构,输出共模电平对器件的特性和失配相当敏感,而且不能通过差动反馈来达到稳定,因此,必须增加共模反馈电路(CMFB )来检测两个输出端

cadence快捷键

原理图:i放大o缩小 ctrl+mouse 放大缩小 ctrl+pageup ctrl+pagedown 左右移动 ctrl+n 下一PART ctrl+b 上一PART view->package 查看全部Part view->part 查看某一PART edit->browse 查看part、nets等 alt断开连接移动 R旋转,V垂直,H水平 原理图R 旋转shift 任意角度走线alt拖动元件时切断连接 全局修改器件属性:edit->browse->parts->shift全选所有器件->edit->properties->browse spreadsheet修改即可。 原理图库:D:\Cadence\SPB_16.3\tools\capture\library\Discrete.olb (散件) 建立原理图库:new->library Cadence olb :ctrl+N 切换到下一PART ctrl+B 切换到前一PART 栅格的控制都在options->preferences->Grid Display Schemtic page grid控制原理图栅格 Part and symbol grid控制元器件库栅格 ******************************************************************************* ******************************* PCB例程:D:\Cadence\SPB_16.3\share\pcb\examples\board_design 测量距离:display->measure / Find->pins PCB Editor:右键->cancel 取消 类、子类color visible PCB提供两种模式,布局布线,封装库(package symbol) PCB 封转库中,怎样设置图纸大小? 显示栅格大小? 焊盘—>元件封装 layout->pins:x0 0 ->右键done dra place_bound_top(矩形) silkscreen_top == assemble_top assemble_top:x0 0.75 ix 1.8 iy -1.5 ix -1.8 iy 1.5 (add line) silkscreen_top: x0.6 0.94 ix -1.38 iy -1.88 ix 1.38 (add line) x1.2 0.94 ix 1.38 iy -1.88 ix -1.38 place_bound_top:add rectangle x-0.85 1 x2.65 -1 参考标号:layout->label->refdes Assembly_top 内部 Silkscreen_top 左上角 file->new->package symbol 必须有:1引脚2零件外形,轮廓线3参考编号4place_bound放置安装区 psm元件封装数据文件,dra元件封装绘图文件

差分运算放大器基本知识

一.差分信号的特点: 图1 差分信号 1.差分信号是一对幅度相同,相位相反的信号。差分信号会以一个共模信号 V ocm 为中心,如图1所示。差分信号包含差模信号和公模信号两个部分, 差模与公模的定义分别为:Vdiff=(V out+-V out- )/2,Vocm=(V out+ +V out- )/2。 2.差分信号的摆幅是单端信号的两倍。如图1,绿色表示的是单端信号的摆 幅,而蓝色表示的是差分信号的摆幅。所以在同样电源电压供电条件下,使用差分信号增大了系统的动态范围。 3.差分信号可以抑制共模噪声,提高系统的信噪比。In a differential system, keeping the transport wires as close as possible to one another makes the noise coupled into the conductors appear as a common-mode voltage. Noise that is common to the power supplies will also appear as a common-mode voltage. Since the differential amplifier rejects common-mode voltages, the system is more immune to external noise. 4.差分信号可以抑制偶次谐波,提高系统的总谐波失真性能。 Differential systems provide increased immunity to external noise, reduced even-order harmonics, and twice the dynamic range when compared to signal-ended system. 二.分析差分放大器电路 图2.差分放大器电路分析图

orCAD使用心得

* * copyright (c) 2005 华北电力大学(北京)自动化系现场总线实验室 * All rights reserved * *文件名: ORCAD使用心得.DOC *文件标识: *摘要:本文写了写我自己的ORCAD使用心得。文中每一条每*一段都记录了这一段时间以来焚膏继晷、暑寒相接、痛苦并快乐的探索历程。今天用了一整天时间把此草稿写完,也算是对自*己有个交待,且对后来人有所启示。不幸的是,这些天茶余饭*后总为发表有ISBN标记的论文而发愁,没有太多心思弄别的.*就写这么多吧。学术腐败,郁闷!! 中国人的悲哀,诺贝尔的遗憾。 *当前版本:1.0.0 *作者:秦宇飞 *完成日期:2005年10月28日 * */ ORCAD使用心得 我自2005年8月25号起,到2005年10月22日止,用CAPTURE和ALLEGR画板,增删数次,校审N回,终成两块电路板。郁闷与欢喜之余,深感ORCAD功能强大,熟练使用真是享受呀。现将我的使用心得写出来,供大家参考。因网上已有许多介绍CAPTURE和ALLEGR操作的文章,这里就不详述具体的操作步骤。 零、ORCAD的安装注意事项 ORCAD的安装涉及CADENCE LICENSE MANAGER安装的问题。选择ALLEGRO程序里的CADENCE LICENSE MANAGER,如果选择CAPTURE里的CADENCE LICENSE MANAGER,会提示IKERNEL错误,这样CADENCE LICENSE MANAGER总也装不上去,程序也无法使用。我也弄不明白为什么CAPTURE 和ALLEGRO里同样的CADENCE LICENSE MANAGER安装程序会有不同的结果。至于其它步骤请看程序中的破解文档吧。 一、 CAPTURE 1、 CAPTURE版本选择 CAPTURE建议使用10.0以上版本。因为9.0的撤消只有一次,用得很郁闷。此外CAPTURE10.0以上版本对ALLEGRO的支持更好。 CAPTURE10.0以上版本增加了从网上原理图库中找元件封装的功能。虽然元件不是很多,但是比自己画方便了很多。我是在画完原理图之后才发现这个功能的,“超级郁闷”(童同学语)。 操作:在原理图编辑窗口点右键,PLACE DATABASE PART再点ICA,然后搜索零件就行了。可以直接放到原理图。 2、命名 (1)、元件编号一定不要重名,虽然文档里不同文件夹内的元件编号可以相同,但是这样会在DRC检测时出问题,所以最好不要这么做。 (2)、CAPTURE的元件库中有两个“地”易弄混。虽然它们的符号不一样。一个叫GND_SIGNAL,另一个叫GND,这个要在使用中要注意。

cadence操作常用快捷键总结

x:检查并存盘,这个经常使用,它会 检查一些简单的连线错误。 s:存盘,保存(save) [:缩小 ]:放大 鼠标上的前后滚轮是放大、缩小 F:整图居中显示 u:撤销上一次操作 Esc:清楚刚键入的命令 Esc 这个很重要,是退出当前快捷方 式,要经常使用。 除非选择了另外的快捷键,否则当前 的快捷键一直存在,所以经常用Esc。 c:复制 m:移动 shift+m:移动器件但不移动连线 按住shift拖动是复制添加 Delete:删除 e 进入symbol的内部电路 Ctrl+e 从symbol内部电路中退回 i:添加元器件 p:添加端口 r:旋转器件并拖动连线 r 是90度旋转 r 后再按F3 可以选择左右翻转或者上 下翻转方向键当然可以上下左右移动 q:属性编辑 L:添加线名 shift+L:标注 N:添加几何图形 shift+N:添加标号 g:查看错误 shift+z:缩小 ctrl+z:放大 F:整图居中显示 u:撤销上一次操作 Esc:清楚刚键入的命令 Ctrl +D:取消选择,这个也可用鼠标 点击空白区域实现。经常使用这个 快捷键可以防止误操作。 c:复制 m:移动 q:显示属性 Delete:删除 i:插入模块(Instance) S:拉伸工具Stretch,要求是框选要拉 伸图形,再拉伸。我觉得这个拉伸 工具是Virtuso版图设计区别于其他 绘图软件的精华所在,能在保持图 形原有性质的前提下,自由拉伸。 这个符合Layout布局的要求。 R:画矩形 Shift+P:多边形工具Polygon P:插入Path,我翻译成“路径”。有

人翻译成“管道”。这些最后都要 Convert to Polygon的。 K:标尺工具 shift+K:清除所有标尺 L:标签工具,标签要加在特定的text 层上,这个有些人总忘记。 Shift+C:裁切(Chop),首先调用命令,选中要裁切的图形,后画矩形裁 切。在用P快捷键画了一条Path 后,如果需要调整线宽,就需要用

全差分运算放大器设计

全差分运算放大器设计 岳生生(200403020126) 一、设计指标 以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下: ?直流增益:>80dB ?单位增益带宽:>50MHz ?负载电容:=5pF ?相位裕量:>60度 ?增益裕量:>12dB ?差分压摆率:>200V/us ?共模电压:2.5V (VDD=5V) ?差分输入摆幅:>±4V 二、运放结构选择

运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。如图2所示;(b )折叠共源共栅,folded-cascode 。如图3所示;(c )共源共栅,telescopic 。如图1的前级所示。本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT N V 之和小于0.5V ,输出端的所有PMOS 管的,DSAT P V 之和也必须小于0.5V 。对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该 要求,因此我们采用两级运算放大器结构。另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。 三、性能指标分析 1、 差分直流增益 (Adm>80db) 该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益 1 3 5 11 1357 113 51 3 57 5 3 ()m m m o o o o o m m m m o o o o m m g g g g g g G A R r r r r g g r r r r =-=-=-+ 第二级增益 9 2 2 9112 9 9 11 ()m o o o m m o o g g G A R r r g g =-=-=- + 整个运算放大器的增益: 4 1 3 5 9 1 2 1 3 5 7 5 3 9 11 (80)10m m m m overall o o o o m m o o dB g g g g A A A g g g g r r r r = = ≥++ 2、 差分压摆率 (>200V/us ) 转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。 定义转换速率SR :

集成电路Cadence IC常用快捷键整理

Cadence常用快捷键整理Cadence 版图绘制 Ctrl+A 全选 Shift+B Return,升到上一级视图 Ctrl+C 中断某个命令,一般用ESC代替。 Shift+C 裁切(chop)。 C 复制,复制某个图形 Ctrl+D 取消选择。亦可点击空白处实现。 Ctrl+F显示上层等级 Shift+F显示所有等级 F fit,显示你画的所有图形 K 标尺工具 Shift+K清除所有标尺 L 标签工具 M 移动工具 Shift+M 合并工具,Merge N 斜45对角+正交。

Shift+O 旋转工具。Rotate O 插入接触孔。 Ctrl+P 插入引脚。Pin Shift+P 多边形工具。Polygon P 插入Path(路径) Q 图形对象属性(选中一个图形先) R 矩形工具。绘制矩形图形 S 拉伸工具。可以拉伸一个边,也可以选择要拉伸的组一起拉伸 U 撤销。Undo。 Shift+U重复。Redo。撤销后反悔 V 关联attach。将一个子图形(child)关联到一个父图形(parent)后,若移动parent,child 也跟着移动;移动child,parent不会移动。 Ctrl+W 关闭窗口。 Shift+W下一个视图。 W 前一个视图。 Y 区域复制Yank。和copy有区别,copy只能复制完整图形对象。 Shift+Y 黏贴Paste。配合Yank使用。 Ctrl+Z 视图放大两倍(也可点住鼠标右键拖动)

Shift+Z 视图缩小两倍 Z 视图放大 ESC键撤销功能 Tab键平移视图Pan。按Tab,用鼠标点击视图区中某点,视图就会移至以该点为中心。Delete键删除 BackSpace键撤销上一点。这就不用因为Path一点画错而删除重画。可以撤销上一点。Enter键确定一个图形最后一点。也可以双击鼠标左键。 Ctrl+方向键移动Cell。 Shift+方向键移动鼠标。 方向键移动视图。 Cadence 仿真常用快捷键 先介绍一些快捷键,快捷键以后会经常使用。 i 是添加instance (instance) f 是合适的显示所有内容(fit) m是移动(move) w是连线(wire) q 看属性(property)

全差分套筒式运算放大器设计

全差分套筒式运算放大器设计 1、设计内容 本设计基于经典的全差分套筒式结构设计了一个高增益运算放大器,采用镜像电流源作为偏置。为了获得更大的输出摆幅及差模增益,电路采用了共模反馈及二级放大电路。 本设计所用到的器件均采用SMIC 0.18μm的工艺库。 2、设计要求及工艺参数 本设计要实现的各项指标和相关的工艺参数如表1和表2所示:

3、放大器设计 3.1 全差分套筒式放大器拓扑结构与实际电路 图1 全差分套筒式放大器拓扑结构 图2 最终电路图

3.2 设计过程 在图1中,Mb1和M9组成的恒流源为差放提供恒流源偏置,且M1,M2完全一样,即两管子所有参数均相同。Mb2、M7和M8构成了镜像电流源,M5、M6和M7、M8构成了共源共栅电流源,M1、M2、M3、M4构成了共源共栅结构,可以显著提高输出阻抗,提高放大倍数(把M3的输出阻抗提高至原来的(gm3 + gmb3)ro2倍。但同时降低了输出电压摆幅。为了提高摆幅,控制增益,在套筒式差分放大器输出端增加二级放大。 本设计中功率上限为10mW,可以给一级放大电路分配3mA的电流。设计要求摆幅为3V,所以图1中M1、M3、M5、M9的过驱动电压之和不大于1.8-3/2=0.3V。我们可以平均分配每个管子的过驱动电压。根据漏电计算流公式(1)(考虑沟道长度调制效应),可以计算出每个管子的宽长比。 I D=1 2μn C ox W L (V GS?V TH)2(1+λV DS)(1) 其中,C ox等于ε/t ox,μn和t ox可以从工艺库中查找。 4、仿真结果 经过调试优化之后的仿真结果如以下各图所示: 图3 增益及相位裕度 从图中可以看出,本设计的低频增益达到了74.25dB,达到了预期要求。3dB 带宽为35kHz左右,比较小,可见设计还有改进的余地。 当CL为2pF时,相位裕度: PM=180°+∠βH(ω)=180°?125.5°=54.5° 电源电压为1.8V时,输出摆幅如下图所示,达到了3V。

在allegro中设置PADS常用的快捷键方法

在allegro中设置PADS常用的快捷键方法 把ENV文件复制到目录C:\\Cadence\\SPB_16.3\\share\\pcb\\text 替换就OK ENV文件内容: # # ALLEGRO GLOBAL Environment file # # The following variables are set by the software if not preset by user: # CDS_SITE, ALLEGRO_SITE, TELENV, ALLEGRO_INSTALL_DIR, # ALLEGRO_INSTALL_TOOLS, ALLEGRO_INSTALL_ROOT, ALLEGRO_TYPE, # __UNIX (if UNIX), _PROGRAM, HOME # # You may set the Operating System variable: # ALLEGRO_PCBENV

Cadence的使用

Cadence软件visor功能的使用说明,远程连接软件为Exceed 设置连接的IP地址就可连接 使用方法如下 1.在桌面找到exceed图标,双击打开-这时弹出登陆界面-输入用户名.密码.就可 登陆系统 2.在登陆到的系统桌面上右击鼠标,可以看到弹出一各菜单,这时可依次选择 TOOLS在弹出的下级菜单中选则terminal , 这时弹出一个像DOS对话框的 窗口出来如图 3.我们要进入project文件夹,因为我们所有的文件都存放于此,进入文件夹的 方法如下: 在当前命令行中继续输入命令:cd project按回车确定执行命令,可以看到目录的路径变成了user/user1/project/这时侯输入命令ls再按回车确定执行命令,就可以看到显示出该目录下的所有文件和子目录 4.例如我们要进入one这个目录就可输入命令(在当前的命令行上输入)cd one 按回车确定执行命令,可以看到目录的路径变成了user/user1/project/one/查看目录下的文件就可输入命令ls 5.在one目录下会有两个子目录,gds和lay说明一下gds 文件夹是用来存 放.gds文件的目录,一般都存放于此。Lay文件夹是用来存放Cadence 导入后的应用文件的目录, 6.下面我们要进入Cadence 导入后的应用文件的目录也就是lay 目录,方法是 继续在当前目录上输入命令cd lay按回车确定执行命令,可以看到目录的路径变成了user/user1/project/lay/ 在该目录下运行Cadence软件:注linux与windows不同,在这个目录下运行该软件该软件就只能查看和修改该目录下的文件。 7.在当前命令行目录下继续输入Cadence软件的执行命令icfb &再按回车确定 执行命令,就可以看到软件正在打开,等到软件完全打开了,我们可以看到在

cadence操作常用快捷键

cadence操作常用快捷键(Layout) Layout快捷键: shift+z:缩小 W快速显示最小化的LSM ctrl+z:放大 F:整图居中显示 c:复制 m:移动 shift+x:进入下一层版图 ctrl+x:还回上一层版图 i:插入模块 R:画矩形 Shift+P:多边形工具Polygon P:插入Path K:标尺工具 shift+K:清除所有标尺 L:标签工具,标签要加在特定的text层上,这个有些人总忘记。 Shift+C:裁切(Chop),首先调用命令,选中要裁切的图形,后画矩形裁切。在用P快捷键画了一条Path后,如果需要调整线宽,就需要用到这个快捷键。Ctrl+Z 视图放大两倍Zoom In by 2Shift+Z 视图缩小两倍Zoom Out by 2Z键视图放大。 Shift+O 旋转工具。RotateCtrl+P 插入引脚。Pin Cadence Virtuoso Layout Editor快捷键归纳 右键点击拖放用来放大。放大后经常配合F键使用,恢复到全部显示。配合Tab 键使用,平移视图。 u:撤销上一次操作

Esc:清楚刚键入的命令 Ctrl +D:取消选择,这个也可用鼠标点击空白区域实现。经常使用这个快捷键可以防止误操作。 q:显示属性 Delete:删除 S:拉伸工具Stretch,要求是框选要拉伸图形,再拉伸。 O键插入接触孔。Create Contact Shift+左键加选图形, Ctrl+左键减选图形。 F2 保存。 F3 这个快捷键很有用,是控制在选取相应工具后是否显示相应属性对话框的。比如在选取Path工具后,想控制Path的走向,可以按F3调出对话框进行设置。F4 英文是Toggle Partial Select,就是用来控制是否可以部分选择一个图形。 F5 打开。 F8 Guided Path Create 切换至L90XYFirst。 Ctrl+A 全选。这个和windows下是一样的。 Shift+B Return。这个牵扯到“Hierarchy”。我翻译成“等级”。这个命令就是等级升一级,升到上一级视图。 Ctrl+C 中断某个命令,不常用。一般多按几次Esc键取消某个命令。 Shift+C 裁切(Chop)。首先调用命令,选中要裁切的图形,后画矩形裁切。 Shift+E和E是控制用户预设的一些选项。 Ctrl+F显示上层等级Hierarchy。 Shift+F显示所有等级。 F键满工作区显示。就是显示你所画的所有图形。 Ctrl+G(Zoom To Grid)。 G 这个快捷键是开关引力(Gravity)的。Gravity我觉得和AutoCAD里的吸附Snap 差不多,就是会吸附到某些节点上去。有时候这个Gravity是很讨厌的,总是乱吸附,这时可以点击G键关闭Gravity,操作完成后再打开。 Shift+M 合并工具。Merge M键移动工具。Move。点选Move工具后,选中要移动的图形,然后在屏幕上任意一处单击一下,这个就是确定移动的参考点,然后就可以自由移动了。这个也可以通过鼠标先选中一个图形,移动鼠标当鼠标箭头变成十字方向的时候就可以拖动来实现。 Ctrl+N,Shift+N和N是控制走向的。 Ctrl+N 先横后竖。L90XFirst Shift+N 直角正交。Orthogonal N键斜45对角+正交。Diagonal Shift+P 多边形工具。Polygon Shift+Q 打开设计属性对话框。选中一个图形先。 Q键图形对象属性。这个实用。经常用来更改图形属性。也是选中一个图形先。Ctrl+R 是Redraw重画。 Shift+R 是Reshape重定形。就是在原来的图形上再补上一块图形。Ctrl+S 是Split。我翻译成“添加拐点”。就是配合Stretch命令可以是原来直的Path打弯。 Shift+S 是Search查找。

全差分运算放大器设计

全差分运算放大器设计 岳生生(0126) 一、设计指标 以上华CMOS 工艺设计一个全差分运算放大器,设计指标如下: 直流增益:>80dB 单位增益带宽:>50MHz 负载电容:=5pF 相位裕量:>60度 增益裕量:>12dB 差分压摆率:>200V/us 共模电压:(VDD=5V) 差分输入摆幅:>±4V 运放结构选择

运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。如图2所示;(b )折叠共源共栅,folded-cascode 。如图3所示;(c )共源共栅,telescopic 。如图1的前级所示。本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的 ,DSAT N V 之和小于,输出端的所有PMOS 管的 ,DSAT P V 之和也必须小于。对于单 级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。 性能指标分析 差分直流增益 (Adm>80db) 该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益 1 3 5 1 1 1 3 5 7 1 1 3 5 1 3 5 7 5 3 ()m m m o o o o o m m m m o o o o m m g g g g g g G A R r r r r g g r r r r =-=-=- +P 第二级增益9 2 2 9 11 2 9 9 11 ()m o o o m m o o g g G A R r r g g =-=-=-+P 整个运算放大器的增益: 4 1 3 5 9 1 2 1 3 5 7 5 3 9 11 (80)10m m m m overall o o o o m m o o dB g g g g A A A g g g g r r r r == ≥++ 差分压摆率 (>200V/us ) 转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。 定义转换速率SR : 1)、输入级: max 1max |2| Cc out DS C C d SR dt I v I C C = = = 单位增益带宽1m u C g C ω= ,可以得到 1m C u g C ω =

Cadence画PCB简单快速教程

Cadence的简单快捷PCB画法 一.原理图 1.建立工程 与其他绘图软件一样,OrCAD以Project来管理各种设计文件。点击开始菜单,然后依次是所有程序—打开cadence软件—》一般选用Design Entry CIS,点击Ok进入Capture CIS。接下来是File--New--Project,在弹出的对话框中填入工程名、路径等等,点击Ok进入设计界面。 2.绘制原理图 新建工程后打开的是默认的原理图文件SCHEMATIC1 PAGE1,右侧有工具栏,用于放置元件、画线和添加网络等等,用法和Protel类似。点击上侧工具栏的Project manager(文件夹树图标)或者是在操作界面的右边都能看到进入工程管理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库等等。 1)修改原理图纸张大小: 双击SCHEMATIC1文件夹,右键点击PAGE1,选择Schematic1 Page Properties,在Page Size中可以选择单位、大小等; 2)添加原理图库: File--New--Library,可以看到在Library文件夹中多了一个library1.olb的原理图库文件,右键单击该文件,选择Save,改名存盘;(注意:在自己话原理图库或者封装库的时候,在添加引脚的时候,最好是画之前设定好栅格等参数,要不然很可能出现你画的封装,很可能在原理图里面布线的时候通不过,没法对齐,连不上线!) 3)添加新元件: 常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元件,或者用别人做好的元件。右键单击刚才新建的olb库文件,选New Part,或是New Part From Spreadsheet,后者以表格的方式建立新元件,对于画管脚特多的芯片元件非常合适,可以直接从芯片Datasheet中的引脚描述表格中直接拷贝、粘贴即可(pdf格式的Datasheet按住Alt键可以按列选择),可以批量添加管脚,方便快捷。 4)生成网络表(Net List): 在画板PCB的时候需要导入网络表,在这之前原理图应该差不多完工了,剩下的工作就是查缺补漏。可以为元件自动编号,在工程管理界面下选中.dsn文件,然后选Tools--Annotate,在弹出的对话框中选定一些编号规则,根据需求进行修改或用默认设置即可。进行DRC检测也是在生成网络表之前的一项重要工作,可以避免出现一些不必要的设计错误。DRC之后可以尝试去生成网络表了,还是在工程管理界面下,选Tools--Create Netlist,可以在弹出的对话框中选择网络表的存放路径,其他默认设置即可,生成网络表的过程中如果出错,可以通Windows--Session Log查看出错的原因,(第一次用cadence 画板子,免不了会出很多错误,通过查阅报表的错误原因,做好记录,是学好该软件的捷径)比如说有元器件忘了添加封装等。 5)更新元件到原理图: 当元件库中的某个元件修改后需要原理图也同步更新时,可以不必重新放置元件(万一有100个或更多该元件岂不是要疯了),在工程管理界面下,双击Design Cache文件夹,选中刚才修改的元件,右键单击选择Update Cache,一路yes下去即可将原理图中该元件全部更新。

cadence操作常用快捷键总结

CIS Explore Ctrl+Tab 切换到原理图页面而不关闭CIS Explore CIS Explore Ctrl+Shift+Tab 切换到原理图页面而不关闭CIS Explore 原理图页面编辑CTRL+A 全选所有 原理图页面编辑 B 放置总线BUS 原理图页面编辑 E 放置总线BUS的分支Entry 原理图页面编辑 F 放置电源符号 原理图页面编辑G 放置GND符号 原理图页面编辑J 放置连接点 原理图页面编辑N 放置网络别名 原理图页面编辑P 放置元件(从元件库) 原理图页面编辑T 放置文本Text 原理图页面编辑W 放置电气连线 原理图页面编辑Y 放置图形连线 原理图页面编辑X 放置无连接符号 原理图页面编辑F7 记录宏操作 原理图页面编辑F8 回放宏操作 原理图页面编辑F9 配置宏操作 元件库编辑(绘图) CTRL+B 跳转至前一个part 元件库编辑(绘图) CTRL+N 跳转至后一个part 原理图页面及元件库编辑 CTRL+E 编辑属性 原理图页面及元件库编辑 CTRL+F 查找 原理图页面及元件库编辑 CTRL+T 吸附格点设置 原理图页面及元件库编辑 CTRL+Y 重做(恢复) 原理图页面及元件库编辑 CTRL+Z 撤销 原理图页面及元件库编辑 F4 重复操作 原理图页面及元件库编辑 C 以鼠标指针为中心 原理图页面及元件库编辑 H 水平镜像 原理图页面及元件库编辑 I 放大 原理图页面及元件库编辑 O 缩小 原理图页面及元件库编辑 R 旋转 原理图页面及元件库编辑 V 垂直镜像 原理图页面及元件库编辑 E 结束连线、BUS、图形连线

全差分运算放大器设计说明

全差分运算放大器设计 岳生生(6) 一、设计指标 以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下: ?直流增益:>80dB ?单位增益带宽:>50MHz ?负载电容:=5pF ?相位裕量:>60度 ?增益裕量:>12dB ?差分压摆率:>200V/us ?共模电压:2.5V (VDD=5V) ?差分输入摆幅:>±4V 二、运放结构选择

运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。如图2所示;(b )折叠共源共栅,folded-cascode 。如图3所示;(c )共源共栅,telescopic 。如图1的前级所示。本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT N V 之和小于0.5V ,输出端的所有PMOS 管的 ,DSAT P V 之和也必须小于0.5V 。对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该 要求,因此我们采用两级运算放大器结构。另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。 三、性能指标分析 1、 差分直流增益 (Adm>80db) 该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益 1 3 5 11135711 3 5 1 3 5 7 5 3 ()m m m o o o o o m m m m o o o o m m g g g g g g G A R r r r r g g r r r r =-=-=- +P 第二级增益 9 2 291129 9 11 ()m o o o m m o o g g G A R r r g g =-=-=- +P 整个运算放大器的增益: 4 1 3 5 9 1 2 1 3 5 7 5 3 9 11 (80)10m m m m overall o o o o m m o o dB g g g g A A A g g g g r r r r == ≥++ 2、 差分压摆率 (>200V/us ) 转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。 定义转换速率SR :

cadence入门教程

本文介绍cadence软件的入门学习,原理图的创建、仿真,画版图和后仿真等一全套过程,本教程适合与初学着,讲到尽量的详细和简单,按照给出的步骤可以完全的从头到尾走一遍,本教程一最简单的反相器为例。 打开终端,进入文件夹目录,输入icfb&启动软件,主要中间有个空格。 启动后出现下图: 点击Tools的Library Manager,出现如下: 上面显示的是文件管理窗口,可以看到文件存放的结构,其中Library就是文件夹,Cell就是一个单元,View就是Cell的不同表现形式,比如一个mos管是一个Cell,但是mos管有原理图模型,有版图模型,有hspice参数模型,有spectre参数模型等,这就列举了Cell的4个View。他们之间是树状的关系,即,Library里面有多个Cell,一个Cell里面有多个View。应该保持一个好习惯就是每个工程都应该建立一个Library,Cell和View之间的管理将在后面介绍。

现在建立工程,新建一个Library,如下左图,出现的对话框如下有图: 在上右图中选择合适的目录,并敲入名字,这里取的是inv,这就是新建的文件夹的名字,以后的各种文件都在这个文件夹下。OK后出现下面对话框 这个对话框是选择是否链接techfile,如果只是原理图仿真而不用画版图,就选择Dont need a techfile,这里我们要画版图,而且有工艺库,选择Attach to an existing techfile,OK 后出现下面对话框:

在technology Library选择tsmc18rf,我们使用的是这个工艺库。Inv的文件夹就建好了,在Library Manager就有它了,如下图: 文件夹建好了后,我们要建立原理图,在inv的Library里面新建Cell如下:

CADENCE快捷键归纳

cadence 快捷键总结 Cadence版图布局软件Virtuso Layout Editor快捷键归纳(也就是Virtuso中说的Bind key) 写在前面:以下我所归纳的快捷键是我在版图培训时通过阅读Cadence帮助文件和菜单命令一个个试出来的,有些我只知道作用而暂时想不到相应的中文翻译。还有一些快捷键帮助文件中有,但我试了没用,可能是要在Unix下吧^_^。希望对学版图设计的有所帮助吧。有不妥的地方还请多多指教啊。 首先介绍下鼠标、键盘操作吧: 1)单击左键选中一个图形(如果是两个图形交叠的话,单击左键选中其中一个图形,在单击选中另一个图形) 2)用左键框选,选中一片图形,某个图形要被完全包围才会被选中。 3)中键单击调出常用菜单命令(很少用,要点两下,麻烦。我们有快捷键的嘛) 4)右键点击拖放用来放大。放大后经常配合F键使用,恢复到全部显示。配合Tab键使用,平移视图。右键还有“Strokes”,就是点住右键画些图线,就能实现调用某些命令。 5)Shift+左键加选图形,Ctrl+左键减选图形。(Cadence菜单中大写表示+按shift,Ctrl 写成^) 6)F1 显示帮助窗口。 7)F2 保存。 7)F3 这个快捷键很有用,是控制在选取相应工具后是否显示相应属性对话框的。比如在选取Path工具后,想控制Path的走向,可以按F3调出对话框进行设置。 8)F4 英文是Toggle Partial Select,就是用来控制是否可以部分选择一个图形。 9)F5 打开。 F6,F7帮助上有,但我试过,没反应-_-!!! 10)F8 Guided Path Create 切换至L90XYFirst。 11)F9 是Filter Size 我不知道怎么用。 12)Ctrl+A 全选。这个和windows下是一样的。 13)Shift+B Return。这个牵扯到“Hierarchy”。我翻译成“层次”。这个命令就是层次升一级,升到上一级视图。

教学EN_cadence+spectre+使用手册

CS/EE 5720/6720 – Analog IC Design Tutorial for Schematic Design and Analysis using Spectre Introduction to Cadence EDA: The Cadence toolset is a complete microchip EDA (Electronic Design Automation) system, which is intended to develop professional, full-scale, mixed-signal microchips. The modules included in the toolset are for schematic entry, design simulation, data analysis, physical layout, and final verification. The Cadence tools at our university are the same as those at most every professional mixed-signal microelectronics company in the United States. The strength of the Cadence tools is in its analog design/simulation/layout and mixed-signal verification and is often used in tandem with other tools for digital design/simulation/layout, where complete top-level verification is done in the Cadence tools. An important concept is that the Cadence tools only provide a framework for doing design. Without a foundry-provided design kit, no design can be done. The design rules used by Cadence set up in this class is based for AMI’s C5N process (0.5 micron 3 metal 2 poly process). So, how is Cadence set up? Broadly, there are three sets of files that need to be in place in order to use Cadence. 1)The Cadence tools These are the design tools provided by the Cadence company. These tools are located in the /home/cadence directory. They are capable of VLSI integration, project management, circuit simulation, design rule verification, and many other things (most of which we won't use). 2)The foundry-based design kit As mentioned before, the Cadence tools have to be supported by a foundry-based design kit. In this class, we use Cadence design kit developed by the North Carolina State University (NCSU CDK). NCSU CDK provides an environment that has been customized with several technology files and a fair amount of custom SKILL code. These files contain information useful for analog/full- custom digital CMOS IC design via the MOSIS IC fabrication service (https://www.360docs.net/doc/563498538.html,). This information includes layer definitions (e.g. colors, patterns, etc.), parasitic capacitances, layout cells, SPICE simulation parameters, Diva rules for Design Rule Check (DRC), extraction, and Layout Versus Schematic (LVS) verification, with various GUI enhancements. For more information on the capability of the NCSU CDK, go to https://www.360docs.net/doc/563498538.html,/CDKoverview.html