一种全数字锁相环的设计与应用

一种全数字锁相环的设计与应用

薛建刚;唐石平;林孝康

【期刊名称】《微计算机信息》

【年(卷),期】2007(000)05Z

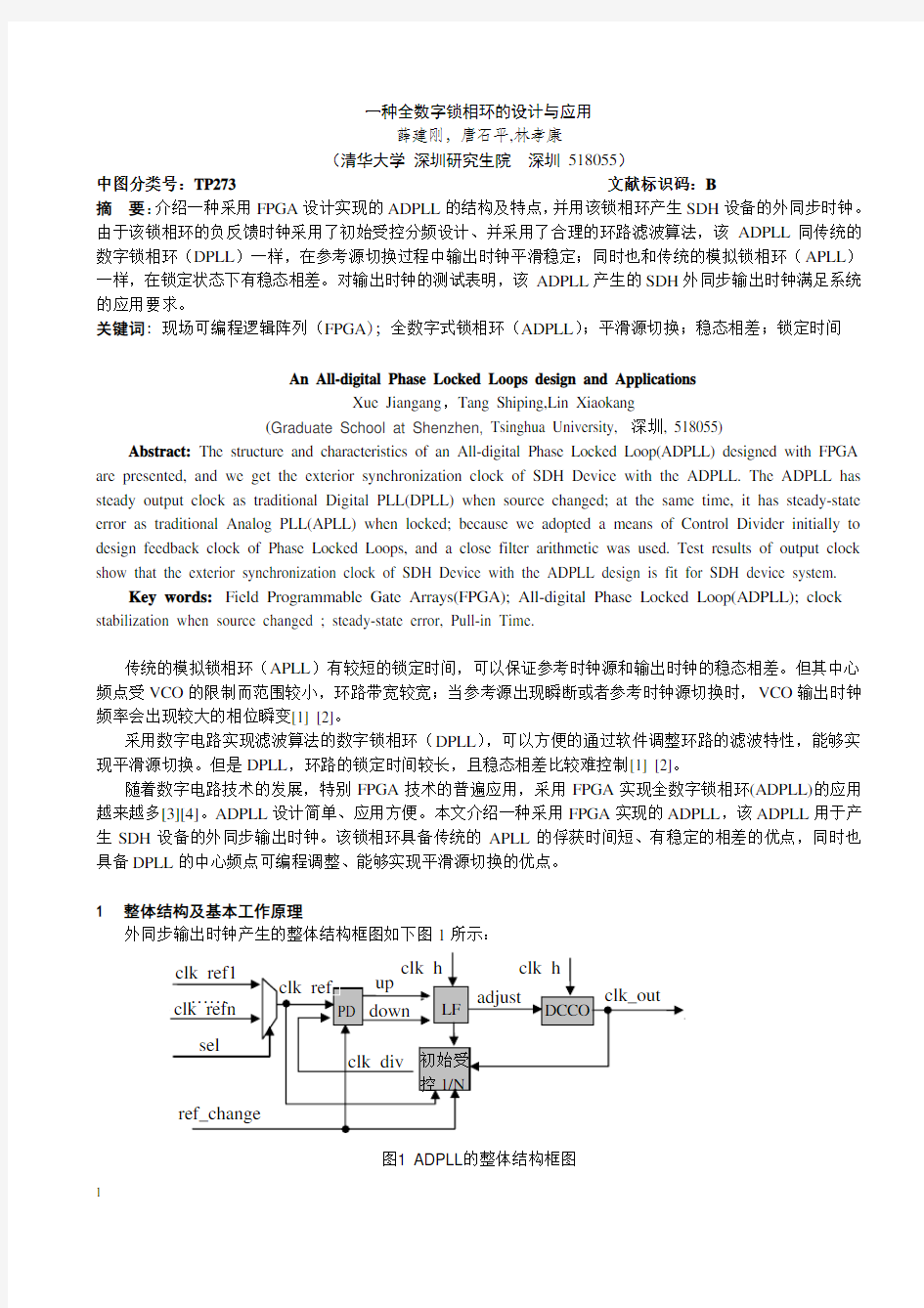

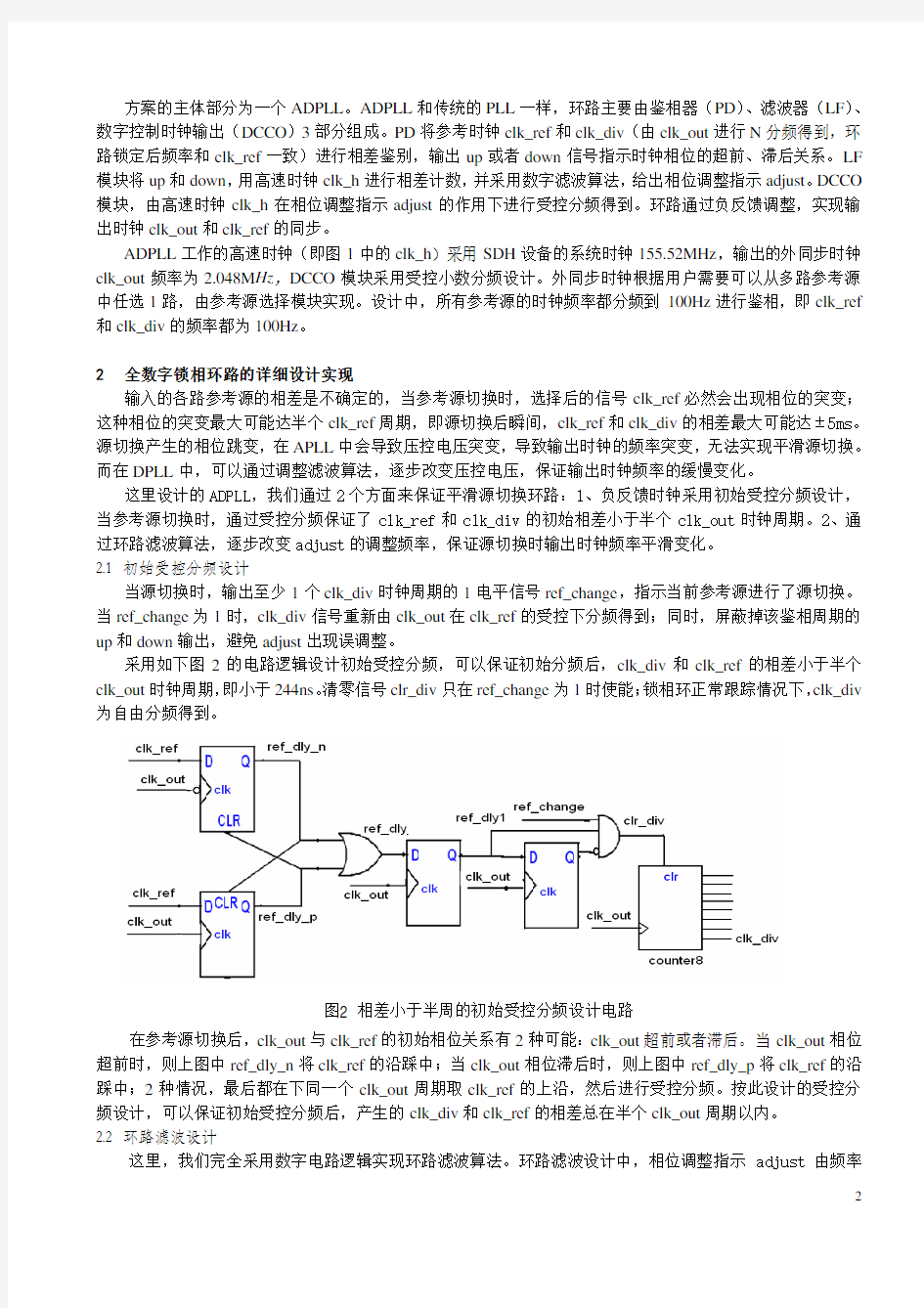

【摘要】介绍一种采用FPGA设计实现的ADPLL的结构及特点,并用该锁相环产生SDH设备的外同步时钟。由于该锁相环的负反馈时钟采用了初始受控分频设计、并采用了合理的环路滤波算法,该ADPLL同传统的数字锁相环(DPLL)一样,在参考源切换过程中输出时钟平滑稳定;同时也和传统的模拟锁相环(APLL)一样,在锁定状态下有稳态相差。对输出时钟的测试表明,该ADPLL产生的SDH外同步输出时钟满足系统的应用要求。

【总页数】3页(P.181-183)

【关键词】现场可编程逻辑阵列(FPGA);全数字式锁相环(ADPLL);平滑源切换;稳态相差;锁定时间

【作者】薛建刚;唐石平;林孝康

【作者单位】清华大学深圳研究生院,广东518128

【正文语种】英文

【中图分类】TP273

【相关文献】

1.一种应用于全数字锁相环的时间数字转换器设计 [J], 盖林冲; 陈岚; 王海永

2.一种全数字锁相环的设计与应用 [J], 薛建刚; 唐石平; 林孝康

3.全数字解调器中一种数字可编程跟踪锁相环的设计分析 [J], 刘向东

4.一种新型PID控制的全数字锁相环的设计与实现 [J], 卢辉斌; 张月强; 杨雪峰

相关主题