基于CMOS摄像头与FPGA的位置检测系统设计

第24卷 第5期

2009年10月

液 晶 与 显 示

Chinese Journal of Liquid Crystals and Displays

Vol 124,No 15Oct.,2009

文章编号:100722780(2009)0520746205

基于CMOS 摄像头与FPGA 的位置检测系统设计

徐正平1,2,葛文奇1,杨守旺1,2,运国勤1,2,赵秀影1,3,王德江1

(1.中国科学院长春光学精密机械与物理研究所,吉林长春 130033,E 2mail :xuzp090@https://www.360docs.net/doc/6e4650059.html, ;

2.中国科学院研究生院,北京 100039;

3.空军航空大学,吉林长春 130022)

摘 要:提出采用CMOS 数字摄像头采集并提取黑色胶条位置来控制冷却转鼓速度的方法。系统以FP GA 作为核心控制器,采用两片SRAM 进行乒乓操作,FP GA 根据CMOS 摄像头输出的同步信号,将采集到的图像信息存储到一片SRAM 中,同时读取另一片SRAM 中的图像数据并进行图像处理,黑色胶条位置检测采用简单的灰度阈值二值化方法。给出了部分采集图像及仿真结果。采集图像显示,CMOS 摄像头成像质量满足工程要求。仿真结果表明,系统实现了SRAM 的乒乓操作,并完成了黑色胶条位置检测。系统与冷却鼓连接,实际运行可靠。

关 键 词:CMOS 数字摄像头;位置检测;现场可编程逻辑器件;OV6620中图分类号:TP212.9 文献标识码:A

收稿日期:2009203215;修订日期:2009203226

基金项目:中国科学院长春光学精密机械与物理研究所创新工程资助项目(No.Z J 99130B );中国科学院知识创新工程领域前沿资

助项目(No.O70Y32R070)

1 引 言

密封胶条自动化生产过程包括胶条挤压成型、冷却及自动缠绕包装。挤压成型后的胶条粘性大,必须进行冷却后才能进行自动缠绕包装。可以将胶条缠绕在冷却鼓上进行自然冷却。自然冷却鼓的旋转速度需与胶条输出速度相匹配。若自然冷却鼓速度过大,胶条将会被拉伸,导致胶条厚度减小,甚至拉断;若自然冷却鼓速度过小,胶条将会堆积进而粘在一起。因此,必须实时检测胶条位置,以调节冷却鼓转速。数字摄像头已在非接触测量中得到了广泛应用[1,2]。由于CCD 摄像头驱动电路复杂[3-6],而CMOS 数字摄像头驱动电路简单,数据采集方便,所以本系统采用微小型CMOS 摄像头OV6620对胶条成像,将采集到的信息送入FP GA ,FP GA 对图像信息进行处理[7],将得到的位置信息经RS232串口传送到冷却鼓速度控制系统,以实时调整冷却鼓的转速。

2 系统结构设计与分析

系统整体结构分为4部分:CMOS 摄像头数

据采集与存储、数据处理及RS232串口通信。

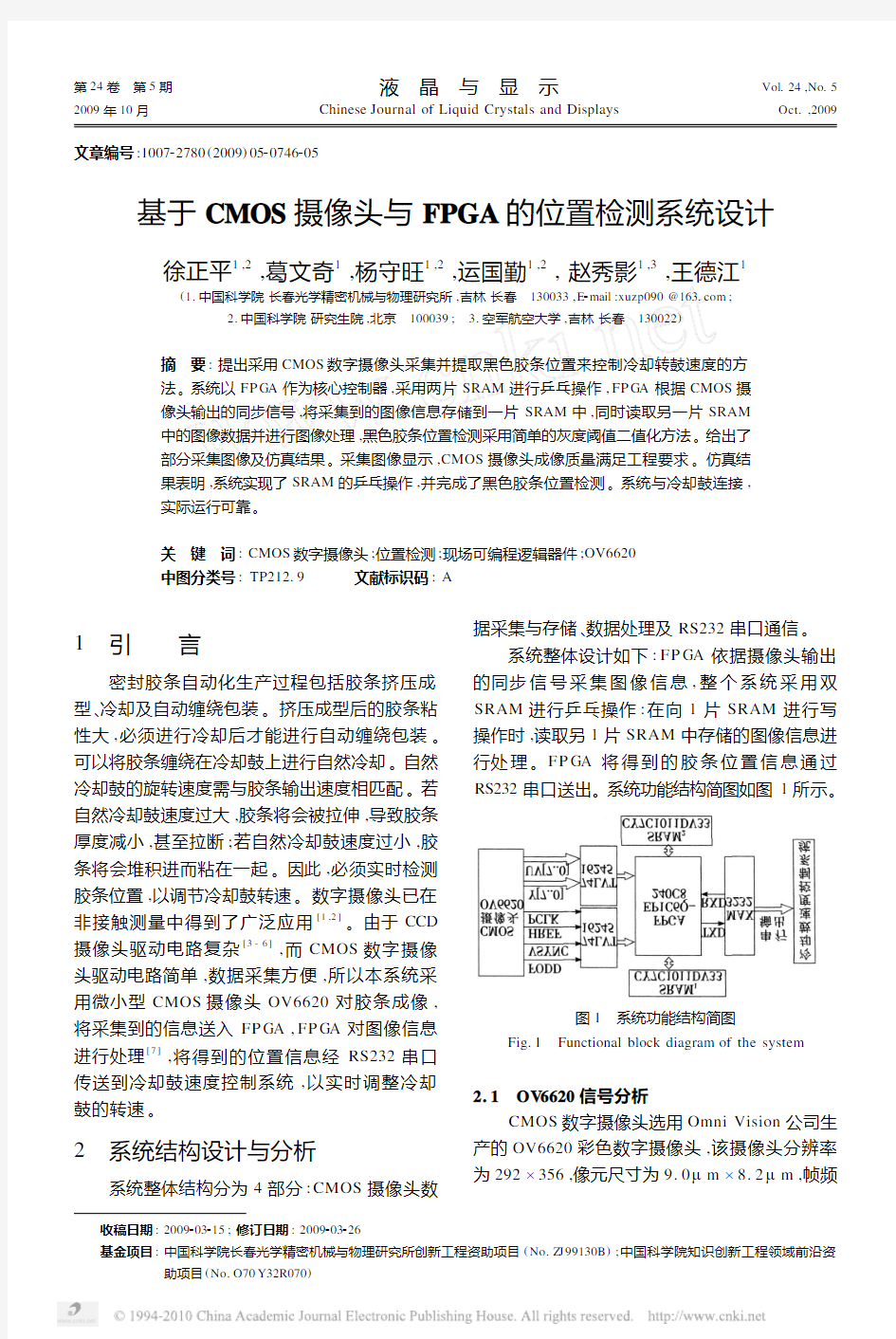

系统整体设计如下:FP GA 依据摄像头输出的同步信号采集图像信息,整个系统采用双SRAM 进行乒乓操作:在向1片SRAM 进行写

操作时,读取另1片SRAM 中存储的图像信息进行处理。FP GA 将得到的胶条位置信息通过RS232串口送出。系统功能结构简图如图1

所示。

图1 系统功能结构简图

Fig.1 Functional block diagram of the system

2.1 OV 6620信号分析

CMOS 数字摄像头选用Omni Vision 公司生

产的OV6620彩色数字摄像头,该摄像头分辨率

为292×356,像元尺寸为9.0μm ×8.2μm ,帧频

第5期徐正平,等:基于CMOS 摄像头与FP GA 的位置检测系统设计

747

为25Hz ,每帧两场:奇数场和偶数场,即每20ms 输出一场。数字输出格式为YCrCb 4∶2∶2,GRB 4∶2∶2,R G B 4∶2∶2可选。

OV6620上电后输出同步信号FODD ,VS YNC ,HREF ,PCL K 及图像灰度信号Y[7..0]、色度信号UV [7..0]。OV6620模块供电电

压为5V ,各输出信号为T TL 信号,FP GA I/O 口供电电压为3.3V ,因此,FPA G 与OV6620之间接口必须添加电平转换芯片,本系统选用74L V T16245。

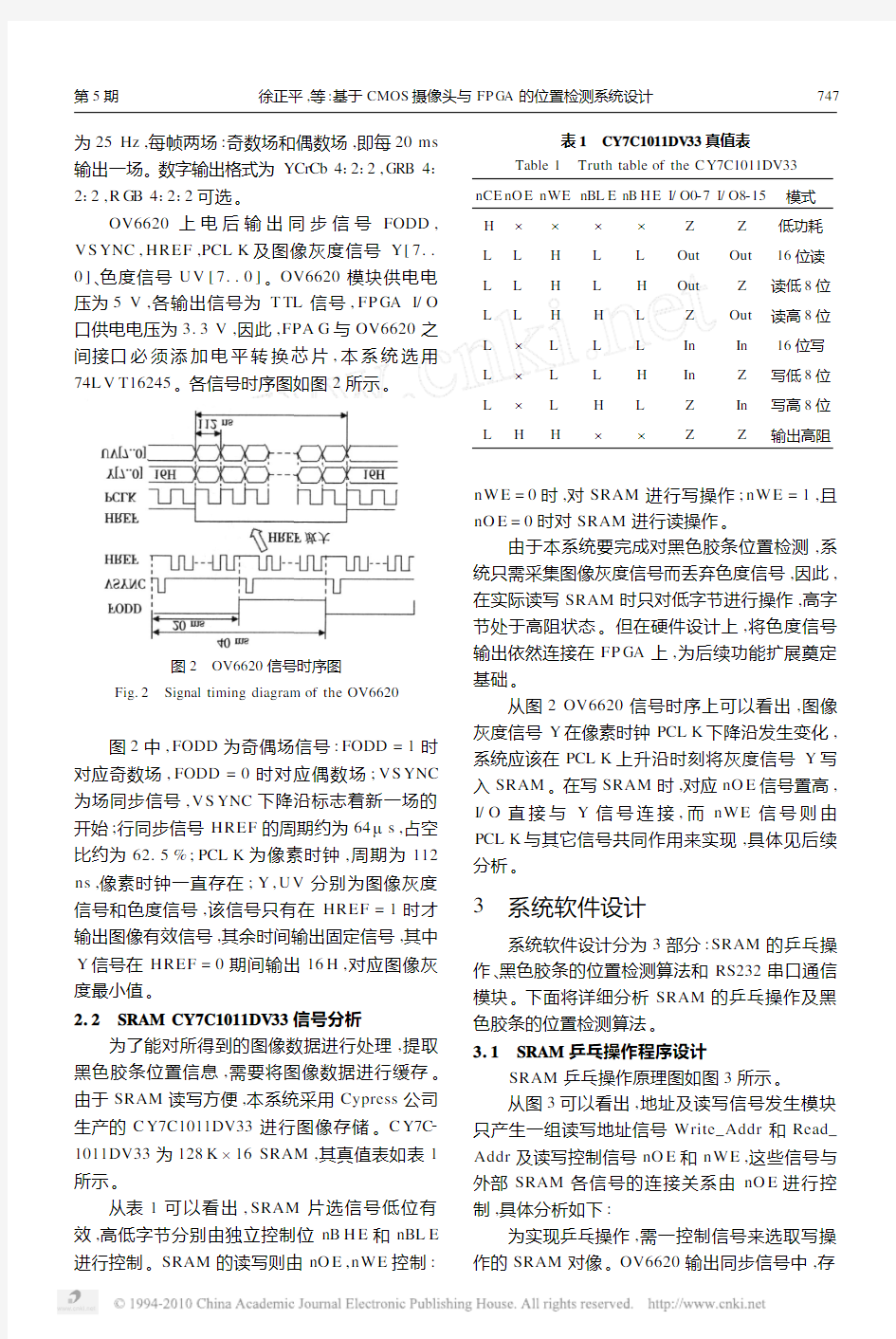

各信号时序图如图2所示。

图2 OV6620信号时序图

Fig.2 Signal timing diagram of the OV6620

图2中,FODD 为奇偶场信号:FODD =1时对应奇数场,FODD =0时对应偶数场;VS YNC 为场同步信号,VS YNC 下降沿标志着新一场的

开始;行同步信号HREF 的周期约为64μs ,占空比约为62.5%;PCL K 为像素时钟,周期为112ns ,像素时钟一直存在;Y ,UV 分别为图像灰度

信号和色度信号,该信号只有在HREF =1时才输出图像有效信号,其余时间输出固定信号,其中Y 信号在HREF =0期间输出16H ,对应图像灰

度最小值。

2.2 SRAM CY7C1011DV 33信号分析

为了能对所得到的图像数据进行处理,提取黑色胶条位置信息,需要将图像数据进行缓存。由于SRAM 读写方便,本系统采用Cypress 公司生产的C Y7C1011DV33进行图像存储。C Y7C 21011DV33为128K ×16SRAM ,其真值表如表1

所示。

从表1可以看出,SRAM 片选信号低位有效,高低字节分别由独立控制位nB H E 和nBL E 进行控制。SRAM 的读写则由nO E ,nWE 控制:

表1 CY7C1011DV 33真值表

Table 1 Truth table of the C Y7C1011DV33nCE nO E nWE nBL E nB H E I/O027I/O8215模式H ×

×

×

×

Z Z 低功耗

L L H L L Out Out 16位读

L L H L H Out Z 读低8位L L

H H L Z Out 读高8位

L ×L L L In In 16位写

L ×L L H In Z 写低8位L ×

L H

L

Z In 写高8位L

H

H

××

Z

Z

输出高阻

nWE =0时,对SRAM 进行写操作;nWE =1,且nO E =0时对SRAM 进行读操作。

由于本系统要完成对黑色胶条位置检测,系统只需采集图像灰度信号而丢弃色度信号,因此,在实际读写SRAM 时只对低字节进行操作,高字节处于高阻状态。但在硬件设计上,将色度信号

输出依然连接在FP GA 上,为后续功能扩展奠定基础。

从图2OV6620信号时序上可以看出,图像灰度信号Y 在像素时钟PCL K 下降沿发生变化,系统应该在PCL K 上升沿时刻将灰度信号Y 写入SRAM 。在写SRAM 时,对应nO E 信号置高,I/O 直接与Y 信号连接,而nWE 信号则由PCL K 与其它信号共同作用来实现,具体见后续

分析。

3 系统软件设计

系统软件设计分为3部分:SRAM 的乒乓操作、黑色胶条的位置检测算法和RS232串口通信模块。下面将详细分析SRAM 的乒乓操作及黑色胶条的位置检测算法。3.1 SRAM 乒乓操作程序设计

SRAM 乒乓操作原理图如图3所示。

从图3可以看出,地址及读写信号发生模块只产生一组读写地址信号Write_Addr 和Read_Addr 及读写控制信号nO E 和nWE ,这些信号与

外部SRAM 各信号的连接关系由nO E 进行控制,具体分析如下:

为实现乒乓操作,需一控制信号来选取写操作的SRAM 对像。OV6620输出同步信号中,存

748

液 晶 与 显 示第24

卷

图3 SRAM乒乓操作原理图

Fig.3 Schematic diagram of Ping2Pong operation

在奇偶场同步信号,如果将nO E与FODD相连接,当FODD=1时,Mem1_nO E=1,Mem1_ nWE=nWE,Mem1_Addr=Write_Addr,Mem1_ DataL=Write_Data,对SRAM1进行写操作; Mem2_nO E=0,Mem2_nWE=1,Mem1_Addr= Read_Addr,Read_Data=Mem2_DataL,对SRAM2进行读操作。当FODD=0时,分析方法类似,区别在于对SRAM2进行写操作,而对SRAM1进行读操作。经上述分析可知,采用图3所示电路可以满足对SRAM乒乓操作的要求。

SRAM地址线宽度为17位,系统将高8位作为行计数器,低9位作为列计数器。行计数器在HREF下降沿进行递增计数,行计数器在复位及行计数器溢出情况下清零;列计数器在PCL K 下降沿进行递增计数,列计数器在复位及列计数器溢出情况下清零。

产生控制信号的部分程序代码如下[8]:

nWE<=PCL K and HREF and(not H_O2 verflow)and(not P_Overflow);

nO E<=FODD;

Write_DataL<=Y;

nWE只有在HREF为高电平,且行列计数器均未溢出的情况下输出PCL K,即实现了对有效像素灰度值的存储,满足设计要求。

系统采集到的一幅黑色胶条图像如图4所示

。

图4 OV6620采集的黑色胶条图像

Fig.4 Black adhesive tape image sampled by OV6620

3.2 黑色胶条的位置检测算法

CMOS摄像头配套光学镜头焦距f=3.6 mm,实际检测胶条宽度d=5mm,应用中黑色胶条距离光学镜头的距离H,即物距约为35cm,则胶条宽度方向在焦平面所成像宽度L由式(1)决定:

L=

f

H

?d(1) 将上述数据代入式(1)可得:L=51.4μm。

第5期徐正平,等:基于CMOS 摄像头与FP GA 的位置检测系统设计749

摄像头像元尺寸b =8.2μm ,则CMOS 摄像头采集到的胶条图像在胶条宽度方向上对应的像元数n 为:

n =

51.4μm

8.2μm

≈6

(2)

由式(2)可见:在CMOS 采集图像中,有6行CMOS 感光像元对应黑色胶条宽度。

黑色胶条的位置检测采用简单的二值化算法:读取某一行像素灰度值,并将各像素灰度值与预先设置的灰度阈值进行比较,如果灰度值小于阈值的像素总数大于某一设定值,则认为该行即为黑色胶条位置。在本系统中,检测行数设置为230,每行检测100个像素;灰度阈值设置为30,

如果检测行像素灰度值小于30的像素数达到80,则认为该行即为胶条位置。胶条背景设置为

白色,按上述位置检测方法,只有检测像素中80%以上灰度值小于30,系统才认为检测行是胶

条位置,具有一定的抗干扰性。

本系统选取黑色胶条的下边沿作为胶条位置,即系统按照上述方法检测到某行检测像素中80%以上灰度值小于30时,将该行位置保留,继

续检测下一行,将最终符合条件的像素行作为胶条位置。原因如下:该位置检测系统的作用是给冷却转鼓速度控制系统提供黑色胶条随时间变化的相对位置信息,作为调速系统控制的依据,位置检测系统只需确保每次输出的位置均以胶条的下边沿为准即可。

4 系统仿真结果及分析

为便于观察仿真结果,对每帧图像取两行,每行取3个像素,在黑条检测时,灰度阈值设置为30,如果一行中有两个像素灰度值小于30,则认

为该行为黑色胶条位置。仿真波形如图5所示。

从仿真结果分析可知,系统实现了双

SRAM

图5 系统仿真结果

Fig.5 Simulation result of the system

的乒乓操作及对黑色胶条位置的检测。

在复位信号Reset 为低后FODD 的第一个跳变沿,FODD =0,Mem2_nO E =1,Mem2_nWE 产生写信号,系统将数据写入SRAM 2中;Mem1_nO E =0,Mem1_nWE =1,系统读取SRAM 1中

的数据并进行处理。在FODD 的第二个跳变沿,FODD =1,系统将数据写入SRAM 1,读取并处理SRAM 2中的数据。

每帧图像的第一行像素存储在SRAM 的地址0,1,2处,第二行像素存储在SRAM 的地址512,513,514处。第一帧图像6个像素灰度值分

别设定为:50,50,25,19,20,32,依据上述判断规则,胶条位置应在第1行(从第0行计),在VS YNC 上升沿后给出数据准备好信号Data _

Ready ,串口开始发送数据;第二帧图像6个像素

灰度值分别设定为:23,18,45,16,65,65,因此,胶条位置应在第0行,同样在VS YNC 上升沿后给出数据准备好信号Data_Ready 。系统实物照片如图6所示

。

图6 实物照片

Fig.6 Picture of the system

750 液 晶 与 显 示第24卷

5 结 论

提出了采用CMOS 摄像头采集并提取黑色胶条位置来控制冷却转鼓速度的方法,以实现黑色胶条生产自动化。在简单介绍系统结构的基础上,对所选用的器件特性和部分软件设计给予详

细分析,并给出采集图像及软件仿真结果。从采集图像结果可以看出,CMOS 摄像头成像质量满足使用要求,软件仿真显示系统能完成对黑色胶条位置的检测。将本系统与冷却鼓速度控制系统连接,实际运行情况良好,冷却鼓转速受控。

参 考 文 献:

[1]艾莉莉,袁峰,丁振良.应用线阵CCD 的空间目标外姿态测量系统[J ].光学精密工程,2008,16(1):1612165.[2]张忠元,邵承会.视觉反馈模糊控制随动系统[J ].液晶与显示,2008,23(4):4682472.

[3]金龙旭,李国宁,刘妍妍.帧转移型面阵CCD 驱动电路的设计[J ].光学精密工程,2008,16(6):114021145.[4]刘金国,余达,周怀得,等.面阵CCD 芯片KA I 21010M 的高速驱动系统设计[J ].光学精密工程,2008,16(9):

162221628.

[5]周怀得,刘海英,徐东,等.行间转移面阵CCD 的TDI 工作方式研究[J ].光学精密工程,2008,16(9):162921634.[6]徐正平,翟林培,葛文奇,等.亚像元的CCD 几何超分辨方法[J ].光学精密工程,2008,16(12):244722453.[7]于超,陈光武,石文静.基于FP GA 的信号采集及其频谱显示[J ].液晶与显示,2008,23(4):4992503.[8]潘松,黄继业.EDA 技术与V HDL (第2版)[M ].北京:清华大学出版社,2007.

Design of Position Detection System B ased on CMOS C amera and FPGA

XU Zheng 2ping 1,2,GE Wen 2qi 1,YAN G Shou 2wang 1,2,YUN Guo 2qin 1,2,ZHAO Xiu 2ying 1,3,WAN G De 2jiang 1

(1.Changchun I nstit ute of Optics ,Fine Mechanics and Physics ,Chi nese A cadem y of S ciences ,

Changchun 130033,China ,E 2mail :x uz p 090@https://www.360docs.net/doc/6e4650059.html,;

2.Graduate S chool of Chinese A cadem y of S ciences ,B ei j ing 100039,China;

3.A viation Universit y of A i r Force ,Changchun 130022,China )

Abstract

The met hod of controlling t he speed of cooling wheel wit h t he position of t he adhesive tape is pro 2posed.The po sition of t he adhesive tape is gained wit h t he CMOS digital camera.Based on t he core of FP GA ,two pieces of SRAM are used in t he system to achieve ping 2pong operation .According to t he synchronous signal p roduced by CMOS camera ,t he image is sampled and stored into one of t he two SRAMs by FP GA.At t he same time ,t he image data stored in t he ot her SRAM is read out and p ro 2cessed.To detect t he po sition of t he adhesive tape ,t he met hod of grey is used.One sampled image and t he simulation result are given.The sampled image shows t hat t he image quality of t he CMOS camera satisfy t he need of t he p roject.The simulation result shows t hat t he SRAM ping 2pong opera 2tion is realized and t he po sition detection of t he adhesive tape is completed.The system is connected wit h t he cooling wheel speed cont rol system and works reliably.K ey w ords :CMOS digital camera ;position detection ;FP GA ;OV6620

作者简介:徐正平(1983-),男,河南许昌人,博士研究生,主要研究方向为CCD 几何超分辨成像方法及基于DSP 、FP GA

的航空相机像面扫描控制系统设计。

CMOS模拟集成电路课程设计

电子科学与技术系 课程设计 中文题目:CMOS二输入与非门的设计 英文题目: The design of CMOS two input NAND gate 姓名:张德龙 学号: 1207010128 专业名称:电子科学与技术 指导教师:宋明歆 2015年7月4日

CMOS二输入与非门的设计 张德龙哈尔滨理工大学电子科学与技术系 [内容摘要]随着微电子技术的快速发展,人们生活水平不断提高,使得科学技术已融入到社会生活中每一个方面。而对于现代信息产业和信息社会的基础来讲,集成电路是改造和提升传统产业的核心技术。随着全球信息化、网络化和知识经济浪潮的到来,集成电路产业的地位越来越重要,它已成为事关国民经济、国防建设、人民生活和信息安全的基础性、战略性产业。 集成电路有两种。一种是模拟集成电路。另一种是数字集成电路。本次课程设计将要运用S-Edit、L-edit、以及T-spice等工具设计出CMOS二输入与非门电路并生成spice文件再画出电路版图。 [关键词]CMOS二输入与非门电路设计仿真

目录 1.概述 (1) 2.CMOS二输入与非门的设计准备工作 (1) 2-1 .CMOS二输入与非门的基本构成电路 (1) 2-2.计算相关参数 (2) 2-3.电路spice文件 (3) 2-4.分析电路性质 (3) 3、使用L-Edit绘制基本CMOS二输入与非门版图 (4) 3-1.CMOS二输入与非门设计的规则与布局布线 (4) 3-2.CMOS二输入与非门的版图绘制与实现 (5) 4、总结 (6) 5、参考文献 (6)

1.概述 本次课程设计将使用S-Edit画出CMOS二输入与非门电路的电路图,并用T-spice生成电路文件,然后经过一系列添加操作进行仿真模拟,计算相关参数、分析电路性质,在W-edit中使电路仿真图像,最后将电路图绘制电路版图进行对比并且做出总结。 2.CMOS二输入与非门的设计准备工作 2-1 .CMOS二输入与非门的基本构成电路 使用S-Edit绘制的CMOS与非门电路如图1。 图1 基本的CMOS二输入与非门电路 1

基于FPGA的多功能数据选择器设计与实现

基于FPGA的多功能数据选择器设计与实现 章军海201022020671 [摘要]传统的数字系统设计采用搭积木式的方法来进行设计,缺乏设计的灵活性。随着可编程逻辑器件(PLD)的出现,传统设计的缺点得以弥补,基于PLD的数字系统设计具有很好的灵活性,便于电路系统的修改与调试。本文采用自顶向下的层次化设计思想,基于FPGA设计了一种多功能数据选择器,实现了逻辑单元可编程、I/O单元可编程和连线可编程功能,并给出了本设计各个层次的原理图和仿真时序图;本文还基于一定的假设,对本设计的速度和资源占用的性能进行了优化。 [关键词]层次化设计;EDA;自顶向下;最大时延 0引言: 在现代数字系统的设计中,EDA(电子设计自动化)技术已经成为一种普遍的工具。基于EDA技术的设计中,通常有两种设计思想,一种是自顶向下的设计思想,一种是自底向上的设计思想[1]。其中,自顶向下的设计采用层次化设计思想,更加符合人们的思维习惯,也容易使设计者对复杂系统进行合理的划分与不断的优化,因此是目前设计思想的主流。基于层次化设计思想,实现逻辑单元、I/O单元和连线可编程可以提高资源的利用效率,并且可以简化数字系统的调试过程,便于复杂数字系统的设计[2][3]。 1系统原理图构架设计 1.1系统整体设计原理 本设计用于实现数据选择器和数据分配器及其复用的I/O端口和连线的可编程却换,提高系统的资源利用效率。系统顶层原理框图如图1所示,系统拥有两个地址选择端口a0、a1,一个功能选择端口ctr,还有五路I/O复用端口。其中,地址选择端口用于决定数据选择器的数据输入端和数据分配器的数据输出端;功能选择端口用于切换数据选择器和数据分配器,以及相应的I/O端口和连线;I/O复用端口数据的输入和输出,其功能表如表一所示。 图1顶层模块原理图 表一顶层系统功能表

网络摄像头使用说明书样本

ImagineWorldClient 网络视频服务器集中管理软件 说 明 书 ( 修订版-1)

目录 1、 ImagineWorldClient 功能........................... 错误!未定义书签。 2、安装ImagineWorldClient ........................... 错误!未定义书签。 3、启动ImagineWorldClient ........................... 错误!未定义书签。 3.1顶部工具栏..................................... 错误!未定义书签。 3.2顶部菜单栏..................................... 错误!未定义书签。 3.3左侧工具栏..................................... 错误!未定义书签。 3.4视频区......................................... 错误!未定义书签。 3.5底部工具栏..................................... 错误!未定义书签。4菜单操作及鼠标操作.................................. 错误!未定义书签。 4.1文件........................................... 错误!未定义书签。 4.2操作........................................... 错误!未定义书签。 4.3设置........................................... 错误!未定义书签。 4.4帮助........................................... 错误!未定义书签。 4.5鼠标操作....................................... 错误!未定义书签。5实时视频显示及控制.................................. 错误!未定义书签。 5.1 实时视频显示画面控制.......................... 错误!未定义书签。 5.1.1 显示模式切换............................. 错误!未定义书签。 5.1.2 单画面显示............................... 错误!未定义书签。 5.1.3 全屏显示................................. 错误!未定义书签。 5.1.4 轮巡监视................................. 错误!未定义书签。 5.2 云台控制...................................... 错误!未定义书签。 5.3分配摄像机..................................... 错误!未定义书签。6本地检索及录像回放.................................. 错误!未定义书签。 6.1录像检索....................................... 错误!未定义书签。

电子科技大学集成电路原理实验CMOS模拟集成电路设计与仿真王向展

实验报告 课程名称:集成电路原理 实验名称: CMOS模拟集成电路设计与仿真 小组成员: 实验地点:科技实验大楼606 实验时间: 2017年6月12日 2017年6月12日 微电子与固体电子学院

一、实验名称:CMOS模拟集成电路设计与仿真 二、实验学时:4 三、实验原理 1、转换速率(SR):也称压摆率,单位是V/μs。运放接成闭环条件下,将一个阶跃信号输入到运放的输入端,从运放的输出端测得运放的输出上升速率。 2、开环增益:当放大器中没有加入负反馈电路时的放大增益称为开环增益。 3、增益带宽积:放大器带宽和带宽增益的乘积,即运放增益下降为1时所对应的频率。 4、相位裕度:使得增益降为1时对应的频率点的相位与-180相位的差值。 5、输入共模范围:在差分放大电路中,二个输入端所加的是大小相等,极性相同的输入信号叫共模信号,此信号的范围叫共模输入信号范围。 6、输出电压摆幅:一般指输出电压最大值和最小值的差。 图 1两级共源CMOS运放电路图 实验所用原理图如图1所示。图中有多个电流镜结构,M1、M2构成源耦合对,做差分输入;M3、M4构成电流镜做M1、M2的有源负载;M5、M8构成电流镜提供恒流源;M8、M9为偏置电路提供偏置。M6、M7为二级放大电路,Cc为引入的米勒补偿电容。 其中主要技术指标与电路的电气参数及几何尺寸的关系:

转换速率:SR=I5 I I 第一级增益:I I1=?I I2 I II2+I II4=?2I I1 I5(I2+I3) 第二级增益:I I2=?I I6 I II6+I II7=?2I I6 I6(I6+I7) 单位增益带宽:GB=I I2 I I 输出级极点:I2=?I I6 I I 零点:I1=I I6 I I 正CMR:I II,III=I II?√5 I3 ?|I II3|(III)+I II1,III 负CMR:I II,III=√I5 I1+I II5,饱和 +I II1,III+I II 饱和电压:I II,饱和=√2I II I 功耗:I IIII=(I8+I5+I7)(I II+I II) 四、实验目的 本实验是基于微电子技术应用背景和《集成电路原理与设计》课程设置及其特点而设置,为IC设计性实验。其目的在于: 根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路设计,掌握基本的IC设计技巧。 学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行电路的模拟仿真。 五、实验内容 1、根据设计指标要求,针对CMOS两级共源运放结构,分析计算各器件尺寸。 2、电路的仿真与分析,重点进行直流工作点、交流AC和瞬态Trans分析,能熟练掌握各种分析的参数设置方法与仿真结果的查看方法。 3、电路性能的优化与器件参数调试,要求达到预定的技术指标。

基于FPGA的脉冲发生器的设计

【基础?应用】 基于FP GA 的脉冲发生器的设计 ① 张 涛 (北方交通大学电子信息工程学院,北京100044)【摘 要】 以脉冲发生器为研究对象,介绍了脉冲发生器的基本原理、硬件构成和实现方法,阐述了一种基于DSP -FP G A 数字系统的PWM 控制脉冲生成方法,并给出了仿真及实测实验结果。 【关键词】 脉宽调制;脉冲发生器;可编程门阵列 1 FP G A 简介 FP G A (Field Programmable G ate Array ,可编程门阵列)是美国Xinlinx 公司推出的一种采用单元型结构的新型PLD 器件。它采用CMOS 、SRAM 工艺制作,在结构上与阵列型PLD 不同,它的内部由许多独立的可编程逻辑单元构成,各逻辑单元之间可以灵活地相互连接,具有密度高、速度快、编程灵活和可重新配置等诸多优点。FP G A 已成为当前主流的PLD 器件之一。 1.1 PLD 的主要特点 (1)缩短研制周期。 (2)降低设计成本。用PLD 来设计和改造电子产品可以大幅度地减少印制板的面积和接插件,降低装配和调试费用。 (3)提高设计灵活性和可靠性。大量分立式元器件在向印制板上装配时,往往会发生由于虚焊或接触率近似于线性增加,且线性斜率较小;肝脏中大小不同的散射源对不同频率的声波存在有不同的散射效应。 由于肝脏组织结构的非均匀性、复杂性及其各部分散射相关长度分布的不一致性,其散射谱随深度增加而衰减变化,并非完全呈线性关系,而呈现较复杂的关系变化。 ⑵肝叶边缘部分及表层区域,其结构散射近似呈瑞利散射特征;肝叶表层以下与肝叶中心之间的中间区域,其结构散射呈随机散射特征;肝叶中心区域,其结构散射呈扩散漫射特征,也有较强的反射。 ⑶利用区域结构散射特征谱,不仅可对各特征区域组织微结构作出粗略估计,而且可通过区域散射谱特征的变化,对生物软组织的生理病理变化的判断提供依据。 综上所述,利用超声散射谱分析,可为B 超的形态学图像信息诊断提供一个组织特征的信息,在临床上是有应用前景的。 参考文献 [1]Luigi Landini et al.IEEE Trans on U FFC.1990,37(5):448-456 [2]陈启敏等.声学学报.1995,Vol.21,No.4:692-699 [3]E.J.Feleppa ,et al.IEEE Annual International Conference ,EMB ,1990;12(1):337 (责任编辑:常 平) 2003年4月第19卷第2期 武警工程学院学报JOURNAL OF EN GG COLL EGE OF ARMED POL ICE FORCE Apr.2003Vol.19No.2 ①收稿日期:2002-12-06作者简介:张涛(1968.07-),1994年毕业于西安交通大学工业电器自动化专业,现在北方交通大学电子信息工程学院电子与信息工程专业攻读硕士学位。

模拟cmos集成电路设计实验

模拟cmos集成电路设计实验 实验要求: 设计一个单级放大器和一个两级运算放大器。单级放大器设计在课堂检查,两级运算放大器设计需要于学期结束前,提交一份实验报告。实验报告包括以下几部分内容: 1、电路结构分析及公式推导 (例如如何根据指标确定端口电压及宽长比) 2、电路设计步骤 3、仿真测试图 (需包含瞬态、直流和交流仿真图) 4、给出每个MOS管的宽长比 (做成表格形式,并在旁边附上电路图,与电路图一一对应) 5、实验心得和小结 单级放大器设计指标 两级放大器设计指标

实验操作步骤: a.安装Xmanager b.打开Xmanager中的Xstart

c.在Xstart中输入服务器地址、账号和密码 Host:202.38.81.119 Protocol: SSH Username/password: 学号(大写)/ 学号@567& (大写)Command : Linux type 2 然后点击run运行。会弹出xterm窗口。 修改密码

输入passwd,先输入当前密码,然后再输入两遍新密码。 注意密码不会显示出来。 d.设置服务器节点 用浏览器登陆http://202.38.81.119/ganglia/,查看机器负载情况,尽量选择负载轻的机器登陆,(注:mgt和rack01不要选取) 选择节点,在xterm中输入 ssh –X c01n?? (X为大写,??为节点名) 如选择13号节点,则输入ssh –X c01n13 e.文件夹管理 通常在主目录中,不同工艺库建立相应的文件夹,便于管理。本实验采用SMIC40nm工艺,所以在主目录新建SMIC40文件夹。 在xterm中,输入mkdir SMIC40 然后进入新建的SMIC40文件夹, 在xterm中,输入cd SMIC40.

基于FPGA的模拟IIC接口设计与实现

研究生课程论文 课程名称基于FPGA的模拟IIC接口设计与实现授课学期2012 学年至2013 学年第一学期学院电子工程学院 专业电子与通信工程 学号2012011603 姓名 任课教师 交稿日期2013.01.10 成绩 阅读教师签名 日期 广西师范大学研究生学院制

基于FPGA的模拟I2C接口设计与实现 摘要:本文论述了I2C总线的基本协议,以及基于FPGA 的模拟I2C 总线接口模块的设计,在QuartusII软件中用Verilog HDL语言编写了部分I2C总线接口功能的程序代码,生成原理图模块。并连接好各个模块,进行了时序仿真。最后,下载到FPGA的板运行测试。 关键词:I2C 接口FPGA Verilog 1课题研究意义、现状及应用分析 目前市场上主流的嵌入式设备主要是微处理器、DSP等,但FPGA 以其独有的高抗干扰性、高安全性正在逐步取得开发公司的青睐,在FPGA上开发I2C势在必行。并且利用EDA 工具设计芯片实现系统的功能,已经成为支撑电子设计的通用平台,并逐步向支持系统级的设计方向发展。模块化的设计思想在软件设计过程中越来越被重视。I2C总线是Philips 公司推出的双向两线串行通讯标准,具有接口线少、通讯效率高等特点。因此,基于FPGA的I2C总线设计有着广泛的应用前景。

2课题总体方案设计及功能模块介绍 本设计主要分三大模块,分别是I2C 总线接口模块、按键输入控制模块、数码管显示模块。I2C总线模块集成了I2C协议用于和总线相接EEPROM的通信;按键输入控制模块用于控制I2C模块的页读、页写、字节读、字节写功能;数码管显示模块用于显示通过I2C总线读取EEPROM中的数据。 3I2C接口设计原理 I2C总线最主要的优点是其简单性和有效性。由于接口直接在组件之上,因此I2C总线占用的空间非常小,减少了电路板的空间和芯片管脚的数量,降低了互联成本。总线的长度可高达25英尺,并且能够以10 Kbps的最大传输速率支持40个组件。I2C总线的另一个优点是,它支持多主控(multimastering),其中任何能够进行发送和接收的设备都可以成为主总线。一个主控能够控制信号的传输和时钟频率。 3.1总线的构成 I2C总线是由数据线SDA和时钟SCL构成的串行总线,可发送和接收数据。在CPU与被控IC之间、IC与IC之间进行双向传送,最高传送速率100kbps。各种被控制电路均并联在这条总线上,但就像电话机一样只有拨通各自的号码才能工作,所以每个电路和模块都

网络摄像机手机使用说明书 - 高清监控系统套装,NVR显示 …

网络摄像机手机使用说明书 网络摄像机手机使用说明书 (1) 一、网络摄像机接入网络 (2) 二、手机软件安装 (4) 三、添加摄像机 (4) 1、二维码扫描自动输入。 (5) 2、通过搜索添加摄像机 (5) 3、手动填写添加摄像机 (5) 四、观看、抓拍、录像 (6) 1、观看 (6) 3、录像 (7) 3、预置位设置 (8) 五、设置摄像机 (9) 1、设置 (9) 2、布防 (15) 3、编辑 (15) 4、删除摄像机 (16)

一、网络摄像机接入网络 连接方式有三种: 网线连接:把网络摄像机电源,取网线一端接在网络摄像机上,一端接在路由器上。 WPS连接:把网络摄像机接上电源,同时按下网络摄像机后面板的WPS键和无线路由器后面板的WPS键,这样网络摄像机就能一键连接无线网了。(注:此方法需无线路由器具有WPS功能) AP模式连接:把网络摄像机接上电源,打开手机无线网,搜到ipcam_ainoia,密钥默认:88888888。连接上后进入客户端,通过局域网搜索连接摄像机。进入设置界面→网络设置→无线设置→选择自己的无线网→输入无线网密码,摄像机自动重启后即可接入无线网。

手机连接到自己的无线网,摄像机连接上无线网后,如下图所示,会显示无线图标:

二、手机软件安装 直接从随机附带光盘中获取对应手机系统的软件,然后安装在手机上。苹果用户需进入Store下载UCCAM。安装后显示图标 三、添加摄像机 打开软件,选择添加摄像机 有三种添加方式,第一种是通过扫描二维码输入UID 添加;第二种是摄像机和手机在同一路由器下,通过搜索添加;第三种是通过手动填写UID 添加。

【书】模拟CMOS集成电路设计 毕查德.拉扎维著

【简介】模拟集成电路的设计与其说是一门技术,还不如说是一门艺术。它比数字集成电路设计需要更严格的分析和更丰富的直觉。严谨坚实的理论无疑是严格分析能力的基石,而设计者的实践经验无疑是诞生丰富直觉的源泉。这也正足初学者对学习模拟集成电路设计感到困惑并难以驾驭的根本原因。. 美国加州大学洛杉机分校(UCLA)Razavi教授凭借着他在美国多所著名大学执教多年的丰富教学经验和在世界知名顶级公司(AT&T,Bell Lab,HP)卓著的研究经历为我们提供了这本优秀的教材。本书自2000午出版以来得到了国内外读者的好评和青睐,被许多国际知名大学选为教科书。同时,由于原著者在世界知名顶级公司的丰富研究经历,使本书也非常适合作为CMOS模拟集成电路设计或相关领域的研究人员和工程技术人员的参考书。... 本书介绍模拟CMOS集成电路的分析与设计。从直观和严密的角度阐述了各种模拟电路的基本原理和概念,同时还阐述了在SOC中模拟电路设计遇到的新问题及电路技术的新发展。本书由浅入深,理论与实际结合,提供了大量现代工业中的设计实例。全书共18章。前10章介绍各种基本模块和运放及其频率响应和噪声。第11章至第13章介绍带隙基准、开关电容电路以及电路的非线性和失配的影响,第14、15章介绍振荡器和锁相环。第16章至18章介绍MOS器件的高阶效应及其模型、CMOS制造工艺和混合信号电路的版图与封装。

模拟CMOS集成电路设计.part1.rar 模拟CMOS集成电路设计.part2.rar 模拟CMOS集成电路设计.part3.rar 模拟CMOS集成电路设计.part4.rar 模拟CMOS集成电路设计.part5.rar

基于fpga的eeprom设计

二线制I2C CMOS 串行EEPROM 的FPGA设计 姓名:钱大成 学号:080230114 院系:物理院电子系 2011年1月1日

一、课程设计摘要: (1)背景知识: A、基本介绍: 二线制I2C CMOS 串行EEPROM AT24C02/4/8/16 是一种采用CMOS 工艺制成的串行可用电擦除可编程只读存储器。 B、I2C (Inter Integrated Circuit)总线特征介绍: I2C 双向二线制串行总线协议定义如下: 只有在总线处于“非忙”状态时,数据传输才能被初始化。在数据传输期间,只要时钟线为高电平,数据线都必须保持稳定,否则数据线上的任何变化都被当作“启动”或“停止”信号。图1 是被定义的总线状态。· ①总线非忙状态(A 段) 数据线SDA 和时钟线 SCL 都保持高电平。 ②启动数据传输(B 段) 当时钟线(SCL)为高电平状态时,数据线(SDA)由高电平变为低电平的下降沿被认为是“启动”信号。只有出现“启动”信号后,其它的命令才有效。

③停止数据传输(C 段) 当时钟线(SCL)为高电平状态时,数据线(SDA)由低电平变为高电平的上升沿被认为是“停止”信号。随着“停在”信号出现,所有的外部操作都结束。 ④数据有效(D 段) 在出现“启动”信号以后,在时钟线(SCL)为高电平状态时数据线是稳定的,这时数据线的状态就要传送的数据。数据线(SDA)上的数据的改变必须在时钟线为低电平期间完成,每位数据占用一个时钟脉冲。每个数传输都是由“启动”信号开始,结束于“停止”信号。 ⑤应答信号 每个正在接收数据的EEPROM 在接到一个字节的数据后,通常需要发出一个应答信号。而每个正在发送数据的EEPROM 在发出一个字节的数据后,通常需要接收一个应答信号。EEPROM 读写控制器必须产生一个与这个应答位相联系的额外的时钟脉冲。在EEPROM 的读操作中,EEPROM 读写控制器对EEPROM 完成的最后一个字节不产生应答位,但是应该给EEPROM 一个结束信号。 C、3. 二线制I2C CMOS 串行EEPROM读写操作 ① EEPROM 的写操作(字节编程方式) 所谓EEPROM 的写操作(字节编程方式)就是通过读写控制器把一个字节数据发送到EEPROM 中指定地址的存储单元。其过程如下:EEPROM 读写控制器发出“启动”信号后,紧跟着送4 位I2C 总线器件特征编码1010 和3 位EEPROM 芯片地址/页地址XXX 以及写状态的R/W 位(=0),到总线上。这一字节表示在接收到被寻址的EEPROM 产生的一个应答位后,读写控制器将跟着发

高清1080P超高清遥控器摄像机、车钥匙摄像机使用手册

1080P超高清遥控器使用说明书 一、产品简介 感谢您选择本产品,本产品是全球首款真正具备1080P 高清摄录、外置存储功能的数码金属红外夜视遥控器,支持大容量Micro SD卡;它有多种实用的功能,时尚精致的外观,稳定卓越的质量,广泛多样的用途,将给您带去全新难忘的使用体验,是您身边不可缺少的实用工具。 本机主要功能为:高解析录像、高解析拍照、优质录音、WEBCAM、随身磁盘。 本产品具有的特点为:多功能、多用途、外观时尚酷炫、录像效果卓越、小巧便携、方便使用、稳定可靠、反应快速等。 本产品适用于:记者采访、突发事件记录、生活片段记录、娱乐休闲记录、体育运动记录、教学辅助记录、家庭安防监控、执法刑侦取证、旅行人文风景记录、户外探险记录、辅助记忆等等。

结构概述

1、关机键(确认键) 2、模式键 3、夜视灯 开关键 4、摄像头 5、夜视灯 6、挡片扣孔、 7、TF卡 8、USB 9、挂绳孔 10、指示灯观察孔 三、产品特点 1、功能操作,震动提示。人机互动,完美接 触。 2、金属壳体,做工精良。隐藏式指示灯。 3、夜视功能,支持低照度录像。 4、支持1920*1080每秒30帧录像。

5、机器小巧,内置260毫安高容量电池。 四、产品操作说明 1、充电: 本机内置可充电锂电池,初次使用本机时,请先进行充电, 接通电源机器开始充电时,会有震动提示。机器可以通过以下方式充电: 1), 连接计算机充电, 使用USB数据线与计算机连接, 即可充电。 2), 用充电器充电, 使用USB数据线与充电器连接, 再把充电器插上 电插座,即可充电。 充电时, 蓝灯熄灭红灯闪烁表示充电, 机器充满电时红灯长亮。 2、震动提示状态: 您发出的每一个命令。当机器开始执行命令时,都会给您一个回复。 机器开/关机时,机器震动提示3秒钟。 录像:录像待机模式、开始录像、保存录像。机器震动提示一 次, 拍照:拍照待机模式、拍照成功。机器震动提示一次, 单独录音:录音待机模式、开始录音、保存录音。机器震动提 示一次, 移动侦测:移动侦测待机模式、开始录像、手动保存录像。机 器震动提示一次, 夜视灯:夜视灯的开启、关闭,机器连续2次震动提示。 3、机器指示灯表示状态: 1、电池电量不足时,机器红灯会快速闪烁并关机。当前录制的档会自动保存。

基于FPGA芯片的最小系统设计

黑龙江大学本科生 毕业论文(设计)档案编码: 学院:电子工程学院 专业:电子信息工程 年级:2007 学生姓名:王国凯 毕业论文题目:基于FPGA 的电梯自动控制 系统设计

摘要 本文在介绍了在当前国内外信息技术高速发展的今天,电子系统数字化已成为有目共睹的趋势。从传统的应用中小规模芯片构成电路系统到广泛地应用单片机,直至今天FPGA 在系统设计中的应用,电子设计技术已迈人了一个全新的阶段。FPGA 利用它的现场可编程特性,将原来的电路板级产品集成为芯片级产品,缩小体积,缩短系统研制周期,方便系统升级,具有容量大、逻辑功能强,提高系统的稳定性,而且兼有高速、高可靠性。越来越多的电子设计人员使用芯片进行电子系统的设计,通过基于FPGA 电梯系统开发设计,说明了FAPG 芯片研究的动机和研究意义。 关键词 FPGA;电梯系统;FLEX10K;JTAG;模块设计

Ab s t ract This paper introduces the rapid development of information technology around the world today. Digitalized electronic systems have become the trend. From the traditional application of small and medium-chip circuitry to Microcontroller and FPGA application in system design, electronic design technology is stepping into a new field. By using its field programmable features, FPGA changes the original circuit board-level products to the chip-level integration products. Now FPGA has advantages of reduced the size, shorten development cycle, facilitated in system upgrades, highly capacity, strong logic functions, stable system and high speed. More and more electronic designers use FPGA to design electronic systems. This paper shows the motivation and significance of designing by FPGA through the elevator FPGA system design. Ke ywo r d FPGA; Mini-System; FLEX10K; JTAG;Module design

高清网络摄像机使用说明书

高清网络摄像机使用手册

声明 本手册可能在某些技术细节方面描述不够准确或存在印刷错误,假如您在使用过程中按照使用手册无法解决问题时,请致电我公司技术部垂询相关操作方法。本手册的内容将做不定期的更新,恕不另行通知。 ?远离高温的热源和环境;避免阳光直接照射; ?为确保摄像机的正常散热,应避开通风不良的场所,注意防水,防潮,防雷。如需安装到户外,则需要安置防水箱,将摄像机固定其中; ?本机应水平安装或壁挂安装,避免安装在会剧烈震动的场所,勿将其它设备放于本机上。 2、避免电击和失火 ?切记勿用湿手触摸电源和摄像机; ?勿将液体溅落在摄像机上,以免造成机器内部短路或失火; ?勿将其它设备直接放置于本摄像机上部; ?非专业人员请勿自行拆开机壳,避免损坏和电击; 3、运输与搬运 ?本机的包装经过抗震设计和实验,确保在运输过程中摄像机不会受到意外损坏,所以在搬运本机时,最好使用原来的包装材料和纸箱; ?避免在过冷、过热的场所间相互搬动摄像机,以免机器内部产生结露,影响机器的使用寿命;?严禁带电搬动本机,否则会损坏主板;

目录 1 产品简介 (4) 1.1产品简介 (4) 1.2功能简介 (4) 1.3技术规格 (4) 2 外观与说明 (5) 3 设备与安装 (6) 3.1 运行环境 (7) 3.2 设备安装 (7) 4 IE 版客户端 (7) 4.1 准备工作 (7) 4.2 开始登陆 (7) 4.3 功能简介 (8) 4.3.1实时监视 (8) 4.3.2录像回放 (10) 4.3.3 参数设置 (11) 4.3.3.1基本信息设置 (12) 4.3.3.2网络参数设置 (15) 4.3.3.3通道参数设置 (20) 4.3.3.4报警参数设置 (24) 4.3.3.5前端存储设置 (26) 5.常见问题解答 (29) 5.1无法通过浏览器访问网络摄像机 (29) 5.2云台或球型摄像机不能控制 (30) 5.3程序升级以后,无法正常播放视频 (30) 5.4如何使网络摄像机在公网(Internet)上进行视频传输服务 (30) 5.5为何正常数据不能通过交换机 (31) 5.6为何升级后通过浏览器访问网络摄像机会出错 (31) 6.附录 (32) 附录A关于网络摄像机端口占用(映射)的问题说明 (32) 附录B 出厂默认参数 (33) 7.术语解释 (34)

cmos模拟集成电路设计_实验报告

北京邮电大学 实验报告 实验题目:cmos模拟集成电路实验 姓名:何明枢 班级:2013211207 班内序号:19 学号:2013211007 指导老师:韩可 日期:2016 年 1 月16 日星期六

北京邮电大学电子工程学院2013211207班何明枢CMOS模拟集成电路与设计实验报告 目录 实验一:共源级放大器性能分析 (1) 一、实验目的 (1) 二、实验内容 (1) 三、实验结果 (1) 四、实验结果分析 (3) 实验二:差分放大器设计 (4) 一、实验目的 (4) 二、实验要求 (4) 三、实验原理 (4) 四、实验结果 (5) 五、思考题 (6) 实验三:电流源负载差分放大器设计 (7) 一、实验目的 (7) 二、实验内容 (7) 三、差分放大器的设计方法 (7) 四、实验原理 (7) 五、实验结果 (9) 六、实验分析 (10) 实验五:共源共栅电流镜设计 (11) 一、实验目的 (11) 二、实验题目及要求 (11) 三、实验内容 (11) 四、实验原理 (11) 五、实验结果 (15) 六、电路工作状态分析 (15) 实验六:两级运算放大器设计 (17) 一、实验目的 (17) 二、实验要求 (17) 三、实验内容 (17) 四、实验原理 (21) 五、实验结果 (23) 六、思考题 (24) 七、实验结果分析 (24) 实验总结与体会 (26) 一、实验中遇到的的问题 (26) 二、实验体会 (26) 三、对课程的一些建议 (27)

实验一:共源级放大器性能分析 一、实验目的 1、掌握synopsys软件启动和电路原理图(schematic)设计输入方法; 2、掌握使用synopsys电路仿真软件custom designer对原理图进行电路特性仿真; 3、输入共源级放大器电路并对其进行DC、AC分析,绘制曲线; 4、深入理解共源级放大器的工作原理以及mos管参数的改变对放大器性能的影响 二、实验内容 1、启动synopsys,建立库及Cellview文件。 2、输入共源级放大器电路图。 3、设置仿真环境。 4、仿真并查看仿真结果,绘制曲线。 三、实验结果 1、实验电路图

FPGA设计方案

FPGA课程设计 题目:全天候温度纪录仪的设计与FPGA实现 姓名: 学号: 院系:信息科学与工程学院 专业:计算机技术

摘要 本设计有效的克服了传统的数字温度计的缺点,采用自上而下的设计思路,绘制出了系统结构流程图,最后又在硬件上通过对其进行调试和验证。基于FPGA在Quartus II13.0软件下应用Verilog HDL语言编写程序,采用ALTRA公司Cyclone- IV系列的EP4CE40F23I7 芯片进行了计算机仿真,并给出了相应的仿真结果。该电路能够实现很好的测温功能。 关键字:数字温度计;FPGA;Quartus II130.;Verilog HDL;EP4CE40F2317 Abstract This design effectively overcomes the traditional digital thermometer’s wea knesses and takes a top-down approach to design flow chart of system, and fi nally pass the circuits to the hardware to debug and verify it. This design is b ased on FPGA using Verilog HDL language to write program in Quartus II sof tware, adopting EP4CE40F23I7 chip of Cyclone- IV series of ALTRA company for computer simulation and at the same time showing the corresponding sim ulation result. This circuit is able to carry out excellent temperature- measurem ent function. KeyWords:Digital thermometer;FPGA;Quartus II 13.0;Verilog HDL ;EP4CE40F2317

高清摄像机说明书

VC-A50 高清摄像机 (Camera) 安装手册-简体中文 [重要]

目录 版权资讯 (3) 第 1 章安全指示 (4) 安全措施 (5) FCC 警告 (5) EN55022 (CE 辐射) 警告 (5) KCC警告 (5) 第 2 章配件清单 (6) 第 3 章产品操作说明图 (7) 3.1产品说明 (7) 3.2LED灯号指示说明 (7) 第 4 章安装说明 (8) 4.1安装前准备 (8) 4.2安装说明 (8) 4.3链接装置 (16) 第 5 章遥控器按键与屏幕菜单介绍 (19) 5.1遥控器按键功能说明 (19) 5.2屏幕菜单 (20) 第 6 章常用功能说明 (27) 6.1我要切换VC-A50 (27) 6.2我要储存目前的镜头位置数据 (27) 6.3我要清除储存的位置数据 (27) 6.4我要开启背光补偿功能 (27) 6.5我要调整镜头的拍摄角度 (27) 6.6我要放大/缩小影像 (27)

6.7我要调整焦距 (28) 6.8我要调整聚焦速度 (28) 6.9我要设定影像模式 (29) 6.10我要冻结影像 (29) 6.11我要旋转影像 (29) 6.12我要改变摄像机的转向 (29) 6.13我要显示目前状态 (29) 第7 章DIP 切换设定 (30) 7.1DIP SWITCH (30) 7.2RS-422连接 (32) 第8 章常见问题排除 (34)

版权资讯 版权所有? Lumens Digital Optics Inc.保留所有权利。 Lumens 为Lumens Digital Optics Inc.正进行注册的商标。 若未获得Lumens Digital Optics Inc.书面同意,不得以任何方式复制、重制、或传送本档,除非因为购买本产品可复制本文件当备份。 为了持续改进产品,产品规格变更恕不另行通知。本文信息如果变更,恕不另行通知。敬请谅解! 其他公司或产品的名称可能会出现在本手册中,仅出于完整解释或描述本产品如何使用之需,并无侵权之意。 免责声明:对于本文可能之技术或编辑错误或遗漏;Lumens Digital Optics Inc. 恕不负责。

高清网络摄像机客户端使用说明

客户端使用说明2011-06-27

目录 一.安装说明 (4) 1.1安装要求 (4) 1.2安装步骤 (4) 二、客户端详细说明 (6) 2.1登录和退出 (6) 2.2软件界面说明 (6) 2.3设备管理 (8) 2.3.1设备添加 (8) 2.3.2分组管理 (10) 2.4图像预览 (11) 2.4.1非循切预览 (11) 2.4.2循切预览 (13) 2.5云台控制 (13) 2.5.1云台控制 (13) 2.5.2预置点设置 (14) 2.5.3图像色彩设置 (14) 2.6录像管理 (15) 2.6.1计划录像 (15) 2.6.2告警录像 (16) 2.6.3手动录像 (17) 2.7录像回放 (17) 2.7.1时间搜索回放 (17) 2.7.2搜索文件回放 (19) 2.8电子地图 (19) 2.8.1添加地图 (19) 2.8.2编辑地图 (19) 2.8.3删除地图 (20) 2.9参数设置 (20) 2.9.1色彩 (20) 2.9.2视频 (20) 2.9.3音频 (21) 2.9.4OSD (21) 2.9.5网络 (21) 2.9.6移动侦测 (21) 2.9.7云台 (22) 2.9.8系统 (22) 2.10用户管理 (22) 2.10.1添加用户 (23) 2.10.2删除用户 (23)

2.10.3修改用户权限 (23) 2.10.4修改用户密码 (23) 2.11日志 (24) 2.11.1日志保存时间 (24) 2.11.2日志查询 (24) 2.11.3日志备份 (24) 2.12其它设置 (25)

基于FPGA的简易的ALU设计

本科毕业设计开题报告 题目:基于FPGA的简易的ALU设计 院(系): 班级: 姓名: 学号: 指导教师: 教师职称:讲师

xxxxx学院本科毕业设计开题报告 题目基于FPGA的简易ALU设计来源工程实际 1、研究目的和意义 从20 世纪中叶的无线电时代,到21 世纪以计算机技术为中心的智能化加信息化的现代电子时代,电子系统发生了巨大的变化。现代电子系统愈发庞大和复杂,很多应用要求能够在现场进行实时的高速运算,并对系统进行有效地控制。作为这一需求的解决方案,嵌入式计算机应用系统已成为现代电子系统的核心技术。 早期的嵌入式系统是将通用计算机经改装后嵌入到被测控对象去,实现数据采集、分析处理、状态显示、输出控制等功能。随着大规模集成电路技术的发展,中央处理器CPU、随机存取存储器RAM、只读存储器ROM、输入/输出端口I/O等主要的计算机功能部件可以集成在一块集成电路芯片上,这颗芯片就被称为单片机。与改装普通计算机相比,单片机具有性能高、速度快、体积小、价格低、稳定可靠、应用广泛、通用性强等突出优点,因此迅速成为最普及的嵌入式应用系统方案。 通常,我们要实现一些功能可以用单片机来完成,但是,用可编程逻辑FPGA同样可以实现。在计算机中,算术逻辑单元(ALU)是专门执行算术和逻辑运算的数字电路。ALU是计算机中央处理器的最重要组成部分,甚至连最小的微处理器也包含ALU作计数功能。此次我要完成的设计是基于FPGA的四位ALU算数逻辑单元设计。通过对ALU功能的拓展,来实现更快更好的运算功能,相信这一功能的实现将使运算功能更加简单、快捷、准确,从而提高我们今后的学习工作效率。 2、发展情况(文献综述) 算术逻辑单元(arithmetic logic unit,缩写ALU)是进行整数运算的结构。现阶段是用电路来实现,应用在电脑芯片中。 在计算机中,算术逻辑单元(ALU)是专门执行算术和逻辑运算的数字电路。ALU是计算机中央处理器的最重要组成部分,甚至连最小的微处理器也包含ALU作计数功能。在现代CPU和GPU处理器中已含有功能强大和复杂的ALU;一个单一元件也可能含有ALU。 1945年数学家冯诺伊曼在一篇介绍被称为EDV AC的一种新型电脑的基础构成的报告中提出ALU的概念。 早期发展:1946年,冯诺伊曼与同事合作为普林斯顿高等学习学院(IAS)设计计算机。随后IAS计算机成为后来计算机的原形。在论文中,冯诺伊曼提出他相信计算机中所需的部件,其中包括ALU。冯诺伊曼写到,ALU是计算机的必备组成部分,因为已确定计算机一定要完成基本的数学运算,包括加减乘除。于是他相信计算机应该含有专门完成此类运算的部件。 ①数字系统 ALU必须使用与数字电路其他部分使用同样的格式进行数字处理。对现代处理器而言,几乎全都使用二进制补码表示方式。早期的计算机曾使用过很多种数字系统,包括反码、符号数值码,甚至是十进制码,每一位用十个管子。以上这每一种数字系统所对应的ALU都有不同的设计,而这也影响了当前对二进制补码的优先选择,因为二进制补码能简化ALU加法和减法的运算。 ②可行性分析 绝大部分计算机指令都是由ALU执行的。ALU从寄存器中取出数据,数据经过处理将运算结果存入ALU输出寄存器中。其他部件负责在寄存器与内存间传送数据,控制单元控制着ALU,通过控制电路来告诉ALU该执行什么操作。 ③简单运算 大部分ALU都可以完成以下运算∶整数算术运算(加、减,有时还包括乘和除,不过成本