北理工通信课程设计报告

本科实验报告

实验名称:锁相式数字频率合成器的设计

课程名称:通信电路与系统实验时间:3月3日-14日任课教师:实验地点:

实验教师:

实验类型:

□原理验证

√综合设计

□自主创新

学生姓名:

学号/班级:组号:

学院:同组搭档:

专业:成绩:

锁相频率合成器的设计

班级: 姓名: 评分:

一、 设计任务和技术指标

1. 工作频率范围:300kHz —700kHz

2. 电源电压:Vcc=5V

3. 通过原理图确定电路,并画出电路图

4. 计算元件参数选取电路元件(R1,R2,C1,R1ˊ,R2ˊ及环路滤波器的配置)

5. 组装连接电路,并测试选取元件的正确性

6. 调试并测量电路相关参数(测量相关频率点,输出波形,频率转换时间t c )

7.

总结并撰写实验报告

二、 设计方案

锁相频率合成器原理

锁相环(PLL )是一个相位误差控制系统,利用反馈控制原理实现频率及相位的同步技术。锁相环通过比较输入信号和压控振荡器输出频率之间的相位差,产生误差控制电压来调整压控振荡器的频率,以达到与输入信号同频。

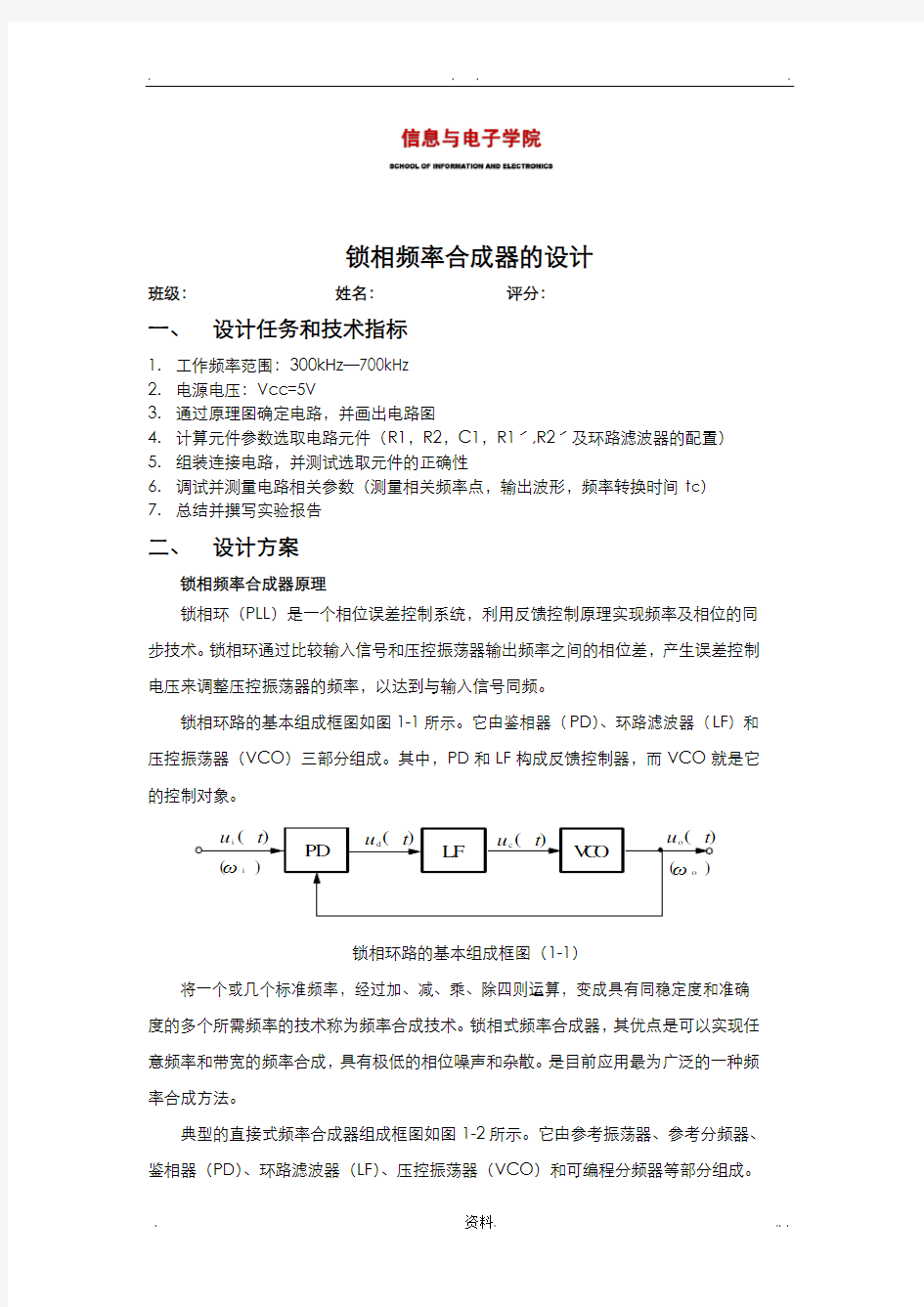

锁相环路的基本组成框图如图1-1所示。它由鉴相器(PD )、环路滤波器(LF )和压控振荡器(VCO )三部分组成。其中,PD 和LF 构成反馈控制器,而VCO 就是它的控制对象。

( )

u t i PD

L F

V C O

( )u t d ( )u t c ( )u t o ( )ωi

( )ωo

锁相环路的基本组成框图(1-1)

将一个或几个标准频率,经过加、减、乘、除四则运算,变成具有同稳定度和准确度的多个所需频率的技术称为频率合成技术。锁相式频率合成器,其优点是可以实现任意频率和带宽的频率合成,具有极低的相位噪声和杂散。是目前应用最为广泛的一种频率合成方法。

典型的直接式频率合成器组成框图如图1-2所示。它由参考振荡器、参考分频器、鉴相器(PD )、环路滤波器(LF )、压控振荡器(VCO )和可编程分频器等部分组成。

直接式频率合成器(图1-2)

由图1-2可知,晶体振荡器的频率i f 经过M 固定分频后得到步进参考频率REF f ,将REF

f 信号作为鉴相器的基准与N 分频器的输入进行比较,鉴相器的输出Ud 正比于两路输入信号的相位差,Ud 经过环路滤波器得到一个平均电压Uc ,Uc 控制压控振荡器(VCO )频率0f 的变化,使鉴相器的两路输入信号相位差不断减小,直到鉴相器的输入为零或者某一直流电平,这时称为锁定。锁定后的频率为0//i REF f M f N f ==即0(/)i REF f N M f N f ==。当预置分频数N 变化时,输出信号频率0f 随着发生变化。

锁相环中的滤波器时间常数据定了跟随输入信号的速度,同时也限制了锁相环的捕捉范围。

三、 电路原理与设计

1.CD4046锁相环工作原理

CD4046是通用的CMOS 锁相环集成电路,其特点是电源电压范围宽(为3V -18V ),输入阻抗高(约100M Ω),动态功耗小,在中心频率f0为10kHz 下功耗仅为600μW ,属微功耗器件。 CD4046是带有RC 型VCO 的锁相环路,属于低频锁相环路。采用 16 脚双列直插式,图1-3为CD4046的内部功能框图和构成锁相频率合成器时的外围元件连接图。从图中可以看出,CD4046主要由相位比较Ⅰ、Ⅱ、压控振荡器(VCO )、线性放大器、源跟随器、整形电路等部分构成。芯片内含有一个低功耗、高线性VCO ,两个工作方式不同的鉴相器PDI 和PDII ,A1为PDI 和PDII 的公用输入基准信号放大器,源跟随器A2与VCO 输入端相连是专门作FM 解调输出之用的,此外还有一个6V 左右的齐纳稳压管。CD4046的管脚排列图如图1-4。

DD

( )Text

A 1

VCO

A 2

PDII

PDI

144

16

10

325

9

6111278

15

V t

f i

u v u i 1

13

3

R 4

R 2

R 1

R 5

R C

C ( )f v

1-3 CD4046的内部功能图 1-4 CD4046引脚图

符号 引脚 名称功能

Ph03 1 输出端(相位脉冲输出) 相位比较器2输出的相位差信号,为上升沿控制逻辑。环路人锁时为高电平,环路失锁时为低电平

Ph11

14

相位比较器输入端(基准信号输入 ),相位比较器输入信号,输入允许将0.1V 左右的小信号或方波信号在内部放大并再经过整形电路后,输出至相位比较器。

PH12 3 相位比较器输入端(比较信号输入) 通常PD 来自VCO 的参考信号。 PH01 2 PD Ⅰ输出端 相位比较器1输出的相位差信号,它采用异或门结构,即鉴相特性为 。

PH02 13 PD Ⅱ输出端 相位比较器Ⅱ的输出端,它采用,上升沿控制逻辑。 VC01 9 压控振荡器的控制端。 VC00 4 压控振荡器输出端

INH 5 VCO 禁止端,1有效 控制信号输入,高电平时禁止,低电平时允许压控振荡器工作。 R1 11 VCO 外接电阻R1 R2 12 VCO 外接电阻R2

C1 6.7 并接振荡电容C1,以控制VCO 的振荡频率。 DEM0 10

解调信号输出端

15

内部独立的齐纳稳压二极管负极。

2.参考振荡器工作原理

参考振荡器可采用门电路(74LS 系列或CD 系列)与标称石英晶体构成振荡器。石英晶体振振器的电路符号、等效电路、电抗曲线如图1-5所示。工作电路图如1-6所示。

1-5晶振1-6参考晶体振荡器电路图从石英晶体谐振器的电抗特性可看出,在串、并联谐振频率之间很狭窄的工作频带内,它呈电感性。因而石英振荡器可以工作于感性区和串联谐振频率上,但不能使用容

性区。根据晶体在振荡电路中的不同作用,振荡电路可分为两类:一类是石英晶体在电

路中作为等效电感元件使用,这类振荡器称为并联型晶体振荡器;另一类是把石英晶体

作为串联谐振元件使用,使它工作于串联谐振频率上,称为串联型晶体振荡器。

3.分频器工作原理

分频器采用预置法将两个74HC163先反馈后级联构成,前一级的RCO信号作为后一级的使能信号。时钟信号采用同一输入。分频数通过改变ABCD的高低电平来实现。工作电路图如图1-7。

1-7 分频器电路图

所测频率点为300kHz、500kHz、700kHz,74LS163设置如下:

频率/kHz 片(1)D3D2D1D0 片(2)D3D2D1D0

四、测量结果及分析

实验在面包上搭建电路,共用了1片2.5MHz晶体振荡器、1KΩ电阻两枚、100KΩ和5.1K Ω电阻各一枚、0.1μf、56pf、0.1nf电容各一枚、4片74HC163、2片74HC04、1片CD4046,搭建的时候完成一个模块测试一个模块。

调试电路设备有双路直流稳压电源、数字频率计、数字示波器、万用表、

低频信号发生器。调试采用分步逐级调试。

1.晶体振荡器输出频率的测量:将晶体振荡器输出的信号接入多功能计

数器接头上,测量晶体产生的频率。稳定在2.5MHz。

2.1/M分频器输出频率的测量:测量74ls163高位片15脚输出频率。

稳定在25KHz。

3.输出频率

f测量:测量CD4046第4管脚输出频率,应稳定在300、500、

700KHz。

4.峰值时间tm和频率转换时间tc的特征参数:N分频器低位片3管脚接50Hz占

空比为50%的方波和双踪示波器1路接,示波器2路测量CD4046第9管脚输出波形,

测量tc和tm。

实验结果:

f输出稳定,结果见下表

参考测量分析

(1)VCO 的压控灵敏度

K 与线性度η。

前已指出,VCO 的压控灵敏度是单位电压控制下,VCO 输出角频率的变化量,记作

0K ()

/rad s v ?,定义为

()()

0max min max min C C K U U ωω=--

理想的压控灵敏度

K 应是不变的,但实际中的

K 是变化的,这样压控特性是非线性的,通

常用线性度η参量来描述线性度,η越接近1越好,η的定义为

0max 0min K K η=

(2)c t

的测量与计算

分频比N 改变时的波形

测量结果为1.6ms ,符合设计要求

五、 总体电路图(附图1) 六、 实验心得

这次试验中,我自己完成了整个程序设计的框架,从最开始的画电路图, 到后来的布线,调试,改进的一系列操作中,收获了很多。开始时布线随意,没有考虑到可能造成的干扰,以至后来的改进十分费力,付出了较多的时间。

实验过程中的重点应该是调试,比如说分频器的测试,4046功能的测试,

如果不按照步骤测试,排出问题基本不可能。

通过这次实验,我对锁相环的工作原理有了进一步的认识。基本掌握了锁相环及频率合成器的设计方法,在实验中,发现自己对图表的理解能力还是有些欠缺,自己的动手操作能力也有待提高,需要进一步加强。

实验中遇到了很多困难,比如连线时,正负极短接,导致电源短路,对实验测量有一定的影响;测频率时频率计上的示数一直在跳动,最后在频率计地线上接上1K电阻有效解决了问题。在最后调试过程中,tc一直过大,使得原来计算的参数都没有用,需要重新计算,外接电容,更换电阻等情况进行修改。这都使得自己的计算动手能力有了很大的提高。

感谢老师们这几天下午的指导,老师您辛苦了。

2014年3月17日参考书目

[1]李晋炬.通信电路与系统实验教程[M].北京:北京理工大学出版社,2006.09

、

附实验电图