高速数据采集系统

目录

1高速数据采集系统简介 2

2几种常用的数据采集系统方案简介与分析比较 3

2.1基于ARM的高速数据采集系统 3

2.2基于MCU+FPGA组合的高速数据采集系统 6

2.3基于USB2.0芯片CY7C68013以及模数转换芯片MAX1195的高速数据采集系统 10

2.4几种高速数据采集系统的比较 12

3自行设计的基于单片机的高速数据采集系统 13

3.1设计原理 13

3.2 AD转换模块设计 14

3.3 DA输出模块设计 16

3.4 LCD显示模块设计 18

3.5 总的电路图 18

4程序设计 19

5心得体会 25

6参考文献 26

1高速数据采集系统简介

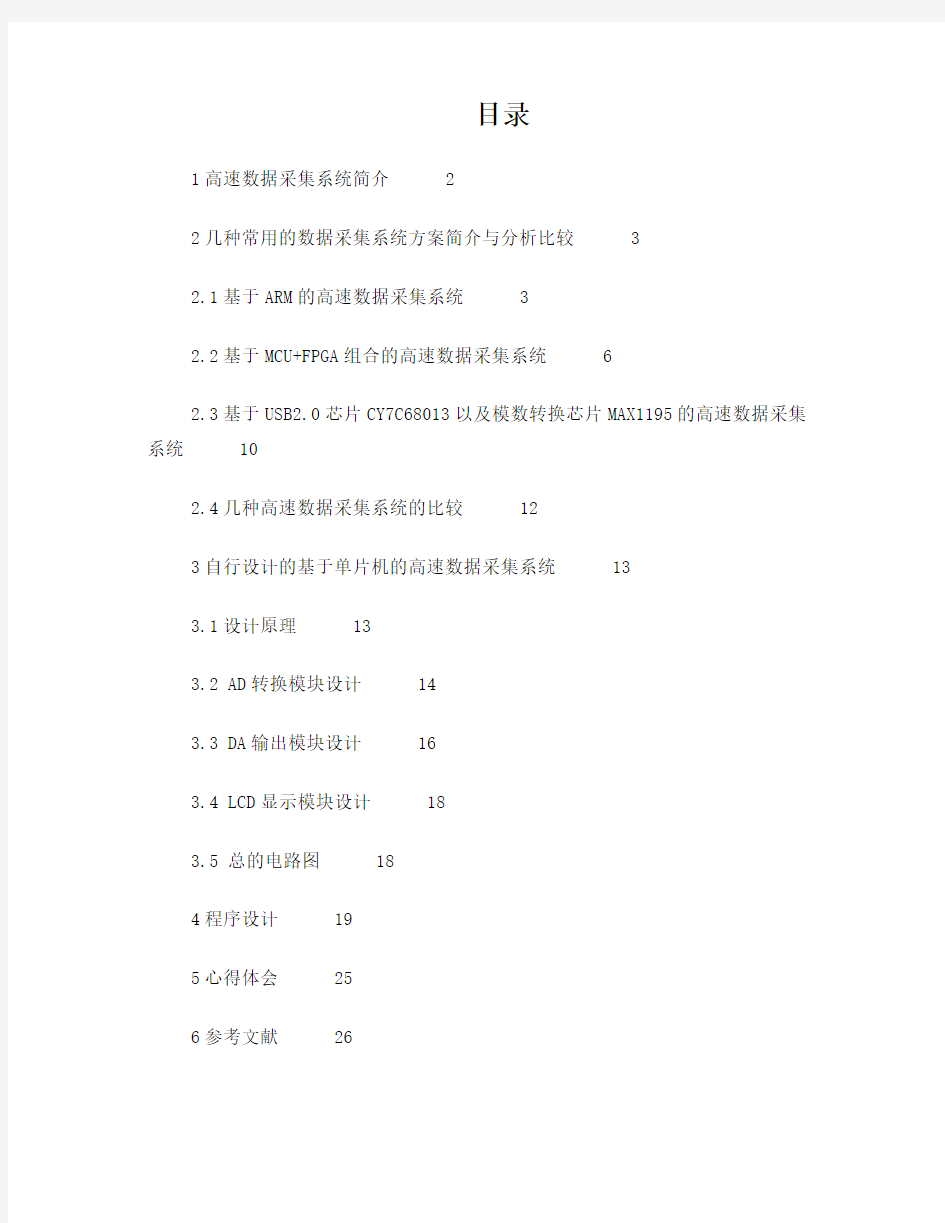

通用的数据采集系统有硬件和软件两部分组成。硬件部分主要完成数据采集,存储等功能,软件部分则完成对硬件控制、对采集数据进行处理等功能。与传统的中、低速数据采集系统相比,高速高精度数据采集系统有其特殊性。首先,对于采样率高到一定程度的系统,很难用软件和常规的微机接口对其采样、转换过程进行控制。在这种情况下,通常用硬件实现转换过程的控制和采样数据的同步;其次,如果系统的实时性要求高,必须采用高速缓存对数据进行存储和高速DS芯片完成数字信号的实时处理。高速高精度数据采集系统的主要任务是将外界模拟信号进行采集转换,然后送往计算机根据相关要求进行数据处理,其结构主要由信号调理、采样保持、模数转换和微机系统等部分组成,系统的结构框图如图1.1所示。

图1.1 高速高精度数据采集系统框图

其中数据采集系统前置电路一般包括传感器、放大器和滤波器等,传感器把外界信号转变成模拟电量(如热电偶传感器、流量传感器、速度传感器等等),其转换后的信号一般比较微弱,需要进行放大处理,在传感器转换信号和放大器工作时,常常产生噪声信号影响采集的准确性,这就需要滤波器降低各种噪声信号提高系统的信噪比。数据采集系统中常常需要对多组模拟量进行采集,在模拟量信号变化周期不快的情况下就可以选用模拟多路开关,这样模数转换电路就可以只选取一套从而降低系统的开发成本。其中模数转换器是数据采集系统中的核心部分,其性能决定了数据采集系统所能实现的功能。

2几种常用的数据采集系统方案简介与分析比较

2.1基于ARM的高速数据采集系统

该系统的控制核心Samsun公司推出的16/32位RISC处理器S3C44B0X。它为手持设备和一般类型应用提供了高性价比和高性能的微控制器解决方案。为了降低成本,S3C44B0X提供了丰富的内置部件:8KB Cache,可选的内部SRAM,LCD控制器,带自动握手的2通道UART,4通道DMA,系统管理器(片选FP/EDO/SDRAM控制器),带PWM功能的5通道定时器,I/O端口,RTC,8通道10为ADC,IIC总线接口,IIS总线接口,同步SIO接口和PLL倍频器。S3C44B0X采ARM7TDMI内核,0.25um工艺的CMOS标准宏单元和存储编译器。它低功耗,精简,出色和全静态的设计特别适用于成本和功耗敏感的应用。同样S3C44B0X还采用了一种新的总线结构,即SAMBAII(SAMSUNG ARM CPU 嵌入式微处理器总线结构)。S3C44B0X的显著特性时它的CPU核,是由ARM公司设计的16或32位的ARM7TDMI最高为66MHz的RISC处理器。微处理器S3C44B0X提供全面的,通用的片上外设,大大减少了系统电路中除处理器以外的元器件配置,从而最小化系统的成本。

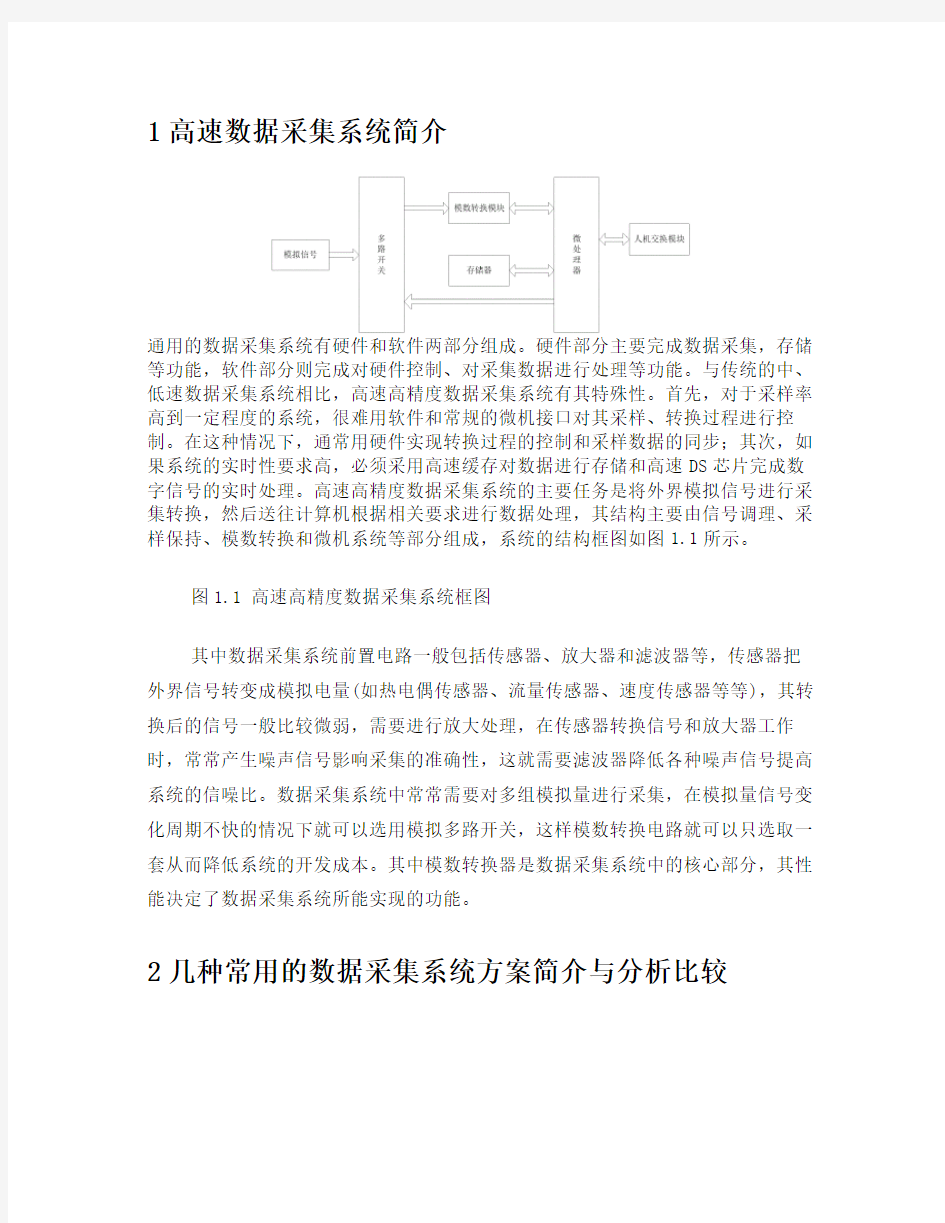

系统以S3C44B0X为数据采集模块核心处理器,采用模块化方法设计,按照功能的不同,分为电源电路、通道选择电路、模数转换电路、通信电路、多路开关及信号调理电路、计算机人机交互界面部分,数据采集系统整体结构图2.1所示。

2.1 高速高精度数据采集系统的电路框图

数据采集系统工作流程:传感器输入的模拟信号经过信号调理电路的处理(包括隔离、变换、放大、滤波等各种处理)以满足数模转换芯片对输入电平和信号质量的要求,然后通过多路开关进行信号选择,选通的信号由高性能高速电压反馈放大器AD8021的进一步的处理获得更精确,精度更高的模拟信号,在微处理器

的控制下模拟信号通过16位逐次渐近型模数转换器AD7663的转换处理存入数据缓存,进一步通过S3C44B0X处理器的控制的显示、键盘模块实现人机交换功能。同时多路开关的选择与控制有微处理器控制。

软件部分的设计分为两个部分,分别为数据采集系统控制软件和数据程序处理两个部分。软件设计共包括五部分:通道选择,数据采集处理,数据存储,数据显示和键盘控制。

系统各模块功能概述:

(1) 多路开关及信号调理模块

模拟多路开关是数据采集系统的一个重要部分,通常在多路被测信号共用一路A/D转换器的采集系统中用来把多路信号有条理的传送到A/D转换器中去,以完成多路信号的数据采集。这里介绍的是采用8通道模拟多路复用器MAX308EPE实现8路模拟信号的采集。信号调理电路主要基于AD623与MAX291芯片的自行设计电路。信号调理电路主要用来对传感器输入的信号进行隔离、变换、放大、滤波等等各种处理,以满足模数转换芯片对输入电平和信号质量的要求,同时大大的简化了信号调理电路的设计,简化了外围电路。多开关由微处理器S3C44B0X进行控制选择。

(2) 模数转换模块

本模块由两部分组成:信号驱动放大器AD8021与具有低噪声、高精度和出色的长期稳定特性的基准电压源ADR421提供基准电压的模数转换芯片AD7663。

传感器输入的信号通过多路开关及信号调理模块处理后得到比较符合要求的模拟信号,进一步通过信号驱动放大电路AD8021的处理得到精度较高的、稳定的模拟信号,通过分辨率高,采样速率高,功耗小的模数转换芯片AD7663的作用,输出符合要求的数字信号,完成模数转换。

(3) 存储模块

传统的数据采集系统由于数据传输率较低,数据量小,一般可以完成实时分析和处理,所以存储问题不突出。但高数高精度数据采集系统的数据传输率很高并且数据量很大,采集速度达到一定的限度就无法进行实时分析和处理,所以合适的存储器显得很有必要。本设计采用的是SST39VF160芯片。它具有成本低和密度大的优点,能很好的完成本系统的存储要求,把通过内部AD7663模块转换成数字量,经通信端口送入计算机进行下一步处理。

(4) 键盘模块

键盘扫描过程就是有规律的时间间隔查看键盘矩阵,以确定是否有键被按下。一旦处理器判定有一个键被按下,键盘扫描程序就会滤掉抖动,然后再判定是哪个键被按下。每个键被分配一个称为扫描码的唯一标示符,应用程序利用该扫描码来判断应按下了什么键。本设计就是采用的是4×4矩阵键盘,完成人机交换的键盘控制。

(5) 显示模块

S3C44B0X内部有一个LCD控制器,只需要在外部接一个液晶驱动模块就可以具有显示功能了。本设计设置了LCD液晶显示驱动模块与S3C44B0X的连接模式,包括接口方式,寄存器的编程。本模块达到了微处理器与显示器的数据传输,实现了显示的功能。

2.2基于MCU+FPGA组合的高速数据采集系统

高速数据采集系统的硬件核心为FPGA控制器,其主要功能为响应计算机通过PCI总线或者USB总线发出的控制命令,接收ADC的实时数据存储在DDRII芯片阵列中,在存储完成后自动将数据通过PCI总线或者USB总线传输到计算机存储到硬盘中。这些功能的实现都是使用Verilog HDL语言编程实现的。Verilog HDL语言

是一种用形式化方法来描述数字电路和系统的硬件语言。利用其进行电路设计,大大提高了逻辑电路的设计效率,缩短了逻辑电路的设计周期。

采用FPGA+MCU的结构,主控逻辑模块用FPGA来实现,在系统中对A/D器件进行采样控制,起到连接采样电路和MCU的桥梁作用,数据处理、远程通信及液晶显示控制等由MCU来完成。FPGA把传统的纯粹以单片机软件操作形式的数据采集变成硬件采集。首先用VHDL语言来设计状态机,用MCU来启动状态机,使其控制A/D器件,实现数据采集。并将采集到的数据存储到FPGA内部的数据缓存区FIFO 中。当FIFO存储已满时,状态机控制FIFO停止数据写入,并通知单片机取走采集数据进行下一步处理。这种设计思想大大减轻了单片机的软件运行时间,提高了采集速率。这里,把6路模拟信号采集任务作为快任务,把用于系统自检的6路检测量信号作为慢任务。为了使快任务的优先级高于慢任务,本系统设计两个状态机分别实现快任务和慢任务的数据采集,并由单片机生成PWM波,分别控制两个状态机。系统的总体框图如下图所示:

FPGA高速数据系统总框图

1)系统主要器件选择

①FPGA芯片选取及依据:

FPGA实现主控逻辑控制,要求响应速度快,效率高。可采用ALTERA公司的ACEX1K 系

列EP1K5O芯片,最高工作频率可达250 MHz。该系列芯片的特点是将LUT(查找表)EAB(嵌入式阵列)相结合,提供了效率最高而又廉价的结构。基于LUT的逻辑对数据路径管理、寄存器强度、数学计算或数字信号处理的设计提供优化的性能和效率,而EBA可实现RAM (随机读写存储器)、ROM(只读存储器)、双口RAM 或FIFO (先入先出存储器)功能,使得ACEX1K适合复杂逻辑以及有存储、缓冲功能的数据采集系统。

②ADC芯片选型及依据

数据采集系统的输入信号多数都来源于现场传感器的输出信号,传感器种类不一,致使信号特性也不同,各通道信号的幅度与频率范围有很大的不同,高精度的、大动态范围的A/D转换芯片使设计更能满足测量的需要。

2)FPGA 方案设计

①设计思想

用VHDL语言来设计两个状态机,状态机1来控制A/D实现快任务的采集,状态机2来完成慢任务采集。两个状态机的时钟信号CLK(高电平有效)均来自单片机生成的PWM波,状态机1直接由单片机控制,状态机2则是由单片机经反向器来控制。首先置P1.0口为高电平,并用定时器来产生中断,使P1.0口产生PWM波。当P1.0口为高电平时启动状态机1,此时状态机2不动作;当快任务采样完成后,由定时器产生中断,将P1.0口置为低电平,此时状态机2动作,来完成慢任务采集。下一个周期完成同样的操作。对应快任务的采集数据缓存在快任务FIFO,慢任务的采集数据缓存在慢任务FIFO里,单片机读对应的FIFO数据来进行相应处理。

②各模块的设计

根据以上的设计思想,FPGA系统的硬件设计模块主要有状态机模块,FIFO设计模块[4-5]。下面具体给出硬件原理设计。

A)状态机的设计

该设计过程主要是建立采集所需要的硬件电路,等待时钟信号的到来便立刻启动A/D进行工作。了解了AD574A的工作时序,就可以写出状态机的采样控制状态。控制状态编码下表所示:

表 1 控制状态编码表

用VHDL语言来实现状态机,其原程序:

SIGNAL current_state,next_state:STD_LOGIL_VECTOR(4 DOWNTO 0);

CONSTANT st0:STD_LOGIL_VECTOR(4 DOWNTO 0):=”01000”;

CONSTANT st1:STD_LOGIL_VECTOR(4 DOWNTO 0):=”10000”;

CONSTANT st2:STD_LOGIL_VECTOR(4 DOWNTO 0):=”01001”;

CONSTANT st3:STD_LOGIL_VECTOR(4 DOWNTO 0):=”01100”;

CONSTANT st4:STD_LOGIL_VECTOR(4 DOWNTO 0):=”01110”;

SIGNAL LOCK :STD_LOGIL;

COM:PROCESS(current_state,STS)

BEGIN

CASE current_state IS

WHEN st0=> next_state<= st1;

WHEN st1=> next_state<= st2;

WHEN st2=> IF(STS=‘0’) THEN next_state<=st3; ELSE next_state<=st2;

END IF;

WHEN st3=> next_state<= st4;

WHEN st4=> next_state<= st0;

WHEN OTHERS=>next_state<=st0;

END CASE;

END PROCESS COM;

REG:PROCESS(CLK)

BEGIN

IF(CLK=‘1’)THEN current_state<=next_state; END IF;

END PROCESS REG;

B)FIFO 模块设计

利用FPGA中的EAB/ESB等嵌入式模块构成的LPM宏功能模块来生成

LPM_FIFO。其编辑定制方法[3]:

(1)进入QuartusⅡ,选择菜单 File—> TOOL—〉Megawizard Plug-In Manager,选择Create a new custommegafunction variation,选择FIFO。

(2)选择FIFO数据位宽度为12,深度为512。

(3)选择FIFO的端口:12位数据输入输出端口data[12..0]和q[12..0];对clock同步的数据写入和读出请求wrreq和rdreq;异步清零aclr;存储数据溢出信号full。

2.3基于USB2.0芯片CY7C68013以及模数转换芯片MAX1195的高速数据采集系统2.

3.1CY7C68013芯片和MAX1195芯片介绍

1) CY7C68013介绍:

CY7C68013在一块芯片上同时集成了USB2.0收发器,串行接口引擎SIE,增强型的8051微控制器以及一个可编程外围接口GPIF(General Programmable Interface)。CY7C68013的“量子FIFO”(FIFO,先进先出存储器)特性使得无需8051CPU的任何干预,数据即可从外设上传到主机,这种数据传输模式彻底解决了USB2.0收发器与一般8051微控制器连接时由于8051的时钟频率低而导致的传输速率瓶颈问题。CY7C68013芯片的另一个突出优点是其“‘软’配置”,代码和数据能够直接通过USB接口下载到片内的RAM上,这一功能通过Cypress公司独创的“重枚举”(ReNumerationTM)功能实现。CY7C68013芯片有四个可编程的批量、中断、同步传输端点,可以分别设置为双缓冲,三缓冲和四缓冲模式,8位或者16位的外部数据接口,该接口可以根据需要工作在 GPIF或者SLAVEFIFO模式。其中GPIF能够和绝大部分并行接口如FIFO等实现“无胶”连接,即无需外加任何微控制器或CPLD、FPGA 等。本文的设计中采用了GPIF方式。

2)MAX1195介绍:

MAX1195是由MAXIM公司推出的一款低功耗、双路、高速、八位模数转换芯片,采用流水线(Pipeline)结构,最高采样率40Mbps,内部集成了两个 ADC,真正实现两路同步采样转换。其工作电压范围是2.7V-3.6V,具有减小功耗的休眠模式和关断(Shut-Down)模式,单端或者差分输入方式,片上采样保持(T/H)电路,内部或者外部参考电压,含有用户可选择的数据输出格式:二的补码格式或者补偿二进制码格式,具有输出使能控制,可以将输出置为高阻态。此外MAXIM还提供了与MAX1195引脚、封装完全兼容的10位、更高采样率的模数转换芯片,如MAX1197、MAX1198等,因此系统升级非常方便。在本文的工作中,采用了内部参考电压、双路单端模拟输入、补偿二进制码输出格式。

2.3.2系统整体构成及其工作原理介绍:

1)系统构成:

系统的整体框图如图1所示。整个系统主要包括USB传输芯片CY7C68013,先进先出存储器(FIFO)SN74V235和模数转换芯片MAX1195组成。反相器74LVC04主要起MAX1195和FIFO之间的逻辑控制作用。

图2.3.2系统整体框图

2)系统工作原理:

MAX1195的两路输入信号是同时被采样的,十六位的数据输出总线使两路数据可以同时输出,分别占八位,即:D0A~D7A和D0B~D7B;SN74V235输入为18位,根据CMOS技术的要求,将未使用的D16和D17引脚接地。MAX1195采集到的数据首先送进FIFO里, FIFO的写时钟(WCLK)和AD的转换时钟反相,这样可以充分满足MAX1195输出数据的建立时间,避免发生数据丢失或者数据重复写入现象。SN74V235的 (Programmable Almost Full)可编程几乎满信号经74LVC04反相后接MAX1195的Sleep和引脚,以免FIFO发生溢出而丢失数据。SN74V235的数据输出引脚Q0~Q15与CY7C68013的GPIF模式下的数据线FD[15:0]即端口B和端口D组成的十六位数据总线相连,数据SN74V235到EZ-USB FX2的时序过程由CY7C68013的GPIF 控制。FX2采用了“量子FIFO”结构,在FX2里面,数据可以分为两个域:USB域和GPIF接口域。这两个域是独立的,允许分别使用不同的时钟和逻辑控制数据的传输,USB域是由SIE控制的,SIE通过USB口接收或者发送端点FIFO 的数据。FX2的“量子FIFO”能够几乎不花时间在这两个数据域中的转移数据,因为这两个域用的FIFO在物理上是同一个。所以根据“量子FIFO”原理,实际上数据已经存在于属于USB域的端点FIFO里面了,采用USB的BULK传输方式,使该数据完全不经过低频CPU干预,而是采用FX2提供的AutoIn模式,即一旦FX2端点缓冲区的数据达到指定字节数,数据将自动被打包从USB口上传到主机。

2.4几种高速数据采集系统的比较

1)基于ARM的高速数字采集系统:

其主要特点如下:

(1) 实时性强。系统的主要工作是对大量的过程状态参数实时监测、数据存储、数据处理、进行实时数据分析等。因此要求硬件上必须要有实时时钟和优先级中断信息处理电路。

(2) 可靠性高。他是系统设计的一个重要要求。由于数据采集系统往往是安放在被控对象的工作环境中,所以不仅温度、湿度大,而且腐蚀多,干扰也很多,为了确保系统的可靠性,要求系统有较好的抗干扰能力和采集速度。

(3) 通用性好,便于扩充。一台以嵌入式系统为核心的控制装置,一般可以控制多个设备和过程参数,这就要求系统的通用性要好,能灵活的进行功能扩充。

(4) 结构简单,功耗低,性能优良。

2)基于MCU+FPGA组合的高速数据采集系统:

随着数据采集对速度性能的要求越来越来高,传统的采集系统的弊端越来越明显,现在多采用FPGA或者FPGA+MCU(主控逻辑模块是FPGA)的结构,各模块设计使用VHDL 语言,其各进程间是并行的关系。它有MCU 无法比拟的优点。FPGA 的时钟频率高,全部控制逻辑由硬件完成,实现了硬件采样,速度快。

利用VHDL语言对FPGA进行设计,可在QuartusⅡ中进行系统仿真和验证。由FPGA在线编程的特点,可以依据现场的具体情况,对FPGA的内部配置进行修改,进一步增加了系统应用的灵活性,因此该系统是一种比较理想的实时高速数据采集方案。

3) 基于USB2.0芯片CY7C68013以及模数转换芯片MAX1195的高速数据采集系统

在这种高速同步数据采集系统的设计中,CY7C68013芯片灵活的接口和可编程特性简化了外部硬件的设计,提高了系统的可靠性,也利于PCB板的制作与调试。CY7C68013的GPIF引擎具有自动传输数据结构的特性,这种特性使得外围设备和主机通过CY7C68013可以无缝的、高速的传输数据。为了实现高速的数据传输,CY7C68013CPU不会直接参与数据的传输,而是直接利用GPIF的自动传

输数据模式。另外,USB设备的可热插拔特性使得该系统具有便携式的特点,使用方便,无需关机重启或打开机箱进行安装。

3自行设计的基于单片机的高速数据采集系统

3.1设计原理

我设计的高速数据采集系统包括以下几个模块:AD转换模块、LCD显示模块、DA输出模块、CPU控制模块。之所以用到DA输出模块,是因为我想让采集到的数据实时的输出。

原理框图

开始是AD模块采集到电压信号,然后经过转换之后将模拟电信号变成数字量并且送到CPU。CPU将数字量处理之后分别送到LCD显示模块和DA输出模块。其中由于我使用的AD和DA的芯片处理的数据位数不同,AD芯片是八位数据而DA芯片是10为数据,所以必须将AD转换后的数据转换成DA芯片能够处理的10位数据格式。

3.2 AD转换模块设计

模拟量输入需要AD转换,本设计使用的是八位精度的串行AD转换芯片

TLC549。

3.2.1 TLC549芯片简介

TLC549是美国德州仪器公司生产的8位串行A/D转换器芯片,可与通用微处理器、控制器通过CLK、CS、DATA OUT三条口线进行串行接口。具有4MHz片内系统时钟和软、硬件控制电路,转换时间最长17μs, TLC549为40 000次/s。总失调误差最大为±0.5LSB,典型功耗值为6mW。采用差分参考电压高阻输入,抗干扰,可按比例量程校准转换范围,VREF-接地,VREF+-VREF-≥1V,可用于较小信号的采样。

TLC549芯片引脚图如下:

3.2.2 AD转换模块电路图

AD转换模块电路图

3.3 DA输出模块设计

数字量转模拟量需要用到DA芯片。本设计采用的是十位精度的串行DA转换芯片TLC5615。

3.3.1 TLC5615简介

TLC5615 为美国德州仪器公司 1999 年推出的产品,是具有串行接口的数模转换器,其输出为电压型,最大输出电压是基准电压值的两倍。带有上电复位功能,即把 DAC 寄存器复位至全零。性能比早期电流型输出的 DAC 要好。只需要通过 3 根串行总线就可以完成 10 位数据的串行输入,易于和工业标准的微处理器或微控制器(单片机) 接口, 适用于电池供电的测试仪表、移动电话,也适用于数字失调与增益调整以及工业控制场合。

TLC5615主要由以下几部分组成:

1、 10 位 DAC 电路;

2、一个 16 位移位寄存器, 接受串行移入的二进制数,并且有一个级联的数据输出端DOUT ;

3、并行输入输出的 10 位 DAC 寄存器, 为 10 位 DAC 电路提供待转换的二进制数据;

4、电压跟随器为参考电压端REFIN提供很高的输入阻抗,大约10MΩ;

5、×2 电路提供最大值为 2 倍于 REFIN 的输出;

6、上电复位电路和控制电路。

两种工作方式:(A)16 位移位寄存器分为高 4 位虚拟位、低两位填充位以及 10位有效位。在单片 TLC5615 工作时,只需要向 16 位移位寄存器按先后输入 10位有效位和低 2 位填充位,2 位填充位数据任意,这是第一种方式,即 12 位数据序列。(B)第二种方式为级联方式, 即 16 位数据列,可以将本片的 DOU T 接到下一片的 DIN , 需要向 16 位移位寄存器按先后输入高 4 位虚拟位、10 位有效位和低 2 位填充位, 由于增加了高 4 位虚拟位, 所以需要 16 个时钟脉冲。

TLC5615芯片引脚图如下:

3.3.2 DA输出模块电路图

DA输出模块电路图3.4 LCD显示模块设计

LCD显示模块电路图

3.5 总的电路图

4程序设计

#include

#include

#define uint unsigned int

#define uchar unsigned char

#define LCD_DB P0

sbit LCD_RS=P1^0;

sbit LCD_RW=P1^1;

sbit LCD_E=P1^2;

sbit cs_AD=P3^7;

sbit sclk_AD=P3^6;

sbit din_AD= P3^5;

sbit CLK_DA=P1^7;

sbit DAT_DA=P1^6;

sbit CS_DA=P1^5;

uint y;

uchar x;

uchar LCD[6];

void LCD_init(void);//初始化函数

void LCD_write_command(uchar command);//写指令函数void LCD_write_data(uchar dat);//写数据函数

void write_5615(uint da);//DA转换

uchar TLC549ADC(void);//AD转换

void delay_n40us(uint n);//延时函数

void Volt_To_LCD(void);

//********************************

//*******初始化函数***************

导航系统及导航方法与设计方案

本技术适于导航领域,提供一种导航系统及导航方法,包括:导航硬件,用于将采集到得导航数据发送给MCU;MCU,用于将导航硬件发送的导航数据读取、并且暂存,当车载电 脑启动完毕时,将导航数据发送给车载电脑;车载电脑,用于接收MCU发送的导航数据,并且完成导航数据的导航应用。通过在导航系统中加入MCU,在系统上电后,MCU瞬间启动,且MCU读取和缓存导航数据,实现导航系统启动即读取导航数据。并且MCU连接的是车载电脑的CPU,将导航数据直接发送到操作系统的硬件抽象层,实现了读取导航数据不与操作系统内核空间打交道,仅从用户空间即可获取导航数据,扩展了应用。 技术要求 1.一种导航系统,其特征在于,包括: 导航硬件, 用于将采集到的导航数据发送给MCU; MCU,用于将导航硬件发送的导航数据读取、并且暂存,当车载电脑启动完毕时,将导航数据发送给车载电脑; 车载电脑,用于接收MCU发送的导航数据,并且完成导航数据的导航应用;MCU将导航数据传递给车载电脑操作系统的硬件抽象层,硬件抽象层将导航数据上报给框架层,框 架层将导航数据上报给应用层,在应用层完成导航数据的导航应用; 所述车载电脑安装的是Android操作系统; 所述导航硬件与所述MCU之间的数据通讯采用串行通信方式; 所述MCU与所述车载电脑的CPU之间数据通讯采用串行通信方式;

所述车载电脑的存储器采用的是阵列硬盘存储。 2.一种导航方法,其特征在于,该导航方法包括以下步骤: A、导航硬件采集导航数据,并且将采集到的导航数据发送给MCU; B、MCU读取导航数据、且暂存导航数据,并且MCU将导航硬件发送的导航数据发送给车载电脑操作系统的硬件抽象层; C、车载电脑操作系统的硬件抽象层将导航数据上报给车载电脑操作系统的框架层,车载电脑操作系统的框架层将导航数据上报给车载电脑操作系统的应用层; D、在车载电脑操作系统的应用层将导航数据完成导航应用; 所述步骤A包括以下步骤: A1、导航硬件采集导航数据; A2、如果导航硬件采集到导航数据,则执行步骤A3,如果导航硬件没有采集到导航数据,则重复执行步骤A1; A3、导航硬件将采集的导航数据发送给MCU。 3.根据权利要求2所述的导航方法,其特征在于,所述步骤B还包括以下步骤: B1、MCU读取导航数据、且暂存导航数据; B2、如果车载电脑操作系统启动完毕,则执行步骤B3,如果车载电脑操作系统未启动完毕,则等待车载电脑操作系统启动完毕; B3、MCU将导航数据发送给车载电脑操作系统的硬件抽象层。 4.根据权利要求2或3所述的导航方法,其特征在于,所述车载电脑操作系统运行的是Android系统。 技术说明书

高速数据采集系统设计

高速数据采集系统 设计

基于FPGA和SoC单片机的 高速数据采集系统设计 一.选题背景及意义 随着信息技术的飞速发展,各种数据的实时采集和处理在现代工业控制和科学研究中已成为必不可少的部分。高速数据采集系统在自动测试、生产控制、通信、信号处理等领域占有极其重要的地位。随着SoC单片机的快速发展,现在已经能够将采集多路模拟信号的A/D转换子系统和CPU核集成在一片芯片上,使整个数据采集系统几乎能够单芯片实现,从而使数据采集系统体积小,性价比高。FPGA为实现高速数据采集提供了一种理想的实现途径。利用FPGA高速性能和本身集成的几万个逻辑门和嵌入式存储器块,把数据采集系统中的数据缓存和控制电路全部集成在一片FPGA芯片中,大大减小了系统体积,提高了灵活性。FPGA 还具有系统编程功能以及功能强大的EDA软件支持,使得系统具有升级容易、开发周期短等优点。 二.设计要求 设计一高速数据采集系统,系统框图如图1-1所示。输入模拟信号为频率200KHz、Vpp=0.5V的正弦信号。采样频率设定为25MHz。经过按键启动一次数据采集,每次连续采集128点数据,单片机读取128点数据后在LCD模块上回放显示信号波形。

图1-1 高速数据采集原理框图 三.整体方案设计 高速数据采集系统采用如图3-1的设计方案。高速数据采集系统由单片机最小系统、FPGA最小系统和模拟量输入通道三部分组成。输入正弦信号经过调理电路后送高速A/D转换器,高速A/D 转换器以25MHz的频率采样模拟信号,输出的数字量依次存入FPGA内部的FIFO存储器中,并将128字节数据在LCD模块回放显示。 图3-1 高速数据采集系统设计方案 四.硬件电路设计 1.模拟量输入通道的设计 模拟量输入通道由高速A/D转换器和信号调理电路组成。信号调理电路将模拟信号放大、滤波、直流电平位移,以满足A/D转换器对模拟输入信号的要求。

多路数据采集器设计报告

多路数据采集器设计 1.设计要求 所设计的数据采集器,共有16路信号输入,每路信号都是直流0~20mV信号,每秒钟采集一遍,将其数据传给上位PC计算机。本采集器地址为50H。要求多路模拟开关用4067,A/D转换用ADC0809,运算放大器用OP07,单片机用89C51,通信用RS232接口,通信芯片用MAX232。 与PC机的RS232串口进行通信。 设计采集器的电原理图,用C51语言编制采集器的工作程序。 2.方案设计 按要求,设计数据采集器方案如下所示: 数据采集器采用AT89C51单片机作为微控制器,模拟开关4067的地址A、B、C、D分别与P1.0~P1.3连接,通过控制P1口输出来选择输入信号,将直流信号依次输入ADC0809的模拟信号输入端,ADC0809共有8路输入通道,在使用模拟开关时,仅将模拟开关的输出端连接到ADC0809的1路输入通道即可,本方案中使用0通道。ADC0809的转换结果通过P0口传给单片机,单片机将采集结果通过串行通信RS232接口上传给上位PC机,实现数据的采集。 数据采集器方案示意图

3.电路原理图 a)AT89C51单片机电路 本实验中选取8位单片机AT89C51作为微控制器,需要片外11.0592MHz的振荡器,4K字节EPROM,128字节RAM,与51单片机有很好的兼容性。在本此实验中程序及数据不多,故无需另加外部程序存储器。单片机部分的电路如下所示: AT89C51单片机电路 b)数据输入部分

数据输入部分由模拟开关4067实现多路信号的切换。CD4067是单16路(单刀16位)模拟开关,各开关由外部输入二进制的地址码A、B、C、D来切换。其中脚10、11、14和13是地址码A(LSB)、B、C、D(MSB)的输入端;脚2~9和16~23是开关的输入/输出端(开关位);脚1是开关的输出/输入公共端(开关刀);脚15为控制端,低电平有效(选通),高电平禁止(开关开路)。 输入脚A、B、C、D分别与单片机P1.0~P1.3相连,改变P1输出即可切换输入通道,控制脚与P2.4相连。输出脚1后接电压放大电路。 c)电压调理放大电路 电压调理电路 由于输入信号均为0~20mV的微弱电压信号,而模数转换器ADC0809的输入量要求为0~5V 直流电压,所以必须后接电压放大电路。放大器选用OP07,将0~20mV电压放大到0~5V,其放大倍数为250倍,一般情况下,放大器的放大倍数最好小于200倍,安全起见,选用两个OP07进行两级放大,前级放大25倍,后级放大10倍,放大电路如上图所示。 d)模数转换部分 ADC0809数模转换电路 模数转换元件选用ADC0809,其主要特性有: 8路8位A/D转换器,即分辨率8位;

激光雷达高速数据采集系统解决方案

激光雷达高速数据采集系统解决方案 0、引言 1、 当雷达探测到目标后, 可从回波中提取有关信息,如实现对目标的距离和空间角度定位,并由其距离和角度随时间变化的规律中得到目标位置的变化率,由此对目标实现跟踪; 雷达的测量如果能在一维或多维上有足够的分辨力, 则可得到目标尺寸和形状的信息; 采用不同的极化方法,可测量目标形状的对称性。雷达还可测定目标的表面粗糙度及介电特性等。接下来坤驰科技将为您具体介绍一下激光雷达在数据采集方面的研究。 1、雷达原理 目标标记: 目标在空间、陆地或海面上的位置, 可以用多种坐标系来表示。在雷达应用中, 测定目标坐标常采用极(球)坐标系统, 如图1.1所示。图中, 空间任一目标P所在位置可用下列三个坐标确定: 1、目标的斜距R; 2、方位角α;仰角β。 如需要知道目标的高度和水平距离, 那么利用圆柱坐标系统就比较方便。在这种系统中, 目标的位置由以下三个坐标来确定: 水平距离D,方位角α,高度H。 图1.1 用极(球)坐标系统表示目标位置

系统原理: 由雷达发射机产生的电磁能, 经收发开关后传输给天线, 再由天线将此电磁能定向辐射于大气中。电磁能在大气中以光速传播, 如果目标恰好位于定向天线的波束内, 则它将要截取一部分电磁能。目标将被截取的电磁能向各方向散射, 其中部分散射的能量朝向雷达接收方向。雷达天线搜集到这部分散射的电磁波后, 就经传输线和收发开关馈给接收机。接收机将这微弱信号放大并经信号处理后即可获取所需信息, 并将结果送至终端显示。 图1.2 雷达系统原理图 测量方法 1).目标斜距的测量 雷达工作时, 发射机经天线向空间发射一串重复周期一定的高频脉冲。如果在电磁波传播的途径上有目标存在, 那么雷达就可以接收到由目标反射回来的回波。由于回波信号往返于雷达与目标之间, 它将滞后于发射脉冲一个时间tr, 如图1.3所示。 我们知道电磁波的能量是以光速传播的, 设目标的距离为 R, 则传播的距离等于光速乘上时间间隔, 即2R=ct r 或 2 r ct R

基于单片机的温度数据采集系统实验报告

基于单片机的温度数据采集系统实验报告 班级:电技10—1班 姓名:田波平 学号:1012020108 指导老师:仲老师

题目:基于单片机的温度数据采集系统 一.设计要求 1.被测量温度范围:0~120℃,温度分辨率为0.5℃。 2.被测温度点:2个,每5秒测量一次。 3.显示器要求:通道号2位,温度4位(精度到小数点后一位)。 显示方式为定点显示和轮流显示。 4.键盘要求: (1)定点显示设定;(2)轮流显示设定;(3)其他功能键。 二.设计内容 1.单片机及电源模块设计 单片机可选用AT89S51及其兼容系列,电源模块可以选用7805等稳压组件,本机输入电压范围9-12v。 2.存储器设计 扩展串行I2C存储器AT24C02。 要求: AT24C02的SCK接P3.2 AT24C02的SDA接P3.4 2.传感器及信号转换电路 温度传感器可以选用PTC热敏电阻,信号转换电路将PTC输出阻值转换为0-5V。 3.A/D转换器设计 A/D选用ADC0832。 要求: ADC0832的CS端接P3.5 ADC0832的DI端接P3.6 ADC0832的DO端接P3.7 ADC0832的CLK端接P2.1 4.显示器设计。 6位共阳极LED显示器,段选(a-h)由P0口控制,位选由P2.2-P2.7控制。数码管由2N5401驱动。 5.键盘电路设计。 6个按键,P2.2-P2.7接6个按键,P3.4接公共端,采用动态扫描方式检测键盘。 6.系统软件设计。 系统初始化模块,键盘扫描模块,数据采集模块,标度变换模块、显示模块等。 三.设计报告要求 设计报告应按以下格式书写: (1)封面; (2)设计任务书; (3)目录; (4)正文;

多路数据采集系统设计毕业论文

多路数据采集系统设计毕业论文 第1章绪论 1.1 多路数据采集系统介绍 随着工、农业的发展,多路数据采集势必将得到越来越多的应用,为适应这一趋势,作这方面的研究就显得十分重要。在科学研究中,运用数据采集系统可获得大量的动态信息,也是获取科学数据和生成知识的重要手段之一。总之,不论在哪个应用领域中,数据采集与处理将直接影响工作效率和所取得的经济效益。 此外,计算机的发展对通信起了巨大的推动作用。算机和通信紧密结合构成了灵活多样的通信控制系统,也可以构成强有力的信息处理系统,这样对社会的发展产生了深远的影响。数据通信是计算机广泛应用的必然产物[2]。 数据采集系统,从严格的意义上来说,应该是用计算机控制的多路数据自动检测或巡回检测,并且能够对数据实行存储、处理、分析计算以及从检测的数据中提取可用的信息,供显示、记录、打印或描绘的系统。 数据采集系统一般由数据输入通道,数据存储与管理,数据处理,数据输出及显示这五个部分组成。输入通道要实现对被测对象的检测,采样和信号转换等

工作。数据存储与管理要用存储器把采集到的数据存储起来,建立相应的数据库,并进行管理和调用。数据处理就是从采集到的原始数据中,删除有关干扰噪声,无关信息和必要的信息,提取出反映被测对象特征的重要信息。另外,就是对数据进行统计分析,以便于检索;或者把数据恢复成原来物理量的形式,以可输出的形态在输出设备上输出,例如打印,显示,绘图等。数据输出及显示就是把数据以适当的形式进行输出和显示。 由于RS-232在微机通信接口中广泛采用,技术已相当成熟。在近端与远端通信过程中,采用串行RS-232标准,实现PC机与单片机间的数据传输。在本毕业设计中对多路数据采集系统作了初步的研究。本系统主要解决的是怎样进行数据采集以及怎样进行多路的数据采集,并将数据上传至计算机[2]。 1.2 设计思路 多路数据采集系统采用ADC0809模数转换器作为数据采集单元和AT89C51单片机来对它们进行控制,不仅具有控制方便、简单和灵活性大等优点,而且可以大幅度提高采集数据的灵敏度及指标。通过MAX232电平转换芯片实现单片机与PC 机的异步串行通信,设计中的HD7279实现了键盘控制与LED显示显示功能。本文设计了一种以AT89C51和ADC0809及RS232为核心的多路数据采集系统。 多路数据采集系统就是通过键盘控制选择通路,将采集到的电压模拟两转换成数字量实时的送到单片机里处理从而显示出采集电压和地址值,最终控制执行单片机与PC机的异步串行通信。 连接好硬件后,给ADC0809的三条输入通路通入直流电压。4-F键为功能键,4-E键为复位键,F键为确认键。1-3键为通道选择键,分别采集三个通道的数据值并实时显示出数值和地址值。结合单片机RS232串口功能还实现了与PC机的异

数据采集系统实验报告

学院名称: 电气信息工程学院 专 业: 测控技术与仪器 班 级: 09测控1W 姓 名: 胡建兵 学 号: 09314111 指导教师姓名: 朱 雷 2012 年 11 月 JIANGSU TEACHERS UNIVERSITY OF TECHNOLOGY 数据采集系统实验报告

实验2——A/D采集模块设计 一.实验目的 学习用状态机实现对ADC0809,AD574A等A/D转换器的采样控制。 二.实验原理 图1和图2分别为ADC0809的引脚图,转换时序图和采样控制状态图。时序图中,START为转换启动控制信号,高电平有效;ALE为模拟信号输入选通端口地址锁存信号,上升沿有效;一旦START有效后,状态信号变EOC变为低电平,表示进入状态转换,转换时间约为100us。转换结束后,EOC将变为高电平。此外外部控制可使OE由低电平变为高电平(输出有效),此时,ADC0809的输出数据总线D【7...0】从原来的高阻态变为输出数据有效。由状态图也可以看到,状态st2中需要对ADC0809工作状态信号EOC进行测试,如果为低电平,表示转换没有结束,仍需要停留在st2状态中等待,直到变成高电平后才说明转换结束,在下一时钟脉冲到来时转向状态st3。在状态st3,由状态机向ADC0809发出转换好的8位数据输出允许命令,这一状态周期同时可作为数据输出稳定周期,以便能在下一状态中向锁存器锁入可靠的数据。在状态st4,由状态机向FPGA中的锁存器发出锁存信号(LOCK的上升沿),将ADC0809的输出数据进行锁存。 图2.1 ADC0809工作时序

图2.2 控制ADC0809采样状态图程序如图实例1所示,其结构框图如图3所示。 图2.3 采样状态机结构框图

温度采集实验报告

课程设计任务书 题目基于AD590的温度测控系统设计 系(部) 信息科学与电气工程学院 专业电气工程及其自动化 班级电气092 学生姓名刘玉兴 学号090819210 月日至月日共周 指导教师(签字) 系主任(签字) 年月日

摘要 温度是工业生产和自动控制中最常见的工艺参数之一。过去温度检测系统设计中,大多采用模拟技术进行设计,这样就不可避免地遇到诸如传感器外围电路复杂及抗干扰能力差等问题;而其中任何一环节处理不当,就会造成整个系统性能的下降。随着半导体技术的高速发展,特别是大规模集成电路设计技术的发展, 数字化、微型化、集成化成为了传感器发展的主要方向。 以单片机为核心的控制系统.利用汇编语言程序设计实现整个系统的控制过程。在软件方面,结合ADC0809并行8位A/D转换器的工作时序,给出80C51单片机与ADC0908并行A /D转换器件的接口电路图,提出基于器件工作时序进行汇编程序设计的基本技巧。本系统包括温度传感器,数据传输模块,温度显示模块和温度调节驱动电路,其中温度传感器为数字温度传感器AD590,包括了单总线数据输出电路部分。文中对每个部分功能、实现过程作了详细介绍。 关键词:单片机、汇编语言、ADC0809、温度传感器AD590

Abstract Temperature is the most common one of process parameters in automatic control and industrial production. In the traditional temperature measurement system design, often using simulation technology to design, and this will inevitably encounter error compensation, such as lead,complex outside circuit,poor anti-jamming and other issues, and part of a deal with them Improperly, could cause the entire system of the decline. With modern science and technology of semiconductor development, especially large-scale integrated circuit design technologies, digital, miniaturization, integration sensors are becoming an important direction of development. In the control systems with the core of SCM,assembly language programming is used to achieve the control of the whole system.Combining with the operation sequence of ADC0809,the interface circuit diagrams of 80C51 SCM and ADC0809 parallel A/D conveger ale given.The basic skills of assembly language programming based on the operation se—quenee of the chip ale put forward.This system include temperature sensor and data transmission, the moduledisplays

高速数据采集系统

目录 1系统摘要 (2) 2系统设计理论 (2) 3系统设计方案 (4) 3.1AD7891高速数据采集系统 (4) 3.1.1 AD7891结构及功能 (4) 3.1.2工作时序和极限参数 (5) 3.1.3 AD7891的应用 (6) 3.1.4 AD7891与微处理器的接口 (8) 3.2PCI-1714高速数据采集系统……………………………….…,,,.9 3.2.1 PCI- 1714 功能结构和特点 (9) 3.2.2 PCI- 1714的系统构成..............................,.. (10) 3.3基于AT89C51的数据采集通信系统设计 (12) 3.3.1系统硬件设计 (12) 3.3.2系统软件设计 (14) 4各种方案的比较 (16) 5心得体会 (17) 6参考文献 (18)

1.系统简介 随着数字技术的飞速发展,高速数据采集系统也迅速地得到了广泛的应用。在生产过程中,应用这一系统可以对生产现场的工艺参数进行采集、监视和记录,为提高生产质量,降低成本提供了信息和手段。在科学研究中,应用数据采集系统可以获取大量的动态数据,是研究瞬间物理过程的有力工具,为科学活动提供了重要的手段。而当前我国对高速数据采集系统的研究开发都处于起步阶段,因此,开发出高速数据采集系统就显得尤为重要了。 所谓高速数据采集系统,是用计算机控制的多路数据自动检测或巡回检测(其对象包括数字和模拟信号),并且能够对数据实行某些处理(包括存储、处理、分析计算以及从检测的数据中提取可用的信息),以供显示、记录、打印或描绘的系统。 在数字技术日新月异的今天,数据采集技术的重要性是十分显著的。它是数字世界和外部物理世界连接的桥梁。而随着现代工业和科学技术的发展,对数据采集技术的要求日益提高,在雷达、声纳、图像处理、语音识别、通信、信号测试等科研实践领域中,都需要高精度,高数据率的数据采集系统。它的关键技术为高速高精度的ADC 技术,高数据率的存储和缓存技术以及系统高可靠性保证等。通过数据采集技术,科研人员在实验现场可以根据需要实时记录原始数据,用于实验室后期的分析和处理,对工程实践和理论分析探索具有重大意义。 2.系统设计理论 整个高速数据系统主要分为四个部分:数据采集部分、数据控制部分、数据处理部分、数据传输部分。 在数据采集部分,主要应用的就是采样定理、模数转换器ADC 及A/D 转换技术。采用定理说明采样频率与信号频谱之间的关系,是连续信号离散化的基本依据。具体内容是,频带为F 的连续信号f(t)可用一系列离散的采样值)1(t f ,)1(t t f ?±,)1(t t f ?±,……来表示,只要这些采样点的时间间隔F t 21≤?,便可根据各采样值完全恢复原来的信号)(t f 。模数转换器ADC 用来把连续变化的模拟信号转换为一定格式的数字量。ADC 转换器实际上就是一个编码器,输

嵌入式系统开发课程-多路数据采集系统设计

嵌入式系统开发课程-多路数据采集系统设计 -CAL-FENGHAI-(2020YEAR-YICAI)_JINGBIAN

多路数据采集系统设计

1题目要求 所设计的数据采集系统,共有16路信号输入,每路信号都是0~10mV,每秒钟采集一遍,将其数据传给上位PC计算机,本采集地址为50H。要求多路模拟开关用4067,A/D转换用ADC0809,运算放大器用OP07,单片机用89C51,芯片用 MAX232。 设计其电路原理图,用C51语言编制工作程序。 2总体方案设计 根据题目要求,传感器首先采集16路信号,然后被多路模拟开关4067选通某一路信号,接着通过信号调理电路,由A/D转换器进行模/数转换后发送给单片机,之后通过MAX232由RS232串口进行通讯,最终将数据传递到上位PC计算机。因此,数据采集系统主要包括以下几个主要环节: 2.1信号选通环节 由于题目要求采集的信号路数达到了16路,每一路信号的流通路线均相同。如果为每路信号都设置相应的放大、A/D转换单元,成本将大幅度提升。因此可以接入一个多路模拟开关4076,轮流选通每一路信号,实现多路信号共用一个运算放大器和A/D转换单元,即降低了成本,又简化了电路。 4067为16路模拟开关,其内部包括一个16选1的译码器和被译码输出所控制的16个双向模拟开关。当禁止端INH置0时,在I/N0-I/N15中被选中的某个输入端与输出公共端X接通,外部地址输入端A、B、C、D决定了被选通端;当INH置1时,所有模拟开关均处于断路状态。 2.2信号调理电路 为了方便信号的进一步传输和处理,一般均要在传感器的输出端接入信号调理电路,对传感器输出的信号进行变换、隔离、放大、滤波等处理。此处的信号波动范围只有0~10mV,属于微弱信号,需要进行放大处理。按照题目要求,本文设计的系统选用运算放大器OP07。OP07是一种高精的度单片运算放大器,其输入失调电压和漂移值均很低,适合用作前级放大器。 2.3A/D转换器 由于单片机只能处理数字信号,所以需要接入A/D转换器将模拟信号转换成数字信号。本文采用题目提供的ADC0809,它可以和单片机直接通讯。ADC0809由一个8路模拟开关、一个地址锁存与译码器、一个A/D转换器和一个三态输出锁存器组成。多路开关可选通8个模拟通道,允许8路模拟量分时输入,共用A/D转换器进行转换。三态输出锁器用于锁存A/D转换完的数字量,当OE端为高电平时,才可以从三态输出锁存器取走转换完的数据。 此处采用中断的方式使数据在单片机与ADC0809之间进行交换,端口地址为 FF50H;P0口和WR信号共同生成单片机的启动转换信号;为了在启动转换的同时选通通道,将通道地址锁存信号ALE与START相连;把P0口和RD同时处在有效位的组

一种高速数据采集系统的研究

第31卷第5期 唐山师范学院学报 2009年9月 Vol. 31 No. 5 Journal of Tangshan Teachers College Sep. 2009 ────────── 收稿日期:2008-12-12 作者简介:李洋(1982-),男,河北衡水人,唐山师范学院基础教育部教师。 -66- 一种高速数据采集系统的研究 李 洋,郭小松 (唐山师范学院 基础教育部,河北 唐山 063000) 摘 要:由于高速数据采集对信号完整性、信号干扰、高速布线及数据处理和高速实时存储要求极高,而其应用环境又往往非常复杂,所以在目前的实际应用中,很难实现一种既能进行长时间高速数据采集、又能进行大容量存储的数据采集系统。在此背景下,提出了一种高速数据采集及存储的解决方案,采用高速FPGA 加嵌入式微处理器作为中央处理器来进行高速数据传输和磁盘阵列数据存储,实现高速数据采集及大容量实时存储。 关键词:数据采集;模数转换;海量存储;RAID0 中图分类号: T N919.5 文献标识码:A 文章编号:1009-9115(2009)05-0066-03 Study of High-Speed Data Acquisition and Storage System LI Yang, GUO Xiao-song (Department of Foundation Education, Tangshan Teachers College, Tangshan Hebei 063000, China) Abstract: Because of the extreme requirements of signal integrity, noise jamming, high-speed layout, high-speed real-time storage and the complex application environments, it is very difficult to realize a high-speed data acquisition system which is suitable for long-time data acquisition and mass storage. Against this background, a solution of high-speed data acquisition and storage system is introduced in this thesis, which is using of high-speed FPGA and embedded microprocessors as the central processing device for high-speed data transfer and data storage of redundant array of inexpensive disks , realized on-time data acquisition and mass storage. Key words: data acquisition; A/D convert; mass storage; RAID 现代工业生产和科学研究对数据采集的要求日益提高,在雷达、声纳、软件无线电、瞬态信号测量等一些高速、高精度的测量中,需要进行高速数据采集。目前,数据采集系统在高速A/D 、D/A 器件发展的带动下,采集带宽在稳步提高,具有100MSPS 采集能力以上的高速数据采集系统产品己较成熟。然而国外厂商的高速采集系统往往都价格不菲,而且由于高速数据采集对信号完整性、信号干扰、高速布线及数据处理和高速实时存储要求极高,国内完全掌握这个技术的厂商并不多,所以在实际应用中,很难找到一种满足需要的高速采集系统。这种情况长期限制了高速数据采集技术在我国工业生产和科学研究中的应用。 在这样的背景下,本文提出一种高速数据采集与实时存储系统的解决方案,解决以往在高速技术、数据存储与传输技术等方面的几个技术难点,采用FPGA 作为核心器件,集成中央逻辑控制及硬盘接口,直接将高速数据存入有多块硬 盘组成的实时RAID 存储系统中,实现了高速采集和实时存储,并可脱机运行。这种方案成本低廉,能提高采集速度,增加系统可靠性,并大大提高可持续采集时间,具有较大的灵活性。 1 总体系统方案硬件设计 高速数据采集系统的主要目的是把采集到的模拟信号转化为数字信号,所以模拟信号进入数据采集系统的第一步就是通过AD 采集电路进行模数转换;采集到的数据为了以后研究调用,就需要存储到存储器中,所以系统的最后一步是使用高速海量存储器对数据进行存储;系统的启动、停止和数据传输的方式还需要使用中央逻辑控制电路,所以在AD 采集电路与高速海量存储器之间增加中央逻辑控制电路来作为AD 采集电路与高速海量存储器之间的桥梁;系统通过人机接口与PC 机连接,可以对数据采集系统进行调试,还方便调用存储数据进行研究测试,并实现

数据采集与传输系统实验报告

(此文档为word格式,下载后您可任意编辑修改!) 数据采集与传输系统 摘要 该数据采集与传输系统以89C51及89C2051为核心,由数据采集模块、调制解调模块、模拟信道、测试码发生器、噪声模拟器、结果显示模块等构成。在本方案中仅使用通用元器件就较好的实现了题目要求的各项指标。其中调制解调模块、噪声模拟器分别采用单片机和可编程逻辑器件实现。本数据采集与传输系统既可对8路数据进行轮检,也可设置为对一路数据单独监控。本系统硬件设计应用了EDA 工具,软件设计采用了模块化的编程方法。传输码元速率为16kHz~48kHz的二进制数据流。另外,还使用了“1”:“01”、“0”:“10”的Manchester编码方法使数据流的数据位减少,从而提高传输速率。

一、方案设计与论证 首先,我们分析一下信道与信噪比情况。本题中码元传输速率为16k波特,而信号被限定在30k~50kHz的范围内,属于典型的窄带高速率数字通信。而信噪比情况相对较好。这是因为信号带宽仅为20kHz,而噪声近似为0~43kHz()的窄带白噪声,这样即使在信号和噪声幅度比值为1:1的情况下,带内的噪声功率仍然比较小,所以系统具有较高的信噪比。 方案一: 常用的数字调制系统有:ASK、FSK、PSK等。其中FSK具有较强的抗干扰能力,但其要求的的带宽最宽,频带利用率最低,所以首先排除。ASK理论上虽然可行,但在本题目中,由于一个码元内只包括约两个周期的载波,所以采用包络检波法难以解调,也不可行。另外,对于本题目,还可以考虑采用基带编码的方法进行传输,如HDB3码,但这种编码方法其抗干扰能力较差,因此也不太适合。 方案二: PSK调制方式具有较强的抗干扰能力,同时其调制带宽相对也比较窄,因此我们考虑采用这种调制方式。为了简化系统,在实际实现时,我们采用了方波作为载波的PSK调制方式。当要求的数据传输速率较低(≤24kbps)时,对原始数据处理的方法如下:

51单片机数据采集系统[1]

课程设计报告书 设计任务书 一、设计任务 1一秒钟采集一次。 2把INO口采集的电压值放入30H单元中。 3做出原理图。 4画出流程图并写出所要运行的程序。 二、设计方案及工作原理 方案: 1. 采用8051和ADC0809构成一个8通道数据采集系统。 2. 能够顺序采集各个通道的信号。

3. 采集信号的动态范围:0~5V。 4. 每个通道的采样速率:100 SPS。 5.在面包板上完成电路,将采样数据送入单片机20h~27h存储单元。 6.编写相应的单片机采集程序,到达规定的性能。 工作原理: 通过一个A/D转换器循环采样模拟电压,每隔一定时间去采样一次,一次按顺序采样信号。A/D转换器芯片AD0809将采样到的模拟信号转换为数字信号,转换完成后,CPU读取数据转换结果,并将结果送入外设即CRT/LED显示,显示电压路数和数据值。 目录 第一章系统设计要求和解决方案 第二章硬件系统 第三章软件系统 第四章实现的功能 第五章缺点及可能的解决方法 第六章心得体会

附录一参考文献 附录二硬件原理图 附录三程序流程图 第一章系统设计要求和解决方案 根据系统基本要求,将本系统划分为如下几个部分: 信号调理电路 8路模拟信号的产生与A/D转换器 发送端的数据采集与传输控制器 人机通道的接口电路 数据传输接口电路 数据采集与传输系统一般由信号调理电路,多路开关,采样保持电路,A/D,单片机,电平转换接口,接收端(单片机、PC或其它设备)组成。系统框图如图1-1所示

信号采集分析 被测电压为0~5V 直流电压,可通过电位器调节产生。 信号采集 多路数据采集系统多采用共享数据采集通道的结构形式。 数据采集方式选择程序控制数据采集。 程序控制数据采集,由硬件和软件两部分组成。,据不同的采集需要,在程序存储器中,存放若干种信号采集程序,选择相应的采集程序进行采集工作,还可通过编新的程序,以满足不同采样任务的要求。如图1-3所示。 程序控制数据采集的采样通道地址可随意选择,控制多路传输门开启的通道地址码由存储器中读出的指令确定。即改变存储器中的指令内容便可改变通道地址。 由于顺序控制数据采集方式 缺乏通用性和灵活性,所以本设计中选用程序控制数据采集方式。 采集多路模拟信号时,一般用多路模拟开关巡回检测的方式,即一种数据采集的方式。利用多路开关(MUX )让多个被测对象共用同一个采集通道,这就是 图1-3 程序控制数据采集原理 图1-1 一般系统框图

数据采集AD转换实验报告

学生实验报告册 课程名称:___________________________________ 学院:______________________________________ 专业班级:___________________________________ 姓名:______________________________________ 学号:______________________________________ 指导教师:___________________________________ 成绩:______________________________________ 学年学期:2017-2018学年秋学期 重庆邮电大学教务处制

STAB! CUt OK ⑵ ADC0809引脚结构 ADC0809各脚功能如下: D7 ~ D0 : 8位数字量输出引脚。IN0 ~ IN7 : 8位模拟量输入引脚。 VCC +5V工作电压。GND地。 REF( +):参考电压正端。REF(-):参考电压负端。 START A/D转换启动信号输入端。 ALE地址锁存允许信号输入端。(以上两种信号用于启动A/D转换). EOC转换结束信号输出引脚,开始转换时为低电平,当转换结束时为高电平。 OE输出允许控制端,用以打开三态数据输出锁存器。 CLK时钟信号输入端(一般为500KHZ。 A B、C:地址输入线。 ⑶ADC0809对输入模拟量要求: 信号单极性,电压范围是0- 5V,若信号太小,必须进行放大;输入的模拟量在转换过程中应该保持不变,如若模拟量变化太快,则需在输入前增加采样保持电路。 地址输入和控制线:4条 ALE为地址锁存允许输入线,高电平有效。当ALE线为高电平时,地址锁存与译码器将A,B, C三条地址线的地址信号进行锁存,经译码后被选中的通道的模拟量进转换器进行转换。A,B和C为地址输入线,用于选通IN0 —IN7上的一路模拟量输入。通道选择表如下表所示。

基于GPS的汽车导航系统的设计与实现

邮局订阅号:82-946360元/年技术 创新 汽车电子 《PLC 技术应用200例》 您的论文得到两院院士关注 基于GPS 的汽车导航系统的设计与实现 Realization and design of automobile guidance system based on GPS (吉林工程技术师范学院)张丹彤 ZHANG Dan-tong 摘要:设计并实现了一种以单片机为主要控制器件、基于GSP 模块的新型智能电动汽车底盘的导航系统。GPS 定位系统主 要采用技术非常成熟的GPS 模块进行与单片机的接口通信完成,使用更方便,定位也更准确。所设计的电动导航系统具有全球定位、自动控制、实时性好等多方面优点为一体,应用在当今的汽车上有较好的发展前景。关键词:GPS;导航;数据采集中图分类号:U49文献标识码:A Abstract:The present paper introduced one kind take the monolithic integrated circuit as the primary control component,based on GSP module new intelligent electric automobile chassis guidance system design.The GPS localization mainly uses the technical ex -tremely mature GPS module to carry on with the monolithic integrated circuit connection correspondence completes,use more conve -nient,the localization is also more accurate.This chassis collection whole world localization,the automatic control,timeliness good and so on the various merit is a body,applies has the good prospects for development on the now automobile.Keywords:GPS;navigation;data acquisition 文章编号:1008-0570(2008)11-2-0255-02 近年来,我国私人小轿车拥有量呈上升趋势,单位用轿车拥有量也在快速发展,对于这一类车辆,GPS 领航系统侧重于电子地图领航,对运行路线不固定的车辆,可预先设置到达目的地,在运行中告知运行路线,起到领航的重要作用。本论文介绍了一种以单片机为主要控制器件,基于GSP 模块的新型智能电动汽车底盘的导航系统设计。 1主体控制方案 本系统是以单片机为主要控制器件,基于GSP 模块的新型智 能电动汽车底盘的导航系统设计。该车底盘具有智能避障、 寻迹、测距、报警、寻光、行驶路程显示、行驶时间显示、车体所在环境温度显示、车体所在环境湿度显示、人工定位等功能。可以使用无线遥控器控制,并可以在上位机显示出它所在的位置等数据信息。本系统设计主要包括硬件电路的设计、实时操作系统程序设计、多机通信设计与总线接口的设计。系统框图如图1所示。 图1系统框图 本系统硬件电路主要包括控制模块、GPS 定位模块、电机 驱动模块、传感器数据采集模块、网络节点接口模块、光报警模 块、 显示驱动模块、时间模块、键盘模块与无线通信模块组成。传感器数据采集模块由光电传感器进行对光线的跟踪,红外传 感器进行对近距离的数据采集,声纳传感器进行对远距离的数 据采集,温度传感器对车体周围的环境温度采集,湿度传感器 对周围环境的相对湿度采集等。网络接口采用串行通信方式。 显示驱动模块由LED 数码管与液晶共同显示。无线通信模块采用FSK 方式进行无线传输。 2GPS 定位系统设计 GPS 定位主要采用技术非常成熟的GPS 模块进行与单片机的接口通信完成。电机驱动电路模块主要采用H 型电路构建而成。GPS 模块的电源接口供电有15v 、12v 、5v 、3.3v 不等,本系统为了设计简单采用全新台湾HOLUX 公司推出的SIRF 第三代高灵敏度超小型GPS 接收模块这是最新推出的产品,采用 SiRF 第三代芯片, 主要是定位灵敏度大大提高,例如在汽车上应用时,只要靠近车窗就能较好工作,使用更方便,定位也更准确。本模块主要是提供给从事GPS 模块二次开发的客户使用的,GPS 模块使用3.3伏 (70毫安)直流工作电压,默认每秒输出一次TTL 的NMEA-0183信号。 此模块接口定义如表1所示。GPS 控制模块口控制模块方框图如图2所示。为了使车具 有导航系统,所以在车体上安装了GPS 模块,本设计采用全新台湾HOLUX 公司推出的SIRF 第三代高灵敏度超小型GPS 接 收模块,该模块由6个控制脚组成。为了减轻主控CPU 的负担,并且为了模块化硬件,所以该GPS 模块由一块STC12C2052单 片机进行单独的控制,并且通过74HS573与主单片机进行总线通信。STC12C2052单片机与GPS 通过串行口连接,并且以4800bps 的波特率进行通信。单片机的P1口与74HC573的数据输入口相连接,作为并行的8为数据总线使用,而LE 端口通过一个反响器与STC12C2052单片机的P3.7连接,并且P3.7口 通过一个74HC14与主控单片机的INT0相连。这样当P3.7为张丹彤:副教授 255--

高速数据采集技术发展综述

高速数据采集技术发展综述 摘要:高速数据采集系统广泛应用于军事、航天、航空、铁路、机械等诸多行业。区别于中速及低速数据采集系统,高速数据采集系统内部包含高速电路,电路系统1/3以上数字逻辑电路的时钟频率>=50MHz;对于并行采样系统,采样频率达到50MHz,并行8bit以上;对于串行采样系统,采样频率达到200MHz,目前广泛使用的高速数据采集系统采样频率一般在200KS/s~100MS/s,分辨率16bit~24bit。本篇文章主要简单介绍高速数据采集技术的发展,高速数据采集系统的结构、功能、原理、实现形式以及一些主要的应用。 关键词:高数数据采集系统、系统结构、系统原理、系统功能、实现形式、应用举例。 引言:高速数据采集技术在通信、航天、雷达等多个领域中广泛应用。随着软件无线电、通信技术、图像采集等技术的发展,对数据采集系统的要求越来越高,不仅要求较高的采集精度和采样速率,还要求采集设备便携化、网络化与智能化,并且需要将采集信息稳定的传输到计算机,进行显示与数据处理。同时,以太网协议已经成为当今局域网采用的最通用的通信协议标准。在嵌入式领域中,将以太网协议与数据采集系统相结合,形成局域网,实现方便可靠的数据传输与控制,是当前的研究热点。 1. 高速数据采集的发展 数据采集系统起始于20世纪50年代,由于数据采集测试系统具有高速性和~定的灵活性,可以满足众多传统方法不能完成的数据采集和测试任务,因而得到了初步的认可。到了70年代中后期,在数据采集系统发展过程中逐渐分为两类,一类是实验室数据采集系统,另一类是工业现场数据采集系统。就使用的总线而言,实验室数据采集系统多采用并行总线,工业现场数据采集系统多采用串行数据总线。随着微型机的发展,诞生了采集器、仪表等同计算机融为一体的数据采集系统。由于这种数据采集系统的性能优良,超过了传统的自动检测仪表和专用数据采集系统,因此获得了惊人的发展他3。随着计算机的普及应用,数据采集系统得到了极大的发展,基于标准总线并带有高速DSP的高速数据采集板卡产品也越来越多,技术先进、市场主流的厂商主要有Spectrum Signal Processing,SPEC,Signatec,Acquisition Logic,Blue Wave等公司 2001年Acquisition logic公司推出了基于PCI总线,采样率为500MS/s,1GS/s的8bit数据采集板卡AL500和AL51G,它的存储深度分别为64MB,256MB和1000MB三种。PCI 总线为主模式,数据宽度32bit,时钟频率33MHz,在突发模式下传输速率可达到133MB /s。两种板卡还同时具有数字信号处理功能:通过板卡上的现场可编程门阵列FPGA来实