c#释放timer

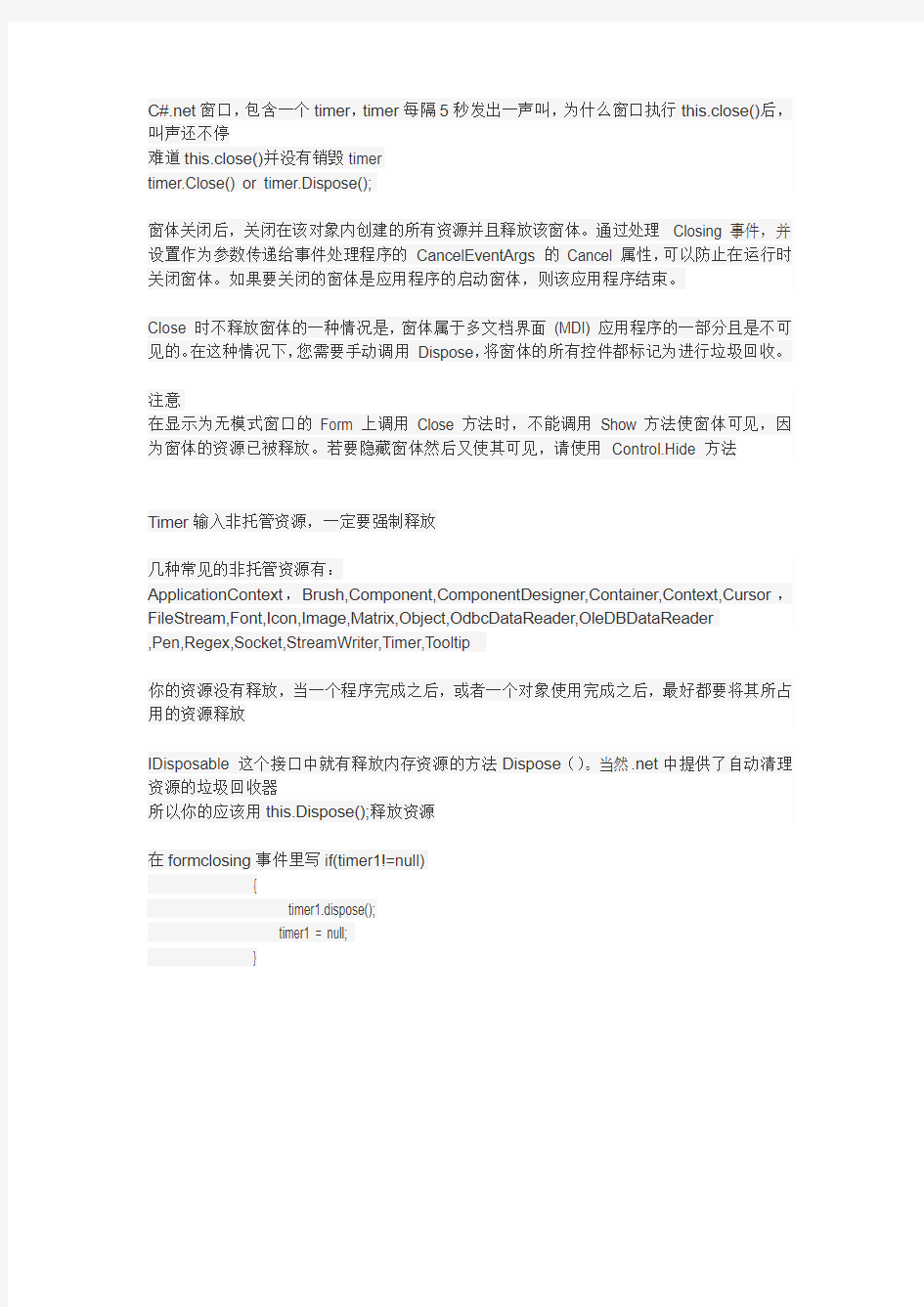

C#.net窗口,包含一个timer,timer每隔5秒发出一声叫,为什么窗口执行this.close()后,叫声还不停

难道this.close()并没有销毁timer

timer.Close() or timer.Dispose();

窗体关闭后,关闭在该对象内创建的所有资源并且释放该窗体。通过处理 Closing 事件,并设置作为参数传递给事件处理程序的 CancelEventArgs 的 Cancel 属性,可以防止在运行时关闭窗体。如果要关闭的窗体是应用程序的启动窗体,则该应用程序结束。

Close 时不释放窗体的一种情况是,窗体属于多文档界面 (MDI) 应用程序的一部分且是不可见的。在这种情况下,您需要手动调用 Dispose,将窗体的所有控件都标记为进行垃圾回收。

注意

在显示为无模式窗口的 Form 上调用 Close 方法时,不能调用 Show 方法使窗体可见,因为窗体的资源已被释放。若要隐藏窗体然后又使其可见,请使用 Control.Hide 方法

Timer输入非托管资源,一定要强制释放

几种常见的非托管资源有:

ApplicationContext,Brush,Component,ComponentDesigner,Container,Context,Cursor,FileStream,Font,Icon,Image,Matrix,Object,OdbcDataReader,OleDBDataReader

,Pen,Regex,Socket,StreamWriter,Timer,Tooltip

你的资源没有释放,当一个程序完成之后,或者一个对象使用完成之后,最好都要将其所占用的资源释放

IDisposable 这个接口中就有释放内存资源的方法Dispose()。当然.net中提供了自动清理资源的垃圾回收器

所以你的应该用this.Dispose();释放资源

在formclosing事件里写if(timer1!=null)

{

timer1.dispose();

timer1 = null;

}

用状态机设计的交通灯控制器

/module traffic (clock, reset, sensor1, sensor2, red1, yellow1, green1, red2, yellow2, green2); input clock, reset, sensor1, sensor2; output red1, yellow1, green1, red2, yellow2, green2; // Define the states. Enumerated type pragma allows Spectrum to chose encoding. parameter /*exemplar enum ee1 */ st0 = 0, st1 = 1, st2 = 2, st3 = 3, st4 = 4, st5 = 5, st6 = 6, st7 = 7; reg [2:0] /* exemplar enum ee1 */ state, nxstate ; reg red1, yellow1, green1, red2, yellow2, green2; // Update the state with the next state on the clock edge // or reset value. always @(posedge clock or posedge reset) begin if (reset) state = st0 ; else state = nxstate; end // // Calculate the next state and the outputs // based on the present state and the inputs // always @(state or sensor1 or sensor2) begin // Default values for the outputs

https://www.360docs.net/doc/7710873660.html, AJAX入门系列:Timer控件简单使用

https://www.360docs.net/doc/7710873660.html, AJAX入门系列:Timer控件简单使用 本文主要通过一个简单示例,让Web页面在一定的时间间隔内局部刷新,来学习一下https://www.360docs.net/doc/7710873660.html, AJAX中的服务端Timer控件的简单使用。 主要内容 Timer控件的简单使用 1.添加新页面并切换到设计视图。 2.如果页面没有包含ScriptManager控件,在工具箱的AJAX Extensions标签下双击ScriptManager控件添加到页面中。 3.单击ScriptManager控件并双击UpdatePanel控件添加到页面中。

4.在UpdatePanel控件内单击并双击Timer控件添加到UpdatePanel中。Timer控件可以作为UpdatePanel的触发器不管是否在UpdatePanel中。 5.设置Interval属性为10000。Interval属性的单位是毫秒,所以我们设置为10000,相当于10秒钟刷新一次。 6.在UpdatePanel控件中添加一个Label控件。

7.设置Label控件的Text属性为“Panel not refreshed yet ”。确保Label控件添加在了UpdatePanel控件里面。 8.在UpdatePanel之外再添加一个Label控件。确保第二个Label控件在UpdatePanel的外面。 9.双击Timer控件添加Tick事件处理,在事件处理中设置Label1的Text属性为当前时间。 protected void Timer1_Tick(object sender, EventArgs e)

{ Label1.Text = "Panel refreshed at: " + DateTime.Now.ToLongTimeString(); } 10.在Page_Load事件中添加代码设置Label2的Text属性为页面创建时间,如下代码所示: protected void Page_Load(object sender, EventArgs e) { Label2.Text = "Page created at: " + DateTime.Now.ToLongTimeString(); } 11.切换到代码视图,确保代码如下所示: protected void Page_Load(object sender, EventArgs e) { Label2.Text = "Page created at: " + DateTime.Now.ToLongTimeString(); } protected void Timer1_Tick(object sender, EventArgs e) { Label1.Text = "Panel refreshed at: " + DateTime.Now.ToLongTimeString(); } 12.保存并按Ctrl + F5运行 13.等待10秒钟后可以看到Panel刷新,里面的Label文字改变为刷新的时间而外面的Label没有改变。

第14章 状态机设计(state machine design)

第14章 状态机设计(State Machine Design) 讲到VHDL设计而不讲state machine,感觉上就是不太完整,我们先来看看什么是state machine,它应该是一种流程控制的设计,在有限的状态中,根据判别信号的逻辑值决定后面要进入哪一个状态,这样的讲法似乎有些抽象,我们先来看看下面的状态图。 图14-1所显示的是一个十字路口的红绿灯控制设计,在一开始时信号Reset 会被设为逻辑’0’,此时state machine会在Reset状态,一直等到信号Reset变成逻辑’1’时,state machine才会进入真正的控制状态。在之后的三个状态中,我们各定义了一个counter,当进入Red或是之后的Green及Yellow状态时,相对的counter值即会开始递减。当counter值递减到0时,state machine即会改变到下一个状态。 当然state machine的执行就是依照这种方式进行,但是其中仍有许多的细节是设计者所要注意的,在接下来的章节中,我们会依据实际的例子来介绍state machine的设计方式。 14-1State Machine的建立 在这一节我们所举的例子是一个类似检查密码的设计,在一般办公室的门口都会有门禁管制,进门前须先输入一组四个数字的密码,当密码确认无误后门才会打开,除此之外还有更改密码的功用。我们先来看看其状态图。 在图14-2中一共有四个状态,一开始会维持在idle状态,当要更改或是第一次输入密码时,需要按下一个特殊的“密码更改”按键,此时InpinN信号会变成逻辑’0’的状态,状态机即会进入LoadPin的状态,接着再输入四个数字的密码,密码输入完毕按下“输入”按键,状态机即回到原先的idle状态。 在另一方面,当处于平时状态,有人进入门口要输入密码前,他也必需要按下另一个特殊键“密码输入”,表示之后输入的数字是待验证的密码,此时InData 信号会变成逻辑’0’,于是状态机进入InPin的状态。在输入四个数字之后,一个

实验四 有限状态机设计(2学时)

实验四有限状态机设计(2学时) 实验内容一: 状态机是指用输入信号和电路状态(状态变量)的逻辑函数去描述时序逻辑电路功能的方法,也叫时序机。有限状态机是指在设计电路中加入一定的限制条件,一般用来实现数字系统设计中的控制部分。 根据时序电路输出信号的特点可将时序电路划为Mealy 型和Moore 型两种。Moore型电路中,输出信号仅仅取决于存储电路的状态。Mealy型电路中,输出信号不仅取决于存储电路的状态,而且还取决于输入变量。图1是某Mealy型电路的状态转换图,图中圆圈内的S0、S1等代表电路的状态,状态转换箭头旁斜杠“/”上边的数字代表输入信号,斜杠“/”下边的数字代表输出信号。假设电路的当前状态为S0,当输入信号为0时,电路的下一个状态仍为S0,输出信号为0;当输入信号为1时,电路的下一个状态为S1,输出为1。 图1 Mealy状态机 下面的程序中使用两个进程来描述该状态机。第一个进程负责状态转化,在CP上升沿到达时,当前状态(PresetState)向下一个状态(NextState)的转换;第二个进程负责检测输入信号(DIN)和当前状态(PresetState)的值,并由CASE-WHEN 语句决定输出信号(OP)和下一个状态值(NextState)的值。请补充下图中虚线“…”部分省略掉的程序,然后对完整程序进行编译,并用Tools->Netlist Views->State Machine Viewer和RTL Viewer工具查看该状态机的状态图和RTL顶层图。

… … 实验内容二: 论文《基于VHDL的一个简单Mealy状态机》中设计了一个Mealy状态机用来检测数据流“1101010”,用以验证状态机在数据检测上的应用。请在读懂文中程序的基础上,在Quartus Ⅱ软件中通过编译仿真得到状态图和波形图,仿真中输入波形的设置应能体现该状态机的用途。 实验报告: 本次实验占用两个学时,请于12周周四(5月12日)上课时交实验报告。对于实验内容一,报告的内容应重在程序的完善上,对于实验内容二,报告的内容应重在对论文中源程序的分析和理解,以及仿真的波形图上。

计时器控件在VB中的应用

计时器控件在VB中的应用 计时器控件在工具箱中的名称是Timer,该控件是一个非可视控件,即在运行时不可见,用于实现每隔一定时间间隔执行指定的操作。Timer控件对于其他后台处理也是非常有用的。本文用实例来介绍在VB程序中利用计时器控件,实现在程序在启动运行期间各种不同的效果。下面给出编程设计过程,供读者参考选用。 一、计时器(Timer)控件与标签(Label)控件的应用 1、启动VB,新建工程。在工程中添加一个窗体Form1,在窗体上加入一个Timer 计时器控件Timer1和标签控件Label1 2、编写相应的代码,实现不同的功能 (1)字体颜色发生随机变化的效果,计时器事件(Timer)代码如下: l 窗体Form1的加载事件代码 Private Sub Form_Load() Timer1.interval=500 Label1.Caption = “欢迎进入VB应用程序” Label1.font.size=20 Label1.autosize=true End Sub l 计时器(Timer1)控件的Timer事件代码 Private Sub Timer1_Timer() Label1.ForeColor = RGB(255 * Rnd, 255 * Rnd, 255 * Rnd) End Sub (2)依次出现字幕的实现效果,相关事件代码如下: Dim i …在通用-声明中定义变量… Private Sub Timer1_Timer() i = i + 1 Label1.Caption = Left(“欢迎进入VB应用程序”, i) If i > 10 Then i = 0 End If End Sub (3)滚动字幕的实现效果,相关事件代码如下: l 窗体Form1的加载事件代码 Private Sub Form_Load() Label1.Caption = “欢迎进入VB应用程序” End Sub l 计时器(Timer1)控件的Timer事件代码 Private Sub Timer1_Timer() If Label1.Left <= Form1.Width Then Label1.Left = Label1.Left + 100 Else Label1.Left = -Label1.Width End If End Sub (4)制作字体闪烁的效果

如何设计最优化的状态机(有图版)

如何设计最优化的状态机 前言:数字电路通常分为组合逻辑电路和时序电路, 组合逻辑电路outputs = F(current inputs) 时序电路outputs = F(current inputs,past inputs) 有限状态机就是时序电路的数学抽象,一个有限状态机系统包括inputs ,outputs, states .状态机分为同步状态机(synchronous)和异步状态机(asynchronous),异步状态机由于输出信号不稳定,所以不详细讨论,对绝大多数设计来说,用的最广泛的是同步状态机。下面主要讨论了同步状态机的设计。 一.状态机的基础知识 1.1. moore状态机和mealy状态机的区别: 2.1.1moore状态机输出只依赖于及其的当前状态,与输入信号无关。这是moore状态机的优点。下面是moore状态机的模型: moore状态机比较容易用数学的方式来分析,因此被更广泛的用在代数状态机理论中(algebraic FSM theory)。 Mealy状态机输出依赖于机器现在的状态和输入的值,如果输入改变,输出可以在一个时钟周期中将发生了改变。其模型如下: 图的说明:state memory :保存现在的状态(current state s(t) ) state transistion function :根据现态和输入x(t),s(t+1)来决定下一个状态。 Output function :根据s(t)和x(t)来决定最后的输出。 Mealy 状态机通常可以有更少的状态变量,因此在工程领域有更为广阔的应用,状态变量越少,则所需的存储单元就越少。

有限状态机设计

有限状态机设计 实验报告 一.实验题目 有机状态机设计 二.实验目的 掌握有机状态机设计的基本方法。 三.实验远离 状态机是指用输入信号和电路状态(状态变量)的逻辑函数去描述时序逻辑电路功能的方法,也叫时序机。有限状态机是指在设计电路中加入一定的限制条件,一般用来实现数字系统设计中的控制部分。 四.实验内容

实验内容一: 状态机是指用输入信号和电路状态(状态变量)的逻辑函数去描述时序逻辑电路功能的方法,也叫时序机。有限状态机是指在设计电路中加入一定的限制条件,一般用来实现数字系统设计中的控制部分。 根据时序电路输出信号的特点可将时序电路划为Mealy 型和Moore 型两种。Moore型电路中,输出信号仅仅取决于存储电路的状态。Mealy型电路中,输出信号不仅取决于存储电路的状态,而且还取决于输入变量。图1是某Mealy型电路的状态转换图,图中圆圈内的S0、S1等代表电路的状态,状态转换箭头旁斜杠“/”上边的数字代表输入信号,斜杠“/”下边的数字代表输出信号。假设电路的当前状态为S0,当输入信号为0时,电路的下一个状态仍为S0,输出信号为0;当输入信号为1时,电路的下一个状态为S1,输出为1。 图1 Mealy状态机 下面的程序中使用两个进程来描述该状态机。第一个进程负责状态转化,在CP上升沿到达时,当前状态(PresetState)向下一个状态(NextState)的转换;第二个进程负责检测输入信号(DIN)和当前状态(PresetState)的值,并由CASE-WHEN 语句决定输出信号(OP)和下一个状态值(NextState)的值。请补充下图中虚线“…”部分省略掉的程序,然后对完整程序进行编译,并用Tools->Netlist Views->State Machine Viewer和RTL Viewer工具查看该状态机的状态转移图和RTL原理图。

iFix定时器控件使用心得

iFix定时器控件使用心得 iFix的定时器控件,经常会把初学者搞得头晕脑涨,我说说自己的心得,供大家参考。 该控件是基于调度功能的,所以有一些用法和其它编程平台(如VB)里的定时器不太一样。 一、定时器的启动/停止 如果在编辑时TimerEnabled设为True,则运行时定时器会自动启动。如果在编辑时TimerEnabled设为False,则运行时需要先将TimerEnabled设为True,然后调用StartTimer方法。如果只将TimerEnabled设为True,但是不调用StartTimer 方法,定时器是不会开始工作的。如果要停止定时器,可以调用StopTimer方法,也可以直接将TimerEnabled设为False。也就是说有两种控制定时器启/停的方式: 方式一: 用如下代码启动:Timer1. TimerEnabled=True Timer1. StartTimer 用如下代码停止:Timer1. TimerEnabled=False 方式2: 在画面或调度的Initializes事件中加入:Timer1. TimerEnabled=True 用如下代码启动:Timer1. StartTimer 用如下代码停止:Timer1. StopTimer 二、以“连续”方式使用 以“连续”方式使用时,你会发现这样的现象,例如你希望一个画面被打开10秒钟后自动关闭,你会将定时器的Interval 属性设为10000,事实上却是,画面不到10秒就会被关闭,而且每次的延时时间还不是固定的,似乎是随机的,有时几乎是10秒,有时还不到1秒。这个举例中,定时器仅运行了1次(因为画面已经被关闭了),如果定时器一直运行下去,你还会发现,除了第一次的延时是“随机”的,从第二次开始,延时都是准确的。 这究竟是怎么回事呢?其实这是StartTime属性在起作用,StartTime属性的默认值是0:00:00,表示从午夜0点0分0秒开始,在这种情况下,如果设置为10秒钟的间隔,定时器被触发的时间将是每一分钟的0秒、10秒、20秒……50秒,如果从某一分钟的18秒启动了定时器,那么定时器第一次被触发的时间将会是20秒,也就是说,从启动到第一次触发之间仅有2秒钟的延时,如果你从15秒启动,会得到5秒钟的延时,这就是为什么你会觉得第一次的延时是“随机”的。 好的,既然知道了原因,自然也就有了解决的方法,那就是在每一次调用StartTimer方法之前,将StartTime属性设为当前时间,即Timer1. StartTime = Now就搞定了。例如在8:15:23秒启动,间隔10秒,第一次触发将会是在8:15:33秒的时候。 那是不是所有以“连续”方式使用时,这样作就都OK了呢?不是。这个方法是否有效(也就是得到精确的延时),要看你所希望的延时时间有多长,如果延时是10秒或更长,那没问题,这样是唯一正确且简便的方法。但如果你设置的延时间隔比较小,如3秒以内,甚至是毫秒级的,那么这个方法就会产生比较严重的误差。因为StartTime属性的时间精度只达到秒级,也就是说,实际的运行效果还是会有一定的误差,当然,这个误差最大不会超过1秒,所以一般来说对于5秒以上的延时设置,这个误差可以忽略。但如果延时设置是2秒,然后产生了接近1秒的误差,这就成问题了,误差率将近50%啊!如何解决此类问题呢?有办法,只是稍复杂一点。 例如,我们希望做到这样一个效果——有一个按钮对象(名为cmd1),当用鼠标点击这个按钮时,按钮消失不见,2秒钟之后又出现。也就是说在点击的时候把按钮的Visible属性设为False,并且启动一个定时器控件,2秒之后在定时器的OnTimeOut事件代码中,再把cmd1的Visible属性设为True。 如何比较精确地实现这2秒的时间间隔呢?具体做法是:将定时器的Interval属性设为100毫秒,定义一个模块级变

状态机及其VHDL设计

第7章状态机及其VHDL设计 内容提要:有限状态机(Finite State Machine,简称FSM)是一类很重要的时序电路,是许多数字系统的核心部件,也是实时系统设计中的一种数学模型,是一种重要的、易于建立的、应用比较广泛的、以描述控制特性为主的建模方法,它可以应用于从系统分析到设计的所有阶段。有限状态机的优点在于简单易用,状态间的关系清晰直观。建立有限状态机主要有两种方法:“状态转移图”和“状态转移表”。标准状态机通常可分为Moore和Mealy两种类型。本章主要介绍了基于VHDL的常见有限状态机的类型、结构、功能及表达方法,重点是如何有效地设计与实现。 学习要求:了解状态机的基本结构、功能和分类,掌握有限状态机的一般设计思路与方法、状态机编码方案的恰当选取、Moore和Mealy状态机的本质区别及设计实现。 关键词:状态机(State Machine),Moore,Mealy,VHDL设计(VHDL Design) 状态机的基本结构和功能 一般状态机的VHDL设计 状态机的一般组成 状态机的编码方案 摩尔状态机的VHDL设计 米立状态机的VHDL设计 状态机的基本结构和功能 状态机的基本结构如图所示。除了输人信号、输出信号外,状态机还包含一组寄存器记忆状态机的内部状态。状态机寄存器的下一个状态及输出,不仅同输入信号有关,而且还与寄存器的当前状态有关,状态机可以认为是组合逻辑和寄存器逻辑的特殊组合。它包括两个主要部分:即组合逻辑部分和寄存器。组合逻辑部分又可分为状态译码器和输出译码器,状态译码器确定状态机的下一个状态,即确定状态机的激励方程,输出译码器确定状态机的输出,即确定状态机的输出方程。寄存器用于存储状态机的内部状态。 状态机的基本操作有两种: 1.状态机的内部状态转换。 状态机经历一系列状态,下一状态由状态译码器根据当前状态和输入条件决定。2.产生输出信号序列。

c_中timer控件的使用

C#中Timer组件用法 Timer组件是也是一个WinForm组件了,和其他的WinForm组件的最大区别 是:Timer组件是不可见的,而其他大部分的组件都是都是可见的,可以设计的。Timer组件也被封装在名称空间System.Windows.Forms中,其主要作用是当Timer组件启动后,每隔一个固定时间段,触发相同的事件。Timer组件在程序设计中是一个比较常用的组件,虽然属性、事件都很少,但在有些地方使用它会产生意想不到的效果。 其实要使得程序的窗体飘动起来,其实思路是比较简单的。首先是当加载窗体的时候,给窗体设定一个显示的初始位置。然后通过在窗体中定义的二个Timer组件,其中一个叫Timer1,其作用是控制窗体从左往右飘动(当然如果你愿意,你也可以改为从上往下飘动,或者其他的飘动方式。),另外一个Timer2是控制窗体从右往左飘动(同样你也可以改为其他飘动方式)。当然这二个Timer 组件不能同时启动,在本文的程序中,是先设定Timer1组件启动的,当此Timer1启动后,每隔0.01秒,都会在触发的事件中给窗体的左上角的横坐标都加上"1",这时我们看到的结果是窗体从左往右不断移动,当移动到一定的位置后,Timer1停止。Timer2启动,每隔0.01秒,在触发定义的事件中给窗体的左上角的横坐标都减去"1",这时我们看到的结果是窗体从右往左不断移动。当移动到一定位置后,Timer1启动,Timer2停止,如此反覆,这样窗体也就飘动起来了。要实现上述思路,必须解决好以下问题。 (1).如何设定窗体的初始位置: 设定窗体的初始位置,是在事件Form1_Load()中进行的。此事件是当窗体加载的时候触发的。Form有一个DesktopLocation属性,这个属性是设定窗体的左上角的二维位置。在程序中是通过Point结构变量来设定此属性的值,具体如下: //设定窗体起初飘动的位置,位置为屏幕的坐标的(0,240) private void Form1_Load ( object sender , System.EventArgs e ) { Point p = new Point ( 0 , 240 ) ; this.DesktopLocation = p ; } (2). 如何实现窗体从左往右飘动: 设定Timer1的Interval值为"10",就是当Timer1启动后,每隔0.01秒触发的事件是Timer1_Tick(),在这个事件中编写给窗体左上角的横坐标不断加"1"的代码,就可以了,具体如下:

使用C#的Timer控件来实现定时触发事件

使用C#的Timer控件来实现定时触发事件 C# Timer用法有哪些呢?我们在使用C# Timer时都会有自己的一些总结,那么这里向你介绍3种方法,希望对你了解和学习C# Timer使用的方法有所帮助。 关于C# Timer类在C#里关于定时器类就有3个 C# Timer使用的方法1.定义在System.Windows.Forms里 C# Timer使用的方法2.定义在System.Threading.Timer类里" C# Timer使用的方法3.定义在System.Timers.Timer类里 下面我们来具体看看这3种C# Timer用法的解释: ◆System.Windows.Forms.Timer 应用于WinForm中的,它是通过Windows消息机制实现的,类似于VB或Delphi中的Timer 控件,内部使用API SetTimer实现的。它的主要缺点是计时不精确,而且必须有消息循环,Console Application(控制台应用程序)无法使用。 ◆System.Timers.Timer 和System.Threading.Timer非常类似,它们是通过.NET Thread Pool实现的,轻量,计时精确,对应用程序、消息没有特别的要求。 ◆System.Timers.Timer还可以应用于WinForm,完全取代上面的Timer控件。它们的缺点是不支持直接的拖放,需要手工编码。 C# Timer用法实例 使用System.Timers.Timer类 System.Timers.Timer t = new System.Timers.Timer(10000); //实例化Timer类,设置间隔时间为10000毫秒; t.Elapsed += new System.Timers.ElapsedEventHandler(theout); //到达时间的时候执行事件; t.AutoReset = true; //设置是执行一次(false)还是一直执行(true); t.Enabled = true; //是否执行System.Timers.Timer.Elapsed事件; public void theout( object source, System.Timers.ElapsedEventArgs e) { MessageBox.Show("OK!"); } C# Timer用法的基本情况就向你介绍到这里,希望对你了解和学习C# Timer使用有所帮助。详细参考:https://www.360docs.net/doc/7710873660.html,/zh-cn/library/vstudio/system.timers.timer.aspx

利用有限状态机进行时序逻辑的设计

利用有限状态机进行时序逻辑的设计 1. 实验目的: (1)掌握利用有限状态机实现一般时序逻辑分析的方法; (2)掌握用Verilog编写可综合的有限状态机的标准模板; (3)掌握用Verilog编写状态机模块的测试文件的一般方法。 (4)在数字电路中已经学习过通过建立有限状态机来进行数字逻辑的设计,而在VerilogHDL硬件描述语言中,这种设计方法得到进一步的发展。通过Verilog HDL提供的语句,可以直观的设计出更为复杂的时序逻辑的电路。关于有限状态机的设计方法在教材中已经作了较为详细的阐述。 2.实验环境 PC机一台,安装有quartusII13.0软件以及modulsim软件 3.实验内容 设计一个简单的状态机,功能是检测一个5位二进制序列“10010”。考虑到序列重叠的可能。有限状态机共提供8个状态(包括初始状态IDLE). 4.实验步骤 1) 源程序: module seqdet(x,z,clk,rst,state); input x,clk ,rst ;

output z; output [2:0] state ; reg[2:0] state ; wire z; parameter IDLE='d0, A='d1, B='d2, C='d3, D='d4, E='d5, F='d6, G='d7; assign z=(state == E && x==0)?1:0; always @(posedge clk) if(!rst) begin state <= IDLE; end else casex(state) IDLE:if(x==1)

有限状态机设计

实验七有限状态机设计 一、实验目的 1、掌握利用有限状态机实现一般时序逻辑分析的方法; 2、掌握用VHDL或Verilog编写可综合的有限状态机的标准模板; 3、掌握用VHDL或Verilog编写序列检测器以及其他复杂逻辑电路的设计; 二、实验内容 1、用MOORE型状态机设计一个具有双向步进电动机控制实验:该控制电路有三个输入信号:clk时钟信号,clr复位信号,dir方向控制信号。输出信号为phase[3..0]用来控制步进电机的动作。当dir=1时要求phase[3..0]按照“0001”,“0010”,“0100”,“1000”的顺序变化;当dir=0时要求phase[3..0]按照“0001”,“1000”,“0100”,“0010”的顺序变化。 2、设计一个简单的状态机,功能是检测一个5位的二进制序列“10010”。 3、设计一个串行数据检测器,要求是:连续4个或4个以上为1时输出为1,其他输入情况为0。(选做) 4、根据状态图,写出对应于结构图b,分别由主控组合进程和主控时序进程组成的VERILOG 有限状态机描述。(选做) 三、实验步骤 实验一: 1、建立工程

2、创建Verilog HDL文件 3、输入程序代码并保存 module moore1(clk,clr,dir,phase); input clk,clr,dir; output[3:0] phase; reg[3:0] phase; reg[1:0] state; parameter s0='b00,s1='b01,s2='b10,s3='b11; always@(posedge clk) begin if(clr)begin phase<='b0000;state<=s0;end else begin case(state) s0:if(dir) begin phase<='b0010;state<=s1;end else begin phase<='b1000;state<=s3;end s1:if(dir) begin phase<='b0100;state<=s2;end else begin phase<='b0001;state<=s0;end s2:if(dir) begin phase<='b1000;state<=s3;end

vb6.0时间控件timer详解

vb6.0时间控件timer详解 通过引发Timer 事件,Timer 控件可以有规律地隔一段时间执行一次代码。 语法 Timer 说明 Timer 控件用于背景进程中,它是不可见的 ************************以下是他的属性**************** Enabled 属性 返回或设置一个值,该值用来确定一个窗体或控件是否能够对用户产生的事件作出反应。 语法 object.Enabled [= boolean] Enabled 属性的语法包含下面部分: 部分描述 object 对象表达式,其值是“应用于”列表中的一个对象。如果object 被省略,则与活动窗体模块相联系的窗体被认为是object。 boolean 一个用来指定object 是否能够对用户产生的事件作出反应的布尔表达式。 设置 boolean 的设置为: 设置描述 True (缺省)允许object 对事件作出反应。 False 阻止object 对事件作出反应。 Enabled 属性示例 该例子使一个CommandButton 控件有效而不管TextBox 控件是否包含文本。要试用此例,先将下面的代码粘贴到带有CommandButton 和TextBox 控件的一个窗体的声明部分,然后按下F5 键并在文本框中随意输入一些内容。 Private Sub Form_Load () Text1.Text = "" ' 清除文本框的内容。

Command1.Caption = "Save" ' 在按钮上放置标题。 End Sub Private Sub Text1_Change () If Text1.Text = "" Then '查看文本框是否为空。 Command1.Enabled = False '使按钮无效。 Else Command1.Enabled = True '使按钮有效。 End If End Sub Interval 属性 返回或设置对Timer 控件的计时事件各调用间的毫秒数。 语法 object.Interval [= milliseconds] Interval 属性语法有以下组成部分: 部分描述 object 对象表达式,其值是“应用于”列表中的一个对象。 milliseconds 数值表达式,指定毫秒数,“设置值”中有详细说明,。 设置值 milliseconds 的设置值为: 设置值描述 0 (缺省值)使Timer 控件无效。 1 to 65,535 设置的时间间隔(以毫秒计),在Timer 控件Enabled 属性设置为True 时开始有效,例如,10,000 毫秒等于10 秒。最大值为65,535 毫秒,等于1 分钟多一些。 说明 可以在设计时或在运行时设置Timer 控件的Interval 属性。使用Interval 属性时,请记住: Timer 控件的Enabled 属性决定该控件是否对时间的推移做响应。将Enabled 设置为False 会关闭Timer 控件,设置为True 则打开它。当Timer 控件置为有效时,倒计时总是从其Interval 属性的设置值开始。 创建Timer 事件程序用以告诉Visual Basic 在每次Interval 到时该做什么。 Interval 属性示例

状态机设计仿真

状态机设计仿真 一、实验例题 设计一个序列检测器电路,检测出串行输入数据data中的二进制序列110,当检测到该序列时,电路输出1 out=;没有检测到该序列时,电路输出0,电路的状态图如1所示: 图1 电路状态转换图 二、实验原理分析 由电路的状态图分析,可列出对应的状态转换表,如图2所示: 图2 状态转换表 +相同,将图1,图2简化可得: 从状态转化表分析可得S3与S0对应的S n1

改进的状态转换表 三、实验任务:依据图1状态图2表,S 存在时,用VerilogHDL设计的参考程序如 3 下: module pulse_check(data,clk,rst,out); input data,clk,rst; output out; reg out; reg[1:0] CST,NST; parameter[1:0] s0=0,s1=1,s2=2,s3=3; always@(posedge clk or negedge rst) if (!rst) CST<=s0;//复位有效,进入下一个状态 else CST<=NST; always@(CST or data) begin case(CST) s0: if(data==1'b1) NST<=s1; else NST<=s0; s1: if(data==1'b1) NST<=s2; else NST<=s0; s2: if(data==1'b0) NST<=s3; else NST<=s2; s3: if(data==1'b0) NST<=s0; else NST<=s1;

default: NST<=s0; endcase end always@(CST or data) case(CST) s0:out=1'b0; s1:out=1'b0; s2: if(data==1'b0) out=1'b1; else out=1'b0; s3:out=1'b0; endcase endmodule rst复位信号(低电平有效),clk状态时钟。四:仿真图形

状态机设计总结

状态机设计 简介 状态机的设计被广泛地用于时序控制逻辑中,它是许多数字系统的核心。状态机可以应付众多应用场合的需求,覆盖宽范围的性能和复杂度;例如微处理器与VLSI外围接口的低级别控制,常规微处理器中的总线裁决和时序产生,定制的位片微处理器,数据加密和解密,传输协议等。 通常在设计周期中,控制逻辑的细节安排在最后处理,因为系统需求的改变和特征的增强会对其造成影响。对于控制逻辑设计,可编程逻辑是一个很宽松的解决方案,因为它允许简单的修改而不必扰乱PCB板布局。其灵活性提供了在不影响市场化时间的前提下,允许设计改动的机会。大多数带寄存器的PAL器件应用都是需要使用状态机设计技术的时序控制逻辑。随着技术的发展,新的高速、高性能的器件不断出现,它们简化了状态机设计的任务。对于状态机设计,宽范围的不同功能与性能的解决方案是可行的。在本次讨论中,我们将检验状态机执行的功能,它们在多种器件中的实现,以及它们的选择。 什么是状态机? 状态机是一个以有序的方式,遍历预定的状态序列的数字设备。状态是在电路的不同部分,测量到的一组数值。一个简单状态机可以由以下几部分构成:基于PAL器件的组合逻辑,输出寄存器和状态寄存器。这样一个序列发生器中的状态由状态寄存器和/或输出寄存器中所存储的值来决定。 状态机的通用形式可以用图1所示的设备来描述。除了这一设备的输入和输出,状态机还有两个必需的组成元件:组合逻辑和存储器(寄存器)。这类似于前面所讨论的带寄存器的记数器设计,它们本质上就是简单的状态机。存储器用来存储状态机的状态,组合逻辑可以看成两个截然不同的功能模块:下一状态解码器和输出解码器(图2)。当输出解码器产生实际的输出时,下一状态解码器决定状态机的下一状态。尽管它们执行截然不同的两个功能,但是它们通常被组合成如图1所示的组合逻辑阵列。 状态机的基本操作有两部分: 1、状态机遍历状态序列,下一状态解码器基于当前状态和输入条件来决定下一状态。

关于使用C#通过Timer控件实现自动播放图片的效果问题

关于使用C#通过Timer控件实现自动播放图片的效果问题 F1ake 4级被浏览52次 2013.04.23 using System; using System.Collections.Generic; using https://www.360docs.net/doc/7710873660.html,ponentModel; using System.Data; using System.Drawing; using System.Text; using System.Windows.Forms; namespace 第五章_work { public partial class Form1 : Form { public Form1() { InitializeComponent(); } int i = 0; private void picRight_Click(object sender, EventArgs e) { i--; if (i > -1) { picPicture.Image = ilImgList.Images[i]; } else { MessageBox.Show("已经是最后一张了","提示",MessageBoxButtons.OK,MessageBoxIcon.Excl amation); } } private void picLeft_Click(object sender, EventArgs e) { i++; if (i < 9)

{ picPicture.Image = ilImgList.Images[i]; } else { MessageBox.Show("已经是最后一张了", "提示", MessageBoxButtons.OK, MessageBoxIcon. Exclamation); } } private void Form1_Load(object sender, EventArgs e) { picPicture.Image = ilImgList.Images[0]; } private void picLook_Click(object sender, EventArgs e) { timer1.Enabled != timer1.Enabled; if (timer1.Enabled==true) { timer1.Start(); } else { timer1.Stop(); } } private void timer1_Tick(object sender, EventArgs e) { //if (count < ilImgList.Images.Count - 1) //{ // count++; //} //else //{

状态机设计

集成电路实验 状态机设计实验报告 专业:电子信息工程 姓名:江燕婷 学号:2011301200025

状态机设计(实验五)实验报告 一.实验目的 1. 掌握状态机设计的基本方法 2.学习利用状态机的方法实现控制电路 二.实验原理 有限状态机(Finite State Machine FSM)是时序电路设计中经常采用的一种方式,尤其适合设计数字系统的控制模块,在一些需要控制高速器件的场合,用状态机进行设计是一种很好的解决问题的方案,具有速度快、结构简单、可靠性高等优点。有限状态机非常适合用FPGA器件实现,用Verilog HDL的case 语句能很好地描述基于状态机的设计,再通过EDA工具软件的综合,一般可以生成性能极优的状态机电路,从而使其在执行时间、运行速度和占用资源等方面优于用CPU实现的方案。 有限状态机一般包括组合逻辑和寄存器逻辑两部分,寄存器逻辑用于存储状态,组合逻辑用于状态译码和产生输出信号。根据输出信号产生方法的不同,状态机可分为两类:米里型(Mealy)和摩尔型(Moore)。摩尔型状态机的输出只是当前状态的函数,如图1-1所示;米里型状态机的输出则是当前状态和当前输入的函数,如图1-2所示。米里型状态机的输出是在输入变化后立即变化的,不依赖时钟信号的同步,摩尔型状态机的输入发生变化时还需要等待时钟的到来,必须在状态发生变化时才会导致输出的变化,因此比米里型状态机要多等待一个时钟周期。 图1-1 摩尔型状态机图1-2 米里型状态机 状态机在硬件描述语言实现上,可使用单过程、双过程或三过程等不同的结构实现。状态机的状态实现上,可采用符号编码或显式数字编码。编码方式有顺序编码(自然二进制编码),一位热码(one-hot encoding),格雷(gray code)码等。顺序编码,简单状态寄存器占用少;一位热码输出译码电路简单;在状态顺序变化时,格雷码每次只有一位变化,避免产生输出信号毛刺。

利用有限状态机进行时序逻辑的设计

实验三利用有限状态机进行时序逻辑的设计 1.实验目的: (1)掌握利用有限状态机实现一般时序逻辑分析的方法; (2)掌握用Verilog编写可综合的有限状态机的标准模板; (3)掌握用Verilog编写状态机模块的测试文件的一般方法。 (4)在数字电路中已经学习过通过建立有限状态机来进行数字逻辑的设计,而在VerilogHDL硬件描述语言中,这种设计方法得到进一步的发展。通过Verilog HDL提供的语句,可以直观的设计出更为复杂的时序逻辑的电路。关于有限状态机的设计方法在教材中已经作了较为详细的阐述。 2.实验环境 PC机一台,安装有quartusII13.0软件以及modulsim软件 3.实验内容 设计一个简单的状态机,功能是检测一个5位二进制序列“10010”。考虑到序列重叠的可能。有限状态机共提供8个状态(包括初始状态IDLE). 4.实验步骤 1)源程序: module seqdet(x,z,clk,rst,state); input x,clk ,rst ; output z; output [2:0] state ; reg[2:0] state ; wire z; parameter IDLE='d0, A='d1, B='d2, C='d3, D='d4, E='d5, F='d6, G='d7; assign z=(state == E && x==0)?1:0; always @(posedge clk) if(!rst) begin state <= IDLE; end else casex(state) IDLE:if(x==1) begin state <= A; end A: if(x==0) begin state <= B; end B: if(x==0) begin state <= C; end else begin state <= F; end C: if(x==1) begin state <= D; end else begin