第2章 逻辑门电路

数电讲义--2章

1.0

VOL(max)0.5

输入标 准低电

平

0.4V

VNL

D VNH

E

V V 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

SL VOFF VON

SH

Vi (V)

输入标准

高电平

2. 输入特性

+VCC

1) 输入伏安特性

iI

R1 3kΩ

1

-1.6 mA

<50 uA vI A

31

B

T1

1.4 V

和边沿,T4放大。 VO随iOH变化不大。 当由i于Oi以OHH受↑:线时功性,R耗变4上的化压限。降制增,大i0,H过T大3 、会T4烧饱毁和T,4管V,O随所

功耗 1mW IOH 400 A

输出高电平时的扇出系数 3.6V

R2 750Ω 2T3 Vc2 1 3 R4

VO

+VCC

R 4 +5V 100Ω

抗干扰能力越强。 高电平噪声容限

VNH= VSH ¯ VON 。

VNH越大,输入为1态下

抗干扰能力越强。

Vo (V)

4.0 A B

3.5

3.0

VOH(min)2.5 2.4V

C

2.0

1.5

A(0V, 3. 6V) B(0.6V, 3.6V) C(1.3V, 2.48V) D(1.4V, 0.3V) E(3.6V, 0.3V)

• 导通(VD>VTH) • 2、二极管的开关时间

截止5V(VDR<VT+H)

0V

D VD

uo

_

VF Vi

二极管开关状态的转换需要时间:

t1 t2

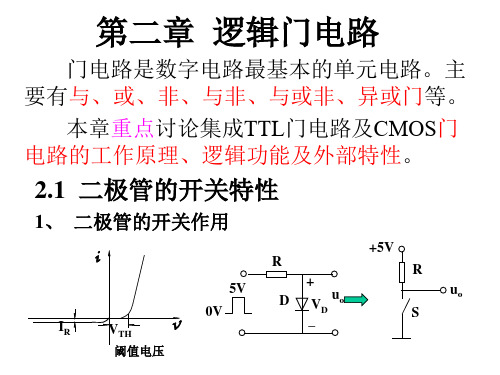

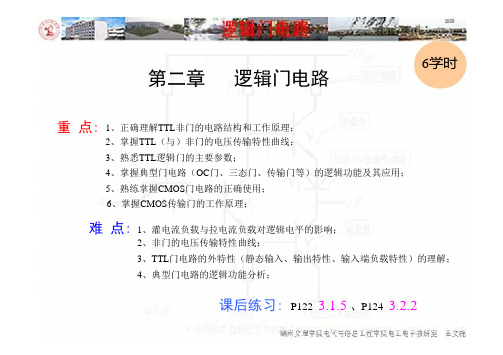

第二章逻辑门电路

B

+V’CC RL

A B

&

线与

F A BC D

C

D

& CD

+V’CC RL & &

RL

构成总线输出

:多个逻辑门分时段

&

1

总线负载

共用同一条输出线

20

2.5.6

三态门

VT3

三态门符号 +VCC

VT4 VT2

A B EN

&

EN

VT1

A B EN

D

A B EN

F

VT5

vi vi vo

tpd tpd

vo

应大于tpd ,输出信号vo才能 完成响应。 如输入脉宽小于tpd ,则输出vo 不能产生完整响应,vo会保持 在原电平上基本不变。

(对称方波)

fmax=1/(2tpd)

fmax :

3

传输延迟的仿真

由仿真知, 门延迟 tpd 150nS. 见

vi

25KHz

20uS

IIS IIS 。 1.4mA。

VCC VB1 R1

IIS

vI /V

1.4V

-0.5

IIS

-1.0 -1.5 -2.0

1V

I IS

3K IIS

R1

VCC

vB1

VT2 R3

VO=VOH

VT5

&

IIS

11

或非门(或门) 输入端有多个并接时:

并接接地时, 每个输入端流出电流IIS

IIS

A A•B=A+B VCC

-2~ -1.5V : VIL

第02章 逻辑门电路

OC门的几种主要应用

实现线与逻辑

电路如右图所示,逻辑关系为

L L1 L2 AB CD

实现电平转换

如下图所示,可使输出高电平变为+12V

+12V

R

A& 3.4V 0.3V

12V F

0.3V

用作驱动电路

右图是用来驱动发光二极管的电路。

2.3.5 三态门

R1 4K

R2 1.6K

A

T1

T2 B

输出低电平时:NOL = IOLmax / IiLmax 输出高电平时:NOH = IOHmax / IiHmax

考虑最坏的情况,扇出系数:N = min(NL , NH)

TTL与非门的灌电流与拉电流负载

2.3.2 TTL与非门的特性及参数

平均传输延迟时间

tpd = 0.5(tpdL + tpdH ) 输出信号略滞后于输入信号. 典型值:纳秒级

Vo(V) VOH A 2.7

电压传输特性及相关参数 (1) 输出高电平 VOH

R1 4K

R2 1.6K

R4

VCC

130

A

B

B

T1

T3

T2

ቤተ መጻሕፍቲ ባይዱ

D3

F

D1

D2

R3

T4

1K

典型值VOH ≥ 3.4V

VOHmin是满足输出电流指标时, 输出高电平允许的最低值,一 般要求 VOHmin ≥ 2.7V

C

(2) 输出低电平 VOL

(5) 关门电平 VOFF

保证T4截止 输出高电平 时, 输入低电平的最大值.

VOFF ≥ 0.8V

2.3.2 TTL与非门的特性及参数

第2章集成逻辑门电路

2.3.2

TTL集电极开路门

TTL集电极开路门(Open Collector Gate)也称为OC门。 在用门电路组成逻辑电路时,如果能将输出端直接并联(称为 “线与”逻辑),可以使电路简化许多。前面所介绍的TTL与非 门却不能这样使用,原因有两个:一是TTL与非门无论输出为高 电平还是低电平,输出电阻都很小;二是两个TTL与非门连在一 起以后,如果一个门输出为高电平,另一个输出为低电平,那么 会有很大的电流从截止门的三极管VT4流到导通门的三极管VT5, 此电流大大超过正常工作电流,严重时会损坏门电路。解决的办 法是把TTL与非门电路的输出级改为集电极开路的三极管结构,

图2.25

二极管的开关电路特性

2.双极型三极管的开关特性 双极型三极管的输出特性曲线如图2.26所示。由输出特性曲线 可知,三极管可分为三个区域:截止区、放大区和饱和区。特别 当三极管工作在截止区和饱和区时,电参数也表现为对立的两个 状态,可以作为开关使用。

图2.26

三极管的输出特性曲线

2.2

晶体二极管和三极管的开关特性

第一个字母C代表中国,T代表TTL;它们对应型号的门电路逻辑 功能和引脚图与国际标准基本是一样的。本书电路举例将以最常 用的74XX系列和74LSXX系列门电路为主。本章讨论的集成逻辑门 属于小规模集成电路(SSI)。

2.3.1

TTL与非门电路

1.电路结构 每个系列的TTL与非门基本都是由输入级、中间级(倒相级) 和输出级组成。图2.30为TTL与非门的基本电路。 输入级通常由多发射极晶体三极管组成,如图中VT1。我们可 以把VT1看成是发射极独立而基极和集电极分别并联在一起的三 极管。输入级完成“与”逻辑功能。 中间级由VT2组成,其集电极和发射极输出的信号相位相反。 由这两个相位相反的信号去控制输出级的VT3和VT5,所以中间级 也称倒相级。 输出级由VT3、VT4和VT5组成,采用推拉式结构。其中VT3、

第二章 逻辑门电路

• (2)放大状态:当VI为正值且大于死区电压时,三极 管导通。有 V V V

IB

I BE

Rb

I

Rb

• 此时,若调节Rb↓,则IB↑,IC↑,VCE↓,工作点沿着负 载线由A点→B点→C点→D点向上移动。在此期间,三极管 工作在放大区, 其特点为: IC=βIB。 • 三极管工作在放大状态的条件为: 发射结正偏,集电结反偏

VIL VOL

VNL

0

4、扇入与扇出数: 1)扇入数: 取决于它的输入端的个数。 2)扇出数: MIN (NOH, NOL)

拉电流工作情况: 输出为高电平时,与 非门带拉电流负载

N OH

I OH (驱动门) I IH (负载门)

0 1

4

IIH II

L

输出为低电平时,与 灌电流工作情况: 非门带灌电流负载

0

T3 通

该与非门输 出低电平, 门 2 T3导通

集电极开路TTL“与非”门(OC门)

OC门的结构

当输入端全为高电 VCC 逻辑符号: 平时,T2、T3导通, A A A R 输出为低电平; L B B B 输入端有一个为 低 电 平 时 , T2 、 输出逻辑电平: T3 截 止 , 输 出 高 低电平0.3V 电 平 接 近 电 源 电 (5-30V) TTL与非门 高电平为VC 压VC。 OC门完成 集电极开路与非门(OC门) “与非”逻辑功 能

§2.3

CC

基本逻辑门电路

真值表

一、二极管“与门”及“或门”电路 A V (5V) 1、与门电路: 0 0 R 3k 0 A 1 L 1 B 1 C 1

A,B,C 任一为0V,其中一个 二极管导通,VL被钳制在0.7V

第2章 逻辑门电路

+VCC Rb b c Rc

uo=0.3V 0.3V

b c

Rc

uo=+VCC ui=UIH

iB≥IBS 0.7V

e

e

+V C C =+5V 例: 1kR c i C Ω uo c Rb b ui β =40 i 10k Ω B e

①ui=1V时,基极电流: 时 基极电流:

第2章 逻辑门电路 章

②ui=0.3V时,因为 BE<0.5V,iB=0, 时 因为u , , 三极管工作在截止状态, 三极管工作在截止状态,ic=0。因 。 为ic=0,所以输出电压: ,所以输出电压:

回首页

第2章 逻辑门电路 章 +VCC=+5V Rc

1kΩ uo c Rb b ui β=40 i 10kΩ B NPN 型三极管截止、放大、饱和 3 种工作状态的特点 e

iC

2、三极管的开关特性

工作状态 条 件

截

止

放

大

饱

和

iB=0 发射结反偏

0<iB<IBS 发射结正偏 集电结反偏 uBE>0,uBC<0 iC=βiB uCE=VCC- iCRc 可变

A

电路图 逻辑符号

Y 1 0

0 1

第二章 逻辑门电路

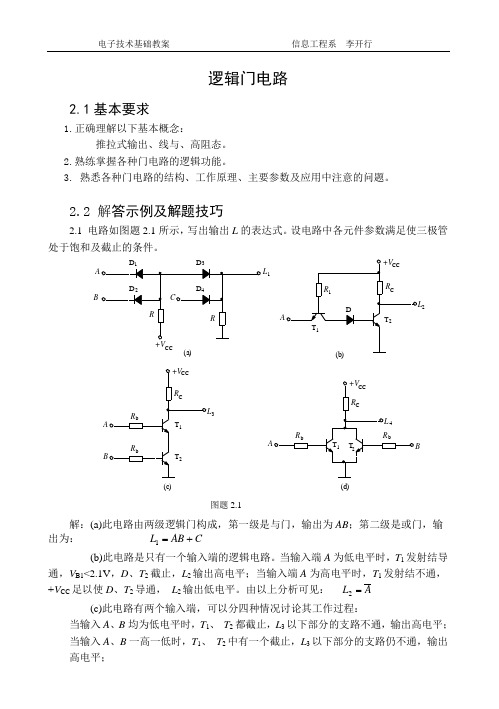

电子技术基础教案 信息工程系 李开行逻辑门电路2.1基本要求1.正确理解以下基本概念:推拉式输出、线与、高阻态。

2.熟练掌握各种门电路的逻辑功能。

3. 熟悉各种门电路的结构、工作原理、主要参数及应用中注意的问题。

2.2 解答示例及解题技巧2.1 电路如图题2.1所示,写出输出L 的表达式。

设电路中各元件参数满足使三极管处于饱和及截止的条件。

BL D D (a)CC(c)1233(d)图题2.1解:(a)此电路由两级逻辑门构成,第一级是与门,输出为AB ;第二级是或门,输出为: C AB L +=1(b)此电路是只有一个输入端的逻辑电路。

当输入端A 为低电平时,T 1发射结导通,V B1<2.1V ,D 、T 2截止,L 2输出高电平;当输入端A 为高电平时,T 1发射结不通,+V CC 足以使D 、T 2导通, L 2输出低电平。

由以上分析可见: A L =2(c)此电路有两个输入端,可以分四种情况讨论其工作过程:当输入A 、B 均为低电平时,T 1、 T 2都截止,L 3以下部分的支路不通,输出高电平; 当输入A 、B 一高一低时,T 1、 T 2中有一个截止,L 3以下部分的支路仍不通,输出高电平;当输入A 、B 均为高电平时,T 1、 T 2都饱和导通,L 3以下部分的支路导通,输出低电平。

根据以上分析可以列出真值表如表2.1(a )。

由真值表可得表达式:AB B A B A B A L =++=3(d) 此电路有两个输入端,可以分四种情况讨论其工作过程:当输入A 、B 均为低电平时,T 1、 T 2都截止,L 4以下部分的支路不通,输出高电平; 当输入A 、B 一高一低时,T 1、 T 2中有一个饱和导通,L 3以下部分的支路导通,输出低电平;当输入A 、B 均为高电平时,T 1、 T 2都饱和导通,L 3以下部分的支路导通,输出低电平。

根据以上分析可以列出真值表如表2.1(b )。

第2章 逻辑门电路

20102010-9-14

2.1.1 非门

定义:输入与输出信号状态满足“ 定义:输入与输出信号状态满足“非”逻辑关系。 逻辑关系。 逻辑符号: 逻辑符号: 非门电路: 非门波形图: 非门电路: 非门波形图:

非门工作特点: 非门工作特点: ● 当输入端A 为高电平1(+5V)时,晶体管 当输入端A 为高电平1 +5V) 导通, 端输出0.2~0.3V的电压 的电压, 导通,L 端输出0.2~0.3V的电压,属于低电平 范围; 范围; ● 当输入端为低电平0(0V)时,晶体管截止,晶体管集电 当输入端为低电平0 0V) 晶体管截止, 发射极间呈高阻状态,输出端L的电压近似等于电源电压; 极—发射极间呈高阻状态,输出端L的电压近似等于电源电压; ● 任何能够实现 L = A “非”逻辑关系的电路均称为“非门”, 逻辑关系的电路均称为“非门” 也称为反相器。式中的符号“ 表示取反, 也称为反相器。式中的符号“-”表示取反,在其逻辑符号的输出 端用一个小圆圈来表示。 端用一个小圆圈来表示。

同或门电路: 同或门电路:

逻辑符号: 逻辑符号:

提

示

双输入端同或门波形图: 双输入端同或门波形图:

当输入端A 当输入端A、B 的电平 状态互为相反时,输出端L 状态互为相反时,输出端L 一定为低电平; 一定为低电平;而当输入端 A、B 的电平状态相同时, 的电平状态相同时, 一定为高电平。 输出端 L 一定为高电平。

20102010-9-14

第二章(1) 第二章(

3

2.1.2 与门

定义:输入与输出信号状态满足“ 定义:输入与输出信号状态满足“与”逻辑关系。 逻辑关系。 与门电路: 逻辑符号: 与门波形图: 与门电路: 逻辑符号: 与门波形图:

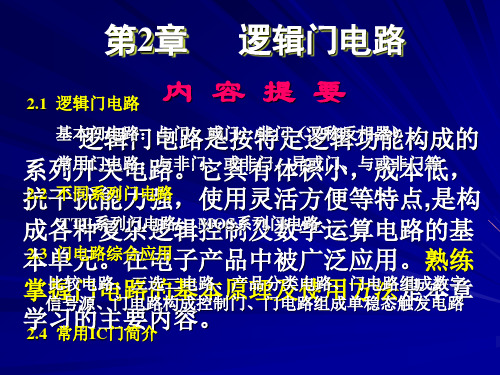

第2章逻辑门电路-PPT精选

逻辑门:完成一些基本逻辑功能的电子电路。现使用的 主要为集成逻辑门。

首先介绍晶体管的开关特性 着重讨论的TTL和CMOS门电路的

逻辑功能和电气特性

简要介绍其他类型的双极型和MOS门电路

2.1 晶体管的开关特性 在数字电路中,常将半导体二极管,三极管和场效应管

作 为开关元件使用。 理想开关: 接通时阻抗为零;断开时阻抗为无穷大;

1

VO

1

VI

VO 1输出 VOHmin

VNH VIHmin

0输出

VILman VNL

VOLman

VI

1输入 1输入

2.3.3 TTL与非门的静态输入与输出特性

1. 输入特性

1)输入伏安特性( II=f(Vi) ) 定义:电流流入T1的发射极

方向为正方向。

II(mA)

高电平输入

0.5 1.0 1.5 2.1 0

1.0

-15 -10 -5 0 5 10 15 I0(mA)

负载门的管脚的个数,即

IH=NIIH (IIH为负载门高电平输入电流,约为40μA左

右)

从曲线上看,当IO大于5mA时,VO才开始出现下降趋势, 但决定IOHmax值的并不是VOHmax,而是器件的功耗。在上 面讨论的电路中, IOHmax约为400mA。

在门输入端和地之间接电阻Ri,当电阻从0Ω逐步增加

时,由于电阻内部有电流流过,会使电阻两端电压Vi逐步

增加。

VCC

当T1管饱和导通时: Vi R1R iRi(VCC VB1E)

R1

4kΩ

T1

Roff≈0.9kΩ, Ron≈3kΩ。

Vi

Ri

当Ri小于R0ff时,输入为低 电平;当Ri高于Ron时,输入 为高电平。

第2章门电路

低电平≤0.7V。 又如,TTL电路中,通常规定高电平的额定值为

3V,但从2V到5V都算高电平;低电平的额定值为0.3V, 但从0V到0.8V都算作低电平。

2. 逻辑状态赋值 在数字电路中,用逻辑0和逻辑1分别表示输入、

输出高电平和低电平的过程称为逻辑赋值。 经过逻辑赋值之后可以得到逻辑电路的真值表,

3.6V

(3) 采用推拉式输出级利于提高开关速度和负载能力

VT3组成射极输出器,优点是既能提高开关速度, 又能提高负载能力。

当输入高电平时,VT4饱和, uB3=uC2=0.3V+0.7V=1V,VT3和VD截止,VT4的集电 极电流可以全部用来驱动负载。

当输入低电平时,VT4截止,VT3导通(为射极输 出器),其输出电阻很小,带负载能力很强。

(5) 阈值电压UTH 电压传输特性曲线转折区中点所对应的uI值称为阈 值电压UTH(又称门槛电平)。通常UTH≈1.4V。

(6) 噪声容限( UNL和UNH ) 噪声容限也称抗干扰能力,它反映门电路在多大 的干扰电压下仍能正常工作。 UNL和UNH越大,电路的抗干扰能力越强。

UIL UNL UOFF UON UNH UIH

2、 动态特性:开通时间 ton = 0 关断时间 toff = 0

客观世界中,没有理想开关。 乒乓开关、继电器、接触器等的静态特性十分 接近理想开关,但动态特性很差,无法满足数字电 路一秒钟开关几百万次乃至数千万次的需要。 半导体二极管、三极管和MOS管做为开关使用 时,其静态特性不如机械开关,但动态特性很好。

逻辑变量←→两状态开关: 在逻辑代数中逻辑变量有两种取值:0和1; 电子开关有两种状态:闭合、断开。

第2章-逻辑门电路

高速,可代替74HC

高速,可代替74HCT

2.4.1.MOS反相器

2. MOS反相器

(1)电阻负载MOS电路:

如图2-37(a)所示,在这种反相器 中,输入器件是增强型MOS管,负载是线性 电阻。这种反相器在集成电路中很少采用。

(2)E/E MOS(Enhancement/Enhancement MOS) 反相器:

2.三态输出门电路(TSL门) 图227 三态门

三态输出门电路简称三态门,用 TSL(Three Sate Logic)表示,TSL电路的 主要特点是输出共有3种状态,即逻辑高电 平、逻辑低电平和高阻态。

图2-27所示为三态门电路及逻辑符号。 图中EN为三态使能端,A、B为输入逻辑变 量,Y为电路输出。

74F

速度比标准系列快近5倍, 功耗低于标准系列

2.2.1.TTL与非门的典型电路 及工作原理

1. 电路结构

电路由输入级、中间级和输出级三部 分组成。

2. 基本工作原理

(1)TTL工作在关态(截止态)

当输入信号A、B、C中少一个为低电 位(0.3V)时:

VO = VOH = VCC – VR2 – VBE3 – VD4 =5V-0.7V-0.7V =3.6V

实现了输出高电平,此时TTL工作在关 态,也称截止态。

(2)TTL工作在开态(饱和态)

输出电压Vo为

VO = VOL = VCES4 = 0.3V 实现了输出低电平,此时TTL工作在开 态,也称饱和态。

通过以上分析可知,当输入信号中至 少一个为低电位,即VI=ABC= VIL时,输出 高电平,即VO = VOH ;当输入信号全部为 高电位时,即VI=ABC= VIH时,输出低电平, 即VO = VOL。说明电路实现了与非门的逻辑 关系,即

第2章 逻辑门电路

A

1

≥1

B1

VDD R

A&

TP

Y B

Y

TN Y

TN

VOH=VDD'- iLR

2.1.6 CMOS漏极开路门

4.OD门和OC门的应用 应用一:可以线与,简化硬件电路。

+5V

A

&

B

C

&

D

R L

L AB CD

2.1.6 CMOS漏极开路门

线与的实际应用实例——光电报警系统

光电传 1

+5V

R3kCΩ VT5

VT6

A

&

F

B

OC 门

A

&

L

B

2.2.2 LSTTL与非门

集成与非门—74LS00

74LS00是在一个封装内有四个相同的与非门。其外形 如图所示。

绝大多数 左上角Vcc

引线排列从左下角 开始,逆时针计算

14

8

正视图

VCC

&

&

缺口标记

&

&

GND

绝大多数

右下角GND

1

7

2.2.3 LSTTL门电路的电气特性

CMOS门电路几种常见系列: (1)CD4000系列:基本系列,速度较慢 (2)74HC系列:速度比CD4000系列提高近10倍 (3)74HCT系列:与LSTTL门电路兼容 (4)LVC系列:低电压系列

TTL集电极开路门 OC 门Open-Collector

A B

VD5

R1 20kΩ VD1

VD2 VD6

2.2.2 LSTTL与非门

电子技术基础数字部分第二章逻辑门电路经典课件

V5

A

V1

V2

F 输出管

V3

R2

输入级

中间级 (推拉式)输出级

(中间放大且驱动互补输出)

(1)A=1时,V1管处于发射结与集电结倒置使用放大状态,V2、V3导通,V4截止,有F=0;

VCC

+2.5V

高电平箝位电路提高输出的正向抗干扰能 力;(低电平输入时正向波动导致V导通,

但只要仍有IQ的存在即VZ导通,仍可以保证 高电平输出)

加速电容

A

提高低电平输入的 正向抗干扰能力

IRC RC

VZ

IQ

Cb

F

Rb

V

R' VCC

饱和的深度提高高电平输入时的负向抗干扰能力; 但饱和深度又降低了开关速度,增加了电路损耗;

1、逻辑非:某件事物发生的条件与结果相反的逻辑关系。 2、非门:实现逻辑非运算,且单端输入单端输出的电路。

3、BJT非逻辑电路基本结构及工作原理

VCC

Rb

A

RC

V

F

电位表

VA VF V 0V 5V 止 5V 0.3V 通

4、非门符号

1

A

F

实现了非 逻辑功能

真值表

AF 01 10

5、BJT非逻辑电路改进

CMOS负载

V OH(min)/V TTL负载

CMOS负载

V OL(max)/V TTL负载

VDD/VCC/V tpd/ns PD/mW NO VNH/V VNL/V

CMOS

74HC 74HCT

0.001 -0.001 -0.02

-4

0.001 -0.001 -0.02

-4

0.02

第2章 逻辑门电路

等式两边的真值表如表1.3所示: 等式两边的真值表如表1.3所示: 1.3所示

A

0 0 1 1

B

0 1 0 1

A⋅ B

1 1 1 0

A+ B

1 1 1 0

2. 常用公式

利用上面的公理、定律、规则可以得到一些常用的公式。 利用上面的公理、定律、规则可以得到一些常用的公式。

(1)吸收律

A+A·B = A

工作原理 请自行分析

◆ 多变量的函数表达式

● ● ● ● ●

与 或 与非 或非

F=A·B·C… F=A+B+C…

F = A⋅ B ⋅C

F = A+ B +C

等等 ◆ 运算的优先级别

与或非 F = AB + CD

括号→非运算→与运算→ 括号→非运算→与运算→或运算

2.3 逻辑变量与逻辑函数

F=A+B

当输入端A 当输入端A、B 的电平 状态互为相反时,输出端L 状态互为相反时,输出端L 一定为高电平;当输入端A 一定为高电平;当输入端A、 B的电平状态相同时输出L 的电平状态相同时输出L 一定为低电平。 一定为低电平。

4. 同或门

◆ 能够实现 同或” L = A ⋅ B + A ⋅ B = A⊙B “同或”逻辑关系的 电路均称为“同或门” 由非门、 电路均称为“同或门”。由非门、与门和或门组合而成的同或门 及逻辑符号如下图所示。 及逻辑符号如下图所示。

F = A ⋅ B ⋅C ⋅ D ⋅ E

1. 要保持原式中逻辑运算的优先顺序; 保持原式中逻辑运算的优先顺序; 原式中逻辑运算的优先顺序 2. 不是一个变量上的反号应保持不变,否则就要出错。 不是一个变量上的反号应保持不变,否则就要出错。 上的反号应保持不变

第2章 逻辑门电路

R2 T3

VCC R5 IR5 T4 IL

RL

VO (V )

3

2

1

0

5 10 15 20 IL (mA)

低电平输出电流

V CC

T2

RL

VO (V )

T5

IL

3

2

R3

1

0.2

5 10 15 20 IL (mA )

例2.5.1:门电路的输入特性曲线和输出特性曲线 分别由图2.5.4、图2.5.8、图2.5.9给出。对于 图2.5.10所示的电路,要求G1的输出高电平满 足VOH≥3.2V,输出低电平满足VOL≤0.2V。

C

VEE

VEE

(b)

F2 =A+B+B+C+D=A+B+BC D

F3 =B +C +D F4 = A+B+BC+BC= AB+BC+BC

F5=A+B+BC+BC=A+BC+BC

2.7 MOS管的开关特性 2.7.1 MOS管的开关特性

结构示意图,符号:N沟道MOS管

SG D

N+

N+

P

D G

S

漏极特性和转移特性

&

VIL

nm

m'

... ...

VIL

&

&

I IL

&

2.5.6 三态门

VCC

R1

R2

T3

R5

A

T4

T1

T2

F

B

EN

D

T5

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Y=A

§2.4 TTL逻辑门电路 逻辑门电路

1、TTL与非门 与非门

+VCC(+5V) R1 3kΩ A B T1 R2 750Ω T2 R3 360Ω R5 3kΩ R4 100Ω T3 T4 T5

+VCC(+5V) Y

A D1 D2 R1 3kΩ b1 D3 c1

B

TTL 与非门电路

T1 的等效电路

Y

T5

74LS04 1 2 3 4 5 6 7

1A 1Y 2A 2Y 3A 3Y GND TTL 反相器电路 6 反相器 74LS04 的引脚排列图

截止, 导通, ①A=0时,T2、T5截止,T3、T4导通,Y=1。 时 。 导通, 截止, ②A=1时,T2、T5导通,T3、T4截止,Y=0。 时 。

+VCC(+5V) R1 3kΩ 2.1V

3.6V A 3.6V B

R2 750Ω + T2 0.3V T3

R4 100Ω T4

T1 + 0.7V R3 360Ω

+T 5 + R5 0.3V 0.7V 3kΩ - -

Y

②输入信号全为1:如uA=uB=3.6V 输入信号全为 : 导通, 则uB1=2.1V,T2、T5导通,T3、T4截止 , 输出端的电位为: 输出端的电位为: uY=UCES=0.3V 输出Y为低电平。 输出 为低电平。 为低电平

中只要有一个为1,即高电平, 就会经过T ①A、B中只要有一个为 ,即高电平,如A=1,则iB1就会经过 1集 、 中只要有一个为 = , 电结流入T 基极, 饱和导通,输出为低电平, 电结流入 2基极,使T2、T5饱和导通,输出为低电平,即Y=0。 = 。 均分别流入T 发射极, ②A=B=0时,iB1、i'B1均分别流入 1、T'1发射极,使T2、T'2、T5 = = 时 均截止, 导通,输出为高电平, 均截止,T3、T4导通,输出为高电平,即Y=1。 = 。

⑵ 中规模集成电路 MSI : 集成度:10≤~ ≤99门/片、 100 ≤~ ≤999元器件/片 如译码器、计数器、寄存器等逻辑功能部件。 ⑶ 大规模集成电路 LSI : 集成度:100≤~ ≤1000门/片、1000 ≤~ ≤10000元器 件/片。 如CPU、存储器、简单的数字逻辑系统等。 ⑷ 超大规模集成电路 VLSI 集成度: ≥1000门/片、 ≥ 10000元器件/片。 如单片机、数字逻辑系统等。

⑵单极型:也称场效应管 单极型: 场效应管 可分为结型的 结型的(JFET)和绝缘栅的 绝缘栅的(IGFET),即MOS管。 结型的 绝缘栅的 MOS又分PMOS、 NMOS、CMOS。 在LSI 和VLSI 中,MOS 型以其集成度高和工艺简 单,获得了青睐。 2. 按集成度分类 按集成度分类——小规模集成电路 小规模集成电路SSI 小规模集成电路 中规模集成电路MSI 中规模集成电路 大规模集成电路LSI 大规模集成电路 超大规模集成电路VLSI 超大规模集成电路 ⑴ 小规模集成电路 SSI : 集成度≤10门/片、 ≤ 100元器件/片, 如逻辑门或 触发器等。

uo=uCE=UCC-iCRc=5-1.5×1=3.5V

§2.3 基本逻辑门电路

1、二极管与门

+VCC(+5V) R 3kΩ

A

0 0 1 1

B

0 1 0 1

Y

0 0 0 1

5V

D1 A D2 B

Y

0V

uA uB

0V 0V 0V 5V 5V 0V 5V 5V

uY

0.7V 0.7V 0.7V 5V

D1 D2 导通 导通 导通 截止 截止 导通 截止 截止

+VCC(+5V) R1 3kΩ

1V 0.3V A 3.6V B

R2 750Ω + T2 0.7V R3 360Ω

R4 100Ω T3 T4 + 0.7VT5

T1

Y

R5 3kΩ

①输入信号不全为1:如uA=0.3V, uB=3.6V 输入信号不全为 : , 截止, 则uB1=0.3+0.7=1V,T2、T5截止,T3、T4导通 , 忽略i 输出端的电位为: 忽略 B3,输出端的电位为: uY≈5―0.7―0.7=3.6V 输出Y为高电平。 输出 为高电平。 为高电平

e

0 工作原理电路 0.5

uBE(V)

0

UCES

VCC 输出特性曲线

uCE(V)

输入特性曲线

+VCC Rb ui=UIL<0.5V e b c Rc uo=+VCC

和 Rb ui=UIH iB≥IBS

0.7V

+VCC b c Rc uo=0.3V

0.3V

e

ui

+V C C =+5V Rc iC 1k Ω uo c Rb b β =40 i 10k Ω B e

1、二极管的开关特性 + uD - 正极 二极管符号: 负极

Ui<0.5V时,二 I F 极管截止,iD=0。

U BR

i D ( mA)

D + ui - 开关电路

D + + - ui =5V 0.7V RL - + u uoo -

0

0.5 0.7

u D (V)

RL

+ uo -

伏安特性

Ui>0.5V时, 二极管导通

Y = A

TTL或非门

+VCC R1 T1 R'1 B T '1 T '2 TTL 或非门电路 R2 T3 A T2 R3 R5 T4 R4 VCC 3Y 3B 3A 4Y 4B 4A 14 13 12 11 10 9 8

Y

T5 1 2 3

74LS02 4 5 6 7

1Y 1B 1A 2Y 2B 3A GND 74LS02 的引脚排列图

74LS00 的引脚排列图

74LS00内含4个2输入与非门, 74LS20内含2个4输入与非门。

非门、 2、TTL非门、或非门、与或非门 非门 或非门、 TTL非门

+VCC R1 3kΩ A T1 R2 750Ω T3 T2 R3 360Ω R5 3kΩ T4 R4 100Ω VCC 4A 4Y 5A 5Y 6A 6Y 14 13 12 11 10 9 8

2、三极管的开关特性

NPN 型三极管截止、放大、饱和 3 种工作状态的特点 工作状态 条 件 偏置情况 工 作 特 点 集电极电流 ce 间电压 ce 间等效电阻 截 止 放 大 饱 和

iB=0 发射结反偏 集电结反偏 uBE<0,uBC<0 iC=0 uCE=VCC 很大, 相当开关断开

0<iB<IBS 发射结正偏 集电结反偏 uBE>0,uBC<0 iC=βiB uCE=VCC- iCRc 可变

数字电子技术基础

第2章 逻辑门电路 章

基本逻辑门电路

一、逻辑门电路的分类

1. 按基本结构分类——双极型逻辑门 双极型逻辑门 按基本结构分类 单极型逻辑门 双极型BJT: ⑴ 双极型 : 按其结构再细分为 PNP 型和 NPN 型; 构成的集成逻辑门电路有 TTL 逻辑门、ECL 逻 辑门、HTL 逻辑门。 其中:TTL集成逻辑门应用的最广泛,由于它的 输入输出都采用三极管构成,也称晶体管 晶体管 晶体管—晶体管 晶体管 逻辑门电路,简称TTL逻辑门。

5V 5V

3、三极管非门

+5V

1k Ω 4.3k Ω

三极管临界饱和 时的基极电流为: 时的基极电流为:

I BS = 5 − 0.3 = 0.16mA 30 × 1

Y β=40 A 1

A

Y

iB>IBS,三极管工作 在饱和状态。 在饱和状态。输出电 压uY=UCES=0.3V。 。

电路图

逻辑符号

A 0 1

3. 常用门电路型号

SN54/74系列 系列

1. 54系列 系列——军用型:尺寸小、功耗小、可靠性 系列 高、工作温度范围大(-55℃~+125 ℃)。 2. 74系列 系列——民用型,低成本改进型,在一般场 系列 合下使用,工作温度(0℃~+70 ℃) 常用集成电路规格一览表

类型 普通型 高速型 低功耗型 超高速型 低功耗超高速型 名称 74 74H 74L 74S 74LS 时延ns 10 6 33 3 9.5 功耗mv 10 22 1 19 2 速度功耗乘积ps 100 132 33 57 19

Y=AB

A B

&

Y

2、二极管或门

5V A D1 0V B D2 R Y

A

0 0 1 1

B

0 1 0 1

Y

0 1 1 1

3kΩ

uA uB

0V 0V 5V 0V 5V 0V

uY

0V 4 .3 V 4 .3 V 4 .3 V

D1 D2 截止 截止 截止 导通 导通 截止 导通 导通

Y=A+B

A B

≥1

Y

iB>IBS 发射结正偏 集电结正偏 uBE>0,uBC>0 iC=ICS uCE=UCES= 0.3V 很小, 相当开关闭合

Rc Rb

b iB

+VCC iC uo c

iB(μA)

iC (mA)

饱 和 区

VCC Rc

直流负载线 Q2 Q

80μA 60μA 40μA 20μA Q1 i =0 B

ui

Y = A+ B

TTL与或非门

+VCC R1 T1 R'1 T '1 T '2 R2 T3 A B T2 R3 R5 T4 Y T5 1 2 3 74LS51 4 5 6 7 R4 VCC 2B 2C 2D 2E 2F 2Y 14 13 12 11 10 9 8