DDS信号发生器电路设计方案

DDS信号发生器电路设计方案

1、了解电子电路设计的一般方法、根据题目要求选择设计方案。

2、根据理论计算分析,查阅相关资料和手册,选择电子元器件。

3、学会使用电子设计自动化软件对电路进行设计、分析、验证。利用可编程逻

辑器件实现电路的设计、仿真、下载。

4、熟练使用常用电子仪器(示波器、万用表、信号发生器等)对电路进行测试。

5、写出符合要求的课程设计报告。

一、实验设备

1、Altera DE2开发板 (CycloneⅡ EP2C35F672C6)

2、QuartusⅡ9.1开发软件

3、数字电路实验面包板

4、示波器、万用表等

二、实验任务要求

利用DE2实验开发装置,在给定电源条件下,完成正弦波信号发生器电路设计。

1、技术指标

①信号频率输出围50Hz~10kHz,频率可调。步进调整,步长0.5Hz或50Hz;

②频率稳定度10-3。

2、发挥部分

①增加脉冲信号的输出,信号频率输出围50Hz~10kHz;

②脉冲信号占空比可调,调整围2%~98%;

③正弦或脉冲频率步长调整分别为1Hz、10Hz、100Hz、1kHz、10kHz;

④完成在数码管上数字频率显示功能;

三、实验原理介绍

1、DDS

直接数字合成(Direct Digital Synthesis、DDS)是一种新的频率合成技术和信号产生的方法。直接数字频率合成器(DDS)具有超高速的频率转换时间,极高的频率分辨率和较低的相位噪声,在频率改变与调频时,DDS 能够保持相位的连续,因此很容易实现频率、相位和幅度调制。此外,DDS 技术大部分是基于数字电路技术的,具有可编程控制的突出优点。因此这种信号产生技术得到了越来越广泛的应用,很多厂家已经生产出了DDS专用芯片,这种器件成为当今电子系统及设备中频率源的首选器件。

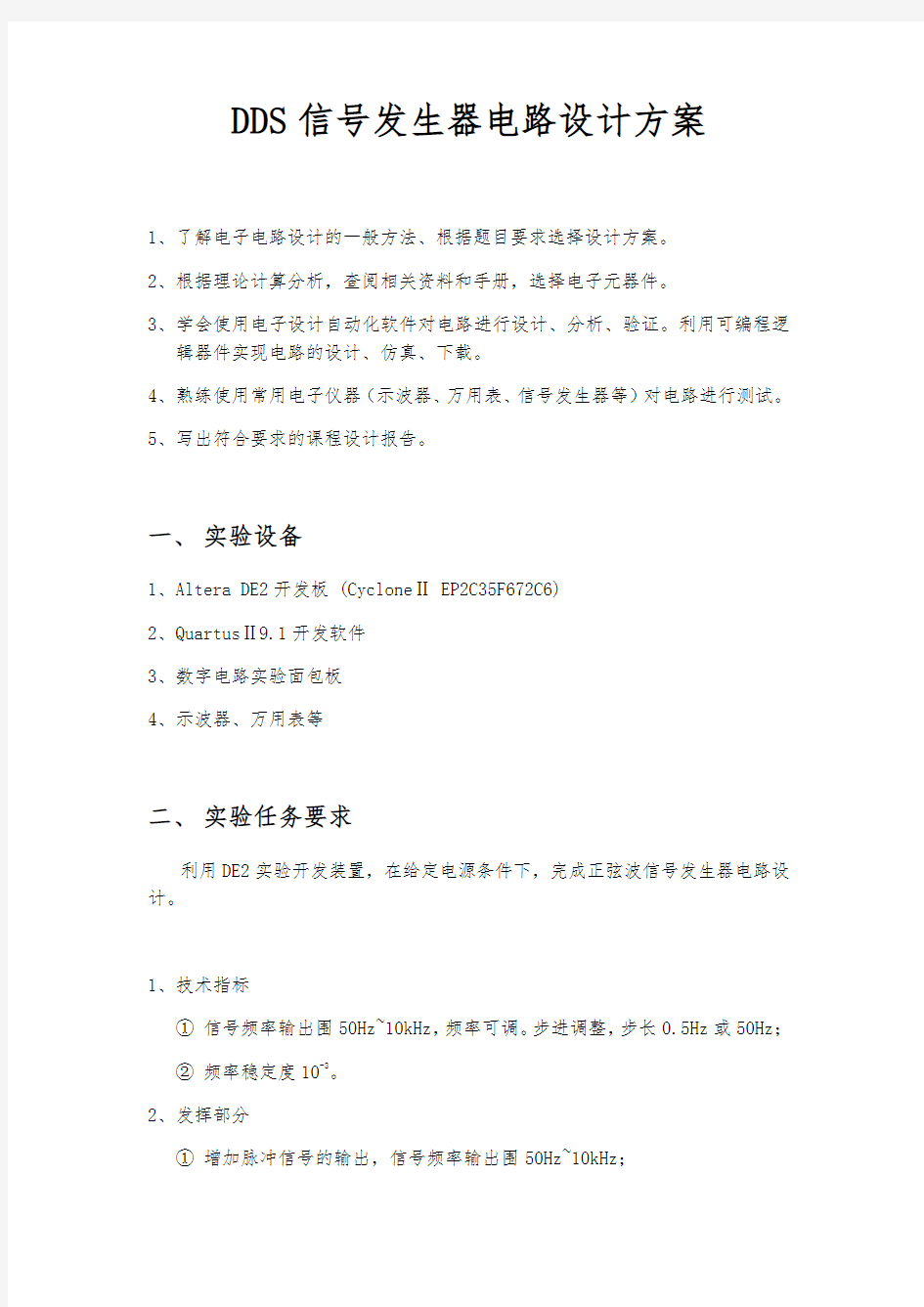

2、相位累加器

一个正弦波,虽然它的幅度不是线性的,但是它的相位却是线性增加的。

DDS利用了这一特点来产生正弦信号。

根据DDS的频率控制字M的位数N,把360°平均分成了2的N次等

份。系统时钟为f

clk 输出频率为f

out

。根据公式f

out

= f

clk

可知,只要选择恰当的

频率控制字,就可以得到所需要的输出频率f

out

。

3、ROM

ROM的作用是构成正弦查找表,其部存储一个完整的正弦波的数字幅度信息,每个查找表的地址对应正弦波中的0~360°围的一个相位点。ROM用相位累加器输出的高M位数据进行相位—幅值转换,在给定的时间上确定输出的波形幅值。

4、D/A

从ROM输出的八位数据是数字量,D/A的作用就是将其转换为模拟量。

将输入的每一位二进制代码按其权值大小转换成相应的模拟量,然后将代表个位的模拟量相加,则所得的总模拟量与数字量成正比,这样便实现了从数字量到模拟量的转换。

5、低通滤波器(LPF)

D/A出来之后的波形是梯形状的,将它通过低通滤波器后就可以看到平滑的、不带毛刺的波形。二阶低通滤波器由一级RC、二级RC和同相比例放

大器组成。当f超过f

0后,其幅频特性以40dB/dec的速率下降,但在f

和

通带截止频率f

p

之间还不够快。

四、实现方案简述

1、设计流程

将系统时钟50MHz送入预分频模块,输出为220Hz。后将其送入DDS累加器作为它的时钟信号。DDS累加器的步长由累加步长控制模块控制,设计频率显示模块显示输出频率。将DDS累加器数据前8位送入ROM进行相位到幅值的转换,ROM 输出经过DAC和低通滤波器,最后用示波器显示波形。

2、功能模块连接图

3、功能模块设计分析

①预分频模块

预分频模块由32位加法器和32位锁存器构成。根据公式f out = f clk 可知,N 为32,f clk =50MHz ,要使f out =220

Hz ,只需求出M 的值,然后对其进行累加。M 的值存储在置数端,cout 端输出的频率便是220Hz ,clk 是系统时钟,clr 为系统清零信号。

② DDS 累加器模块

根据公式f out = f clk 可知,要使输出频率可控,则DDS 累加器的位数要与预分频输出频率相对应。已知预分频输出频率为220Hz ,那么DDS 累加器的加法器和锁存器都对应为20位。化简公式得f out =M ,可通过控制M 的值来控制DDS 累加器的输出频率。dataa[19..0]输入为累加步长(由累加步长控制模块输出),fclk 输入为预分频输出时钟,clr 为系统清零信号。

③ 累加步长控制模块

累加步长控制模块包含步长选择和累加控制两个模块。步长选择模块置题目要求的1Hz、10Hz、50Hz、100Hz、1kHz(由于题目要求DDS累加器的频率输出围为50Hz~10kHz,所以设置步长10kHz意义不大,将之改为50Hz),通过步长选择脉冲循环切换步长频率。累加控制模块将选好的步长进行累加,每当key输入一个脉冲信号,就将选好的步长累加一次,当超过10kHz返回50Hz,这就将DDS累加器的输出频率控制在了50~10kHz之间。clr用于对累加步长的清零,接清零信号,key接单次脉冲信号。

④频率显示模块

频率显示模块用于显示DDS累加器频率,由于题目要求的最大输出频率为10000Hz,所以设计的频率显示模块只输出5位数。该模块输入为累加步

=M,所以DDS的输出频率就是累加后长控制模块输出的累加步长,由于f

out

的步长。输入信号为20为2进制数,将它转换为10进制数,再依次将个十百千万位提取出来做判断。将判断后的值对应的七段数码显示器值输出到5位7段数码显示管显示。num1对应地位,num5对应高位。clk接时钟信号,用于驱动显示模块工作。

⑤波形存储器模块

波形存储模块由高位提取模块和ROM构成。高位提取模块作用是将DDS 累加器中锁存器数据的高8位提取出来送入ROM,之所以取高位弃低位,是因为如果包含低位,则一个周期中将会出现的多于28(256)个值,就不能与ROM表中的256个幅度值形成一一对应。ROM中存储了256个波形幅度值,用高8位的数据进行相位—幅值转换,在给定的时间上确定输出的波形幅值。clk接预分频输出时钟,clr接系统清零信号。

其它波形同理,只需修改ROM查找表中的幅值信息。产生多种波形之后将多个波形输出接到波形选通器上进行选通控制。四个输入分别接正弦波、三角波、方波和锯齿波,output[7..0]接DAC。

ROM正弦查找表:

⑥D/A转换器

DAC用到的芯片为:DAC0832、LF356

DAC0832管脚:

* D0~D7:8位数据输入线,TTL电平,有效时间应大于90ns(否则锁存器的数据会出错);

* ILE:数据锁存允许控制信号输入线,高电平有效;

* CS:片选信号输入线(选通数据锁存器),低电平有效;

* WR1:数据锁存器写选通输入线,负脉冲(脉宽应大于500ns)有效。由ILE、CS、WR1的逻辑组合产生LE1,当LE1为高电平时,数据锁存器状态随输入数据线变换,LE1的负跳变时将输入数据锁存;

* XFER:数据传输控制信号输入线,低电平有效,负脉冲(脉宽应大于500ns)有效;

* WR2:DAC寄存器选通输入线,负脉冲(脉宽应大于500ns)有效。

由WR2、XFER的逻辑组合产生LE2,当LE2为高电平时,DAC寄存器的输出随寄存器的输入而变化,LE2的负跳变时将数据锁存器的容打入DAC 寄存器并开始D/A转换。

* IOUT1:电流输出端1,其值随DAC寄存器的容线性变化;

* IOUT2:电流输出端2,其值与IOUT1值之和为一常数;

* Rfb:反馈信号输入线,改变Rfb端外接电阻值可调整转换满量程精度;

* Vcc:电源输入端,Vcc的围为+5V~+15V;

* VREF:基准电压输入线,VREF的围为-10V~+10V;

* AGND:模拟信号地

* DGND:数字信号地

LF356芯片管脚:

1&5、偏置平衡(调零端)

2、反向输入端

3、正向输入端

4、接电源负

6、输出

7、接电源正

8、空脚

由于不需要用到DAC0832芯片中的输入寄存器和DAC寄存器,所以将1、2、17、18号脚接地,19号脚接+5V。20号脚接+5V。3、10号脚接地,基准电压U

REF 的8号脚接+5V。12号脚接LF356的3号脚并接地,11号脚接LF356的2号脚。9号脚接LF356的6号脚。DI0~DI7接ROM输出。

LF356的1号脚和5号脚接一个电位器RV1用于调零,电位器的滑动端接+15V。4号脚接-15V,7号脚接+15V。由于DAC0832芯片输出为电流信号,而实际操作中需要用电压信号,所以将DAC0832的输出接LF356,将之转换成电压信号。LF356的作用就是讲电流信号转换成电压信号。

ROM输出围为00000000~11111111。已知基准电压U

=+5V,由公式

REF

可得,当输入为00000000时,;

当输入为11111111时,。

将输入全置0,然后用万用表对LF356芯片的输出进行调零。LF356的输出电压均为负值,产生的波形在x轴以下,要想将它反向到x轴以上,可以接一个反向比例放大器。在其基础上加求和运算电路就可上下平移波形。

芯片OP07管脚:

1&8、偏置平衡(调零端)

2、反向输入端

3、正向输入端

4、接电源负

5、空脚

6、输出

7、接电源正

信号从LF356的6号脚输出后通过定值电阻R1和电位器器RV2后进入OP07的2号脚。3号脚接地,4号脚接-15V,7号脚接+15V。1号脚和8号脚接一个电位器RV4用于调零,电位器滑动端接+15V。6号脚接电阻R2反馈到2号脚。在2号脚接一个电位器RV3构成求和运算电路,电位器另一端接+15V。

使输入端(即2号脚)开路,用万用表对OP07芯片输出进行调零,由反向求和运算电路输出电压表达式,可求出输出电压u

。其中RV2可调节放大器增益,

o

调节RV3可上下平移波形。

⑦低通滤波器(LPF)

经过反向、放大后的信号,通过一级RC,二级RC,进入OP07芯片的正向输入端3号脚。1号脚和8号脚接一个电位器RV6用于调零,滑动端接+15V。

4号脚接-15V,7号脚接+15V。6号脚接一个电阻R6反馈到2号脚。2号脚出来接一个电阻R5后接地。

使输入端(即3号脚)开路,用万用表对OP07芯片进行调零。二阶低通滤波器,通带截止频率。已知R=51kΩ,C=100pF,由此可解得,高于输出频率上限10kHz,满足设计要求。

DAC和LPF完整电路:

五、实验仿真结果

1、预分频模块仿真图

编译好电路后新建一个波形向量文件(Vector Waveform File),然后将要进行仿真的节点(Nodes)添加到仿真文件中,保存后打开仿真工具(Simulator Tool),选择功能仿真(Functional),生成网表(Generate Functional Simulation Netlist),之后开始仿真,仿真结束后打开仿真报

告文件(Report)。通过公式f

out = f

clk

求出的M的值为“1000”来一个时钟

信号累加一次。由于最低三位为0,无论怎么累加都不会出现进位,所以,最低三位一直为低电平。

2、DDS累加器模块仿真图

由于f

out

=M,又因为输出频率围为50Hz~10kHz,所以进位高位的进位较

慢,符合设计要求。

3、波形存储模块仿真图

从ROM出来的数据就是输入相位对应的幅值数据了,符合要求。

4、动态仿真正弦波

打开QuartusⅡ SignalTap Ⅱ Logic Analyzer工具,将编译好的sof文件下载到开发板中。然后单击Autorun Analysis,右击output,选择Bus Display Format,然后选择Signed Line Chart就可出现以上动态仿真波形。上面的仿真都是基于QuartusⅡ软件的静态功能仿真。动态仿真是用SignalTapⅡ这一工具捕获FPGA芯片中实时信号的状态,达到硬件和软件的交互。方波、三角波、锯齿波的动态仿真方法与上面一致。

5、动态仿真方波

6、动态仿真三角波

7、动态仿真锯齿波

动态仿真结束后,将输出信号附上管脚,用示波器测量输出最高位信号的频率,而后与理论值作比较。

8、5000Hz测量波形

示波器测量值:

绝对误差:

Δ= |5000-5000| = 0 相对误差:

δ= = 0

9、5001Hz测量波形

示波器测量值:

绝对误差:

Δ= |5001-5001| = 0 相对误差:

δ= = 0

10、5011Hz测量波形

示波器测量值:

绝对误差:

Δ= |5011-5011| = 0 相对误差:

δ= = 0

11、5061Hz测量波形

示波器测量值:

绝对误差:

Δ= |5061.01-5061| = 0.01 相对误差:

δ= = 0.0001976%

12、5161Hz测量波形