三种加法器

三种加法器

加法器是为了实现加法的,即是产生数的和的装置。加法器常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。在此以三种加法器为例分析加法器的结构、设计及优缺点等性能参数。

加数和被加数为输入,和数与进位为输出的装置为半加器。半加器有两个二进制的输入,其将输入的值相加,并输出结果到和进制。半加器虽能产生进制值,但半加器本身并不能处理进制值。若将A、B分别作为一位二进制数,S表示A、B相加的“和”,C是相加产生的“进位”,半加器的真值表如表1所示。由表1可直接写出,

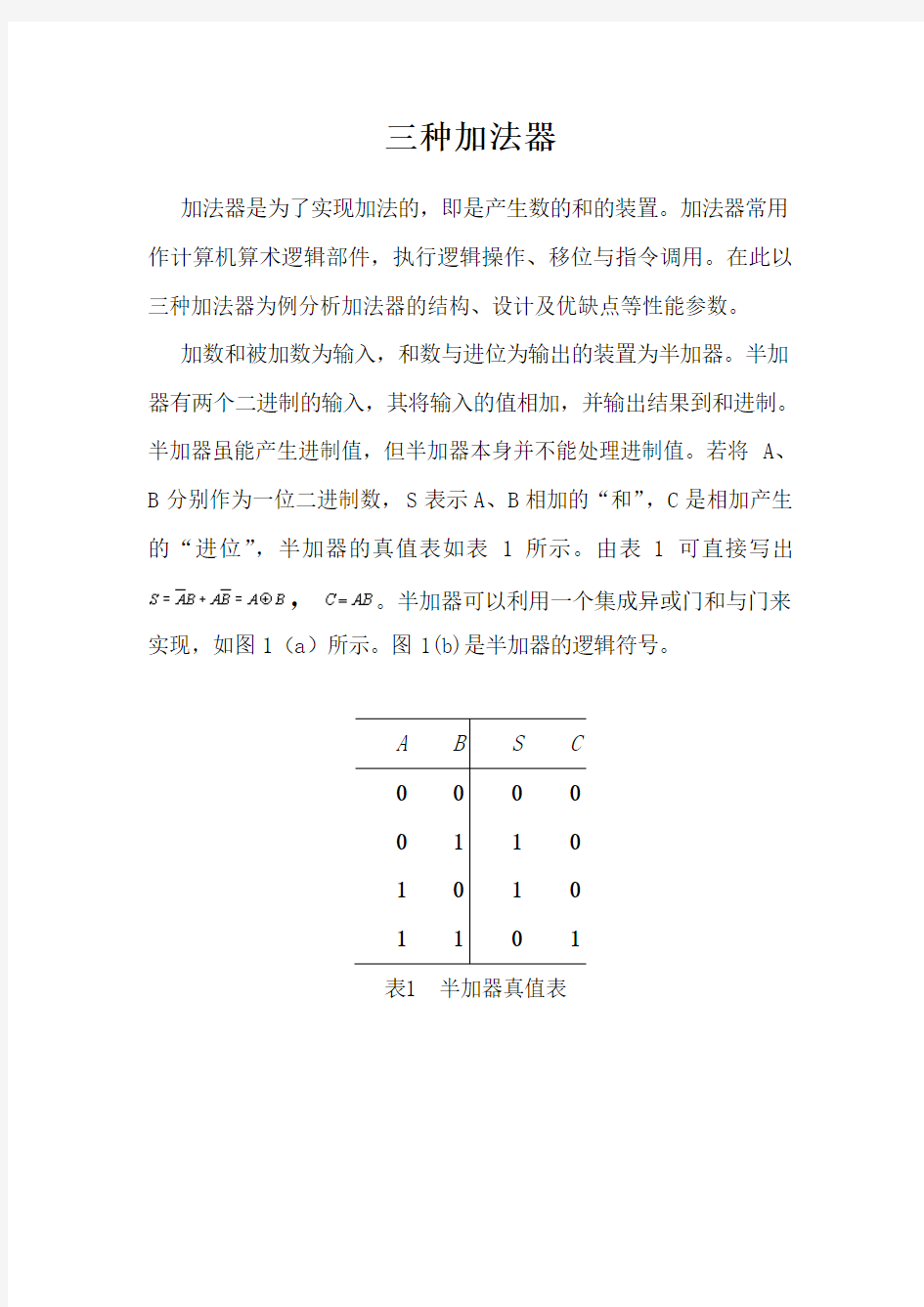

。半加器可以利用一个集成异或门和与门来实现,如图1(a)所示。图1(b)是半加器的逻辑符号。

A B S C

0000

0110

1010

1101

表1 半加器真值表

图1 半加器逻辑图及其逻辑符号半加器实验时的VHDL代码如下:

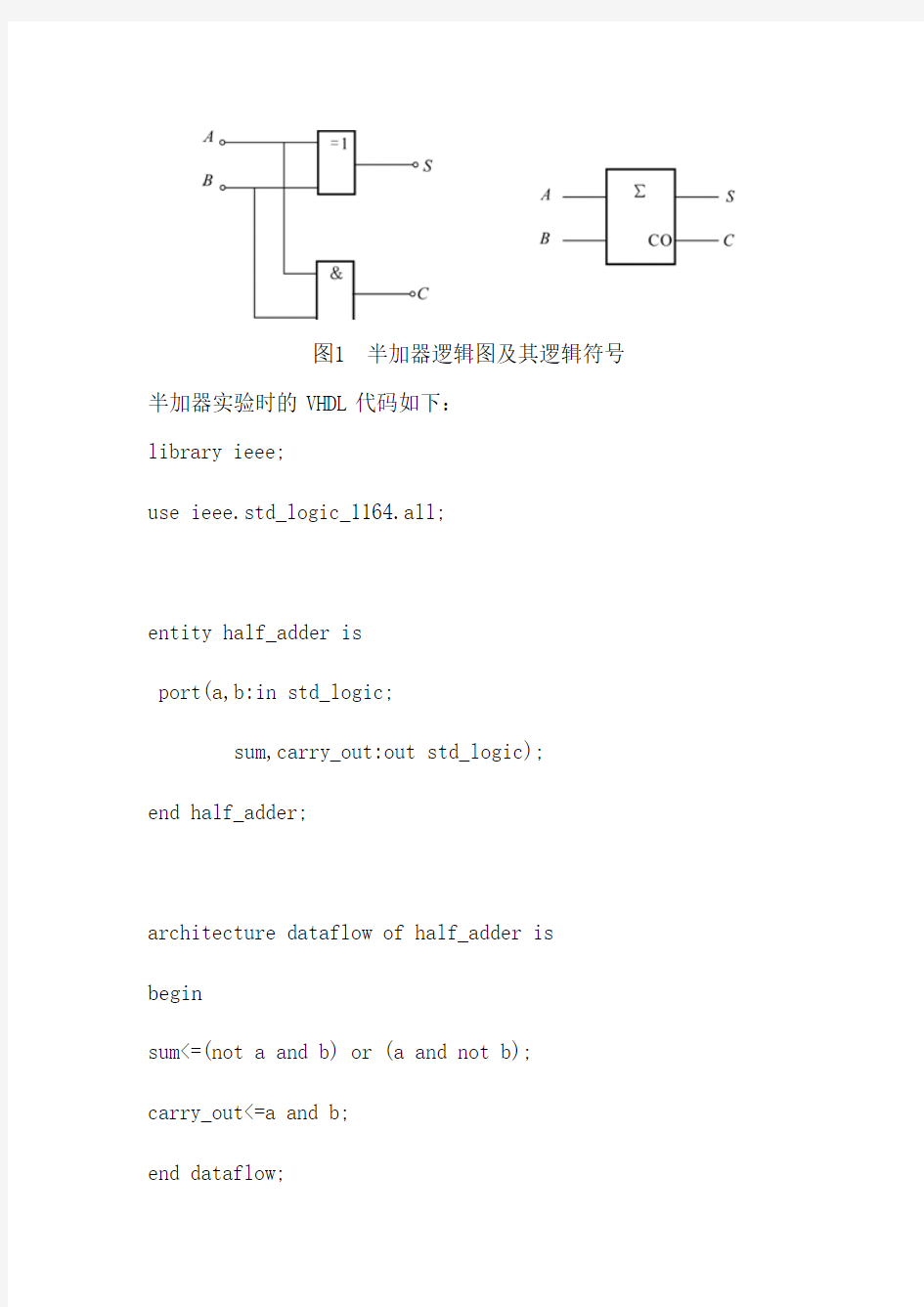

library ieee;

use ieee.std_logic_1164.all;

entity half_adder is

port(a,b:in std_logic;

sum,carry_out:out std_logic);

end half_adder;

architecture dataflow of half_adder is begin

sum<=(not a and b) or (a and not b);

carry_out<=a and b;

end dataflow;

加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。全加器可以处理低位进位,

并输出本位加法进位。对两个一位二进制数及来自低位的“进位”进行相加,产生本位“和”及向高位“进位”的逻辑电路称为全加器。由此可知,全加器有三个输入端,二个输出端,其真值表如表2所示。其中Ai 、Bi 分别是被加数、加数,Ci –1是低位进位,Si 为本位全加和,Ci 为本位向高位的进位。

A i

B i

C i –1

S i

C i

0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1

1

1

1

1

表2 全加器真值表

由真值表可分别写出输出端Si 和Ci 的逻辑表达式

和的逻辑表达式中有公用项,因此,在组成电路时,可令其共享同一异或门,从而使整体得到进一步简化。全加器的逻辑电路图和逻辑符号如图2所示。

图2 全加器的逻辑电路图和逻辑符号

全加器实验时的VHDL代码如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY ADD2 IS

PORT( A8,B8:IN STD_LOGIC_vector(1 downto 0);

CIN:in std_logic;

COUT:out std_logic;

SUM:OUT STD_LOGIC_vector(1 downto 0)); --2bit full adder END ENTITY;

ARCHITECTURE ONE OF ADD2 IS

component Fulladd

PORT( a,b,cin:IN STD_LOGIC;

sum,cout:OUT STD_LOGIC);

END COMPONENT;

signal CINdata,SUMdata:std_logic_vector(1 downto 0);

begin

U1:Fulladd PORT MAP(a=>A8(0),b=>B8(0),cin=>CIN,sum=>SUMdata(0),cout=>CINdat a(0));

U2:Fulladd PORT MAP(a=>A8(1),b=>B8(1),cin=>CINdata(0),sum=>SUMdata(1),cout= >CINdata(1));

SUM<=SUMdata;COUT<=CINdata(1);

END ARCHITECTURE;

利用全加器可以构成4位串行进位加法器,逻辑符号如图所

示:

四位串行加法器在实验中的VHDL代码如下:

library ieee;

entity mux8 is

port(a,b:in bit_vector(4 downto 1);

sum:out bit_vector(4 downto 1);

cout:out bit);

end mux8;

architecture exam of mux8 is component add

port(ain,bin,cin:in bit;

sum:out bit;

cout:out bit);

end component;

signal temp:bit_vector(4 downto 1)

constant x:

bit:='0';

begin

u4:add

Port

map(ain=>a(4),bin=>b(4),cin=>temp(3),sum=>sum(4),cout=>cout );

u3:add

port

map(ain=>a(3),bin=>b(3),cin=>temp(2),sum=>sum(3),cout=>temp (3));

u2:add

port

map(ain=>a(2),bin=>b(2),cin=>temp(1),sum=>sum(2),cout=>temp (2));

u1:add

port

map(ain=>a(1),bin=>b(1),cin=>x,sum=>sum(1),cout=>temp(1)); end exam;

加法器是数字系统中的基本逻辑器件,在数字系统中必不可少,有着非常重要的地位,同时各种加法器均有其相应的优缺点。首先,加法器的设计是却很耗费资源的。其次,串行加法器相对于并行加法器来说占用的资源更少,但运算速度却较慢。因此利用加法器时,应注意其功能及功耗等,使电路具有尽可能高的运算速度和效率。

实验一-加法器的设计与实现讲解

实验项目二:简单计算器设计与实现基本要求: 1. 能够实现加减运算 2. 能够实现乘法运算 扩展要求: 1.能够实现除法运算 一、实验目的 利用原件例化语句完成一个8位加法器的设计。 二、实验环境 Quartus II 开发系统 三、实验内容 1、掌握层次化设计的方法; 2、掌握一位全加器工作原理; 3、掌握用VHDL文本输入法设计电子线路的详细流程; 4、掌握元件例化语句用法; 5、熟悉软硬件设计验证方法。 四、实验过程 设计思想: 8位二进制加法器可以由8个全加器通过级联的方式构成。根据全加器级联的原理,用VHDL设计一个8位二进制数的加法器,可以先设计一个一位全加器,然后利用一位全加器采用元件例化的方式实现加法器。 实验步骤: 1、设计一个全加器 新建工程,建立源文件,输入VHDL设计文件,如下图所示:

完成设计文件输入后,保存文件,对文件进行编译、仿真,以下是仿真结果,如图所示: 由图可知仿真结果正确。 2、元件例化 把VHDL设计文件转为原理图中使用的元件。在文件菜单File中选择Creat/Update选项,单击Create Symbol File for Current File 选项,系统自动生成相应的元件标号。 重复新建文件的操作,选择Block Diagram/Schmatic File 选项,新建一个原理图文件,在添加元件列表中可以看到自动生成的元件,选择full_adder这个元件添加到原理图中,如下图所示:

3、完成顶层图的设计 用生成的元件标号,完成顶层图的设计。这里有两种方法,一种是直接用原理图设计,根据原理图设计工具的使用方法,完成顶层文件的设计,这个方法比较复杂,所以这里选择另一种方法,通过VHDL设计文件。 继续建立源文件,输入VHDL设计文件,如下图所示: 依照上述步骤,保存文件,对文件进行编译、仿真,以下是仿真结果,如图所示:

加法器设计介绍

加法器设计介绍 算术逻辑部件主要处理算术运算指令和逻辑运算指令,它的核心单元是加法器。这个加法器是影响算术逻辑部件整体性能的关键部分,因为几乎所有的算术运算和逻辑运算,都要通过它来完成。 加法器结构包括串行进位加法器(Carry Ripple Adder,CRA)、进位跳跃加法器(cany skip Adder,CKA),以及较高速度的进位选择加法器(carry select Adder,CSA)、超前进位加法器(Can 了Look—a}lead Adder,CLA)和并行前缀加法器(Parallel Prcfix Adder)等。 串行进位加法器(CRA) 串行进位加法器是最简单、最基本的加法器结构。串行进位加法器的进位像水波一样依次通过每位,因此也称为“行波进位加法器”。它每次只能进行一位运算,因此速度很慢。 如下图所示 进位跳跃加法器(CKA) 进位跳跃加法器是串行进位加法器的改进结构。它将整个加法器分为几个组,如果某组的所有进位传播信号都为“1”,则将该组的进位输入直接传送到输出,而不需要进行进位运算。这个过程好像进位做了一个跳过该组的动作,因此称为进位跳跃加法器。 为了实现跳跃进位,每组需要增加一个多路选择器和一个与门,这种结构可以提高加法器的运算速度,但是,速度的提高只有在某些特定的情况下才会出现。如下图所示

进位选择加法器(CSA) 进位选择加法器采用资源复制的基本思想,用硬件来换取速度。它将整个加法器分为几 个组,每组有两条路径,进位输入为“O”和“1”的两种情况通过两条路径同时计算。一 旦该组进位输入信号到来,通过多路选择器选择正确的进位输出与和值。如下图所示 由于采用了前瞻的思想,因此进位选择加法器的速度有很大提高。如果整个加法器分为 M 组,则运算延时可由第一组进位延时、M 个多路选择器的延时及一个和产生延时相加得到。进位选择加法器虽然具有较快的速度,但由于它采用了资源复制的方法,因此实现代价 也成倍增加。 一般的进位选择加法器每组具有相同的位数,延迟也与位数成线性关系,称为“线性进 位选择加法器”。如果不把每组设置为相同的位数,而是从低位到高位组内位数逐渐增大, 例如第一组2 位,第二组3 位,等三组4 位,等等。这种逐组位数加长的方法使加法器结构具有亚线性延迟的特性。经过计算,这种结构的延迟与位数的平方根成正比,因此称为“平 方根进位选择加法器”。

集成运放的基本运算电路

实验2.3 集成运放的基本运算电路 一、实验目的 1、进一步熟悉THM-4模拟电路实验箱面板布局。 2、深入理解集成运放工作于线性区的条件与特点。 3、掌握用集成运算放大器组成电压跟随器、比例、求和电路的特点及性能。 4、学会上述电路的测试和分析方法。 二、实验原理 由于集成电路运放通常都具有极高的差模电压增益,欲使其稳定工作于线性状态下,必须加入深度负反馈,否则它必将工作于非线性状态。 图2.3.1(a)所示是在集成运放中引入了电压负反馈的电路,(b )则是其理想化后的闭环电压传输特性。由此可见,假设A f =2,输入电压U i 不超出-5V —+5V 的范围,则运放将稳定工作于线性区A0B 内,当U i 超出线性范围时,集成运放将进入 饱和状态,输出保持为最大值不变(其大小决定于电源电压)。对于这一点,有时容易忽视甚至误解,以为在集成运放中加入负反馈后,其输出就会随输入而无限增加,这是必须加以注意的。 图2.3.1 (b) 闭环电压传输特性 (a) 引入电压负反馈集成运放电路 U i U o

对于理想化了的运放,当它工作于线性状态下时具有两个十分突出的特点。其一是“虚断”,即I +=I -=0;其二是“虚短”,即U +=U -(在反相输入同相接地电路中因U +=0,故“虚短”又可引伸为“虚地”)。不管电路结构形式如何复杂,均可根据这两个特点推导出输出与输入之间的函数关系。例如在图2.3.1(a )中,由于I +=I -(I -=0),U -=0(虚地),故有 这就是反相放大器的闭环电压传输特性。其中 称为闭环电压放大倍数。 实际运行与理想运放之间总存在一定的差异,故在实际使用中常采用一些措施以减小它的误差,提高其运算精度。经常采用的一个措施是加入平衡电阻R ,以保证实际运放的反相与同相输入端对地的等效电阻相等,从而使其处于对称与平衡工作状态,减小由输入偏置电流引入的误差。其次是防自激,运放在使用中有时会产生自激,此时即使U i =0,也会产生一定的交流输出、使运放无法正常工作。消余自激的办法是在电源端加接去耦电容或增设电源滤波电路,同时应尽可能减小线路、元件间的分布电容,对于具有补偿引脚的集成运放器件,还可接入适当的补偿电容。 三、实验设备 1、模拟电路实验箱 一套 2、示波器 一台 3、数字万用表 一块 1 R R A f f - =i f U R R U =-=1

实验五全加器的设计与应用

实验五全加器的设计及应用 一、实验目的 (1)进一步加深组和电路的设计方法。 (2)会用真值表设计半加器和全加器电路,验证其逻辑功能。 (3)掌握用数据选择器和译码器设计全加器的方法。 二、预习要求 (1)根据表5-1利用与非门设计半加器电路。 (2)根据表5-2利用异或门及与非门设计全加器电路。 三、实验器材 (1)实验仪器:数字电路实验箱、万用表; (2)实验器件:74LS04、74LS08、74LS20、74LS32、74LS86、74LS138、74LS153; 四、实验原理 1.半加器及全加器 电子数字计算机最基本的任务之一就是进行算术运算,在机器中的四则运算——加、减、乘、除都是分解成加法运算进行的,因此加法器便成了计算机中最基本的运算单元。 (1)半加器 只考虑了两个加数本身,而没有考虑由低位来的进位(或者把低位来的进位看成0),称为半加,完成半加功能的电路为半加器。框图如图5-1所示。一位半加器的真值表如表5-1所示。 表5-1 半加器真值表

1位半加器S C i A i B i 和数向高位进位 加数被加数 图5-1 半加器框图 由真值表写逻辑表达式: ? ? ?=⊕=+=i i i i i i i i i i B A C B A B A B A S '' 画出逻辑图,如图5-2所示: (a )逻辑图 (b )逻辑符号 图5-2 半加器 (2)全加器 能进行加数、被加数和低位来的进位信号相加,称为全加,完成全加功能的电路为全加器。根据求和结果给出该位的进位信号。即一位全加器有3个输入端:i A (被加数)、i B (加数)、1-i C (低位向本位的进位);2个输出端:i S (和数)、i C (向高位的进位)。 下面给出了用基本门电路实现全加器的设计过程。 1)列出真值表,如表5-2所示。 表5-2 全加器真值表 从表5-2中看出,全加器中包含着半加器,当01=-i C 时,不考虑低位来的进位,就是半加器。而在全加器中1-i C 是个变量,其值可为0或1。 2)画出i S 、i C 的卡诺图,如图5-3所示。 半加器 全加器

基于FPGA的快速加法器的设计与实现

基于FPGA的快速加法器的设计与实现 赵亚威1吴海波2 (1.沈阳理工大学,辽宁沈阳 110045; 2.东北大学,辽宁沈阳 110004) E-mail: hb_0427@https://www.360docs.net/doc/ad13260195.html, 摘要:加法器是算术运算的基本单元,可以有多种实现结构,采用不同的结构实现其耗用的资源和运算的速度也各不相同。本文研究了基于FPGA的常用加法器的结构及其设计方法,对各自性能加以分析比较,在此基础上采用流水线结构设计了一个8bit的加法器。并在Xilinx 公司的ISE 5.2i 软件环境下, 采用VHDL和Verilog HDL 硬件描述语言进行了设计实现并使用Modelsim进行仿真验证,在此基础上对其性能进行了比较分析。实验结果表明流水线加法器的速度高于其它结构实现的加法器。 关键词:加法器、进位、FPGA、Verilog HDL、流水线 1. 引言 算术逻辑单元(ALU) 不仅能完成算术运算也能完成逻辑运算,是微处理器芯片中的一个十分重要的部件[3]。但是所有基本算术运算(加、减、乘、除)最终都可归结为加法运算,所以加法运算的实现显得尤为重要。对于多位加法操作来说,因为存在进位问题,使得某一位计算结果的得出与所有低于它的位都相关。为了减少进位传输所耗费的时间,提高计算速度,人们设计了多种类型的加法器,提出了很多实现加法器的设计方法,如行波进位加法器、快速行波进位加法器、超前进位加法器等。以上提到的都是并行加法器,此外还有串行加法器,其具有占用资源少、设计灵活等优点。 2. 常用加法器设计方法的分析比较 并行加法器中全加器的位数与操作数的位数相同,可同时对操作数的各位相加。影响运算速度的主要是传递进位信号的逻辑线路(即进位链)。接下来就上面提到的几种并行加法器加以分析比较。 2.1 行波进位加法器 N位行波进位加法器是将N个一位全加器串联进行两个N位数的相加,进位是采用串行进位的方法来实现的,即本级的C out作为下一级的C in参与下一位的加法运算[3]。这种加法器结构简单,但速度较慢,从其逻辑表达式: Sum i = A i⊕B i⊕C i,C i + 1 =A i B i + C i(A i⊕B i)可以看 - 1 -

计组-加法器实验报告

半加器、全加器、串行进位加法器以及超前进位加法器 一、实验原理 1.一位半加器 A和B异或产生和Sum,与产生进位C 2.一位全加器 将一位半加器集成封装为halfadder元件,使用两个半加器构成一位的全加器 3.4位串行进位加法器 将一位全加器集成封装为Fulladder元件,使用四个构成串行进位加法器

4.超前进位加法器(4位) ⑴AddBlock 产生并行进位链中的ti(即Cthis)和di(即Cpass),以及本位结果Sum ⑵进位链(Cmaker) 四位一组并行进位链,假设与或非门的级延迟时间为1.5ty,与非门的延迟时间为1ty,在di和ti产生之后,只需2.5ty就可产生所有全部进位

⑶超前进位加法器 将以上二者结合起来即可完成,A和B各位作为各个AddBlock的输入,低一位的进位Ci-1作为本位AddBlock的C-1的输入。各个AddBlock输出的C_this和C_pass作为对应的Cmaker的thisi和passi的输入。

二、实验器材 QuartusII仿真软件,实验箱 三、实验结果 1.串行进位加法器结果 2.超前进位加法器结果

四、实验结果分析 1.实验仿真结果显示串行加法器比超前进位加法器快,部分原因应该是电路结构优化 不到位。另外由于计算的位数比较少,超前进位加法链结构较复杂,所以优势没体现出来,反倒运作的更慢一点。当位数增加的时候,超前进位加法器会比串行的更快。 2.波形稳定之前出现上下波动,应该与“竞争冒险”出现的情况类似,门的延迟和路径 的不同导致了信号变化时到达的时间有先有后,因此在最终结果形成前出现了脉冲尖峰和低谷;另外也可能部分原因由于电路结构优化的不到位所致

运放篇--之求和电路应用

加法器概念 加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。在电子学中,加法器是一种数位电路,其可进行数字的加运算。随着微电子技术突飞猛进的发展,电路设计技术也由计算机辅助设计逐渐进入自动设计时代。随着加法器在集成电路中被大量的用到,研究加法器成了人们改进现有技术,发展集成电路产业的另一个重要部分。 加法器简介 加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。在电子学中,加法器是一种数位电路,其可进行数字的加法计算。在现代的电脑中,加法器存在于算术逻辑单元(ALU)之中。加法器可以用来表示各种数值,如:BCD、加三码,主要的加法器是以二进制作运算。由于负数可用二的补数来表示,所以加减器也就不那么必要。 加法器是为了实现加法的。 即是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。 对于1位的二进制加法,相关的有五个的量:1,被加数A,2,被加数B,3,前一位的进位CIN,4,此位二数相加的和S,5,此位二数相加产生的进位COUT。前三个量为输入量,后两个量为输出量,五个量均为1位。 对于32位的二进制加法,相关的也有五个量:1,被加数A(32位),2,被加数B(32位),3,前一位的进位CIN(1位),4,此位二数相加的和S(32位),5,此位二数相加产生的进位COUT(1位)。 要实现32位的二进制加法,一种自然的想法就是将1位的二进制加法重复32 次(即逐位进位加法器)。这样做无疑是可行且易行的,但由于每一位的CIN 都是由前一位的COUT提供的,所以第2位必须在第1位计算出结果后,才能开始计算;第3位必须在第2位计算出结果后,才能开始计算,等等。而最后的第32位必须在前31位全部计算出结果后,才能开始计算。这样的方法,使得实现32位的二进制加法所需的时间是实现1位的二进制加法的时间的32倍。 加法器电路运算原理

FPGA一位全加器设计实验报告

题目:1位全加器的设计 一.实验目的 1.熟悉QUARTUSII软件的使用; 2.熟悉实验硬件平台的使用; 3.掌握利用层次结构描述法设计电路。 二.实验原理 由于一位全加器可由两个一位半加器与一个或门构成,首先设计半加器电路,将其打包为半加器模块;然后在顶层调用半加器模块组成全加器电路;最后将全加器电路编译下载到实验箱,其中ain,bin,cin信号可采用实 验箱上SW0,SW1,SW2键作为输入,并将输 入的信号连接到红色LED管 LEDR0,LEDR1,LEDR2上便于观察,sum,cout 信号采用绿色发光二极管LEDG0,LEDG1来 显示。 三.实验步骤 1.在QUARTUSII软件下创建一工程,工程名为full_adder,芯片名为EP2C35F672C6; 2.新建Verilog语言文件,输入如下半加器Verilog语言源程序; module half_adder(a,b,s,co); input a,b; output s,co; wire s,co; assign co=a & b; assign s=a ^ b; Endmodule 3.保存半加器程序为,进行功能仿真、时序仿真,验证设计的正确性。 其初始值、功能仿真波形和时序仿真波形分别如下所示

4.选择菜单File→Create/Update→Create Symbol Files for current file,创建半加器模块; 5.新建一原理图文件,在原理图中调用半加器、或门模块和输入,输出引脚,按照图1所示连接电路。并将输入ain,bin,cin连接到FPGA的输出端,便于观察。完成后另保存full_adder。 电路图如下 6.对设计进行全编译,锁定引脚,然后分别进行功能与时序仿真,验证全加器的逻辑功能。其初始值、功能仿真波形和时序仿真波形分别如下所示

实验一 4位全加器的设计

实验一4位全加器的设计 一、实验目的: 1 熟悉QuartusⅡ与ModelSim的使用; 2 学会使用文本输入方式和原理图输入方式进行工程设计; 3 分别使用数据流、行为和结构化描述方法进行四位全加器的设计; 4 理解RTL视图和Technology Map视图的区别; 5 掌握简单的testbench文件的编写。 二、实验原理: 一个4位全加器可以由4个一位全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相邻的高位加法器的进位输入信号cin相接。 三、实验内容: 1.QuartusII软件的熟悉 熟悉QuartusⅡ环境下原理图的设计方法和流程,可参考课本第4章的内容,重点掌握层次化的设计方法。 2.设计1位全加器原理图 设计的原理图如下所示:

VHDL源程序如下(行为描述):-- Quartus II VHDL Template -- Unsigned Adder library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity f_add is port ( a : in std_logic; b : in std_logic; ci : in std_logic; y : out std_logic; co : out std_logic ); end entity; architecture rtl of f_add is begin (co,y)<=('0',a)+('0',b)+('0',ci); end rtl;

快速加法器的设计与应用

实验报告 课程名称: 数字系统设计实验 II 指导老师:屈民军、唐奕 成绩:_________________ 实验名称: Lab7 快速加法器的设计与应用 实验类型: 设计型 _ 一、 实验要求 实验任务为3.3:采用“进位选择加法”技术设计32位加法器 二、 实验设计思路 “进位选择加法”是通过增大元器件数量、增加硬件面积来提高运算性能。以四位先行加法器为最基本的运算单元,并在每个单元内分别计算出初始进位为‘0’和‘1’时的结果,再通过数据选择器(根据从低一级的进位信号来判断初始进位的值)选择出正确的该四位加法结果,并且将该四位中最高位的进位输出给下一级,作为下一级的初始进位输入。 具体分析:将32位的计算分为八块,0-3位为一块,4-7位一块,依次类推。除去第一块(0-3位的计算),后7块采用进位选择,即每块均计算出初始进位为‘0’或者‘1’时的情况,然后根据低一级的进位输出,来选择正确的结果。 因此,首先要设计4位的先行进位加法器。根据书上的公式,即可实现。这里可以看到,为了提高运算速度,每一个进位的计算都直接依赖于整个加法器的最初输入,而不需要等待相邻低位的进位传递。所以,在verilog 代码中关于c[3],c[2],c[1],c[0]的公式要全部展开,而不是利用前面的进位来计算后面的进位值。 之后,就是模块调用,第一块调用一个4为先行进位加法器,后面七块全部调用两个4为先行进位加法器。 专业:信息与通信工程 姓名:陈博华 学号:3120101830 日期:2014-12-01 地点:教11-400

三、verilog代码部分 整个工程(包括测试文件)的代码有 分别为:1位全加器及其测试文件,4位先行进位加法器及其测试文件,32位快速加法器及其测试文件,和数据选择器。 其中代码 为了充分加快运算速度,,每一位的进位直接依赖于整个加法器的最初输入。 四、仿真结果及其分析 1、四位先行进位加法器的仿真

加法器实验报告

加法器实验报告 篇一:加法器实验报告 实验 __一__ 【实验名称】 1位加法器 【目的与要求】 1. 掌握1位全加器的设计 2. 学会1位加法器的扩展 【实验内容】 1. 设计1位全加器 2. 将1位全加器扩展为4位全加器 3. 使4位的全加器能做加减法运算 【操作步骤】 1. 1位全加器的设计 (1)写出1位全加器的真值表 (2)根据真值表写出表达式并化简 (3)画出逻辑电路 (4)用quartusII进行功能仿真,检验逻辑电路是否正确,将仿真波形截图并粘贴于此 (5)如果电路设计正确,将该电路进行封装以用于下一个环节 2. 将1位全加器扩展为4位全加器 (1)用1位全加器扩展为4位的全加器,画出电路图

(2)分别用两个4位补码的正数和负数验证加法器的正确性(注意这两 个数之和必须在4位补码的数的范围内,这两个数包括符号在内共4位),用quartusII进行功能仿真并对仿真结果进行截图。 3. 将4位的全加器改进为可进行4位加法和减法的运算器 (1)在4位加法器的基础上,对电路进行修改,使该电路不仅能进行加 法运算而且还能进行减法运算。画出该电路 (2)分别用两个4位补码的正数和负数验证该电路的正确性(注意两个 数之和必须在4位补码的数的范围内),用quartusII进行功能仿真并对仿真结果进行截图。 【附录】 篇二:加法器的基本原理实验报告 一、实验目的 1、了解加法器的基本原理。掌握组合逻辑电路在Quartus Ⅱ中的图形输入方法及文本输入方法。 2、学习和掌握半加器、全加器的工作和设计原理 3、熟悉EDA工具Quartus II和Modelsim的使用,能够熟练运用Vrilog HDL语言在Quartus II下进行工程开发、调试和仿真。

加法器及差分放大器项目实验报告

加法器及差分放大器项目实验报告 一、项目内容和要求 (一)、加法器 1、任务目的: (1)掌握运算放大器线性电路的设计方法; (2)理解运算放大器的工作原理; (3)掌握应用仿真软件对运算放大器进行仿真分析的方法。 2、任务内容: 2.1 设计一个反相加法器电路,技术指标如下: (1)电路指标 运算关系:)25(21i i O U U U +-=。 输入阻抗Ω≥Ω≥K R K R i i 5,521。 (2)设计条件 电源电压Ec=±5V ; 负载阻抗Ω=K R L 1.5 (3)测试项目 A :输入信号V U V U i i 5.0,5.021±=±=,测试4种组合下的输出电压; B :输入信号V KHz U V U i i 1.0,1,5.021为正弦波±=信号,测试两种输入组合情况下的输出电 压波形。 C :输入信号V U i 01=,改变2i U 的幅度,测量该加法器的动态范围。 D :输入信号V U i 01=,V U i 1,2为正弦波,改变正弦波的频率,从1kHz 逐渐增加,步长为 2kHz ,测量该加法器的幅频特性。 2.2 设计一个同相加法器电路,技术指标如下: (1)电路指标 运算关系:21i i O U U U +=。 (2)设计条件 电源电压Ec=±5V ; 负载阻抗Ω=K R L 1.5 (3)测试项目 A :输入信号V U V U i i 1,121±=±=,测试4种组合下的输出电压; B :输入信号V KHz U V U i i 1,1,121为正弦波±=信号,测试两种输入组合情况下的输出电压 波形。 (二)、差分放大器 1、任务目的: (1)掌握运算放大器线性电路的设计方法; (2)理解运算放大器的工作原理; (3)掌握应用仿真软件对运算放大器进行仿真分析的方法。 2、任务内容 2.1 设计一个基本运放差分放大器电路,技术指标如下: (1)电路指标 运算关系:)(521i i O U U U --=。 输入阻抗Ω≥Ω≥K R K R i i 5,521。 (2)设计条件

加法器的基本原理实验报告

一、实验目的 1、了解加法器的基本原理。掌握组合逻辑电路在Quartus Ⅱ中的图形输入方法及文本输入方法。 2、学习和掌握半加器、全加器的工作和设计原理 3、熟悉EDA工具Quartus II和Modelsim的使用,能够熟练运用Vrilog HDL语言在Quartus II下进 行工程开发、调试和仿真。 4、掌握半加器设计方法 5、掌握全加器的工作原理和使用方法 二、实验内容 1、建立一个Project。 2、图形输入设计:要求用VHDL结构描述的方法设计一个半加器 3、进行编译,修改错误。 4、建立一个波形文件。(根据真值表) 5、对该VHDL程序进行功能仿真和时序仿真Simulation 三、实验步骤 1、启动QuartusⅡ 2、建立新工程NEW PROJECT 3、设定项目保存路径\项目名称\顶层实体名称 4、建立新文件Blok Diagram/Schematic File 5、保存文件FILE /SA VE 6、原理图设计输入 元件符号放置通过EDIT_>SYMBOL 插入元件或点击图标 元件复制 元件移动 元件转动 元件删除 管脚命名PIN_NAME 元件之间连线(直接连接,引线连接) 7、保存原理图 8 、编译:顶层文件设置,PROJECT_>Set as Top_Level 开始编译processing_>Start Compilation 编译有两种:全编译包括分析与综合(Analysis&Synthesis)、适配(Fitter)、编程(assembler)时序分析(Classical Timing Analysis)4个环节,而这4个环节各自对应相应菜单命令,可单独发布执行也可以分步执行

实验一:8位全加器

实验一:8位全加器 一:8位全加器的源程序: module add8(SUM,cout,A,B,cin); output[7:0] SUM; output cout; input[7:0] A,B; input cin; assign {cout,SUM}=A+B+cin; endmodule 二:8位全加器的测试代码: `timescale 1ns/1ns module add8_tp; reg[7:0] A,B; reg cin; wire[7:0] SUM; wire cout; parameter DEL Y = 100; add8 AD1(SUM,cout,A,B,cin); initial begin A= 8'd0; B= 8'd0; cin=1'b0; #DELY A= 8'd100; B= 8'd200; cin=1'b1; #DELY A= 8'd200; B= 8'd88; #DELY A= 8'd210; B= 8'd18; cin=1'b0; #DELY A= 8'd12; B= 8'd12; #DELY A= 8'd100;B= 8'd154; #DELYA= 8'd255; B= 8'd255; cin=1'b0; #DELY $finish; end initial $monitor($time,,,"%d + %d + %b = {%b, %d}",A,B,cin,cout,SUM); endmodule 三:Transcript显示结果: # Loading work.add8_tp # Loading work.add8 # ** Warning: (vsim-3009) [TSCALE] - Module 'add8' does not have a `timescale directive in effect, but previous modules do. # Region: /add8_tp/AD1 add wave sim:/add8_tp/* run # 0 0 + 0 + 0 = {0, 0} run

加法器实验报告

实验三加法器的设计与仿真 一、实验目的 熟悉quartus ⅱ仿真软件的基本操作,用逻辑图和vhdl语言设计加法器并验证。 二、实验内容 1、熟悉quartus ⅱ软件的基本操作,了解各种设计输入方法(原理图设计、文本设计、 波形设计) 2、用逻辑图和vhdl语言设计全加器并进行仿真验证; 3、用设计好的全加器组成串行加法器并进行仿真验证; 4、用逻辑图设计4位先行进位全加器并进行仿真验证; 三、实验原理 1. 全加器 全加器英文名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。 用途:实现一位全加操作逻辑图 真值表 第 1 页共 7 页 利用与或门设计的全加器,它只能做一位的加法,先预想好它的功能,写出真值表,就可以根据这些来设计电路了。 2.四位串行加法器 逻辑图 利用全加器的组合实现4位串行加法器,全加器只能对一位进行操作,将每一位的结果传给下一位,就可以实现4位的加法器。 3.74283:4位先行进位全加器(4-bit full adder) 利用74283芯片实现的4位先行进位全加器比前两者功能更完善,它可以实现进位功能,这个自己设计难度比较大,可以参照74283的功能表加深对它的理解, 第 2 页共 7 页 按照如下的逻辑图实现进位全加器。 逻辑框图 逻辑功能表 注:1、输入信号和输出信号采用两位对折列表,节省表格占用的空间,如:[a1/a3]对应的列取值相同,结果和值[σ1/σ3]对应的运算是σ1=a1+b1和σ3=a3+b3。请自行验证一下。 2、c2是低两位相加产生的半进位,c4是高两位相加后产生的进位输出,c0是低位级加法器向本级加法器的进位输入。 四、实验方法与步骤 实验方法: 第 3 页共 7 页 采用基于fpga进行数字逻辑电路设计的方法。 采用的软件工具是quartusii软件仿真平台,采用的硬件平台是altera epf10k20ti144_4的fpga试验箱。 实验步骤: ? 全加器 1、编写源代码。打开quartusⅱ软件平台,点击file中得new建立一个文件。编写的文件 名与实体名一致,点击file/save as以“.vhd”为扩展名存盘文件。vhdl设计源代码

实验六:加法器的使用

实验六:加法器的使用 1.实验目的 1) 熟悉加法器的工作原理与逻辑功能; 2) 掌握加法器的使用。 2.理论准备 1)二进制并行加法器是一种能并行产生两个二进制数算术和的逻辑部件,按其进位方式的不同可分为串行进位和超前进位二进制并行加法器; 2)串行进位二进制并行加法器是由全加器级联而成的。其特点是:被加数和加数的各位能同时并行到达各位的输入端,而各位全加器的进位输入则是按照由低位向高位逐级串行传递的,各进位形成一个进位链。由于每一位相加的和都与本位进位输入有关,所以,最高位必须等到各低位全部相加完成并送来进位信号之后才能产生运算结果。显然,这种加法器运算速度较慢,而且位数越多,速度就越低; 3)为了提高加法器的运算速度,必须设法减小或去除由于进位信号逐级传送所花的时间,使各位的进位直接由加数和被加数来决定,而不需依赖低位进位。根据这一思想设计的加法器称为超前进位(又称先行进位)二进制并行加法器。超前进位4位二进制并行加法器有74283。 3.实验内容 用4位并行加法器(74283)设计一个可以做加法和减法的电路。当控制信号M=0时,将两个无符号的4位二进制数相加,当M=1时它将两个无符号数相减。 4.设计过程 1)输入:a[4..1]为被加数(或被减数,b[4..1]为加数(或减数),a[4..1]和b[4..1]为4位二进制数,控制信号M,当M=0时,电路实现加法运算,即执行a[4..1]+b[4..1],当M=1时,电路实现减法运算,即执行a[4..1]-b[4..1]。减法采用补码运算。 2)用一个4位二进制并行加法器(74283)和4个异或门实现上述逻辑功能。将4位二进制a[4..1]直接加到并行加法器的A4、A3、A2和A1输入端,4位二进制b[4..1]通过异或门加到并行加法器的B4、B3、B2和B1输入端,并将功能变量M作为异或门的另一个输入且同时加到并行加法器的CIN进位输入端。 3)当M=0时,CIN=0,b[4..1]⊕M= b[4..1]⊕0= b[4..1],加法器实现a[4..1]+b[4..1];当M=1时,CIN=1,b[4..1]⊕M= b[4..1]⊕1 = b[4..1]’,加法器实现a[4..1]+b[4..1]’+1,即a[4..1]-b[4..1]。 4)根据真值表和逻辑函数画逻辑图。根据上式可以画出如图一所示的逻辑图。

四位加法器

电子设计技术课程设计 四位加法器 姓名:罗鹏 学号:09325215 专业:电子信息工程 班级:093252 指导教师:黄河 2012年11月8日

目录 一、设计目的 (3) 二、设计要求 (3) 三、设计过程 (4) 1.原理图的设计 (4) 2.程序的设计 (5) 3.功能仿真设计文件 (8) 四、设计体会 (10) 附录:A 参考文献 (11) 附录:B 评分表 (12)

一、设计目的 1.学习实用EDA设计软件QuartusⅡ,了解电路描述、综合、模拟过程。 2.学习VHDL程序中数据对象、数据类型、顺序语句、并行语句的综合使用,了解VHDL程序的基本结构。 3.掌握使用EDA工具设计数字系统的设计思路和设计方法。学习VHDL基本逻辑电路的综合设计应用。 二、设计内容 设计并调试好一个由4个1位全加器级连构成的,本级的近位输出作为下一集的近位输入。

三、设计过程 1、原理图的设计 打开QuartusⅡ,单击file,选择new ,选择BlockDiagram/Schematic类型。在原理图编辑界面中,元件选择对话框的符号名“Symbol Name”栏目内直接输入xor,或者在“Symbol Files”栏目中,用鼠标双击“xor”元件名,即可得到异或门的元件符号。用上述同样的方法也可以得到与门及输入端和输出端的元件符号。用鼠标双击输入或输出元件中原来的名称,使其变黑后就可以进行名称修改,用这种方法把输入端的名称分别更改为“in3,in4,in5”,把两个输出端的名称分别更改为“led3”和“led4”,然后按照图1所示的一位加法器逻辑电路的连接方式,用鼠标将相应的输入端和输出端及电路内部连线连接好,并以“xxx.bdf”(注意后缀是.bdf)为文件名,存在自己建立的工程目录D:\xxx内。进行存盘操作时,系统在弹出的存盘操作对话框中,自动保留了上一次存盘时的文件名和文件目录,不要随意单击“OK”按钮结束存盘,一定要填入正确的文件名并选择正确的工程目录后,才能单击“OK”按钮存盘,这是上机实验时最容易忽略和出错的地方。 图1 一位加法器原理图

数电实验报告半加全加器

实验二 半加/减器与全加/减器 一、 实验目的: (1) 掌握全加器和半加器的逻辑功能。 (2) 熟悉集成加法器的使用方法。 (3) 了解算术运算电路的结构。 二、 实验设备: 1、 74LS00 (二输入端四与非门) 2、 74LS86 (二输入端四异或门) 3、 数字电路实验箱、导线若干。 Ver 4B 4A 4¥ 3B 3A 3Y 1A IB !Y 2A 2B 2Y GND (74LS86引脚图) 三、 实验原理: 两个二进制数相加,叫做半加,实现半加操作的电路,称为半加器。 A 表示 被加数,B 表示加数,S 表示半加和,Co 表示向高位的进位。 全加器能进行加数、被加数和低位来的信号相加,并给出该位的进位信号以 及和。 四、 实验内容: 用74LS00和74LS86实现半加器、全加器的逻辑电路功能。 (一)半加器、半减器 M=0寸实现半加,M=1时实现半减,真值表如下: (74LS00引脚 )

功能M A B S C 半加00000 00110 01010 01101 半减10000 10111 11010 11100 —s +/- ——co M (半加器图形符号) 2、 ⑴S真值表: 00011110 00110 11001 A ⑵C真值表: 00011110 00000 10101 C 二B(A二M)

(二)全加器、全减器 S CO C^BC i-1 ?(M 十 A )(B 十 C ) 、实验结果 半加器: S 二 AB AB = A 二 B C =B (A 二 M ) 全加器: S = A 二 B - C i-1 G 二GM C 2M CI B +/一

第6章 信号运算电路 习题解答

第6章习题解答 自测题6 一、填空题 1.采用BJT 工艺的集成运放的输入级是( )电路,而输出级一般是( )电路。 2.在以下集成运放的诸参数中,在希望越大越好的参数旁注明“↑”,反之则注明“↓”。 vd A ( ),C M R K ( ),id R ( ),ic R ( ),o R ( ),BW ( ), B W G ( ),SR ( ),IO V ( ),dT dV IO /( ),IO I ( ),dT dI IO /( )。 3.集成运放经过相位补偿后往往具有单极点模型,此时-3dB 带宽BW 与单位增益带宽BWG 之间满足关系式( )。 4.集成运放的负反馈应用电路的“理想运放分析法则”由虚短路法则,即( )和虚开路法则,即( )组成。 5.理想运放分析法实质是( )条件在运放应用电路中的使用。 6.图T6-1a 是由高品质运放OP37组成的( )放大器,闭环增益等于( )倍。在此放大器中,反相输入端②称为( )。电路中10k Ω电位器的作用是( )。R P 的取值应为( )。 7.将图T6-1a 中电阻( )换成电容,则构成反相积分器。此时u o =( ),应取R P =( )。 8.将图T6-1a 中电阻( )换成电容,则构成反相微分器。此时. v o =( ),R P 应取( )。 9.图T6-1b 是( )放大器,闭环增益等于( )倍。应取R P =( )。 10.比较图T6-1a 和图T6-1b 两种放大器,前者的优点是没有( )电压,缺点是( )较小。 + - 图T6-1a 图T6-1b 11.将图T6-1b 中的电阻( )开路,电阻( )短路,电路即构成电压跟随器。 12.负反馈运放的输出电压与负载电阻几乎无关的原因是( )。

quarters加法器实验报告

加法器数字逻辑实验报告 一、实验目的 1.熟悉Quartus II软件的基本操作,了解各种设计方法(原理图设计、文本设计、波形设计) 2.用VHDL语言设计一个加法器。 3.用VHDL语言设计串行加法器、并行加法器。 二、实验内容 1、熟悉QuartusⅡ软件的基本操作,了解各种设计输入方法 (原理图设计、文本设计、波形设计) 2、用VHDL语言设计加法器、串行全加器、并行全加器,再利 用波形编辑区进行逻辑功能仿真,以此验证电路的逻辑功能 是否正确,最终在FPGA芯片上下载验证逻辑实现。三、实验原理 1.全加器 用途:实现一位全加操作 逻辑图 真值表 X Y CIN S COUT

0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1 VHDL程序 数据流描述: 波形图

2.四位串行加法器逻辑图 波形图

3.74283:4位先行进位全加器(4-Bit Full Adder) 逻辑框图 逻辑功能表 注:1、输入信号和输出信号采用两位对折列表,节省表格占用的空间,如:[A1/A3]对应的列取值相同,结果和值[Σ1/Σ3]对应的运算是Σ1=A1+B1和Σ3=A3+B3。请自行验证一下。 2、C2是低两位相加产生的半进位,C4是高两位相加后产

生的进位输出,C0是低位级加法器向本级加法器的进位输入。四、实验方法与步骤 实验方法: 采用基于FPGA进行数字逻辑电路设计的方法。 采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4的FPGA电路板。 实验步骤: 1、建立工程project,并命名顶层文件为JFQ,按照实验箱上 FPGA的芯片名更改编程芯片的设置。操作是点击Assignment/Device,选取芯片的类型。选择“FLEX10K—— EPF10K20TI144_4” 2、编写VHDL源代码。打开QuartusⅡ软件平台,点击File中得 New建立一个VHDL文件。编写的文件名与实体名一致且为JFQ。VHDL如下:

快速浮点加法器的FPGA实现

—202 — 快速浮点加法器的FPGA 实现 郭天天,张志勇,卢焕章 (国防科技大学ATR 实验室,长沙 410073) 摘 要:讨论了3种常用的浮点加法算法,并在VirtexII 系列FPGA 上实现了LOP 算法。实验结果表明在FPGA 上可以实现快速浮点加法器,最高速度可达152MHz ,资源占用也在合理的范围内。 关键词:浮点加法器;移位器;前导1预测;FPGA FPGA Implementation of Fast Floating-point Adder GUO Tiantian, ZHANG Zhiyong, LU Huanzhang (ATR Lab, NUDT, Changsha 410073) 【Abstract 】Three commonly used Floating-point addition algorithms are discussed, and the LOP algorithm is implemented on VirtexII series FPGA. The implementing results show that the fast floating-point adder can be implemented on FPGA, the highest running frequency is 152MHz and the area cost is rational compare to the entire resources. 【Key words 】Floating point adder ;Shifter ;Leading-one predicator ;FPGA 计 算 机 工 程Computer Engineering 第31卷 第16期 Vol.31 № 16 2005年8月 August 2005 ·开发研究与设计技术· 文章编号:1000—3428(2005)16—0202—03 文献标识码:A 中图分类号:TP302 浮点加/减法是数字信号处理中的一个非常频繁并且非常重要的操作。在现代数字信号处理应用中,浮点加减运算几乎占到全部浮点操作的一半以上。浮点算法比定点算法更复杂,占用更多资源。目前在大多数数字信号处理系统中,一般都是由DSP 芯片来完成浮点运算。用DSP 芯片完成浮点运算的好处是容易实现,精度高,缺点是加重DSP 芯片的负担,系统速度可能会受到影响。在某些情况下需要使用专门的浮点处理部件才能满足系统要求。 FPGA 具有可编程、资源丰富、开发周期短、小批量成本低等优点,它已经成为数字电路研究开发的一种重要实现形式,并广泛应用于各种数字信号处理系统当中。原来在FPGA 中实现浮点处理部件是很困难的,主要是由于早期的FPGA 速度较慢,资源较少,浮点算法对它来说过于复杂。例如一个32位的浮点加法器就要占用Altera 8188 72%的资源,时钟频率最大只有10MHz [1],这样的效果当然不能令人满意。近年来随着集成电路工艺水平的不断提高,以及体系结构方面的发展,FPGA 的容量、速度、资源等方面都有了很大的提高。例如Xilinx 公司最新的FPGA 已经采用90nm 工艺,最高时钟频率达到420MHz ,容量达到1 000万逻辑门以上,内部还包括处理器、数字锁相环、块RAM 、大量的寄存器等多种资源,支持多种I/O 接口标准[6]。FPGA 的速度和容量已经不再是瓶颈了,所以研究浮点处理部件的FPGA 实现具有很强的实际意义。 本文将介绍在Xilinx 公司的VirtexII 系列FPGA 上快速浮点加法器的一种实现形式。 1 浮点格式 常用的浮点格式为IEEE 754标准,IEEE 754标准有单精度浮点数、双精度浮点数和扩展双精度浮点数3种,单精度为32位,双精度为64位,扩展双精度为80位以上,位数越多精度越高,表示范围也越大。在通常的数字信号处理应用中,单精度浮点数已经足够用了,本文将以它为例来设计快速浮点加法器。单精度浮点数如图1所示。 图1 IEEE 754单精度浮点数格式 其中s 为符号位,s 为1时表示负数,s 为0时表示正数;e 为指数,取值范围为[1,254],0和255表示特殊值;f 有22位,再加上小数点左边一位隐含的1总共23位构成尾数部分。由它表示的浮点数v 的值如下式所示。 (127)(1)2(1.)s e v f ?=??? 32位浮点数可以表示的范围为38 38 1.210 3.410?+±×?±×。在某些情况下可能不需要32位的精度,那么可以用24位或者16位来表示浮点数,如16位浮点数表示如图2所示。 图2 16位浮点数格式 16位浮点数v 的值如下式所示。 (31)(1)2(1.)s e v f ?=??? 16位浮点数可以表示的范围为9 10 8.581510 6.98510?±×?±×。 2 浮点加法器算法 浮点加法一般包括求阶差、对阶、尾数求和、规格化和舍入等步骤,具体的算法在各种文献[1,2]上都有详细的叙述,这里就不再一一介绍了。目前比较常用的浮点加法有3种[3],如图3所示。图中用到的符号描述如下: a E , b E :加数a 和加数b 的指数; a M ,b M :加数a 和加数b 的尾数; diff :两个指数的绝对差,diff =b a M M ?; 作者简介:郭天天(1974—),男,博士生,主研方向为ASIC 与实时系统、DSP 与FPGA 应用等;张志勇,博士生;卢焕章,教授、博导 定稿日期:2004-07-08 E-mail :ttguo0452@https://www.360docs.net/doc/ad13260195.html, 位数位数