高性价比实时时钟日历芯片AT8563设计考虑

https://www.360docs.net/doc/c39719353.html,/

高性价比实时时钟日历芯片AT8563设计考虑

作者:徐维锋 武汉芯景科技有限公司

AT8563是武汉芯景科技有限公司最新推出的CMOS 实时时钟/日历芯片。它内置一个包括世纪/年/月/日/时/分/秒的计时器,在电路中起到钟表的作用。系统可以设置和读取AT8563中存放的当前时间,从而对数据进行相应处理(例如计费、显示、记录等)。AT8563通过先进的I 2C 总线接口与系统之间串行传送数据,比起采用并行总线的方案大大减少电路板上的布线数目,非常适合于复杂系统。

AT8563目前提供DIP-8、SOP-8、TSSOP-8、MSOP-8四种封装形式,可应用于移动电话类通讯产品、便携仪器、电信计费、考勤机、电脑主板、微机外设……等等一切与计时有关的电子产品中。

器件特性:

● 宽工作电压范围:1.0~5.5V ● 低休眠电流典型值为0.25μA

● 具有世纪标志,可工作于1900-2099年 ● I 2C 总线频率最高达400KHz

● 时钟输出的频率可编程选择32.768KHz/1024Hz/32Hz/1Hz ● 内含报警和定时器

● 具备低电压检测和上电复位失效功能

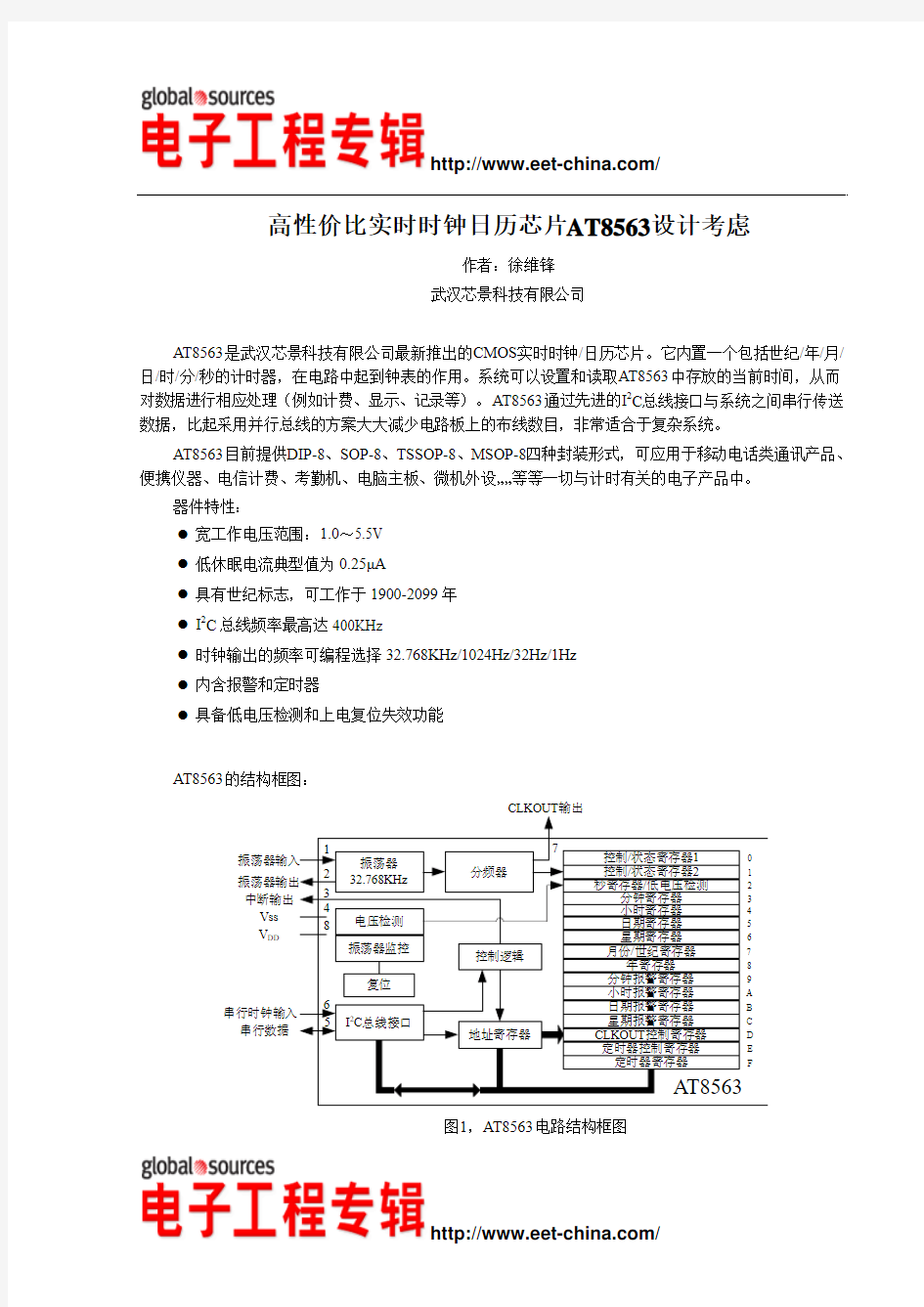

AT8563的结构框图:

中断输出Vss V DD

串行数据

图1,AT8563电路结构框图

https://www.360docs.net/doc/c39719353.html,/

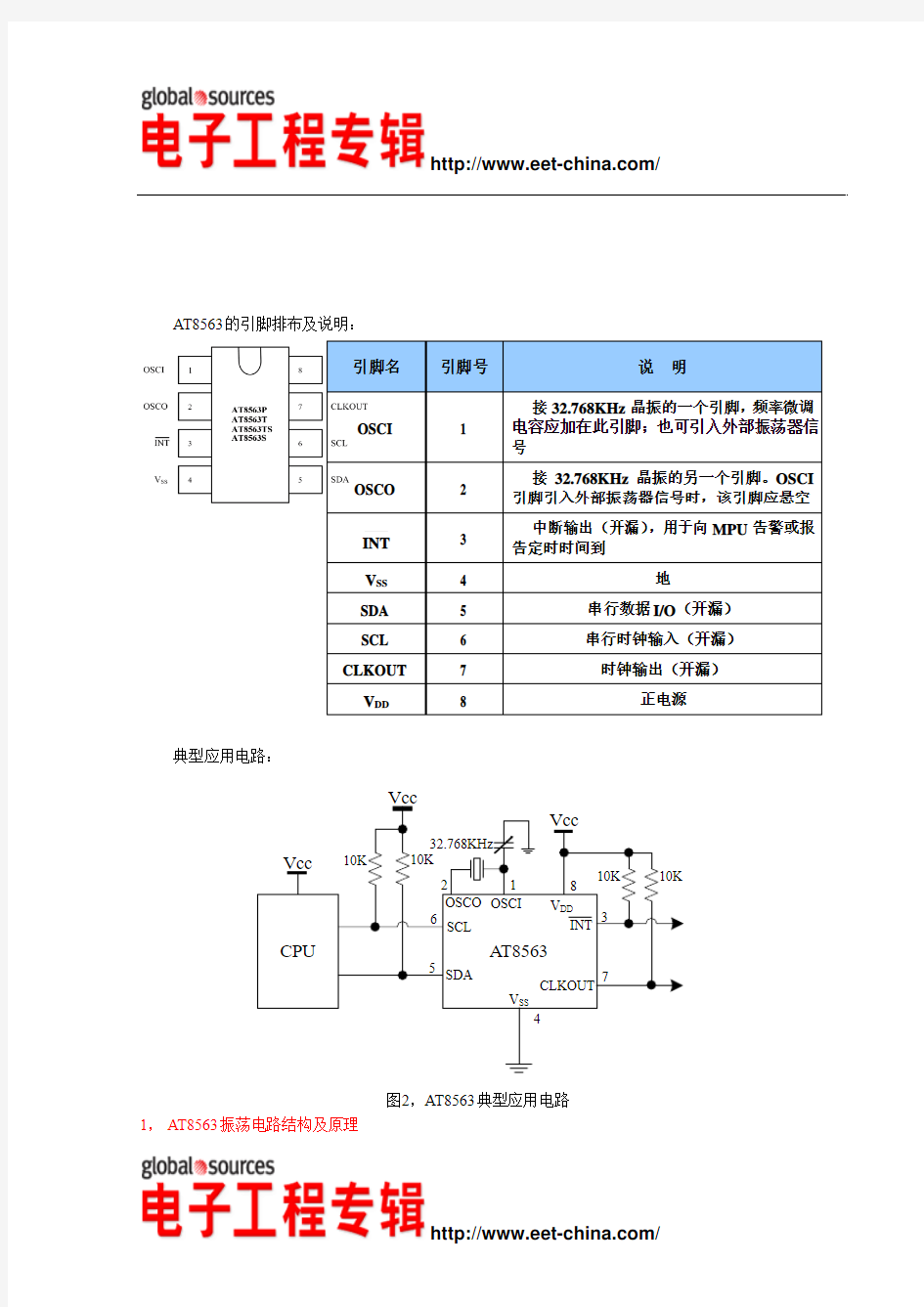

AT8563的引脚排布及说明:

典型应用电路:

图2,AT8563典型应用电路

1, AT8563振荡电路结构及原理

https://www.360docs.net/doc/c39719353.html,/

AT8563芯片中集成的晶振振荡电路采用Pierce 结构。振荡电路的工作电流由振幅控制电路提供,而工作电流的大小由振幅控制电路检测振荡电路的输出振幅来决定。电路的基本工作原理是:电路上电时,振荡输出为零,此时振幅控制电路输出比较大的电流,振荡电路迅速起振;振幅逐渐增大,振幅控制电路随之降低输出电流;当振幅达到设定值时,振幅控制电路的输出电流不再降低,电路维持在这个状态,输出振幅保持不变。通过工作电流来控制振幅,一方面电路的工作点比较稳定,另一方面振幅受限后,非线性作用的影响降低,因此频率稳定性得到提高。同时,工作点的稳定也使工作电流随电压的变化小,有效降低了功耗。另外,利用振幅到电流的反馈机制,电路能够根据晶体和工艺参数的变化自动调节工作点。

图3,AT8563晶振等效电路

AT8563采用负载电容为12.5pF 的晶振,芯片中Cin 电容已被集成,C T 调节范围为15~21pF 。为避免信号干扰,PCB 制作时,必须遵守以下设计规则:

1) 将晶振尽量靠近OSCIN ,OSCOUT 引脚。保持RTC 和晶振之间的距离尽量小,以减少天线长度

来,从而降低噪声的接收。

2) 保持晶振Pad 和连接OSCIN ,OSCOUT 的线宽尽可能的小。Pad 和线宽越大,越容易接收邻近的

噪声信号。

3) 在晶振周围设置保护环(保护环接地)。它将保护晶振相对于噪声信号独立。参见图4; 4) 尽量不要让其他层的信号直接从晶振或连接OSCIN ,OSCOUT 的信号线下穿过。相对于板上其

他信号越独立,晶振越不容易接收到噪声信号。任何信号线和X1,X2之间的信号线必须保证最少0.200英寸的距离。RTC 应该与任何产生电磁信号的元件隔离,特别是离散的和模块化的RTCs 。

5) 在晶振的正下方的层设置一块地(ground plane )十分有帮助。它有助于晶振与其他层的层间

隔离。注意地只用设置在晶振的周围而不用覆盖整块板,并且最好不要超出保护环的范围。具体布线示意图如下:

https://www.360docs.net/doc/c39719353.html,/

图4,AT8563 晶振布线示意图

2,在芯片实际使用过程中,经常遇到的一些问题

●I2C总线无反映

首先检查晶振是否起振,简单的办法即用示波器观察OSCO引脚有无32768Hz波形输出(有直流分量)。但此种办法,因为探头直接加载在OSCO上增大AT8563晶振的负载电容,有可能导致晶体振荡器停振。更准确的办法是在CLKOUT端接10K的上拉电阻,不需要初始化程序上电后直接观察CLKOUT是否有32768方波输出。如果未起振,建议用户检查电源电压是否在2-6V范围内;电源到AT8563经过的二极管是否可靠;是否是采用12.5pF的等效负载电容的晶振;调整晶振至AT8563引脚的电路板布线,加地线保护环,引脚中间不要走其它信号线;检查OSCI引脚对地接的电容是否漏电。

如果晶振起振,请检查I2C频率是否较高,降低频率再试;是否接了上拉电阻,阻值是否合适(建议一般为10KΩ)。较低的电源电压、较高的I2C频率要求上拉电阻的阻值较小;访问AT8563所用的I2C总线地址是否正确(读地址为A3H,写地址为A2H),地址不对,AT8563不会响应。

如果以上都无问题,I2C依然无反应,I2C总线上可能存在总线竞争现象,断开I2C总线上其他I2C从器件,单独访问I2C上唯一一个I2C从器件测试。

●I2C总线读出的是乱码或不正确的时间

可尝试的处理办法:

?降低I2C频率再试;

?I2C时序是否符合标准,建议用示波器查看,并对照I2C总线文档说明;

?I2C总线上是否还接有其它I2C器件,如有的话,暂时先取下再试;

?AT8563的电源和地引脚应有0.1μ~1μF去耦电容;

?I2C总线上拉电阻阻值是否合适,与地或电源之间是否存在有电容;

?I2C总线是否走线较长,而一端是否悬空。如果悬空,建议切断微处理器与AT8563之外的走线再试;

?所读的寄存器是否确为要读的寄存器地址;

?寄存器内容为BCD码形式,而非十六进制,请确保程序按这种格式编写;

?AT8563的许多寄存器都有未使用的比特位,这些位读出时可能为0也可能为1,所以对同一寄存器读出的内容可能有差异,这是正常现象,只要其中的有效位正确就不碍事。

https://www.360docs.net/doc/c39719353.html,/

● 走时不准确

可尝试的处理办法:

? 电源电压是否合适;

? 检查OSCI 引脚是否对地接有电容,调整该电容的容值到合适的值; ? 检查晶振有无随机停振的现象,如有,建议客户换用质量较好的晶振;

? 读秒寄存器(02H )的最高位(VL )是否置位。如果是,表明供电电源有过断电或欠压情况,

导致AT8563无法保证正确走时;

● 时间有不正常的突变现象 可尝试的处理办法:

? 降低I 2

C 频率再试;

? I 2

C 总线上还接有其它I 2

C 器件,如有的话,暂时先取下再试; ? AT8563的电源和地引脚是否有0.1μ~1μF 去耦电容;

? 确信电源不存在干扰,必要时用电池供电、用+5V 电源试试,也可将电源至AT8563之间的

二极管去掉,或换为肖特基二极管再试;

? 检查I 2

C 访问程序(包括初始化、中断访问程序等),看是否存在误向芯片写入数据的代码; ● 星期显示与日期不对应

? AT8563的星期寄存器(06H )内容是用户自定义的,并非设置好日期,由芯片“自动计算”

出星期几。因此在对AT8563初始化时,应根据所设日期的值对星期寄存器适当初始化,后者的内容将随着日期的变更而自动加1(模7:0-6)。

● 将AT8563当万年历用

? AT8563只在月份/世纪寄存器最高位存放1比特的世纪信息,即0代表20xx 年,1代表19xx

年(其中“xx ”由年寄存器(08H )决定),根据其值由程序显示为21世纪或20世纪。也就是说,AT8563可进行1900-2099年的计时,除此之外的年份由于闰月规则的关系,日期无法保证准确性。

因此如果电路出现显示年份不在此世纪范围内的现象,必定是显示程序没有编写正确造成的。

● CLKOUT 或INT ———

引脚无输出 可尝试的处理办法:

? 有的可能需要这些引脚的输出信号实现某些功能,却发现它们并无输出。像这种情况,往

往是没有注意到CLKOUT 和INT ———

引脚均为OD 门输出所致。必须接上拉电阻方可得到需要的信号。另外,INT ———

引脚可能一直保持某个状态不变,这是由于控制/状态寄存器2(01H )

https://www.360docs.net/doc/c39719353.html,/

中的比特位设置不合适所致。如需要用到INT ———

引脚输出信号,请确保控制/状态寄存器2设置正确。

● 接上AT8563后系统除了显示时间外,几乎干不成任何事情 可尝试的处理办法:

? 这种情况明显是对AT8563的中断没有正确初始化造成的。INT ———

引脚由于不断送出中断信号,使得处理器不断运行中断服务子程序(以便访问AT8563的时间寄存器)。几乎没有空闲时间跳出中断服务子程序进行其它的操作。

● AT8563寄存器可以访问,但不走时 可尝试的处理办法:

? 寄存器可以访问,说明晶振可正常振荡,因此芯片必定在走时。但外观显得不走时,可能

是因为由于某种原因晶振停振,寄存器已无法访问,但程序编得不完善,没有考虑到这一情况,于是处理器一直等待,而先前的存放时间的变量因为一直未修改,或者显示器件自身带有显存,显存未改动,所以一直显示着先前的时间。

? 还有一种可能,就是芯片误进入了“加电复位失效模式”,而CLKOUT 引脚并未送入时钟

信号(该引脚在此模式下为输入引脚),或者控制/状态寄存器1(00H )的STOP 位(b5)为1,导致芯片无法走时。

3, AT8563 I 2C 上拉电阻设计考虑

I 2

C 上拉电阻主要取决于I 2

C 总线的上升时间要求。100/400KHz I 2

C 总线上升时间要求分别是1000ns/300ns 。τ=R*C ,其中R 为上拉电阻,C 为I 2

C 总线电容;对于I 2

C 总线电容预估如下:

对于3cm 长、0.5mm 宽的铜线,0.7mm 厚的PCB 板寄生电容Ctr

对于400 kHz I2C 总线,R400kHz=Tr/2C=300ns/(2*14.9pF)=10k Ω 对于100kHz I2C 总线,R100kHz=Tr/2C=1000ns/(2*14.9pF)= 33.3k Ω

时钟系统设计

《单片机原理及接口》 课程设计报告 题目:时钟系统设计 专业名称:电子信息工程 班级: 092 学号: 910706220 姓名: 2011年 12月

时钟系统设计 陈 (电子信息工程学系) 中文摘要:本设计基于单片机仿真技术,以单片机芯片AT89C52作为核心控制器,通过硬件电路的制作以及软件程序的编制,设计制作出一个多功能数字时钟系统。单片机扩展的LCD显示器用来显示秒、分、时计数单元中的值。整个设计包括两大部分:硬件部分和软件部分,以单片机为核心,蜂鸣器,数码管,晶体管等为外围器件,设计一个正常走时,报时、初始化、闹钟的数字时钟。 关键词:单片机;数字时钟;AT89C52;闹钟 1、设计目标 设计一时钟系统,系统具有时钟功能,能准确显示时、分、秒,系统还应具有校正功能:能够修改当前的时间。 2、设计环境 Windows7 Keil uVision3 Proteus7.5 3、系统硬件设计 3.1单片机控制系统: 本设计基于单片机技术原理,以单片机芯片AT89C52作为核心控制器,通过硬件电路的制作 以及软件程序的编制,利用单片机的控制作用通过LCD来直接时、分、秒,并能对其分别进行设 置、修改;利用对蜂鸣器的控制来实现闹钟功能。同时使用C语言程序来控制整个时钟显示,使 得编程变得更容易,这样通过三个模块:键盘、芯片、显示屏即可满足设计要求。 3.2各部分功能实现: 单片机采用52系列单片机。由ATMEL公司生产的AT89S52是一种低功耗、高性能CMOS8位微控 制器,具有8K在系统可编程Flash存储器。使用Atmel公司高密度非易失性存储器技术制造,与工 业80C51产品指令和引脚完全兼容。在单芯片上,拥有灵巧的8位CPU和在线系统可编程Flash,使 得AT89S52为众多嵌入式控制应用系统提供高灵活、有效的解决方案。AT89S52具有以下标准功能: 8K字节Flash,256字节RAM,32位I/O口线,2个数据指针,三个16位定时器/计数器,一个6向量2 级中断结构,全双工串行口,片内晶振及时钟电路。空闲模式下,CPU停止工作,允许RAM、定时 器/计数器、串口、中断继续工作。掉电保护方式下,RAM内容被保存,振荡器被冻结,单片机一 切工作停止,直到下一个中断或硬件复位为止。而且,它还具有一个看门狗(WDT)定时/计数器, 如果程序没有正常工作,就会强制整个系统复位,还可以在程序陷入死循环的时候,让单片机复

单片机课程设计-万年历、数字时钟

单片机课程设计-万年历、数字时钟 采用MAX7221可以极大的节省I/O口线,同时DS1302时钟芯片可以提供精确的时间信息 汇编语言程序编写 DSRST BIT P1.0 DSCLK BIT P1.1 DSIO BIT P2.2 DIN BIT P2.5 CS BIT P2.6 CLK BIT P2.7 D158 EQU 30H D70 EQU 31H ADDRESS EQU 32h CONTENT EQU 33h COMMAND EQU 34h SECOND equ 35h MINITE equ 36h HOUR equ 37h ORG 0000H LJMP MAIN ORG 0030H MAIN: LCALL INTI7221 LCALL INTI1302

LOOP: LCALL READ1302 LCALL CONVERT LCALL DELAY LCALL DISPLAY LCALL DELAY SJMP LOOP ;DS1302初始化 INTI1302:MOV ADDRESS, #8EH MOV CONTENT, #00H LCALL SENT_BYTE MOV ADDRESS, #90H MOV CONTENT, #0A7H ;慢充电寄存器LCALL SENT_BYTE READ1302: MOV ADDRESS, #81h LCALL REV_BYTE MOV SECOND, A MOV ADDRESS, #83h LCALL REV_BYTE MOV MINITE, A MOV ADDRESS, #85h LCALL REV_BYTE MOV HOUR, A RET SENT_BYTE: CLR DSRST CLR C NOP CLR DSCLK NOP SETB DSRST MOV A, ADDRESS MOV R3, #2 MOV R2, #8 LOOP0: RRC A MOV DSIO, C SETB DSCLK NOP CLR DSCLK DJNZ R2, LOOP0 MOV A, CONTENT MOV R2, #8 DJNZ R3, LOOP0 CLR DSRST RET

软件设计模式(JAVA)习题答案

软件设计模式(Java版)习题 第1章软件设计模式基础 1.1 软件设计模式概述 1.2 UML中的类图 1.3 面向对象的设计原则 一、名词解释 1.一个软件实体应当对扩展开放,对修改关闭,即在不修改源代码的基础上扩展 一个系统的行为。 2.一个对象应该只包含单一的职责,并且该职责被完整地封装在一个类中。 3.在软件中如果能够使用基类对象,那么一定能够使用其子类对象。 4.是一套被反复使用、多数人知晓的、经过分类编目的、代码设计经验的总结, 使用设计模式是为了可重用代码、让代码更容易被他人理解、保证代码可靠性。 二、单选择题 1.( A ) 2.( A ) 3. ( A ) 4. ( D ) 5. ( D ) 6.( A ) 7. ( D ) 8.( D ) 9.( D ) 10.( E ) 11.( C ) 12.( C ) 13. ( A ) 三、多选择题 1.( A、B、C、D ) 2. ( A、B ) 3.( A、D ) 4.( A、B、C、D ) 四、填空题 1.依赖倒转、迪米特法则、单一职责 2.模式名字、目的、问题、解决方案、效果、实例代码 3.超类、子类 4.开闭 5.用户 6.依赖倒转 7.组合/聚合 8.结构型、行为型 9.依赖倒转 10.开闭 11.需求收集是否正确、体系结构的构建是否合理、测试是否完全 12.人与人之间的交流 13.接口 14.名称、目的、解决方案 15.对象组合、类继承

16.对象组合 17.对象组合、类继承 18.抽象类的指针 五、简答题 1.答:设计模式按类型分为以下三类: 1)创建型设计模式:以灵活的方式创建对象集合,用于管理对象的创建。 2)结构型设计模式:将己有的代码集成到新的面向对象设计中,用于处理类或对象的组合。 3)行为型设计模式:用于描述对类或对象怎样交互和怎样分配职责。 2.答:设计模式的主要优点如下: 1)设计模式融合了众多专家的经验,并以一种标准的形式供广大开发人员所用,它提供了一套通用的设计词汇和一种通用的语言以方便开发人员之间沟通和交 流,使得设计方案更加通俗易懂。 2)设计模式使人们可以更加简单方便地复用成功的设计和体系结构,将已证实的技术表述成设计模式也会使新系统开发者更加容易理解其设计思路。设计模式使得重用成功的设计更加容易,并避免那些导致不可重用的设计方案。 3)设计模式使得设计方案更加灵活,且易于修改。 4)设计模式的使用将提高软件系统的开发效率和软件质量,且在一定程度上节约设计成本。 5)设计模式有助于初学者更深入地理解面向对象思想,一方面可以帮助初学者更加方便地阅读和学习现有类库与其他系统中的源代码,另一方面还可以提高软件的设计水平和代码质量。 3.答:设计模式一般有如下几个基本要素:模式名称、问题、目的、解决方案、效 果、实例代码和相关设计模式,其中的关键元素包括模式名称、问题、解决方案和效果。 4.答:正确使用设计模式具有以下优点: ⑴可以提高程序员的思维能力、编程能力和设计能力。 ⑵使程序设计更加标准化、代码编制更加工程化,使软件开发效率大大提高,从 而缩短软件的开发周期。 ⑶使设计的代码可重用性高、可读性强、可靠性高、灵活性好、可维护性强。 5.答:根据类与类之间的耦合度从弱到强排列,UML中的类图有以下几种关系:依赖关 系、关联关系、聚合关系、组合关系、泛化关系和实现关系。其中泛化和实现的耦合度相等,它们是最强的。

数字集成电路物理设计阶段的低功耗技术

数字集成电路物理设计阶段的低功耗技术 张小花(200XXXXXXXX) 2011年六月 摘要:通过一个图像处理SoC的设计实例,着重讨论在物理设计阶段降低CMOS功耗的方法。该方法首先调整 PAD摆放位置、调整宏单元摆放位置、优化电源规划,得到一个低电压压降版图,间接降低CMOS功耗;接着,通过规划开关活动率文件与设置功耗优化指令,直接降低CMOS功耗。最终实验结果表明此方法使CMOS功耗降低了 10.92%。基于该设计流程的图像处理SoC已经通过ATE设备的测试,并且其功耗满足预期目标。 关键词: 集成电路; 物理设计; 电压降; 低功耗 Digital integrated circuit physical design phase of the low power technology luo jiang nan(2008102041) June, 2011 Abstract: through a image processing of SoC design examples, the paper discuss the physical design stage reduce power consumption method. CMOS This method firstly PAD put the position, adjusting adjustment macro unit put the position, optimizing power planning, get a low voltage pressure drop, reduce the power consumption of the CMOS indirect territory; Then, through the planning activities rate documents and set switch power optimization, reduce the power consumption of the CMOS setup instructions directly. Finally the experimental results show that the method that CMOS power consumption was reduced by 10.92%. Based on the design process of the image processing has been through the ATE the SoC test equipment, and its power consumption to meet expectations. Keywords: IC; physical design; voltage drop; low power consumption 1 引言 随着集成电路规模的扩大以及便携式和嵌入式应用需求的增长,低功耗数字集成电路设计技术日益受到重视,已成为集成电路设计的研究热点.通常低功耗设计技术包括三个方面:设计中的低功耗技术、封装的低功耗技术和运行管理的低功耗技术.其中设计中的低功耗技术包括前端设计阶段的 体系结构级低功耗技术、RTL级低功耗技术、门级低功耗技术和物理设计阶段的低功耗 技术.

最全最好的课程设计-51单片机电子日历时钟( 含源程序)

LED日历时钟课程设计 院系: 班级: 姓名: 学号: 指导教师: 2012 年06 月16 日

目录

摘要 单片机自20世纪70年代问世以来,以其极高的性能价格比,受到人们的重视和关注,应用很广、发展很快。单片机体积小、重量轻、抗干扰能力强、环境要求不高、价格低廉、可靠性高、灵活性好、开发较为容易。由于具有上述优点,在我国,单片机已广泛地应用在工业自动化控制、自动检测、智能仪器仪表、家用电器、电力电子、机电一体化设备等各个方面,而51单片机是各单片机中最为典型和最有代表性的一种。这次毕业设计通过对它的学习、应用,以AT89S51芯片为核心,辅以必要的电路,设计了一个简易的电子时钟,它由4.5V直流电源供电,通过数码管能够准确显示时间,调整时间,从而到达学习、设计、开发软、硬件的能力。 第一章前言 数字电子钟具有走时准确,一钟多用等特点,在生活中已经得到广泛的应用。虽然现在市场上已有现成的电子钟集成电路芯片,价格便宜、使用也方便,但是人们对电子产品的应用要求越来越高,数字钟不但可以显示当前的时间,而且可以显示期、农历、以及星期等,给人们的生活带来了方便。另外数字钟还具备秒表和闹钟的功能,且闹钟铃声可自选,使一款电子钟具备了多媒体的色彩。单片机具有体积小、功能强可靠性高、价格低廉等一系列优点,不仅已成为工业测控领域普遍采用的智能化控制工具,而且已渗入到人们工作和和生活的各个角落,有力地推动了各行业的技术改造和产品的更新换代,应用前景广阔。 时钟电路在计算机系统中起着非常重要的作用,是保证系统正常工作的基础。在一个单片机应用系统中,时钟有两方面的含义:一是指为保障系统正常工作的基准振荡定时信号,主要由晶振和外围电路组成,晶振频率的大小决定了单片机系统工作的快慢;二是指系统的标准定时时钟,即定时时间,它通常有两种实现方法:一是用软件实现,即用单片机内部的可编程定时/计数器来实现,但误差很大,主要用在对时间精度要求不高的场合;二是用专门的时钟芯片实现,在对时间精度要求很高的情况下,通常采用这种方法,典型的时钟芯片有:DS1302,DS12887,X1203等都可以满足高精度的要求。 AT89S51是一个低功耗,高性能CMOS 8位单片机,片内含4k B ytes ISP(In-system programmable)的可反复擦写1000次的Flash只读程序存储器,器件采用ATMEL公司的高密度、非易失性存储技术制造,兼容标准MCS-51指令系统及80C51引脚结构,芯片内集成了通用8位中央处理器和ISP Flash存储单元,功能强大的微型计算机的AT89S51可为许多嵌入式控制应用系统提供高性价比的解决方案。 AT89S51具有如下特点:40个引脚,4k Bytes Flash片内程序存储器,128 bytes的随机存取数据存储器(RAM),32个外部双向输入/输出(I/O)口,5个中断优先级2层中断嵌套中断,2个16位可编程定时计数器,2个全双工串行通信口,看门狗(WDT)电路,片内时钟振荡器。

ARM低功耗设计_全面OK

嵌入式系统中的低功耗设计 2008-12-31 18:19:55 作者:电子之都来源:电子之都浏览次数:59 网友评论 0 条 经过近几年的快速发展,嵌入式系统(Embedded system)已经成为电子信息产业中最具增长力的一个分支。随着手机、PDA、GPS、机顶盒等新兴产品的大量应用,嵌入式系统的市场正在以每年30%的速度递增(IDC预测),嵌入式系统的设计也成为软硬件工程师越来越关心的话题。 在嵌入式系统的设计中,低功耗设计(Low-Power Design)是许多设计人员必须面对的问题,其原因在于嵌入式系统被广泛应用于便携式和移动性较强的产品中去,而这些产品不是一直都有充足的电源供应,往往是靠电池来供电,所以设计人员从每一个细节来考虑降低功率消耗,从而尽可能地延长电池使用时间。事实上,从全局来考虑低功耗设计已经成为了一个越来越迫切的问题。 那么,我们应该从哪些方面来考虑低功耗设计呢?笔者认为应从以下几方面综合考虑: 1.处理器的选择 2.接口驱动电路设计 3.动态电源管理 4.电源供给电路的选择 下面我们分别进行讨论: 一、处理器的选择 我们对一个嵌入式系统的选型往往是从其CPU和操作系统(OS)开始的,一旦这两者选定,整个大的系统框架便选定了。我们在选择一个CPU的时候,一般更注意其性能的优劣(比如时钟频率等)及所提供的接口和功能的多少,往往忽视其功耗特性。但是因为CPU 是嵌入式系统功率消耗的主要来源---对于手持设备来讲,它几乎占据了除显示屏以外的整

个系统功耗的一半以上(视系统具体情况而定),所以选择合适的CPU对于最后的系统功耗大小有举足轻重的影响。 一般的情况下,我们是在CPU的性能(Performance)和功耗(Power Consumption)方面进行比较和选择。通常可以采用每执行1M次指令所消耗的能量来进行衡量,即Watt/M IPS。但是,这仅仅是一个参考指标,实际上各个CPU的体系结构相差很大,衡量性能的方式也不尽相同,所以,我们还应该进一步分析一些细节。 我们把CPU的功率消耗分为两大部分:内核消耗功率PCORE和外部接口控制器消耗功率PI/O,总的功率等于两者之和,即P=PCORE+PI/O。对于PCORE,关键在于其供电电压和时钟频率的高低;对于PI/O来讲,除了留意各个专门I/O控制器的功耗外,还必须关注地址和数据总线宽度。下面对两者分别进行讨论: 1、CPU供电电压和时钟频率 我们知道,在数字集成电路设计中,CMOS电路的静态功耗很低,与其动态功耗相比基本可以忽略不计,故暂不考虑。其动态功耗计算公式为: Pd=CTV2f 式中,Pd---CMOS芯片的动态功耗 CT----CMOS芯片的负载电容 V----CMOS芯片的工作电压 f-----CMOS芯片的工作频率 由上式可知,CMOS电路中的功率消耗是与电路的开关频率呈线性关系,与供电电压呈二次平方关系。对于一颗CPU来讲,Vcore电压越高,时钟频率越快,则功率消耗越大。所以,在能够满足功能正常的前提下,尽可能选择低电压工作的CPU能够在总体功耗方面得到

网络时钟系统方案设计

时钟系统 技术方案 烟台北极星高基时间同步技术有限公司 2012年3月

第一部分:时钟系统技术方案 一、时钟系统概述 1.1概述 根据办公楼的实际情况,特制定如下施工设计方案: 时钟系统主要由GPS接收装置、中心母钟、二级母钟(中继器)、全功能数字显示子钟、、传输通道和监测系统计算机组成。 系统中心母钟设在中心机房内,其他楼各设备间设置二级母钟,在各有关场所安装全功能数字显示子钟。 系统中心母钟接收来自GPS的标准时间信号,通过传输通道传给二级母钟,由二级母钟按标准时间信号指挥子钟统一显示时间;系统中心母钟还通过传输系统将标准时间信号直接传给各个子钟,为楼宇工作人员提供统一的标准时间 二、时钟系统功能 根据本工程对时钟系统的要求,时钟系统的功能规格如下: 时钟系统由GPS校时接收装置(含防雷保护器)、中心母钟、扩容接口箱、二级母钟、数字式子钟、监控终端(也称监测系统计算机)及传输通道构成。其主要功能为: ☉显示统一的标准时间信息。 ☉向其它需要统一时间的系统及通信各子系统网管终端提供标准时间信息。 2.1 中心母钟 系统中心母钟设置在控制中心设备室内,主要功能是作为基础主时钟,自动接收GPS的标准时间信号,将自身的精度校准,并分配精确时间信号给子钟,二级母钟和其它需要标准时间的设备,并且通过监控计算机对时钟系统的主要设备进行监控。 中心母钟主要由以下几部分组成: ☉标准时间信号接收单元 ☉主备母钟(信号处理单元) ☉分路输出接口箱 ☉电源 中心母钟外观示意图见(附图) 2.1.1标准时间信号接收单元 标准时间信号接收单元是为了向时间系统提供高精度的时间基准而设置的,用以实现时间系统的无累积误差运行。 在正常情况下,标准时间信号接收单元接收来自GPS的卫星时标信号,经解码、比对后,经由RS422接口传输给系统中心母钟,以实现对母钟精度的校准。 系统通过信号接收单元不断接收GPS发送的时间码及其相关代码,并对接收到的数据进行分析,判断这些数据是否真实可靠。如果数据可靠即对母钟进行校对。如果数据不可靠便放弃,下次继续接收。

集成电路的功耗优化和低功耗设计技术

集成电路的功耗优化和低功耗设计技术 摘要:现阶段各行业的发展离不开对能源的消耗,随着目前节能技术要求的不 断提升,降低功耗成为行业发展的重要工作之一。本文围绕集成电路的功耗优化 以及低功耗设计技术展开分析,针对现阶段常见的低功耗设计方式以及技术进行 探究,为集成电路功耗优化提供理论指导。 关键词:集成电路;功耗优化;低功耗 目前现代节能技术要求不断提升,针对设备的功耗控制成为当前发展的主要问题之一。 针对数字系统的功耗而言,决定了系统的使用性能能否得到提升。一般情况下,数字电路设 计方面,功耗的降低一直都是优先考虑的问题,并且通过对整个结构进行分段处理,同时进 行优化,最后总结出较为科学的设计方案,采用多种方式降低功耗,能够很大程度上提升设 备的使用性能。下面围绕数字电路的功耗优化以及低功耗设计展开分析。 一、设计与优化技术 集成电路的功耗优化和低功耗设计是相对系统的内容,一定要在设计的每个环节当中使 用科学且合理的技术手段,权衡并且综合考虑多方面的设计策略,才能够有效降低功耗并且 确保集成电路系统性能。因为集成电路系统的规模相对较大且具有一定的特殊性,想要完全 依靠人工或者手动的方式来达到这些目的并不现实且缺少可行性,一定要开发与之对应的电 路综合技术。 1 工艺级功耗优化 将工艺级功耗应用到设计当中,通常情况下采取以下两种方式进行功耗的降低: 首先,根据比例调整技术。进行低功耗设计过程中,为了能够实现功耗的有效降低会利 用工艺技术进行改善。在设计过程中,使用较为先进的工艺技术,能够让设备的电压消耗有 效缩减。现阶段电子技术水平不断提升,系统的集成度也随之提高,目前采用的零件的规格 也逐渐缩小,零件的电容也实现了良好的控制,进而能够很大程度上降低功耗。借助比例技术,除了能够将可见晶体管的比例进行调整,而且也能够缩小互连线的比例[1]。目前在晶体 管的比例缩小方面,能够依靠缩小零件的部分重要参数,进而在保持性能不被影响的情况下,通过较小的沟道长度,确保其他的参数不受影响的栅压缩方式,进而将零件的体积进行缩减,同时也缩短了延长的用时,使功耗能够有效降低。针对互连线缩小的方式主要将互连线的整 个结构进行调整,工作人员在进行尺寸缩减的过程中,会面临多方面的难题,比如系统噪音 无法控制,或者降低了电路使用的可靠性等等。 其次,采用封装技术进行降低。采用封装技术,能够让芯片与外部环境进行有效的隔离,进而避免了外部环境给电气设备造成一定的破坏与影响,在封装阶段,芯片的功耗会受到较 大的影响,因此需要使用更加有效的封装手段,才能够提升芯片的散热性,进而有效降低功 耗[2]。在多芯片的情况下,因为芯片与其他芯片之间的接口位置会产生大量的功耗,因此针 对多芯片采取封装技术,首先降低I/0接口的所有功能,接着解决电路延迟的问题,才能够 实现对集成电路的优化。 2 电路功耗优化 一般情况下,对电路级的功耗会选择动态的逻辑设计。在集成电路当中,往往会包含多 种电路逻辑结构,比如动态、静态等等,逻辑结构从本质上而言具有一定的差异性,这种差 异性也使得逻辑结构有着不同作用的功能。动态逻辑结构有着较为典型的特性[3]。静态的逻 辑结构当中所有的输入都会对接单独的MOS,因此逻辑结构功耗更大,动态的逻辑结构当中 电路通常具备N、M两个沟道,动态电路会利用时钟信号采取有效的控制,进而能够实现预

dsp时钟日历课程设计

课程设计说明书(本科) 题目: 时钟日历 姓名: 专业: 电子信息工程 班级: 09级一班 2012年 6 月

目录 摘要 (1) 一、硬件设计 (1) 1、硬件方案设计 (1) 2、单元电路设计 (2) 3、电路原理图 (5) 4、硬件调试 (6) 二、软件设计 (6) 1、系统分析 (6) 2、软件系统设计 (7) 3、软件代码实现 (9) 4、软件调试 (24) 四、课程设计体会总结 (24) 五、参考文献 (24)

时钟日历 摘要:课程设计的主要目的是用tms320f2812芯片为核心控制部件,设计一个能用LCD液 晶显示屏显示当前年,月,日,时,分,秒以及星期的具有电子时钟功能的万年历。 ⑴学习并了解ICETEK-F2812-A板及教学实验箱的使用; ⑵学习DSP芯片的I/O端口的控制方法; ⑶熟悉字模的简单构建和使用; ⑷熟悉Emulator方式下的程序调试规程,并最终能够熟练掌握在DSP软硬件环境下 的程序开发流程;能够对现有器件进行简单地编程,实现各种简单地显示控制。 关键词:dsp 时钟日历 一、硬件设计 1、硬件方案设计 本系统以TMS2812为核心控制部件,利用软件编程,通过DS1302进行时钟控制,使用12864 LCD液晶显示器进行时钟显示,能实现题目的基本要求,尽量做到硬件电路简单稳定,减小电磁干扰和其他环境干扰,充分发挥软件编程的优点,减小因元器件精度不够引起的误差。由于时间有限和本身知识水平的发挥,我们认为本系统还有需要改进和提高的地方,例如选用更高精度的元器件,硬件电路更加精确稳定,软件测量算法进一步的改进与完善等。总体框图如图1所示。 GND +5V ADD PWM4 PWM3 VSS PWM2 V0 IOPA7 IOPA6 IOPA5 REST IOPA4 IOPA3 OSCBYP TXAL1 TXAL2 IOPB0- IOPB7 E CS1 CS2 R/W RS DB0-DB7 RST I/O SCLK VCC1/VCC2 X1/X2 GND 复位电路 OSCBYP为高电平。采 用内部振荡 双电源 32768hz 10K DS1302

软件体系结构与设计模式期末复习

体系结构期末复习 一、选择题 (一) 1. 设计模式的基本原理是( C ) A. 面向实现编程 B. 面向对象编程 C. 面向接口编程 D. 面向组合编程 2. 设计模式的两大主题是( D ) A. 系统的维护与开发 B. 对象组合与类的继承 C. 系统架构与系统开发 D. 系统复用与系统扩展 3. 依据设计模式思想,程序开发中应优先使用的是( A )关系实现复用。 A. 组合聚合 B. 继承 C. 创建 D. .以上都不对 4. 关于继承表述错误的是( D ) A. 继承是一种通过扩展一个已有对象的实现,从而获得新功能的复用方法。 B. 泛化类(超类)可以显式地捕获那些公共的属性和方法。特殊类(子类)则通过 附加属性和方法来进行实现的扩展。 C. 破坏了封装性,因为这会将父类的实现细节暴露给子类。 D. 继承本质上是“白盒复用”,对父类的修改,不会影响到子类。 5. 常用的设计模式可分为( A ) A. 创建型、结构型和行为型 B. 对象型、结构型和行为型 C. 过程型、创建型和结构型 D. 抽象型、接口型和实现型 6. “不要和陌生人说话”是对( D )设计原则的通俗表述。 A. 接口隔离 B. 里氏代换 C. 依赖倒转 D. .迪米特法则 7. 在适配器模式中,对象适配器模式是对( A )设计原则的典型应用 A. 合成聚合 B. 里氏代换 C. 依赖倒转 D. .迪米特法则 8. 将一个类的接口转换成客户希望的另一个接口,这句话是对(C)设计模式的描述 A. 策略模式 B. 桥接模式 C. 适配器模式 D. 单例模式 9. 以下设计模式中属于结构模式的是( D ) A. 观察者模式 B. 单例模式 C. 策略模式 D. 外观模式 10. 以下不属于对象行为型模式是( D ) A. 命令模式 B. 策略模式 C. 访问者模式 D. 桥接模式 11. 下面的类图表示的是哪个设计模式( D ) A. 抽象工厂模式 B. 观察者模式 C. 策略模式 D. 桥接模式

常用低功耗设计

随着半导体工艺的飞速发展和芯片工作频率的提高,芯片的功耗迅速增加,而功耗增加又将导致芯片发热量的增大和可靠性的下降。因此,功耗已经成为深亚微米集成电路设计中的一个非常重要的考虑因素。为了使产品更具有竞争力,工业界对芯片设计的要求已从单纯的追求高性能、小面积,转换为对性能、面积、功耗的综合要求。微处理器作为数字系统的核心部件,其低功耗设计对降低整个系统的功耗具有非常重要的意义。 本文首先介绍了微处理器的功耗来源,重点介绍了常用的低功耗设计技术,并对今后低功耗微处理器设计的研究方向进行了展望。 1 微处理器的功耗来源 研究微处理器的低功耗设计技术,首先必须了解其功耗来源。高层次仿真得出的结论如图1所示。 从图1中可以看出,时钟单元(Clock)功耗最高,因为时钟单元有时钟发生器、时钟驱动、时钟树和钟控单元的时钟负载;数据通路(Datapath)是仅次于时钟单元的部分,其功耗主要来自运算单元、总线和寄存器堆。除了上述两部分,还有存储单元(Mem ory),控制部分和输入/输出 (Control,I/O)。存储单元的功耗与容量相关。 如图2所示,C MOS电路功耗主要由3部分组成:电路电容充放电引起的动态功耗,结反偏时漏电流引起的功耗和短路电流引起的功耗。其中,动态功耗是最主要的,占了总功耗的90%以上,表达式如下: 式中:f为时钟频率,C1为节点电容,α为节点的翻转概率,Vdd为工作电压。

2 常用的低功耗设计技术 低功耗设计足一个复杂的综合性课题。就流程而言,包括功耗建模、评估以及优化等;就设计抽象层次而言,包括自系统级至版图级的所有抽象层次。同时,功耗优化与系统速度和面积等指标的优化密切相关,需要折中考虑。下面讨论常用的低功耗设计技术。 2.1 动态电压调节 由式(1)可知,动态功耗与工作电压的平方成正比,功耗将随着工作电压的降低以二次方的速度降低,因此降低工作电压是降低功耗的有力措施。但是,仅仅降低工作电压会导致传播延迟加大,执行时间变长。然而,系统负载是随时间变化的,因此并不需要微处理器所有时刻都保持高性能。动态电压调节DVS (Dynarnic Voltage Scaling)技术降低功耗的主要思路是根据芯片工作状态改变功耗管理模式,从而在保证性能的基础上降低功耗。在不同模式下,工作电压可以进行调整。为了精确地控制DVS,需要采用电压调度模块来实时改变工作电压,电压调度模块通过分析当前和过去状态下系统工作情况的不同来预测电路的工作负荷。 2.2 门控时钟和可变频率时钟 如图1所示,在微处理器中,很大一部分功耗来自时钟。时钟是惟一在所有时间都充放电的信号,而且很多情况下引起不必要的门的翻转,因此降低时钟的开关活动性将对降低整个系统的功耗产牛很大的影响。门控时钟包括门控逻辑模块时钟和门控寄存器时钟。门控逻辑模块时钟对时钟网络进行划分,如果在当前的时钟周期内,系统没有用到某些逻辑模块,则暂时切断这些模块的时钟信号,从而明显地降低开关功耗。图3为采用“与”门实现的时钟控制电路。门控寄存器时钟的原理是当寄存器保持数据时,关闭寄存器时钟,以降低功耗。然而,门控时钟易引起毛刺,必须对信号的时序加以严格限制,并对其进行仔细的时序验证。 另一种常用的时钟技术就是可变频率时钟。根据系统性能要求,配置适当的时钟频率,避免不必要的功耗。门控时钟实际上是可变频率时钟的一种极限情况(即只有零和最高频率两种值),因此,可变频率时钟比门控时钟技术更加有效,但需要系统内嵌时钟产生模块PLL,增加了设计复杂度。去年Intel公司推出的采用先进动态功耗控制技术的Montecito处理器,就利用了变频时钟系统。该芯片内嵌一个高精度数字电流表,利用封装上的微小电压降计算总电流;通过内嵌的一个32位微处理器来调整主频,达到64级动态功耗调整的目的,大大降低了功耗。

电子时钟系统设计

《嵌入式系统》课程设计说明书 电子时钟系统 院部: 学生姓名: 指导教师:职称 专业: 班级: 学号:

湖南工学院嵌入式系统课程设计课题任务书 2.显示的时间为开发板当前的系统时间,显示的结果随着系统时间变化而变 I

摘要 嵌入式操作系统是一种支持嵌入式系统应用的操作系统软件,它是嵌入式系统( 包括硬、软件系统) 极为重要的组成部分,通常包括与硬件相关的底层驱动软件、系统内核、设备驱动接口、通信协议、图形界面、标准化浏览器等Browser 。嵌入式操作系统具有通用操作系统的基本特点,如能够有效管理越来越复杂的系统资源;能够把硬件虚拟化,使得开发人员从繁忙的驱动程序移植和维护中解脱出来;能够提供库函数、驱动程序、工具集以及应用程序。与通用操作系统相比较,嵌入式操作系统在系统实时高效性、硬件的相关依赖性、软件固态化以及应用的专用性等方面具有较为突出的特点。嵌入式技术已成为信息产业中发展最快、应用最广的计算机技术之一,并被广泛应用于网络通信、消费电子、医疗电子、工业控制和交通系统等领域。 本次设计采用QT程序开发框架开发的模拟时钟程序,使用Linux系统到嵌入式终端移植和交叉编译环境搭建,最终成功实现了在嵌入式终端的运行。 关键词:嵌入式系统;QT;模拟时钟;Linux系统

目录 1绪论 (1) 1.1 设计背景 (2) 1.2 设计目的和意义 (2) 2 嵌入式Linux系统 (2) 2.1 嵌入式Linux概念 (2) 2.2 嵌入式Linux组成 (2) 3 Qt工具 (3) 3.1 Qt简介 (3) 3.2 Qt优点 (3) 4 模拟时钟的设计 (4) 4.1 代码的编写 (4) 4.2 代码的调试与运行 (4) 5 模拟时钟到开发板的下载 (6) 5.1 交叉编译环境的构建 (7) 5.2 模拟时钟到开发板的下载运行 (7) 结论 (10) 参考文献 (11) 致谢 (12) 附录 (13)

日历时钟单片机课程设计

单片机课程设计 ——日历时钟与键盘显示程序设计 姓名:管曌 学号:3081109003 班级:J通信0801 指导老师:熊书明

日历时钟与键盘显示程序设计 一、设计目的 (1)能在LED显示器上实现正常的时分秒计时 (2)能通过键盘输入当前时间,并从该时间开始计时 (3)有校时、校分功能 (4)有报时功能,通过指示灯表示 (5)有闹时功能,闹时时间可以设定,通过指示灯表示 二、设计内容 该课程设计是利用MCS-51单片机内部的定时/计数器、中断系统、以及行列键盘和LED显示器等部件,设计一个单片机电子时钟。设计的电子时钟通过数码管显示,并能通过按键实现设置时间和暂停、启动控制等。 三、MCS-51单片机系统简介 单片机应用系统由硬件系统和软件系统两部分组成。硬件系统是指单片机以及扩展的存储器、I\O接口、外围扩展的功能芯片以及接口电路。软件系统包括监控程序和各种应用程序。 在单片机应用系统中,单片机是整个系统的核心,对整个系统的信息输入、处理、信息输出进行控制。与单片机配套的有相应的复位电路、时钟电路以及扩展的存储器和I\O接口,使单片机应用系统能够运行。 在一个单片机应用系统中,往往都会输入信息和显示信息,这就涉及键盘和显示器。在单片机应用系统中,一般都根据系统的要求配置相应的键盘和显示器。配置键盘和显示器一般都没有统一的规定,有的系统功能复杂,需输入的信息和显示的信息量大,配置的键盘和显示器功能相对强大,而有些系统输入/输出的信息少,这时可能用几个按键和几个LED指示灯就可以进行处理了。在单片机应用系统在中配置的键盘可以是独立键盘,也可能是矩阵键盘。显示器可以是LED指示灯,也可以是LED数码管,也可以是LCD显示器,还可以使用CRT显示器。单片机应用系统中键盘一般用的比较多的是矩阵键盘,显示器用的比较多的是LED数码管还LCD显示器。 四、设计方案

ASIC低功耗设计

三、低功耗技术 1. 功耗分析 (1)由于电容的充放电引起的动态功耗 V DD C l i VDD v out 图(20)充放电转换图 如图(20)所示:PMOS 管向电容L C 充电时,电容的电压从0上升到DD V ,而这些能量来 自于电源。一部分能量消耗在PMOS 管上,而剩余的则保存在电容里。从高电压向低转换的过程中,电容放电,电容中储存的能量消耗在NMOS 管上。 我们来推导一下:考虑从低电压转换到高电压的情况,NMOS 和PMOS 不同时导通。在转换过程中电源提供的能量为C E ,而是转换后储存在电容里的能量。 ???====∞∞VDD DD L out DD L out L DD VDD VDD V C dv V C dt dt dv C V dt t i E 0 002)( ???====∞∞VDD DD L out out L out out L out VDD C V C dv v C dt v dt dv C dt v t i E 02002 )( 这两个等式说明电源提供的能量只有一半储存在电容里。另一半被PMOS 管消耗掉了。 为了计算总体能量消耗,我们不得不考虑器件的翻转。如果门每秒钟翻转10?→? f 次,那么 102 ?→?=f V C P DD L dyn 10?→?f 表示能量消耗的翻转频率。 随着数字电路集成度的提高,能量问题将成为人们关注的焦点。从以上分析看出,dyn P 跟电源电压的平方成正比,因此降低供电电压对降低功耗有非常显著的意义。 但是,降低供电电压对电路性能有一定的影响,这时我们可以考虑减小有效电容和减少翻转率。电容主要是由于晶体管的门和扩散电容引起的,因此降低由于电容的充放电引起的动态功耗方法之一是将晶体管设计得尽可能小,这种方法同样对提高电路的性能有很大的帮助。

日历时钟单片机课程设计(附汇编程序+方案图+模块图+ddb模拟图)

;山东科技大学信电通信07-1 lfj 作品lifaji@https://www.360docs.net/doc/c39719353.html, 方案一:

方案二:

采用方案二。模块图

; ------------------------- 按键说明-------------------------;--------------------------1键——进入可调状态-------------------------; -------------------------2键——结束返回-------------------------; -------------------------3键——秒加1/日加1 -------------------------; -------------------------4键——分加1/月加1 -------------------------; -------------------------5键——显示24小时制/时加1/年加1-------------------------; -------------------------6键——显示12小时制-------------------------; -------------------------7键——可调时间-------------------------; -------------------------8键——可调日期-------------------------CLK BIT P1.6 ;时钟信号端 DISP BIT P1.7 ;串出锁存端 DBUF EQU 30H ;秒的最低位地址 LED BIT P1.1 CHANGE2 BIT 21H ;加12的标志位 AD1 EQU 40H ;秒 AD2 EQU 41H ;分 AD3 EQU 42H ;时 AD4 EQU 43H ;天 AD5 EQU 44H ;月 AD6 EQU 45H ;年 ; 初始化存储单元结束 ORG 0000H LJMP MAIN ORG 000BH ;T0中断入口 LJMP INT ORG 0030H MAIN: MOV R0,#AD1 MOV R7,#06H LOOP0: MOV A,#00H MOV @R0,A INC R0 DJNZ R7,LOOP0 ;R0~R7清零 MOV AD1,#37H MOV AD2,#22H MOV AD3,#0CH MOV AD4,#08H MOV AD5,#08H MOV AD6,#08H ;初始化时间为12:34:56,日期为08年08月08日 MOV IE,#82H ;允许T0中断

软件设计模式及其使用

龙源期刊网 https://www.360docs.net/doc/c39719353.html, 软件设计模式及其使用 作者:罗兴荣 来源:《数字技术与应用》2013年第04期 摘要:在计算机软件快速发展的今天,软件设计模式在计算机程序设计的运用中越来越重要。软件设计模式按其完成工作的种类可分为了创建型的模式、结构型的模式以及行为型的模式。在实际应用中根据分析研究问题的结果选择和使用合适的软件设计模式。 关键词:软件设计设计模式模式分类模式选择模式使用 中图分类号:P631 文献标识码:A 文章编号:1007-9416(2013)04-0194-01 关于模式这个概念,最早的时候是在城市建筑领域当中出现的,而Christopher Alexander[1]所写的一本关于建筑的书中对模式这一概念有明确的定义,其大概含义是说每一个模式都是描述我们周围发生的事情,并对发生的问题进行合理的解释,使得利用这个模式就可以重复的解决类似的问题。Christopher Alexander利用他所得出的模式这个概念解决了建筑领域中的一些问题,模式这一概念发展到现在,已经逐渐成为计算机领域当中独有的概念了。 1 软件设计模式分类 对软件设计模式的分类有许多不同的方法,在这里主要是根据模式在计算机软件设计中能够完成何种种类的工作来决定的,大致可以分为创建型的模式、结构型的模式以及行为型的模式这三种类型。而当模式运用于不同因素的时候又可以分为不同的类型,运用于类的时候可以分为类模式,运用于对象的时候可以分为对象模式。所谓类模式就是处理系统中的类与子类之间关系的模式,这些关系可以通过继承的形式来建立,静态的类模式在进行编译的时候便要确定下来;所谓对象模式,就是处理对象之间关系的模式,这些关系在系统运行的时候是能够不断变化的,所以对象模式是动态的模式。 第一,创建型的软件设计模式。创建型的设计模式是和对象的创建有着十分必然的关系,也就是说,在描述创建对象的时候,要将对象创建过程的具体细节进行隐藏设计,使得系统程序代码能够不依赖具体的对象。所以当我们需要在系统中增加一个新的对象的时候,是不需要修改系统的源代码的。创建型的类模式需要将对象当中的部分在子类当中进行延迟性的创建工作,而创建型的对象模式则是将对象的部分在另一个对象中进行延迟性的创建。 第二,结构型的软件设计模式。结构型的软件设计模式是处理类的和处理对象的设计模式的组合形式,也就是能够描述类与对象之间的大的结构如何组建起来,并且在组建之后还能够拥有新的功能的一种模式。结构型的类模式是采用继承性的机制来对类进行组合。而结构型的对象模式则是能够描述对象之间的组装方式。

低功耗物门控时钟的三种功耗分析

低功耗物门控时钟的三种功耗分析 电路在功能仿真通过后,开始进行寄存器级综合。采用高阈值标准单元库和多级门控时钟技术相结合,在RTL阶段插入门控时钟单元,并在布局布线时在IC Comp iler中进行了基于门控时钟的布局布线优化,布局布线正确完成仿真通过后,在PT中做静态时序分析并进行最终的功耗分析。 1、时钟门控的RTL级实现 在RTL级,门控时钟的实现不需要对设计本身进行修改,而只需在综合脚本中加入一些控制项。 控制项set_clock_gating_ STyle是门控时钟的核心。它的参数大小决定门控时钟的质量,对功耗的优化效果和对CTS的影响。目前尚无完备的体系介绍如何设置控制项以使门控效果达到最优。 首先确定时序单元的类型。为了避免非Latch单元易产生毛刺的缺点,此处选定时序单元的类型为Latch。由于库中提供基于锁存器的门控单元,固正边沿逻辑positive_edge_ logic采用工艺库提供的专用单元。采用集成单元的优势在于不仅不需要设置门控单元输入端建立时间和保持时间,因为集成单元的时序信息在单元库中已有说明,而且有效缓解了插入门控单元对延时带来的不利影响。

fanout的大小对功耗和时序都有影响。数值越大则表示一个门 控单元可承受较多的负载,即代表越节省功耗,需要的门控单元也越少,但对门控单元输入端建立时间的要求也就更加严格。位宽决定一组寄存器能被门控的最小宽度。级数则确定多级门控时钟的最大级数。这三个参数主要是依据设计本身对功耗的要求,结合综合时的时序约束和单元库中门控单元的时延信息加以估计,确定一个粗略的数值范围。 2、时钟门控的版图级实现 在布局布线阶段,基于门控时钟的功耗优化流程主要如下:在布 局之前,设置set_power_op tiONs–clock_gating true,之后在布局、时钟树综合和布线阶段的主要命令中添加选项- power即可。设置可实现最基本的门控时钟布局布线,但在设计中生成的时钟网络分布不均匀,而且skew很大。需要采取额外的优化措施来消除其带来的不利影响。 门控单元的加入给CTS带来的影响主要有两个方面,一方面会 造成整个时钟网络分布不平衡,另一方面导致时钟偏移增大。单采用上述措施,时钟偏移最大可达到1. 11,严重偏离了不采用门控时钟时的偏移量0. 12。在优化时钟偏移上,目标有三个方面:构造一个 相对平衡的时钟网络,使得在各个层上,层的各个分支上的单元数目相近;减小时钟偏移至可承受范围;尽量保持功耗同只采用门控时钟 而不优化时钟偏移状况下的功耗相近或更小。