modelsim仿真详细过程

由于我们只需要了解仿真的完整过程,所以不需要自己写源文件和测试文件(也称为testbench)。一下就是简单的源文件和测试文件(亲自测试过)。

//源文件

module compare(equal,a,b);

input a,b;

output equal;

assign equal=(a==b)?1:0;

endmodule

//测试文件

`timescale 1ns/1ns

`include"./compare.v"

module comparetest;

reg a,b;

wire equal;

initial

begin

a=0;

b=0;

#100 a=0;b=1;

#100 a=1;b=1;

#100 a=1;b=0;

#100 $stop;

end

compare compare1(.equal(equal),.a(a),.b(b));

endmodule

有了源文件和测试文件下面就开始用modelsim进行仿真了。

步骤一:新建工程和.v文件(也就是源文件和测试文件)

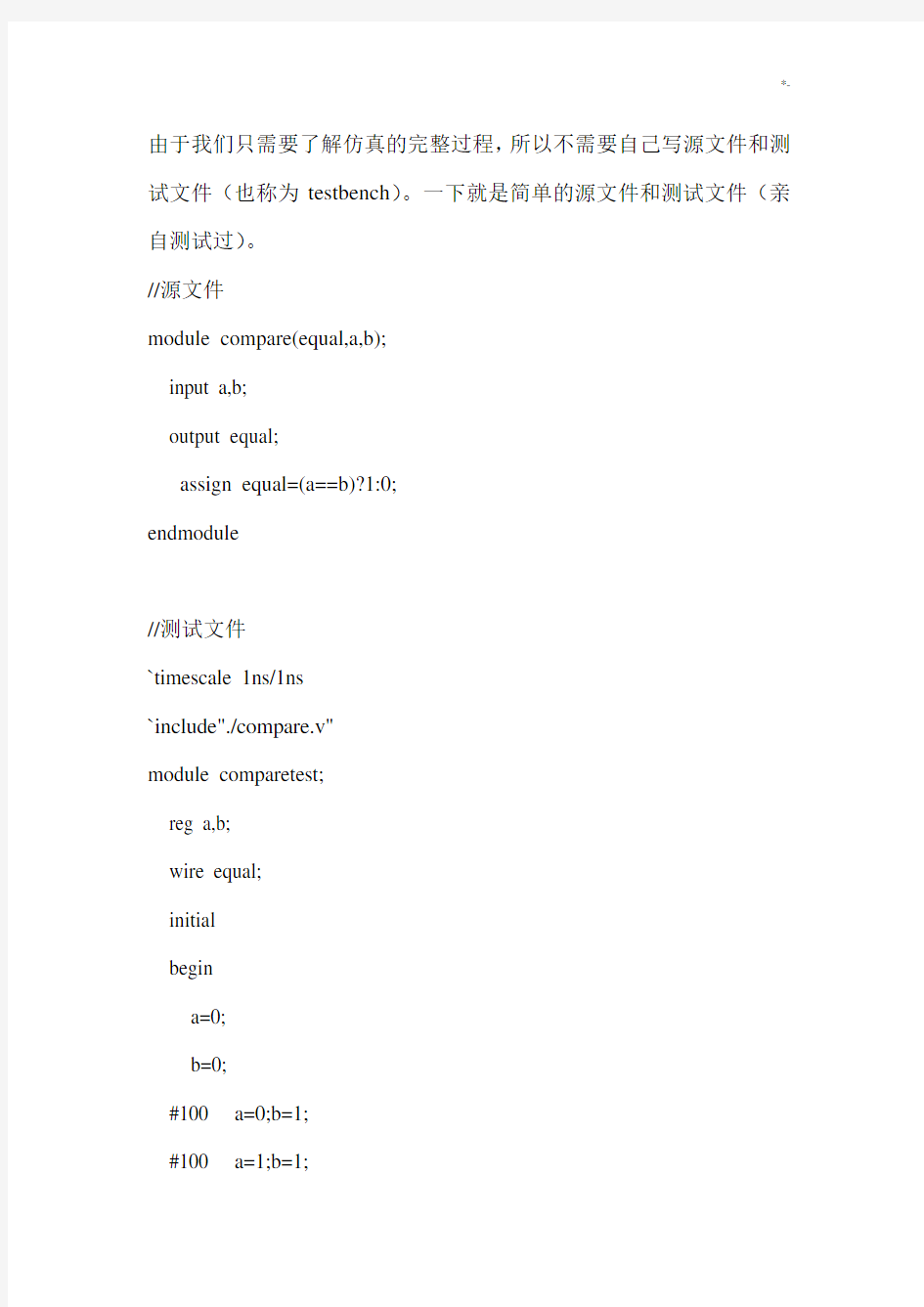

打开modelsim软件,点击file,选择new—>project 然后就会弹出下面窗口:

然后在project name那一栏写上工程名(随便去,一般是字母),在project location选择工程路径(路径最好没有中文,听说的),然后点OK。进入下个界面:

然后点击小框里面的“create new file”.弹出界面:

在file name中写下源文件名,由于这是比较两数的大小,我取为:compare。在“add file as type”中选择verilog,点OK,然后有:

双击compare.v文件会弹出编译窗口:

复制上面源文件代码,粘贴到上图右边窗口里面。

然后点击保存图标,然后再新建测试文件。点击下图的新建文件图标。过程如同上。你会看见下图的两个.v文件。

步骤二:编译文件

在添加文件在已建的工程后,两个文件的status都是问号,编译后就变成勾。具体步骤为:

点击compile all图标就可以了。

步骤三:仿真,添加波形

选中compare.v文件,点击仿真图标如下图:

接着会弹出界面:

选中comparetest,点击OK,有:

选中compare1 右击鼠标,选择add,继续选择To Wave.,我用的是10.0a 版本,还要选择all items in region.然后就有界面:

点击run图标就会出现仿真波形。