【原创】锁相环PLL制作与调试要点

基于MC145152+MC12022+MC1648L+LM358 的锁相环电路

一、MC145152(鉴相器)

MC145152-2 芯片是摩托罗拉公司生产的锁相环频率合成器专用芯片。它是MC145152-1 芯片的改进型。主要具有下列主要特征:

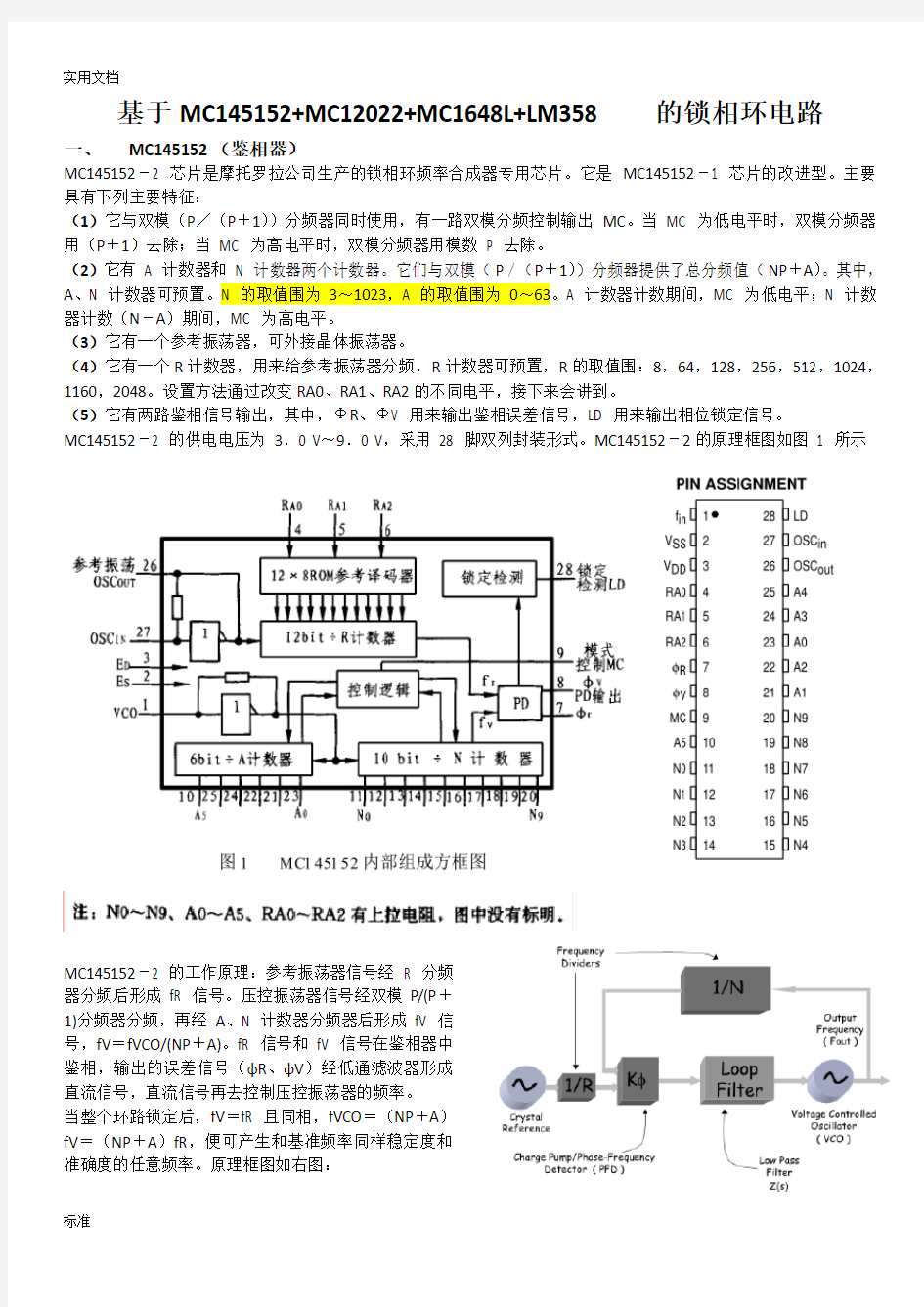

(1)它与双模(P/(P+1))分频器同时使用,有一路双模分频控制输出MC。当MC 为低电平时,双模分频器用(P+1)去除;当MC 为高电平时,双模分频器用模数P 去除。

(2)它有 A 计数器和N 计数器两个计数器。它们与双模(P/(P+1))分频器提供了总分频值(NP+A)。其中,A、N 计数器可预置。N 的取值围为3~1023,A 的取值围为0~63。A 计数器计数期间,MC 为低电平;N 计数器计数(N-A)期间,MC 为高电平。

(3)它有一个参考振荡器,可外接晶体振荡器。

(4)它有一个R计数器,用来给参考振荡器分频,R计数器可预置,R的取值围:8,64,128,256,512,1024,1160,2048。设置方法通过改变RA0、RA1、RA2的不同电平,接下来会讲到。

(5)它有两路鉴相信号输出,其中,ФR、ФV 用来输出鉴相误差信号,LD 用来输出相位锁定信号。

MC145152-2 的供电电压为3.0 V~9.0 V,采用28 脚双列封装形式。MC145152-2的原理框图如图1 所示

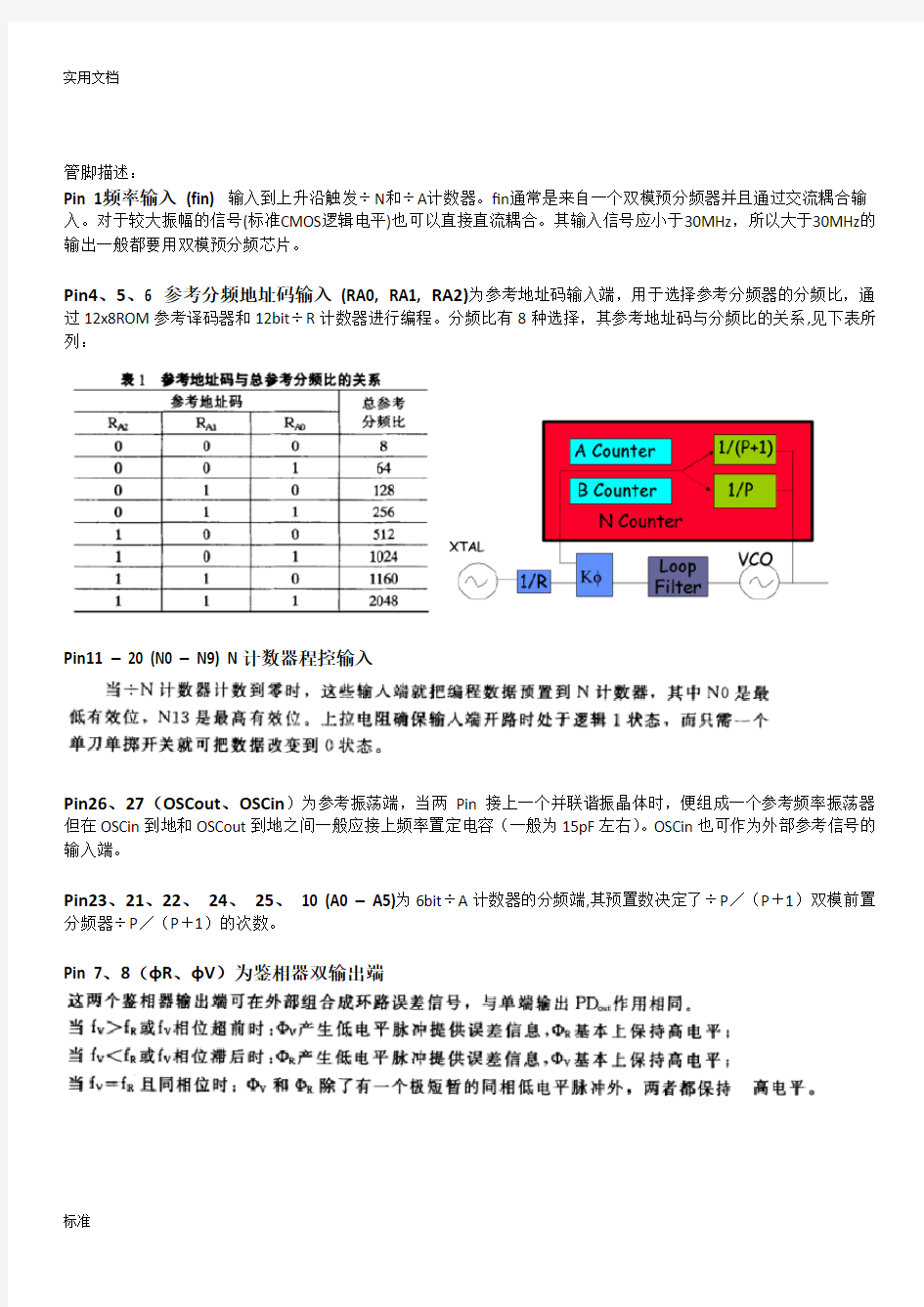

MC145152-2 的工作原理:参考振荡器信号经R 分频

器分频后形成fR 信号。压控振荡器信号经双模P/(P+

1)分频器分频,再经A、N 计数器分频器后形成fV 信

号,fV=fVCO/(NP+A)。fR 信号和fV 信号在鉴相器中

鉴相,输出的误差信号(φR、φV)经低通滤波器形成

直流信号,直流信号再去控制压控振荡器的频率。

当整个环路锁定后,fV=fR 且同相,fVCO=(NP+A)

fV=(NP+A)fR,便可产生和基准频率同样稳定度和

准确度的任意频率。原理框图如右图:

管脚描述:

Pin 1频率输入(fin) 输入到上升沿触发÷N和÷A计数器。fin通常是来自一个双模预分频器并且通过交流耦合输入。对于较大振幅的信号(标准CMOS逻辑电平)也可以直接直流耦合。其输入信号应小于30MHz,所以大于30MHz的输出一般都要用双模预分频芯片。

Pin4、5、6 参考分频地址码输入(RA0, RA1, RA2)为参考地址码输入端,用于选择参考分频器的分频比,通过12x8ROM参考译码器和12bit÷R计数器进行编程。分频比有8种选择,其参考地址码与分频比的关系,见下表所列:

Pin11 – 20 (N0 – N9) N计数器程控输入

Pin26、27(OSCout、OSCin)为参考振荡端,当两Pin接上一个并联谐振晶体时,便组成一个参考频率振荡器但在OSCin到地和OSCout到地之间一般应接上频率置定电容(一般为15pF左右)。OSCin也可作为外部参考信号的输入端。

Pin23、21、22、24、25、10 (A0 – A5)为6bit÷A计数器的分频端,其预置数决定了÷P/(P+1)双模前置分频器÷P/(P+1)的次数。

Pin 7、8(φR、φV)为鉴相器双输出端

Pin 9(MC)双模前置分频控制输出端

Pin 28(LD)锁定指示器输出端

官方芯片手册例举的典型应用:

二、MC12022(分频器)

RL取值太大将导致下降变慢!

输入阻抗,如果来自VCO实际中没接(如果你的最终输出用了AGC那接这50Ω也就无所谓),因为这信号不仅要输入分频器,还要供下级使用,不想被衰减太多:

三、MC1648(压控振荡器)

(我这个是0-5V 50MHz-90MHz)