99se导出贴片机用坐标文件

PROTEL PROTEL--9999SE SE SE软件导出贴片机坐标的方法软件导出贴片机坐标的方法

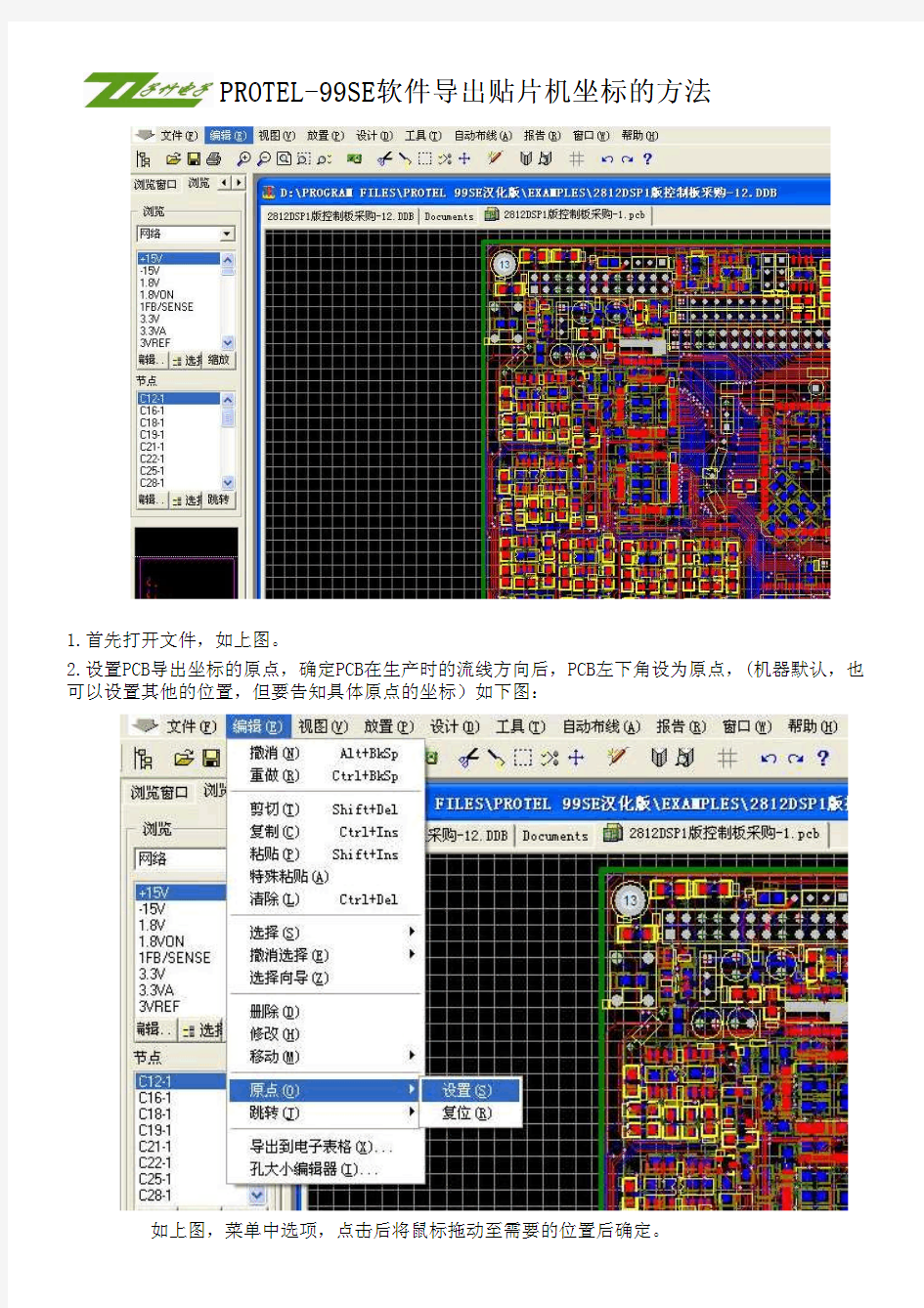

1.首先打开文件,如上图。

如上图,菜单中选项,点击后将鼠标拖动至需要的位置后确定。

2.设置PCB导出坐标的原点,确定PCB在生产时的流线方向后,PCB左下角设为原点,(机器默认,也

可以设置其他的位置,但要告知具体原点的坐标)如下图:

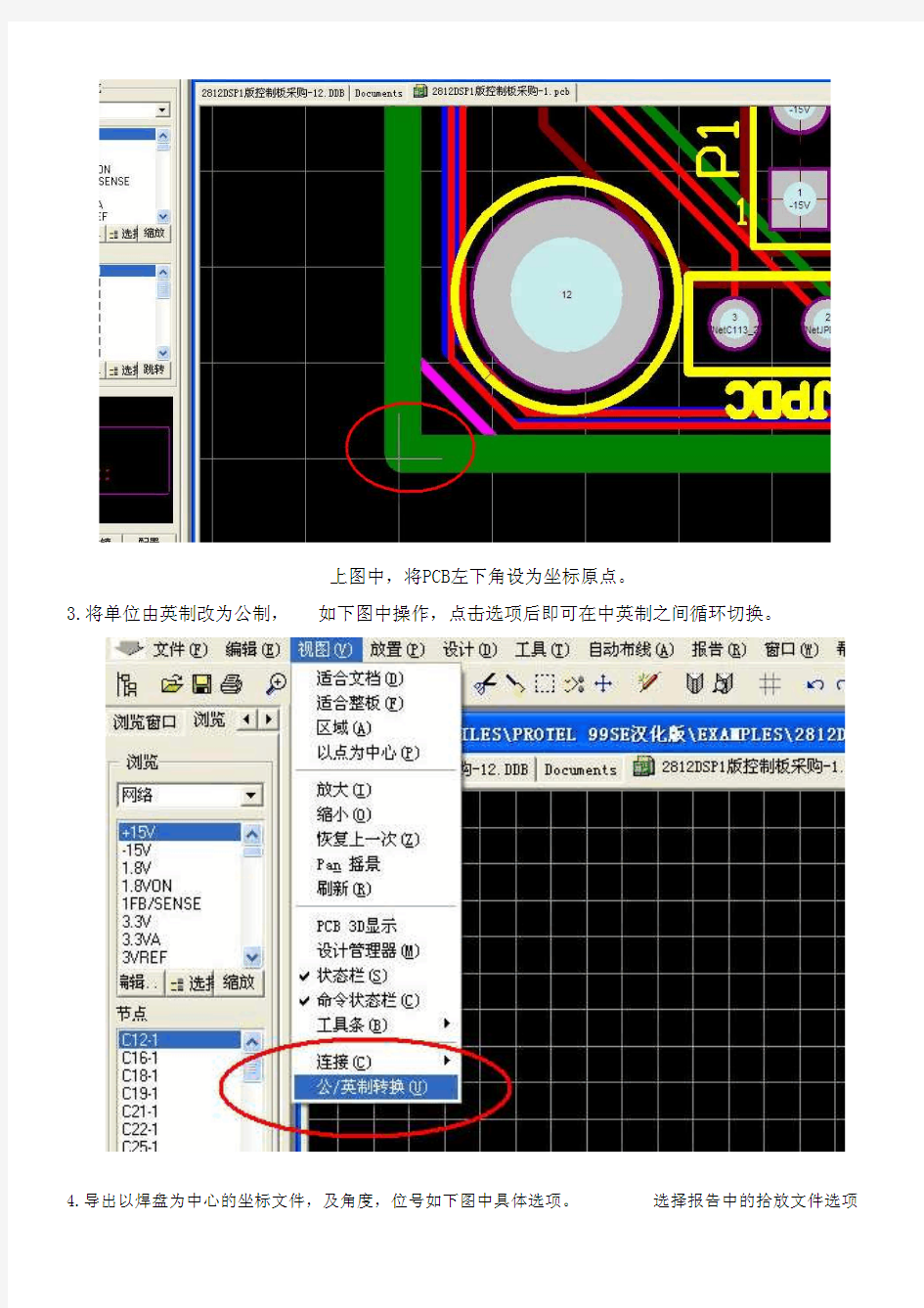

3.将单位由英制改为公制,如下图中操作,点击选项后即可在中英制之间循环切换。

4.导出以焊盘为中心的坐标文件,及角度,位号如下图中具体选项。选择报告中的拾放文件选项

上图中,将PCB左下角设为坐标原点。

5.导出的文件如下,做贴片机程序需要的坐标就是图中标出的4组数据。

6,保存文件,然后再导出一般excel能打开的文本文件即,步骤如下图。

刚导出的文件,保存在下列文件中,如图示:.pik文件。

点解鼠标右键导出文件到指定的目录。

7.保存文件,请发到我司的邮箱即可!sxzzdz@https://www.360docs.net/doc/e31779748.html,

制作人:任小勇 2012.03.29

常用电子设计大赛元器件清单

常用电子元器件清单 类别名称规格或型号规格 电阻碳膜电阻RT 0.25W 1Ω-1MΩ电阻碳膜电阻RT 0.5W 1Ω-1MΩ电阻碳膜电阻RT 1W 1K 电阻碳膜电阻RT 1W 10K 电阻金属膜电阻RJ 0.125W 1Ω-1MΩ电阻金属膜电阻RJ 0.25W 1Ω-1MΩ电阻金属膜电阻RJ 0.5W 1Ω-1MΩ电阻金属膜电阻RJ 1W 1K 电阻金属膜电阻RJ 1W 10K 电位器蓝色长方,102 102 电位器蓝色长方,103 103 电位器蓝色长方,104 104 电位器蓝色长方,105 105 电位器蓝色长方,504 504 瓷片电 瓷片电容102 容 瓷片电 瓷片电容103 容 瓷片电 瓷片电容104 容 瓷片电 瓷片电容105 容 瓷片电 瓷片电容221 容 瓷片电 瓷片电容224 容 瓷片电 瓷片电容472 容 瓷片电 瓷片电容682 容 电解电 铝电解电容10u 25V 容 电解电 铝电解电容10u 50V 容 电解电 铝电解电容22u 16V 容 电解电 铝电解电容1u 50V 容 电解电铝电解电容33u 16V

电解电 铝电解电容47u 50V 容 电解电 铝电解电容47u 100V 容 电解电 铝电解电容100u 25V 容 电解电 铝电解电容220u 50V 容 电解电 铝电解电容330u 16V 容 电解电 铝电解电容330u 50V 容 电解电 铝电解电容470u 25V 容 电解电 铝电解电容1000u 35V 容 二极管普通二极管1N4001 二极管普通二极管1N4007 二极管4148 二极管LED红灯LED灯-5mm 二极管LED红绿LED灯-5mm 二极管LED白5mm 高亮 二极管LED绿LED灯-5mm 二极管LED蓝LED灯-5mm 二极管LED黄LED灯-5mm 三极管三极管9012 三极管三极管9013 三极管三极管9014 三极管三极管8050 三极管三极管8550 三极管三极管3DG6 晶振32768 晶振8M LED数码 LED数码管LG5011BSR 管 LED数码 LED数码管SM420501KW 管 LED数码 0.56寸共阴红色 管 散热片YA25 集成电 555定时器 NE555 路 集成电运放 4558

OrCAD Capture CIS Cadence原理图绘制

OrCADCaptureCIS(Cadence原理图绘制) 1,打开软件........................................ 2,设置标题栏..................................... 3,创建工程文件................................... 4,设置颜色........................................ 2.制作原理库.......................................... 1,创建元件库...................................... 2,修改元件库位置,新建原理图封库................. 3,原理封装库的操作............................... 3.绘制原理图.......................................... 1.加入元件库,放置元件............................ 2.原理图的操作.................................... 3.browse命令的使用技巧 ........................... 4.元件的替换与更新................................ 4.导出网表............................................ 1.原理图器件序号修改.............................. 2.原理图规则检查.................................. 3.显示DRC错误信息................................ 4.创建网表........................................ 5.生成元件清单(.BOM)..................................

Cadence原理图绘制流程

第一章设计流程 传统的硬件系统设计流程如图1-1所示,由于系统速率较低,整个系统基本工作在集中参数模型下,因此各个设计阶段之间的影响很小。设计人员只需要了解本阶段的基本知识及设计方法即可。但是随着工艺水平的不断提高,系统速率快速的提升,系统的实际行为和理想模型之间的差距越来越大,各设计阶段之间的影响也越来越显著。为了保证设计的正确性,设计流程也因此有所变动,如图1-2所示,主要体现在增加了系统的前仿真和后仿真。通过两次仿真的结果来预测系统在分布参数的情况下是否能够工作正常,减少失败的可能性。 细化并调整以上原理图设计阶段的流 程,并结合我们的实际情况,原理图设计 阶段应该包括如下几个过程: 1、 阅读相关资料和器件手册 在这个阶段应该阅读的资料包括,系统的详细设计、数据流分析、各器件手册、器件成本等。 2、 选择器件并开始建库 在这个阶段应该基本完成从主器件到各种辅助器件的选择工作,并根据选择结果申请建库。 3、 确认器件资料并完成详细设计框图 为保证器件的选择符合系统的要求,在这一阶段需要完成各部分电路具体连接方式的设计框图,同时再次确认器件的相关参数符合系统的要求,并能够和其他器件正确配合。 4、 编写相关文档 这些文档可以包括:器件选择原因、可替换器件列表、器件间的连接框图、相关设计的来源(参考设计、曾验证过的设计等),参数选择说明,高速连接线及其它信息说明。 5、 完成EPLD 内部逻辑设计,并充分考虑可扩展性。

在编写相关文档的的同时需要完成EPLD内部逻辑的设计,确定器件容量及连接方式可行。 6、使用Concept-HDL绘制原理图 7、检查原理图及相关文档确保其一致性。 以上流程中并未包括前仿真的相关内容,在设计中可以根据实际情况,有选择的对部分重要连线作相关仿真,也可以根据I/O的阻抗,上升下降沿变化规律等信息简单分析判断。此流程中的各部分具体要求、注意事项、相关经验和技巧有待进一步完善。

Proteus常用元件清单 详细非常实用

Proteus常用元器件中英文对照表 AND 与门 ANTENNA 天线 BA TTERY 直流电源 BUFFER 缓冲器 BUZZER 蜂鸣器 CAP 电容 CAPACITOR 电容 CRYSTAL 晶体整荡器 DIODE 二极管 FUSE 熔断器 INDUCTOR 电感 LAMP 灯泡 LED 发光二极管 METER 仪表 MICROPHONE 麦克风 MOTOR 电机 NAND 与非门 NOR 或非门 NOT 非门 NPN NPN三极管 OPAMP 运放 OR 或门 PNP 三极管 POT 滑线变阻器 RESPACK 排阻 SCR 晶闸管 SOCKET 插座 SPEAKER 扬声器 SW- 开关类 TRIAC 三端双向可控硅 TRIODE 三极真空管 V ARISTOR 变阻器 7407 驱动门 1N914 二极管 74Ls00 与非门 74LS04 非门

74LS08 与门 74LS390 TTL 双十进制计数器 7SEG 4针BCD-LED 输出从0-9 对应于4根线的BCD码 7SEG 3-8译码器电路BCD-7SEG转换电路 ALTERNATOR 交流发电机 BA TTERY 电池/电池组 BUS 总线 CLOCK 时钟信号源 CRYSTAL 晶振 GROUND 地 LED-RED 红色发光二极管 LM016L 2行16列液晶可显示2行16列英文字符,有8位数据总线D0-D7,RS,R/W,EN三个控制端口(共14线),工作电压为5V。没背光,和常用的1602B功能和引脚一样(除了调背光的二个线脚) LOGICPROBE 逻辑探针 LOGICSTATE 逻辑状态用鼠标点击,可改变该方框连接位置的逻辑状态LOGICTOGGLE 逻辑触发 POT-LIN 三引线可变电阻器 POWER 电源 RES 电阻 RESISTOR 电阻器 VOLTMETER 伏特计 Electromechanical 电机 Inductors 变压器 CSOURCE DC Current Source恒流源 Proteus元件总目录中英文对照表及说明

Cadence Capture输出带属性的PDF原理图设置步骤

Cadence Capture 输出带属性的PDF 原理图设置步骤 作者:Myedacn 2016-01-06 1.准备工作 需要安装两个工具,一个是虚拟打印机,一个是脚本运行工具 1.1虚拟打印机安装 官方推荐Adobe Acrobat ,但是这个是需要购买授权的,所以推荐安装免费开源的工具PDFCreator ,可以从网上下载到该工具。https://www.360docs.net/doc/e31779748.html,/可以下载到最新版本的软件。 按照提示进行安装,安装完成后,可以看到打印机列表里面多了一个虚拟打印机 记住这个打印机的名称,后面会用到。1.2安装脚本运行工具基于Adobe 、PostScript 及可移植文档格式(PDF )的页面描述语言等而编译成的免费软件GhostScript 可以在官网下载到最新版本https://www.360docs.net/doc/e31779748.html,/按照提示进行安装,安装完成后记住安装路径,比如:C:\Program Files (x86)\gs\gs9.09\bin\gswin32c.exe 后面会用到。2.修改配置文件 打开Cadence Capture 安装目录,比如: C:\Cadence\SPB_16.6\tools\capture\tclscripts\capUtils 找到文件:capPdfUtil.tcl 用文本编辑器打开此文件: 找到以下位置进行修改: set ::capPdfUtil::mPSDriver "PDFCreator " 把默认的Adobe 打印机修改为PDFCreator 修改打印机安装程序位置,红色字体位置所示 set ::capPdfUtil::mPSToPDFConverterList { { "PDFCreator " {{C:\Program Files\PDFCreator\PDFCreator.exe }/N /q /o M y e d a c n 出品

电赛元件清单及题目

2001年全国大学生电子设计竞赛 一、基本仪器清单 20MHz普通示波器(双踪,外触发输入,有X轴输入); 60MHz双踪数字示波器; 1Hz~200kHz低频信号发生器; 普通函数信号发生器; 50MHz~150MHz调频/调幅高频信号发生器; 低频毫伏表; 高频毫伏表; 普通频率计; 通用计数器(可选); 失真度仪(可选); 位数字万用表; 秒表; 单片机开发系统及EDA开发系统。 二、主要元器件清单

单片机最小系统板(不含A/D、D/A等芯片); 可编程逻辑器件系统板(不含A/D、D/A等芯片); 手写输入板; 普通A/D、D/A,采样速率大于1MHz的8位A/D变换器; 运算放大器,电压比较器; 常用逻辑电路、可编程器件,常用阻、容元器件,电位器及晶体管;反射式光电检测器; 电动玩具车(外形尺寸:长≤35cm;宽≤15cm)。 三、题目 A、波形发生器 B、简易数字存储示波器 C、自动往返电动小汽车 D、高效率音频功率放大器 E、数据采集与传输系统 F、调频收音机

2003全国大学生电子设计竞赛 一、基本仪器清单 20MHz普通示波器(双通道,外触发输入,有X轴输入,可选带Z轴输入)60MHz双通道数字示波器 低频信号发生器(1Hz~200kHz) 信号发生器(1kHz~15MHz) 高频信号发生器(1MHz~35MHz) 频率特性测量仪(可选) 数字相位计(可选) 低频毫伏表 高频毫伏表 普通频率计 3位半数字万用表 电感、电容测试仪(或Q表) 秒表 单片机开发系统及EDA开发系统

二、主要元器件清单 单片机最小系统板(仅含单片机芯片、键盘与显示装置、存储器) 可编程逻辑器件下载板(仅含可编程芯片、下载电路、配置存储器)A/D、D/A变换器 运算放大器、电压比较器 可编程逻辑器件 显示器件 电动玩具车(外形尺寸:长≤35cm;宽≤15cm) 小型电动机 开关二极管 高频变容二极管 小型继电器 模拟开关 高频磁芯 传感器(光电传感器、超声传感器、金属探测传感器、红外传感器等)三、题目

如何将altium designer的原理图和PCB转入cadence里

说明: 1)本教程适用于将altium designer的原理图和PCB转入cadence(分别对应capture CIS和allegro)里。对于protel 99se,可以将其先导入较新版本的AD里,再转入cadence中。 2)整个过程中使用的软件包括altium designer Summer 08,cadence16.6,orCAD10.3-capture(免安装精简版),PADS9.3三合一完美精简版。其中,后面两个软件较小,便于下载。 3)原理图的转化路线是,从altium designer导出的.dsn文件,用orcad10.3-capture打开后,保存为cadence16.6可以打开的文件。因为较新版本的cadence不能直接打开AD转换出来的.dsn文件。如果你不是这些版本的软件,也可以参考本人的方法进行尝试。 4)pcb转化的顺序是,altium designer导出的文件,导入PADS9.3打开,然后导出.asc文件。随后利用allegro对pads的接口,将pads文件导入。 1. 原理图的导入 1.1选中原理图的项目文件,即.PRJPCB文件,右键-》save projec as,选择.dsn文件,输入要保存的文件名,保存。注意输入新的文件名的时候要把文件名的后缀手动改掉。 1.2打开orCAD10.3-capture文件夹下面的capture.exe(如果同一台电脑装了新版本的cadence,例如cadence16.6的话,环境变量中的用户变量会有冲突。具体地来说对于orCAD10.3来说,CDS_LIC_FILE的值必须是安装目录\orCAD10.3-capture\crack\license.dat。而对于cadence16.6来说,环境变量必须是5280@localhost。因此要使用orCAD10.3的话,必须将CDS_LIC_FILE 的值改掉,否则无法打开。等下使用cadence16.6,就必须将值改回来)。 1.3使用orCAD10.3将刚才保存的.dsn文件打开,并保存成project。 1.4 随后就可以使用新版本的cadence的capture CIS打开保存的文件(注意改环境变量中的用户变量CDS_LIC_FILE)。 2. PCB的导入 由于allegro可以根据已有的brd文件生成元器件的封装,因此将PCB导入allegro后使用者免于重新使用allegro绘制一遍封装。 1.1打开pads9.3,file-》new,按照默认配置建立一个文件,保存。 1.2file-》import,选中要转换的.pcb文件,打开,保存在C盘的PADS Projects文件夹下面。 (安装PADS9.3三合一完美精简版时会自动在C盘产生这个文件夹。) 1.3file-》export,将文件保存为.asc文件。接下来回弹出下图所示的对话框。注意要将.pcb

常用元器件参考清单

需要购买的参考器件 常备器件 名称 数量 参考价格(元) 备注 调温电烙铁 1 40—50 焊锡丝 1 30—50 价格因质量而定,一般40左右万用板 大板5小板5 大板5-6小板3-4 价格因质量而定,一般5块左右排针 20排

电阻 每样至少50个 常用电阻从100Ω到100MΩ不等电位器(蓝色) 每样至少10个 型号102,103,104,105 瓷片电容 104整包购买 30P 20个 最小系统板上需要30P 电解电容 50V10uf 100个 50V100uf 100个 50V3300uf 10个 3300和10多用于直流电源的制作杜邦线 一排40根 3排

杜邦钱多买点也无妨,以后会用到很多直流线性、稳压电源制作需要器件 名称 数量 价格 备注 整流二极管或者整流桥 整流二极管50个 整流桥50个 二者均用于交流电到直流电的整流 区别在于整流桥是二极管的集成块 电解电容 50V3300uf 10个 50V10uf 50个 25V1uf 5个 用于整流后滤波 瓷片电容 104 整包购买 配合电解电容达到更好的滤波效果

103电位器 10 三端可调正电压LM317 6 三端可调负电压LM337 4 输出正5V稳压器7805 4 输出负5V稳压器7905 4 输出正12V稳压器7812 4 输出负12V稳压器7912

输出正15V稳压器7815 4 输出负15V稳压器7915 4 51最小系统制作所需器件名称 数量 参考单价价格(元) 备注 STC89C52单片机 2 5 核心控制芯片 排阻 4

9脚8位排阻 紧锁座 2 5 绿色40脚,方便取单片机12MHz晶振 2 2 30PF瓷片电容 10 0.2 接晶振电路 10UF电解电容 10 0.2 接复位电路。长脚正,短脚负47K欧姆电阻 10

CADENCE从原理图到PCB步骤(精)

CADENCE从原理图到PCB步骤 一.原理图 1.建立工程 与其他绘图软件一样,OrCAD以Project来管理各种设计文件。点击开始菜单,然后依次是所有程序-- Allegro SPB 15.5--Design Entry CIS,在弹出的Studio Suite Selection对话框中选择第一项OrCAD_Capture_CIS_option with capture,点击Ok进入Capture CIS。接下来是File--New--Project,在弹出的对话框中填入工程名、路径等等,点击Ok进入设计界面。2.绘制原理图 新建工程后打开的是默认的原理图文件SCHEMATIC1 PAGE1,右侧有工具栏,用于放置元件、画线和添加网络等等,用法和Protel类似。点击上侧工具栏的Project manager(文件夹树图标)进入工程管理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库等等。 1)修改原理图纸张大小: 双击SCHEMATIC1文件夹,右键点击PAGE1,选择Schematic1 Page Properties,在Page Size 中可以选择单位、大小等; 2)添加原理图库: File--New--Library,可以看到在Library文件夹中多了一个library1.olb的原理图库文件,右键单击该文件,选择Save,改名存盘; 3)添加新元件: 常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元件,或者用别人做好的元件。右键单击刚才新建的olb库文件,选New Part,或是New Part From Spreadsheet,后者以表格的方式建立新元件,对于画管脚特多的芯片元件非常合适,可以直接从芯片Datasheet中的引脚描述表格中直接拷贝、粘贴即可(pdf格式的Datasheet按住Alt键可以按列选择),可以批量添加管脚,方便快捷。 4)生成网络表(Net List): 在画板的时候需要导入网络表,在这之前原理图应该差不多完工了,剩下的工作就是查缺补漏。可以为元件自动编号,在工程管理界面下选中.dsn文件,然后选Tools—Annotate (注解),在弹出的对话框中选定一些编号规则,根据需求进行修改或用默认设置即可。进行DRC检测也是在生成网络表之前的一项重要工作,可以避免出现一些不必要的设计错误。DRC之后可以尝试去生成网络表了,还是在工程管理界面下,选Tools--Create Netlist,可以在弹出的对话框中选择网络表的存放路径,其他默认设置即可,生成网络表的过程中如果出错,可以通Windows--Session Log查看出错的原因,比如说有元器件忘了添加封装等。 5)更新元件到原理图: 当元件库中的某个元件修改后需要原理图也同步更新时,可以不必重新放置元件(万一有100个或更多该元件岂不是要疯了),在工程管理界面下,双击Design Cache文件夹,选中刚才修改的元件,右键单击选择Update Cache,一路yes下去即可将原理图中该元件全部更新。 6)一些细节: 画原理图时的放大和缩小分别是按键“i”(Zoom In)和“o”(Zoom Out)和Protel有所区别;在创建元件封装的时候,除了GND可以同名以外,不能有其他同名的管脚,否者报错,不过貌似报错也没有影响,因为打开OrCAD自带的元件库时(比如Xilinx的FPGA),也有除GND外的同名管脚;添加网络标号的快捷键是“n”,不过在OrCAD中网络标号无法复制,记得Protel中是可以通过复制已有的网络标号来添加新的网络标号的。

如何将altiumdesigner的原理图和PCB转入cadence里

说明: 1)本教程适用于将altiumdesigner的原理图和PCB转入cadence(分别对应captureCIS和allegro)里。对于protel99se,可以将其先导入较新版本的AD里,再转入cadence中。 2)整个过程中使用的软件包括altiumdesignerSummer08,cadence16.6,orCAD10.3-capture(免安装精简版),PADS9.3三合一完美精简版。其中,后面两个软件较小,便于下载。 3)原理图的转化路线是,从altiumdesigner导出的.dsn文件,用orcad10.3-capture打开后,保存为cadence16.6可以打开的文件。因为较新版本的cadence不能直接打开AD转换出来的.dsn文件。如果你不是这些版本的软件,也可以参考本人的方法进行尝试。 4)pcb转化的顺序是,altiumdesigner导出的文件,导入PADS9.3打开,然后导出.asc文件。随后利用allegro对pads的接口,将pads文件导入。 1.原理图的导入 1.1选中原理图的项目文件,即.PRJPCB文件,右键-》saveprojecas,选择.dsn文件,输入要保存的文件名,保存。注意输入新的文件名的时候要把文件名的后缀手动改掉。 1.2打开orCAD10.3-capture文件夹下面的capture.exe(如果同一台电脑装了新版本的cadence,例如cadence16.6的话,环境变量中的用户变量会有冲突。具体地来说对于orCAD10.3来说,CDS_LIC_FILE的值必须是安装目录\orCAD10.3-capture\crack\license.dat。而对于cadence16.6来说,环境变量必须是5280@localhost。因此要使用orCAD10.3的话,必须将CDS_LIC_FILE的值改掉,否则无法打开。等下使用cadence16.6,就必须将值改回来)。 1.3使用orCAD10.3将刚才保存的.dsn文件打开,并保存成project。 1.4随后就可以使用新版本的cadence的captureCIS打开保存的文件(注意改环境变量中的用户变量CDS_LIC_FILE)。 2.PCB的导入 由于allegro可以根据已有的brd文件生成元器件的封装,因此将PCB导入allegro后使用者免于重新使用allegro绘制一遍封装。 1.1打开pads9.3,file-》new,按照默认配置建立一个文件,保存。 1.2file-》import,选中要转换的.pcb文件,打开,保存在C盘的PADSProjects文件夹下面。 (安装PADS9.3三合一完美精简版时会自动在C盘产生这个文件夹。) 1.3file-》export,将文件保存为.asc文件。接下来回弹出下图所示的对话框。注意要将.pcb 文件和.asc文件保存在同一个目录下,即C盘的PADSProjects文件夹下面,否则allegro 转换时会出现pads_in.log找不到的现象。(关于AD的pcb文件导入pads,网上还有一种方法是AD保存为PCB二进制文件,即.PcbDoc文件,再由pads导入.PcbDoc文件。用户可以自行尝试。总之,ad转换成pads似乎较为顺畅) 1.4格式选择PowerPCBV5.0,勾选认为比较的项目。点击“OK”。 1.5随后使用allegro的import-》translator,选择pads,弹出如下的对话框。 其中第一行是指定.asc文件,第三行是指定要转换成的.brd文件。一般而言都是C盘的PADSProjects文件夹内部。第二行只要指定目录,然后在对话框里点保存即可。点击translate,即可完成转换。随后file-》open,打开刚才建立的.brd文件。

电子元器件清单

心电数据采集板元器件清单 1.心电信号调理电路: 1)电阻 电阻阻值数量配件图号 10K 3 R3,R16,R17 1M 1 R4 24K 2 R5,R6, 8.2K 1 RG 510K 1 R7 1K 1 R8 45K 2 R10,R11 24K 1 R12 20K 6 R14,R15,R18,R19,R20,R21 100K(变阻器) 2 R9,R13 2)电容 1u 2 C1,C7 0.1u 6 C22,C23,C24,C25,C26,C27 10u(电解电容) 1 C2 0.068u 4 C3,C5,C4,C42 3)芯片 TL084 2 U2,U3 AD620 1 U1

4)插针 T1,T2,T3,T4,T5,T6,T7,T8,T9,T10,T11,T12 2.A/D转换电路部分 1)电阻 10K 3 R22,R30,R31 100 1 R32 2k 2 R28,R29 1k 4 R24,R25,R26,R27 10K变阻器 1 R23 2)电容器 0.1u 11 C7,C29,C11,C12,C13,C14,C15,C8,C16,C18,C28 22u(电解电容) 1 C21 22p 2 C9,C10 1000u(电解电容) 1 C17 220u(电解电容) 1 C19 1u 1 C20 晶振22.1184Hz 1 X1 3)二极管 IN4001 1 发光二极管L2,L3,L5 3 4)三极管

7805 1 BG8550 1 蜂鸣器BP 5)芯片 STC89C52 1 TLC1549CP 1 MAX232EPE 1 74LS14芯片 1 ICL7660 1 6)开关 SW 1

CADENCE导出BOM

用OrCAD Capture导出BOM的方法 2011-01-20 18:43:38 OrCAD Capture是Cadence公司的产品,在高速电子设计中使用十分的广泛。导出BOM是我们设计人员在项目开发过程中很重要的步骤,OrCAD Capture提供了强大的导出BOM功能,并且具有很好的扩展性,用户可以自定义导出需要的参数,本文将介绍使用OrCAD Capture正确导出BOM 的方法。 和之前发布的一些文章一样,我在这里仍然会分步讲解,目的是使网友能够有较清晰的认识,能够更好的理解导出BOM的方法。 PS:在较大的公司里,通常会有一个元件库,使用OrCAD Capture CIS可以链接这个元件库,这样就大大方便了设计者选择元件的过程,而且通 常这个元件库也会是该公司较常用的器件,这样也很有利于控制成本。 第一步,选中OrCAD中的设计文件,如下图:

第二步,点击工具栏中Tools,然后再点击下拉菜单中的Bill Of Materials,如下图 第三步,这时就会弹出导出BOM的对话框,在这里,你可以设置很多选项,如下图

仔细瞧瞧Line Item Dfinition那里,有两个框框,其中的Header设置的BOM中最上方的项目的名称,如Reference,Value,Part Number等, 这里的设计可以比较随意,对输出的结果不会有太大的影响。 Combined property string,这项的设置直接决定了最终的导出结果。仔细看看上面的图片,我们会发现,这个框框里面的字符都是带{}的,相信编过程序的人肯定都会对变量这种东西很敏感,我感觉这里的字符就是“变量”(个人见解,未经过考证),那么这里的“变量”应该如何填写呢? 让我们进入原理图,随便双击某一器件查看其详细信息,如下图,仔细一看,这个器件有很多属性,像ATHEROS KEY,AtherosDescription, Description,Reference,PART_NUMBER等等。

Cadence-原理图批量修改元器件属性

一、导出BOM 前提条件:对所有器件的位号进行过检测。不允许出来两个器件使用相同的位号。最简单的方式是通过Tool→Annotate重新进行编排,保证不会出错。 步骤1,选中所在的工程设计,如下图 步骤2,点击Tools→Bill of Meterials

步骤3:选中“Place each part entry on a separate line”,并且在header和Combined propert string 中输入你所想要导出的参数,其中必须选择”Reference”,这个是器件的位号,属于唯一值,后面有大用。 至此,BOM已经按照我们想要的格式导出来的。接下来就是修改BOM 二、修改BOM的内容 步骤1:打开BOM,刚打开的BOM应该是长得跟下面差不多

应该是这样。 这个演示只是装简单地添加了一个叫做Mount的属性,用于表明这个器件要不要焊接

修改完成后,如下图所示: 三、生成upd文件。 Cadence Capture CIS能够从UPD文件中自动更新器件的属性。所以一个很重要的步骤就是生成UPD文件。 UPD文件格式的基本样子是这样子的: "{Part Reference}" "TOL" "R1" "10%" "U1" "/IGNORE/" 步骤1:添加分号。方便起见将工作簿修改一下名字,同时增加两个新的工作页。如下图

步骤2:在sheet2的A1格中输入="$"&sheet1!A1&"$" 。如下图所示。这样做的目录是将sheet1的A1格的内容前后各加一个$号。其实添加$号也不是最终目的,只是这样操作比较简单

元器件选型,清单

实现功能 (1)能够显示时分秒 (2)能够调整时分秒 (1)能够任意设置定时时间 (2)定时时间到闹铃能够报警 (3)实现了秒表功能 系统工作原理图 详细电路功能图如图: 单片机控制数码管显示时、分、秒,当秒计数计满60时就向分进位,分计数器计满60后向时计数器进位,小时计数器按“23翻0”规律计数。时、分、秒的计数结果经过数据处理可直接送显示器显示。当计时发生误差的时候可以用校时电路进行校正。设计采用的是时、分、秒显示,单片机对数据进行处理同时在数码管上显示。

详细元器件列表: 2,时钟各功能分析 按键功能: K1:秒表 K2:调时 K3:调分 K4:显示时间 K5:闹铃 K6:暂停 (1)时钟运行图 仿真开始运行时,或按下key4键时,时钟从12:00:00开始运行,其中key2键对分进行调整,key3对小时进行

调整,key6可以让时钟暂停。 (2)秒表计时图 当按下key1键进入秒表计时状态,key6是秒表暂停键,可按key4键跳出秒表计时状态。

(3)闹铃设置图及运行图 设置图: 当按下key5,开始定时,分别按key2调分,key3调时设置闹铃时间,然后按下key4键恢复时钟运行状态当闹铃 设置时间到时,蜂鸣器将发出10秒钟蜂鸣声。

运行图: 该数字钟是用一片AT89C51单片机通过编程去驱动8个数码管实现的。通过6个开关控制,从上到下6个开关KEY1-KEY6的功能分别为:KEY1,切换至秒表;KEY2,调节时间,每调一次时加1;KEY3, 调节时间,每调一次分加1;KEY4,从其它状态切换至时钟状态;KEY5,切换至闹钟设置状态,也可以对秒表清零;KEY6,秒表暂停.控制键分别与P1.0~P1.5口连接.其中: A通过P2口和P3口去控制数码管的显示如图所示P2口接数码管的a——g端,是控制输出编码,P3口接数码管的1—— 8端,是控制动态扫描输出.

cadence原理图到PCB(原创)

首先说明一下我的版本是Allergro SPB 16.2。原理图设计用的是OrCAD Capture,PCB设计用的是Allegro PCB Design GXL。 教材手里有好几种,网上找的、图书馆借的。在Altium Designer里面原理图转PCB是个很简单的事情,可是在cadence里面,折腾了好几天才能通过这一步。怎么说呢,这些教材讲的都不够细,尤其是在如何操作软件这上面,完全是把help手册翻译了一遍,反而把大家在学习protel时候就知道的东西啰嗦了半天。 cadence 原理图转PCB网上流传有两种方法,我现在也只会这两种。 切入正题吧。原理图转PCB之间沟通的纽带是netlist文件,就是网表文件。正确生成网表文件的前提是原理图正确,能通过DRC检查。如果只画原理图不需要layout那就不用生成网表,在footprint选项里也不用填,否则要填上对应的封装名称,即使你没有这个封装填上封装名称也能生成网表,可以在生成网表之后再去画封装。 画封装,打开Allegro PCB Design GXL,File-New-Package symbol(wizard)。为了下文讲解,设置名称就叫dip40-8051,路径自己设定,最好不要有中文名。选DIP-next-load template-next-next-引脚数填40-next-选择焊盘(任意)-保存。 先别急,还有一项重要的事情没做,那就是生成device文件。其中的一种方法用到了它。如何生成呢,在生成封装之后,File-create device file 就可以啦,记住文件格式是.txt,和你刚才设计封装库放在同一目录下。此时可以退出 Allegro PCB Design GXL。 两种办法之前的工作都要把原理图设计好,如果你只想体验一下流程的话随便弄个IC(如8051),设计即正确,不要考虑电气特性。在属性设置里面把footprint名称填上任意名称,如(dip40-8051)。接着把不用的管教都XX掉。弄好之后进行DRC检查,有警告不要紧,只要没有错误就可以。体验流程嘛!检查无误就可以生成网表了。 生成网表第一种方法(三个文件pstchip.dat、pstxnet、pstxprt): 在capture里面,通过DRC检查之后,选Create Netlist出现上图对话框。默认标签是PCB editor,也

电赛元件清单及题目

电赛元件清单及题目 Coca-cola standardization office【ZZ5AB-ZZSYT-ZZ2C-ZZ682T-ZZT18】

2001年全国大学生电子设计竞赛 一、基本仪器清单 20MHz普通示波器(双踪,外触发输入,有X轴输入); 60MHz双踪数字示波器; 1Hz~200kHz低频信号发生器; 普通函数信号发生器; 50MHz~150MHz调频/调幅高频信号发生器; 低频毫伏表; 高频毫伏表; 普通频率计; 通用计数器(可选); 失真度仪(可选); 位数字万用表; 秒表; 单片机开发系统及EDA开发系统。

二、主要元器件清单 单片机最小系统板(不含A/D、D/A等芯片); 可编程逻辑器件系统板(不含A/D、D/A等芯片); 手写输入板; 普通A/D、D/A,采样速率大于1MHz的8位A/D变换器; 运算放大器,电压比较器; 常用逻辑电路、可编程器件,常用阻、容元器件,电位器及晶体管;反射式光电检测器; 电动玩具车(外形尺寸:长≤35cm;宽≤15cm)。 三、题目 A、波形发生器 B、简易数字存储示波器 C、自动往返电动小汽车 D、高效率音频功率放大器 E、数据采集与传输系统 F、调频收音机

2003全国大学生电子设计竞赛 一、基本仪器清单 20MHz普通示波器(双通道,外触发输入,有X轴输入,可选带Z轴输入)60MHz双通道数字示波器 低频信号发生器(1Hz~200kHz) 信号发生器(1kHz~15MHz) 高频信号发生器(1MHz~35MHz) 频率特性测量仪(可选) 数字相位计(可选) 低频毫伏表 高频毫伏表 普通频率计 3位半数字万用表 电感、电容测试仪(或Q表) 秒表 单片机开发系统及EDA开发系统

实验室目前具有的实训所需元器件清单及材料

自动化与电气工程学院电气信息类专业综合实训“基于MCS51单片机热电偶测温系统的设计与实现”实验室目前具有的实训所需元器件、工具及材料清单 实训需要的元器件序号名称规格 1 线路板 220×120 2 8位A/D转换器 ADC0809 3 四运算放大器 LM324 4 单运算放大器 OP07 、μA741 5 单片机 AT89S52或STC89C52 6 数码管共阴 7 数码管共阳 8 四位一体数码管共阴 9 四位一体数码管共阳 10 液晶 LD1602 11 液晶 12864 12 晶振 12MHZ或6MHZ 13 电容 30pf 14 电解电容 22uf/50v 15 显示驱动芯片 ULN2003A 16 显示驱动器 74HC573 17 并行接口芯片 8255 18 直流开关电源±12V,+5V 19 驱动器 75452 20 移位寄存器 74LS164 21 NPN三极管 9013 22 PNP三极管 9012 23 缓冲驱动器 74LS07 24 双D触发器 74LS74 25 六反向驱动器 74LS04 26 反向驱动器 74LS00 27 或非门 74LS02 28 译码器 74LS138 29 各类电阻 100K,8.2K,1K,10K 30 各类集成芯片管脚座 31 高温导线红、黑、蓝 32 连接导线黑红 33 接线端子(大)两座 34 接线端子(小)两座 35 蜂鸣器 5V 36 按键(大或小)自动复位功能

37 发光二极管绿 38 发光二极管红 KΩ、100KΩ、50K 39 电位器 10 40 排线 41 双排线座及插头 42 发光二极管 ф5 绿、红 43 ф3带罗纹铜柱 12mm 44

元器件清单表

电子课程设计元器件清单一览表 课题直流稳压电源 班级: 10电信姓名:于超超,,指导教师: 器件类别元件序 号 型号参数数量参考价封装形式铜板 1 保险丝座 1 保险丝管 1 插头 1 变压器220-12V/20W 1 二极管D1 1N4001 4 DIODE0.4 D2 1N4148 1 DIODE0.4 D3-D5 1N4001 3 DIODE0.4 稳压二极管D6 1N5233B 1 DIODE0.4 可调稳压器U2 LM317 1 VR5 三极管Q1 TIP127 1 TOP220 电容C1 2200uF/25V 1 RAD0.2 C2 C3 0.1uF/50V 2 RAD0.2 C4 10uF/25V 1 RAD0.2 C5 1uF/25V 1 RAD0.2 C6-C8 220uF/25V 3 RAD0.2 电阻R1 6.2Ω 1 AXIAL0.3 R2-R4 240Ω 3 AXIAL0.3 R5 100Ω 1 AXIAL0.3 可变电阻R6 4.7kΩ 1 VR5 散热片 1 电源线 1 保险丝 1.2A 1 螺丝 M3.5*15 6个螺母 6个垫片 12个 M2.5*6 1个(固定散热片)黑色导线 50cm红色导线 50cm 绿色导线 50cm 焊锡丝 1M

日期:年月日

电子课程设计元器件清单一览表(事例) 课题“汽车智能化灯光控制器” 班级:姓名:,,指导教师: 器件类别元件序 号 型号参数数量参考价封装形式施密特触发器U2 CC40106 1 1.00 DIP14 单片机芯片U3 8051 1 10.00 DIP40 运算放大器U1 LM358 1 1.00 DIP8 三极管Q1 S8050 1 1.00 T0-92A Q2 S8050 1 1.00 T0-92A 二极管D1 IN4148 1 0.1 DIODE0.4 D2 IN4148 1 0.1 DIODE0.4 复位键D4 SW-SB 1 0.05 RAD0.2 D5 SW-SB 1 0.05 RAD0.2 D6 SW-SB 1 0.05 RAD0.2 D7 SW-SB 1 0.05 RAD0.2 三端稳压器IC2 7805 1 1.00 VR5 可调稳压器IC1 LM317 1 1.00 VR5 继电器V3 RELAY-SPDT 1 V4 RELAY-SPDT 1 晶振Y1 CRYSTAL 1 电容C1 1000P 1 0.1 RAD0.2 C2 1000P 1 0.1 RAD0.2 C3 30P 1 0.1 RAD0.2 C4 30P 1 0.1 RAD0.2 炭膜电阻R1 10MΩ 1 1.00 VR5 R2 10MΩ 1 1.00 VR5 可调电阻RP1 10KΩ 1 1.00 VR5 RP2 1M 1 0.1 AXIAL0.3 RP3 100K 1 0.1 AXIAL0.3 、日期:年月日

Protel原理图PCB到Cadence的数据转换

Protel原理图PCB到Cadence的数据转换 Date: 2008/ 04 / 25 Author:周曙光 Version: v16.x Keywords:数据转换AD6(Altium Designer 6) Note: 任何两个EDA工具之间的数据转换都不是百分百的正确,都需要做一定修改。 随着PCB设计的复杂程度和高速PCB设计需求的不断增加,越来越多的PCB设计者、设计团队选择Cadence的设计平台和工具。但是,由于没有AD6数据到Cadence数据直接转换工具,长期以来如何将现有的基于AD6平台的设计数据转化到Cadence平台上来一直是处于平台转化期的设计者所面临的难题。 下面结合Cadence和Altium的PCB设计工具,提供一条比较合理的转换途径。 1、环境:转换中使用到的工具 a) Altium Designer 6 b) Cadence Capture CIS c) Cadence Orcad Layout d) Cadence PCB Editor e) Cadence PCB Router(CCT) 2、Altium - AD6原理图到Cadence - Capture CIS 在Altium Designer 6原理图的转化上我们可以利用Altium Designer 6的Save Preject As来实现。通过这一功能我们可以直接将AD6的原理图转化到Capture CIS中。 然后直接保存为*.dsn文件。

注意事项: 这里,我们仅提出几点通过实践总结出来的注意事项。 a)封装信息 AD6在输出Capture DSN文件的时候,没有输出封装信息,在Capture中我们会看到所以元件的PCB Footprint属性都是空的。这就需要我们手工为元件添加封装信息,这也是整个转化过程中最耗时的工作。在添加封装信息时要注意保持与AD6 PCB设计中的封装一致性,以及Cadence在封装命名上的限制。 例如一个电阻,在AD6中的封装为AXIAL0.4,在后面介绍的封装库的转化中,将被修改为AXIAL04,这是由于Cadence不允许封装名中出现“.”;再比如DB9接插件的封装在AD6中为DB9RA/F,将会被改为DB9RAF。因此我们在Capture中给元件添加封装信息时,要考虑到这些命名的改变。当然,如果自己有一些标准的Cadence的PCB封装库,也可以直接输入对应的封装库名称。只是需要注意的就是在后面要导入器件的位置信息的时候,需要把AD6中的PCB封装名称修改为Cadence的PCB封装名称。当然两个软件中封装库的原点应该是一致的,否则后面导入PCB Editor时候,器件不在原来的位置。 b)原始设计要规范 AD6的原理图应该要规范,保证导出之后的错误尽可能的少,譬如,网络的连线最好不要直接连接到pin管脚,应该来出来一段线之后再去连接其他管脚。还有电源地符号,最好在AD6中引出一段线再接。 c)管脚信息 一些器件的隐藏管脚或管脚号在转化过程中会丢失,需要在Capture中使用库编辑的方法添加上来。通常易丢失管脚号的器件时电阻电容等离散器件。 d)层次化设计中的问题 在层次化设计中,模块之间连接的总线需要在Capture中命名。即使在AD6中已经在父设计中对这样的总线命名了,还是要在Capture中重新来过,以确保连接。 e)一个封装对应几个部分的器件