集成电路引脚排列图大全

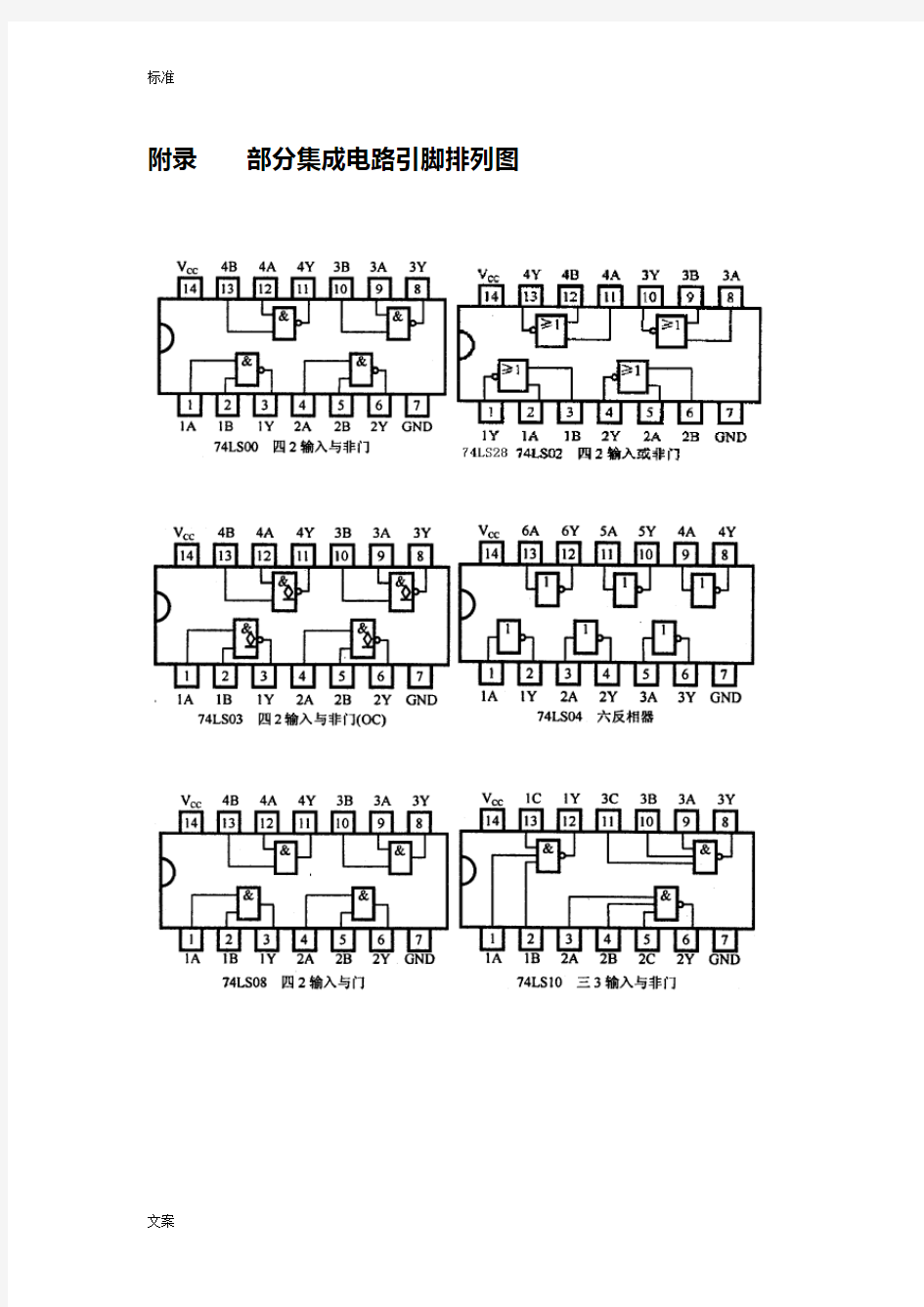

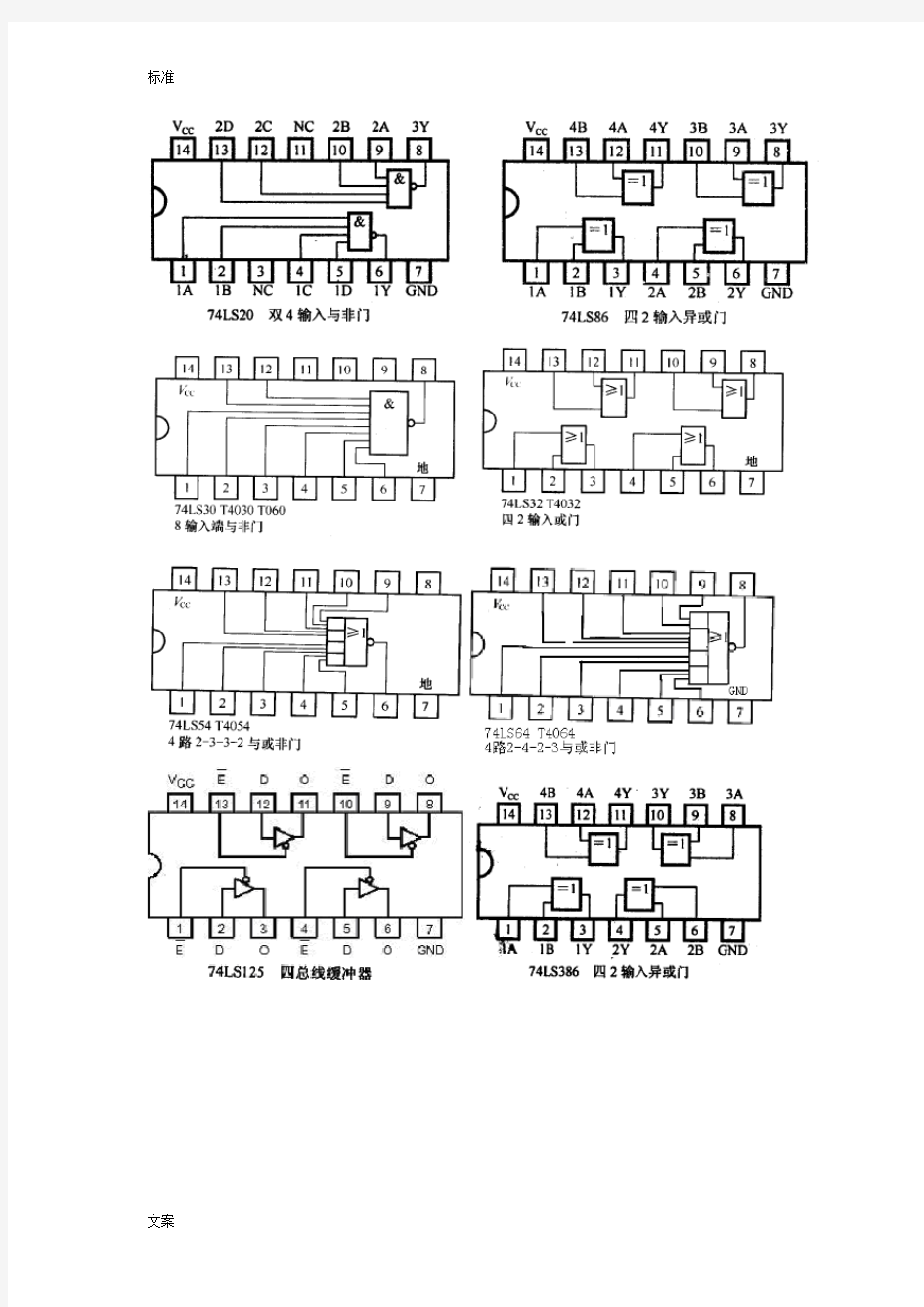

附录部分集成电路引脚排列图

常用集成电路管脚图

12345 6 78 9 10 11 12 13 14 74LS00 1A 1B 1Y 2A 2B 2Y GND 3Y 3A 4Y 4B 4A Vcc 3B 2输入四与非门 74LS00 1 2 3 4 5678 9 10 11 12 13 14 74LS02 1A 1B 1Y 2A 2B 2Y GND 3Y 3A 4Y 4B 4A Vcc 3B 二输入四或非门 74LS02 六反相器 74LS04 1 2 3 4 5678 9 10 11 12 13 14 74LS10 1B 1Y 1A 2A 3B 2B GND 2Y 2C 3Y 3C 3A Vcc 1C 三输入三与非门 74LS10 1 2 3 4 5678 9 10 11 12 13 14 74LS20 1B 2C 1A NC 2B 1C GND 1Y 1D 2Y NC 2A Vcc 2D 四输入二与非门 74LS20 4线-10线译码器 74LS42 1234 5 6789 10 11 12 13 14 15 16 74LS48 B C LT BI/RBO RBI D A GND e d c b a g f Vcc BCD-七段译码器/驱动器 74LS48 12 345678 9 10 11 12 13 14 74LS74 1CLR 1D 1CLK 1PR 1Q GND 2Q 2PR 2CLK 2D 2CLR Vcc 2Q 正沿触发双D 型触发器 74LS74 双J-K 触发器 74LS76 二输入四异或门 74LS86 常用集成电路管脚图(一) 4位移位寄存器 74LS95 负沿触发双J-K 触发器 74LS112

常用集成电路外部引脚图

附录B 常用集成电路外部引脚图 Z^LSOO 料丽 Wc 聘 t* ? ia JI 而冋网KH 丽R1 m 74LS(52 z 吃 Xkn 4V 4fl 4A n JQ U 冋冋丽冋冋〒面 和畀1 Wi r?i bL I Q L TT 阡 LU I2J L2J LU LU lAJ LZJ 1 1A -Ifl tV 詁 afl JV I “1 21 ? Ml 4J Jj |引 IV IB 2Y lA 2B GhO 四2输入正“或非”门 ⑵ 74LS02 ⑴74LS00四2输入正“与非”门 ⑶74LS04六反相器 ⑷ 74LS08 四2输入正“与”门 74LS04 Mtoc fl* S T SA rniiiai nil iV Ji 4A 回 rri 堆 Pl Pl 2 b 1 A LU lU LU Ld 国回 LU U If JA iv ik iY &泌 ⑸74LS10三3输入正“与非”门 ⑹ 74LS14 六反相施密特触发器 丫 A 74LS10 T.sec 1C IT- K JB W 3T 而 丽 [iJI liil 岡面 IT I MOf 回 Pl Ul |Z| 口 .4 丨国□ |T. g IB ZA K 2V SMT ⑺74LS20双4输入正“与非”门 (8) 74LS32 74LS20杠呢 ) L- T 1 M 區」 LJ LzJ LiJ N lAl bJ IT 2a !1f SA av 四2输入或门 4 lA IT Ifi M 冋冋 rni n^i m <30! R1 74LS08 VEAD Vbr d 臼 M 廿 9 H 押 而河豆同而 jj .3| J. 1*1 hl in W IB E M * zv cw ? K NC a 2A 丹 而57 ny 丽両 回 m 2 I 」.Jj 丨列回巴 3 16 MC 1C 1O IV G*? wc ri ii LiJ LU Ld LU u u lY u zb A dU

教你认识如何看懂集成电路的线路图

教你认识如何看懂集成电路的线路图 集成电路应用电路图功能集成电路应用电路图具有下列一些功能: ①它表达了集成电路各引脚外电路结构、元器件参数等,从而表示了某一集成电路的完整工作情况。 ②有些集成电路应用电路中,画出了集成电路的内电路方框图,这时对分析集成电路应用电路是相当方便的,但这种表示方式不多。 ③集成电路应用电路有典型应用电路和实用电路两种,前者在集成电路手册中可以查到,后者出现在实用电路中,这两种应用电路相差不大,根据这一特点,在没有实际应用电路图时可以用典型应用电路图作参考,这一方法修理中常常采用。 ④一般情况集成电路应用电路表达了一个完整的单元电路,或一个电路系统,但有些情况下一个完整的电路系统要用到两个或更多的集成电路。 .集成电路应用电路特点集成电路应用电路图具有下列一些特点: ①大部分应用电路不画出内电路方框图,这对识图不利,尤其对初学者进行电路工作分析时更为不利。 ②对初学者而言,分析集成电路的应用电路比分析分立元器件的电路更为困难,这是对集成电路内部电路不了解的原缘,实际上识图也好、修理也好,集成电路比分立元器件电路更为方便。 ③对集成电路应用电路而言,大致了解集成电路内部电路和详细了解各引脚作用的情况下,识图是比较方便的。这是因为同类型集成电路具有规律性,在掌握了它们的共性后,可以方便地分析许多同功能不同型号的集成电路应用电路。 .集成电路应用电路识图方法和注意事项分析集成电路的方法和注意事项主要有下列几点:(1)了解各引脚的作用是识图的关键了解各引脚的作用可以查阅有关集成电路应用手册。知道了各引脚作用之后,分析各引脚外电路工作原理和元器件作用就方便了。例如:知道①脚是输入引脚,那么与①脚所串联的电容是输入端耦合电路,与①脚相连的电路是输入电

74LS系列芯片引脚图资料大全

74系列芯片引脚图资料大全 作者:佚名来源:本站原创点击数:57276 更新时间:2007年07月26日【字体:大中小】 为了方便大家我收集了下列74系列芯片的引脚图资料,如还有需要请上电子论坛https://www.360docs.net/doc/0110559607.html,/b bs/ 反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373

反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│ Y =A+C )│四总线三态门74LS125 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND

芯片引脚图及引脚描述

555芯片引脚图及引脚描述 555的8脚是集成电路工作电压输入端,电压为5~18V,以UCC表示;从分压器上看出,上比较器A1的5脚接在R1和R2之间,所以5脚的电压固定在2UCC/3上;下比较器A2接在R2与R3之间,A2的同相输入端电位被固定在UCC/3上。 1脚为地。2脚为触发输入端;3脚为输出端,输出的电平状态受触发器控制,而触发器受上比较器6脚和下比较器2脚的控制。 当触发器接受上比较器A1从R脚输入的高电平时,触发器被置于复位状态,3脚输出低电平; 2脚和6脚是互补的,2脚只对低电平起作用,高电平对它不起作用,即电压小于1Ucc/3,此时3脚输出高电平。6脚为阈值端,只对高电平起作用,低电平对它不起作用,即输入电压大于2 Ucc/3,称高触发端,3脚输出低电平,但有一个先决条件,即2脚电位必须大于1Ucc/3时才有效。3脚在高电位接近电源电压Ucc,输出电流最大可打200mA。 4脚是复位端,当4脚电位小于0.4V时,不管2、6脚状态如何,输出端3脚都输出低电平。 5脚是控制端。 7脚称放电端,与3脚输出同步,输出电平一致,但7脚并不输出电流,所以3脚称为实高(或低)、7脚称为虚高。 555集成电路管脚,工作原理,特点及典型应用电路介绍. 1 555集成电路的框图及工作原理 555集成电路开始是作定时器应用的,所以叫做555定时器或555时基电路。但后来经过开发,它除了作定时延时控制外,还可用于调光、调温、调压、调速等多种控制及计量检测。此外,还可以组成脉冲振荡、单稳、双稳和脉冲调制电路,用于交流信号源、电源变换、频率变换、脉冲调制等。由于它工作可靠、使用方便、价格低廉,目前被广泛用于各种电子产品中,555集成电路内部有几十个元器件,有分压器、比较器、基本R-S触发器、放电管以及缓冲器等,电路比较复杂,是模拟电路和数字电路的混合体,如图1所示。 2. 555芯片管脚介绍 555集成电路是8脚封装,双列直插型,如图2(A)所示,按输入输出的排列可看成如图2(B)所示。其中6脚称阈值端(TH),是上比较器的输入;2脚称触发端(TR),是下比较器的输入;3脚是输出端(Vo),它有O和1两种状态,由输入端所加的电平决定;7脚是放电端(DIS),它是内部放电管的输出,有悬空和接地两种状态,也是由输入端的状态决定;4脚是复位端(MR),加上低电平时可使输出为低电平;5脚是控制电压端(Vc),可用它改变上下触发电平值;8脚是电源端,1脚是地端。 图2 555集成电路封装图 我们也可以把555电路等效成一个带放电开关的R-S触发器,如图3(A)所示,这个特殊的触发器有两个输入端:阈值端(TH)可看成是置零端R,要求高电平,触发端(TR)可看成是置位端S,要求低电平,有一个输出端Vo,Vo可等效成触发器的Q端,放电端(DIS)可看成是由内部放电开关控制的一个接点,由触发器的Q端控制:Q=1时DIS端接地,Q=0时DIS 端悬空。另外还有复位端MR,控制电压端Vc,电源端VDD和 地端GND。这个特殊的触发器有两个特点: (1)两个输入端的触发电平要求一高一低,置零端R即阈值端(TH)要求高电平,而置位端s 即触发端(TR)则要求低电乎; (2)两个输入端的触发电平使输出发生翻转的阈值电压值也不同,当V c端不接控制电压时,对TH(R)端来讲,>2/3VDD是高电平1,<2/3VDD是低电平0:而对TR(S)端来讲,>1/3VDD是

74系列芯片引脚图

74系列芯片引脚图、功能、名称、资料大全(含74LS、74HC等),特别推荐为了方便大家,我收集了下列74系列芯片的引脚图资料。 说明:本资料分3部分:(一)、TXT文档,(二)、图片,(三)、功能、名称、资料。 (一)、TXT文档 反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门 LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373

反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘

1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│ Y =A+C )│四总线三态门 74LS125 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND Vcc -G B1 B2 B3 B4 B8 B6 B7 B8 ┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位总线驱动器 74LS245 │20 19 18 17 16 15 14 13 12 11│ )│ DIR=1 A=>B │ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A └┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘ DIR A1 A2 A3 A4 A5 A6 A7 A8 GND

各种集成电路介绍

第一节三端稳压IC 电子产品中常见到的三端稳压集成电路有正电压输出的78××系列和负电压输出的79××系列。故名思义,三端IC是指这种稳压用的集成电路只有三条引脚输出,分别是输入端、接地端和输出端。它的样子象是普通的三极管,TO-220的标准封装,也有9013样子的TO-92封装。 用78/79系列三端稳压IC来组成稳压电源所需的外围元件极少,电路内部还有过流、过热及调整管的保护电路,使用起来可靠、方便,而且价格便宜。该系列集成稳压IC型号中的78或79后面的数字代表该三端集成稳压电路的输出电压,如7806表示输出电压为正6V,7909表示输出电压为负9V。 78/79系列三端稳压IC有很多电子厂家生产,80年代就有了,通常前缀为生产厂家的代号,如TA7805是东芝的产品,AN7909是松下的产品。(点击这里,查看有关看前缀识别集成电路的知识) 有时在数字78或79后面还有一个M或L,如78M12或79L24,用来区别输出电流和封装形式等,其中78L调系列的最大输出电流为100mA,78M系列最大输出电流为1A,78系列最大输出电流为1.5A。它的封装也有多种,详见图。塑料封装的稳压电路具有安装容易、价格低廉等优点,因此用得比较多。79系列除了输出电压为负。引出脚排列不同以外,命名方法、外形等均与78系列的相同。 因为三端固定集成稳压电路的使用方便,电子制作中经常采用,可以用来改装分立元件的稳压电源,也经常用作电子设备的工作电源。电路图如图所示。 注意三端集成稳压电路的输入、输出和接地端绝不能接错,不然容易烧坏。一般三端集成稳压电路的最小输入、输出电压差约为2V,否则不能输出稳定的电压,一般应使电压差保持在4-5V,即经变压器变压,二极管整流,电容器滤波后的电压应比稳压值高一些。 在实际应用中,应在三端集成稳压电路上安装足够大的散热器(当然小功率的条件下不用)。当稳压管温度过高时,稳压性能将变差,甚至损坏。 当制作中需要一个能输出1.5A以上电流的稳压电源,通常采用几块三端稳压电路并联起来,使其最大输出电流为N个1.5A,但应用时需注意:并联使用的集成稳压电路应采用同一厂家、同一批号的产品,以保证参数的一致。另外在输出电流上留有一定的余量,以避免个别集成稳压电路失效时导致其他电路的连锁烧毁。 第二节语音集成电路 电子制作中经常用到音乐集成电路和语言集成电路,一般称为语言片和音乐片。它们一般都是软包封,即芯片直接用黑胶封装在一小块电路板上。语音IC一般还需要少量外围元件才能工作,它们可直接焊到这块电路板上。

常用集成电路管脚图

1 / 2 勿用作商业用途 12345 6 78 9 10 11 12 13 14 74LS00 1A 1B 1Y 2A 2B 2Y GND 3Y 3A 4Y 4B 4A Vcc 3B 2输入四与非门 74LS00 1 2 3 4 5678 9 10 11 12 13 14 74LS02 1A 1B 1Y 2A 2B 2Y GND 3Y 3A 4Y 4B 4A Vcc 3B 二输入四或非门 74LS02 六反相器 74LS04 1 2 3 4 5678 9 10 11 12 13 14 74LS10 1B 1Y 1A 2A 3B 2B GND 2Y 2C 3Y 3C 3A Vcc 1C 三输入三与非门 74LS10 1 2 3 4 5678 9 10 11 12 13 14 74LS20 1B 2C 1A NC 2B 1C GND 1Y 1D 2Y NC 2A Vcc 2D 四输入二与非门 74LS20 4线-10线译码器 74LS42 1234 5 6789 10 11 12 13 14 15 16 74LS48 B C LT BI/RBO RBI D A GND e d c b a g f Vcc BCD-七段译码器/驱动器 74LS48 12 345678 9 10 11 12 13 14 74LS74 1CLR 1D 1CLK 1PR 1Q GND 2Q 2PR 2CLK 2D 2CLR Vcc 2Q 正沿触发双D 型触发器 74LS74 双J-K 触发器 74LS76 二输入四异或门 74LS86 常用集成电路管脚图(一) 4位移位寄存器 74LS95 负沿触发双J-K 触发器 74LS112 常用集成电路管脚图(二)

74系列芯片引脚大全

74系列芯片引脚图资料大全(2008-04-24 17:37:47) 74系列芯片引脚图资料大全 反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373 反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│ Y =A+C )│四总线三态门74LS125 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND Vcc -G B1 B2 B3 B4 B8 B6 B7 B8 ┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐8位总线驱动器74LS245 │20 19 18 17 16 15 14 13 12 11│ )│DIR=1 A=>B │1 2 3 4 5 6 7 8 9 10│DIR=0 B=>A └┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘ DIR A1 A2 A3 A4 A5 A6 A7 A8 GND 页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器 正逻辑与门,与非门:

各种集成电路引脚识别方法

集成电路引脚的识别方法 集成电路的引脚较多,如何正确识别集成电路的引脚则是使用中的首要问题。下面介绍几种常用集成电路引脚的排列形成。 集成电路的引脚较多,如何正确识别集成电路的引脚则是使用中的首要问题。下面介绍几种常用集成电路引脚的排列形成。 圆形结构的集成电路和金属壳封装的半导体三极管差不多,只不过体积大、电极引脚多。这种集成电路引脚排列方式为:从识别标记开始,沿顺时针方向依次为l、2、3……如图18-2(a)所示。单列直插型集成电路的识别标记,有的用切角,有的用凹坑。这类集成电路引脚的排列方式也是从标记开始,从左向右依次为1、2、3……如图18-2(b)、(c)所示。 扁平型封装的集成电路多为双列型,这种集成电路为了识别管脚,一般在端面一侧有一个类似引脚的小金属片,或者在封装表面上有一色标或凹口作为标记。其引脚排列方式是:从标记开始,沿逆时针方向依次为1、2、3……如图18-2(d)所示。但应注意,有少量的扁平封装集成电路的引脚是顺时针排列的。 双列直插式集成电路的识别标记多为半圆形凹口,有的用金属封装标记或凹坑标记。这类集成电路引脚排列方式也是从标记开始,沿逆时针方向依次为1、2、3……如图18-2(e)、(f)。 集成电路引出脚排列顺序的标志一般有色点、凹槽及封装时压出的圆形标志。对于双列直插集成块,引脚识别方法是将集成电路水平放置,引脚向下,标志朝左边,左下角为第一个引脚,然后按逆时针方向数,依次为2,3,4,等等。对于单列直插集成板,让引脚向下,标志朝左边,从左下角第一个引脚到最后一个引脚,依次为1,2,3,等等。如图8所示。

各种集成电路引脚识别方法 集成电路通常有扁平、双列直插、单列直插等几种封装形式。不论是哪种集成电路的外壳上都有供识别管脚排序定位(或称第一脚)的标记。对于扁平封装者,一般在器件正面的一端标上小圆点(或小圆圈、色点)作标记。塑封双列直插式集成电路的定位标记通常是弧形凹口、圆形凹坑或小圆圈。进口IC的标记花样更多,有色线、黑点、方形色环、双色环等等。图1(a)、(b)示出了数字集成电路采用扁平封装与双列直插式塑料封装常见的管脚定位标记。图1(c)是采用陶瓷封装的双列直插式数字集成电路,它采用金属片与色点双重标记。 识别数字IC管脚的方法是:将IC正面的字母、代号对着自己,使定位标记朝左下方,则处于最左下方的管脚是第1脚,再按逆时针方向依次数管脚,便是第2脚、第3脚等等。图2(a)、(b)是模拟IC的定位标记及管脚排序,情况与数字IC相似。模拟IC有少部分管脚排序较特殊,如图2(c)、(d)所示。

及其他系列芯片引脚图大全

一:分类 74ls00 2输入四与非门 74ls01 2输入四与非门 (oc) 74ls02 2输入四或非门 74ls03 2输入四与非门 (oc) 74ls04 六倒相器 74ls05 六倒相器(oc) 74ls06 六高压输出反相缓冲器/驱动器(oc,30v) 74ls07 六高压输出缓冲器/驱动器(oc,30v) 74ls08 2输入四与门 74ls09 2输入四与门(oc) 74ls10 3输入三与非门 74ls11 3输入三与门 74ls12 3输入三与非门 (oc) 74ls13 4输入双与非门 (斯密特触发) 74ls14 六倒相器(斯密特触发) 74ls15 3输入三与门 (oc) 74ls16 六高压输出反相缓冲器/驱动器(oc,15v) 74ls17 六高压输出缓冲器/驱动器(oc,15v) 74ls18 4输入双与非门 (斯密特触发) 74ls19 六倒相器(斯密特触发) 74ls20 4输入双与非门 74ls21 4输入双与门 74ls22 4输入双与非门(oc) 74ls23 双可扩展的输入或非门 74ls24 2输入四与非门(斯密特触发)

74ls25 4输入双或非门(有选通) 74ls26 2输入四高电平接口与非缓冲器(oc,15v) 74ls27 3输入三或非门 74ls28 2输入四或非缓冲器 74ls30 8输入与非门 74ls31 延迟电路 74ls32 2输入四或门 74ls33 2输入四或非缓冲器(集电极开路输出) 74ls34 六缓冲器 74ls35 六缓冲器(oc) 74ls36 2输入四或非门(有选通) 74ls37 2输入四与非缓冲器 74ls38 2输入四或非缓冲器(集电极开路输出74ls39 2输入四或非缓 冲器(集电极开路输出) 7 4ls40 4输入双与非缓冲器 7 4ls41 bcd-十进制计数器 7 4ls42 4线-10线译码器(bcd输入) 7 4ls43 4线-10线译码器(余3码输 入) 7 4ls44 4线-10线译码器(余3葛莱 码输入) 7 4ls45 bcd-十进制译码器/驱动器 7 4ls46 bcd-七段译码器/驱动器

74系列元件引脚图

反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS24 5 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373 反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│

Y =A+C )│四总线三态门74LS125 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND Vcc -G B1 B2 B3 B4 B8 B6 B7 B8 ┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位总线驱动器74LS245 │20 19 18 17 16 15 14 13 12 11│ )│ DIR=1 A=>B │1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A └┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘ DIR A1 A2 A3 A4 A5 A6 A7 A8 GND 页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器 正逻辑与门,与非门: Vcc 4B 4A 4Y 3B 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = AB )│ 2输入四正与门74LS08 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1B 1Y 2A 2B 2Y GND Vcc 4B 4A 4Y 3B 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ __ │14 13 12 11 10 9 8│ Y = AB )│ 2输入四正与非门74LS00 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1B 1Y 2A 2B 2Y GND Vcc 1C 1Y 3C 3B 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ ___ │14 13 12 11 10 9 8│ Y = ABC )│ 3输入三正与非门74LS10 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1B 2A 2B 2C 2Y GND

74ls系列主要芯片引脚及参数.doc

<74LS00引脚图> 74l s00 是常用的2输入四与非门集成电路,他的作用很简单顾名思义就是实现一个与非门。 Vcc 4B 4A 4Y 3B 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ __ │14 13 12 11 10 9 8│ Y = AB )│ 2输入四正与非门 74LS00 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1B 1Y 2A 2B 2Y GND 74LS00真值表: A=1 B=1 Y=0 A=0 B=1 Y=1 A=1 B=0 Y=1 A=0 B=0 Y=1

74HC138基本功能74LS138 为3 线-8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,其74LS138工作原理如下: 当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。 74LS138的作用: 利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器 用与非门组成的3线-8线译码器74LS138

图74ls138译码器内部电路 3线-8线译码器74LS138的功能表 备注:这里的输入端的三个A0~1有的原理图中也用A B C表示(如74H138.pdf中所示,试用于普中科技的HC-6800 V2.2单片机开发板)。<74ls138功能表> 74LS138逻辑图

无论从逻辑图还是功能表我们都可以看到74LS138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。 当附加控制门的输出为高电平(S=1)时,可由逻辑图写出 74ls138逻辑图 由上式可以看出,在同一个时间又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。 71LS138有三个附加的控制端、和。当、时,输出为高电平(S=1),译码器处于工作状态。否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。 带控制输入端的译码器又是一个完整的数据分配器。在图3.3.8电路中如果把作为“数据”输入端(在同一个时间),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。这就不难理解为什么把叫做地址输入了。例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。 例2.74LS138 3-8译码器的各输入端的连接情况及第六脚()输入信号A的波形如下图所示。试画出八个输出管脚的波形。

芯片引脚图及引脚描述

555的8脚是集成电路工作电压输入端,电压为5~18V,以UCC表示;从分压器上看出,上比较器A1的5脚接在R1和R2之间,所以5脚的电压固定在2UCC/3上;下比较器A2接在R2与R3之间,A2的同相输入端电位被固定在UCC/3上。 1脚为地。2脚为触发输入端;3脚为输出端,输出的电平状态受触发器控制,而触发器受上比较器6脚和下比较器2脚的控制。 当触发器接受上比较器A1从R脚输入的高电平时,触发器被置于复位状态,3脚输出低电平; 2脚和6脚是互补的,2脚只对低电平起作用,高电平对它不起作用,即电压小于1Ucc/3,此时3脚输出高电平。6脚为阈值端,只对高电平起作用,低电平对它不起作用,即输入电压大于2 Ucc/3,称高触发端,3脚输出低电平,但有一个先决条件,即2脚电位必须大于1Ucc/3时才有效。3脚在高电位接近电源电压Ucc,输出电流最大可打200mA。 4脚是复位端,当4脚电位小于时,不管2、6脚状态如何,输出端3脚都输出低电平。 5脚是控制端。 7脚称放电端,与3脚输出同步,输出电平一致,但7脚并不输出电流,所以3脚称为实高(或低)、7脚称为虚高。 555集成电路管脚,工作原理,特点及典型应用电路介绍. 1 555集成电路的框图及工作原理 555集成电路开始是作定时器应用的,所以叫做555定时器或555时基电路。但后来经过开发,它除了作定时延时控制外,还可用于调光、调温、调压、调速等多种控制及计量检测。此外,还可以组成脉冲振荡、单稳、双稳和脉冲调制电路,用于交流信号源、电源变换、频率变换、脉冲调制等。由于它工作可靠、使用方便、价格低廉,目前被广泛用于各种电子产品中,555集成电路内部有几十个元器件,有分压器、比较器、基本R-S触发器、放电管

常用数字集成电路管脚图

实验室提供的常用TTL 器件如下: 附录:常用数字集成电路管脚排列及逻辑符号 1A 1B 1Y 2A 2B 2Y 4A 4B 4Y 3A 3B 3Y GND V 图D-1 74LS00四2输入与非门 图D-2 74LS01四2输入与非门(OC ) 8 9 10 11 1 2 12 13 3 14 4 5 6 7 4Y GND 4A 5Y 6A 6Y 5A V CC 1A 1Y 2A 2Y 3A 3Y 。 1。 1 。 1 。 1 。 1 。 1 图D-3 74LS02四2输入或非门 图D-4 74LS04六反相器 8 910 11 121213 314 4567GND & & & & 1A 1B 1Y 2A 2B 2Y 4A 4B 4Y 3A 3B 3Y V CC 8 9 10 11 1212 13 314 4567 1C 1Y 3C 3B 3A 3Y 1A 1B 2A 2B 2C 2Y GND Vcc 。&&&。。 图D-5 74LS08四2输入与门 图D-6 74LS10三3输入与非门 8 9 10 11 1111 2 2 3 3 4 4 5 6 7 Vcc 2D 2C 2B 2A 2Y 1A 1B 1C 1D 1Y GND 。 &。 & N N 1A 1B 2Y 2A 2B 3Y 3A 3B 4Y 4A 4B GND V CC 8 9 10 11 1111 2 2 3 3 4 4 5 6 7 1Y 1 1 1 1 ≥≥≥≥ 图D-7 74LS20双4输入与非门 图D-8 74LS32四2输入或门

8 9 10 11 1212 13 314 45 6 7 ≥1 。 A C D E F N GND N N B H G Y V CC D R S D Q 2D R 1 1D 1CP 1 1Q 1 S D Q GND D Q CP 8 9 10 11 1111 2 2 3 3 4 4567 Q O O D Q CP Q O O D R D S D D R S Vcc 2 2D 2CP 2 2Q 图D-9 74LS54 4路2-2-2-2输入与或非门 图D-10 74LS74双上升沿D 型触发器 1A 1B 2Y 2A 2B 3Y 3A 3B 4Y 4A 4B GND V CC 8 9 10 11 1111 2 2 3 3 4 4 5 6 7 1Y =1 =1 =1 =1 9 10 11 1111 2 2 3 3 4 45678 115 6 Vcc D 2R D 22K 21J 22Q 1R CP CP 1K 1J S D 11Q 1Q 2Q GND K J CP D D Q Q R S S D 。 。 。。。 。 K CP J D R D S Q Q 图D-11 74LS86四2输入异或门 图D-12 74LS112双下降沿J-K 触发器 8 9 10 11 1 2 12 13 3 14 4 5 6 7 GND 1E 1A 1Y 2E 2A 2Y 4E 4A 4Y 3E 3A 3Y V CC EN 1EN 1 EN 1 EN 1 9 10 11 111122 3 3 4 4 5 6 7 8 115 6 Y 0 Vcc Y Y Y Y Y Y 1 2 3 4 5 6 S S Y GND 3 2 1 S A A A 012 7Y 0 Y Y Y Y Y 1 2 3 45 S S Y S A A 12 71 3 2 A 0 Y 6。 。 。 。 。 。 。 。 。 。 图D-13 74LS126四总线缓冲器 图D-14 74LS138 3线-8线译码器 9 10 11 1212 13 314 4567815 16 I 4。I 0 GND V CC I 5I 6I 7I 0 I 1 I 2 I 3 Y 0 Y 1Y 2Y S Y EX S I 1 I 2 I 3 I 4 I 5 I 6 I 7 Y 0 Y 1 Y 2 Y S Y EX S(E)。。。。。。 。。。。。。。 9 10 11 111122 3 3 4 4 5 6 7 8 115 6D 4V C C D D D A A A 56 7 1 2 GND D D D 321D 4D D D A A 56701D W D D 2 1 D 3A 2S ( E ) W S (E )D 0W W 。 。 图D-15 74LS148 8线-3线优先编码器 图D-16 74LS151 8选1数据选择器 9 10 11 1 2 12 13 314 45678 15 16 1D 3GND V CC 1D 21D 11D 0A 0 A 11W 2S 2D 3 2D 2 2D 1 2D 0 2W . . 。 。 A 0 2S 2D 32D 2 2D 1 2D 02W 1D 3 1D 2 1D 1 1D 0 A 11W A 0A 1 1S 9 10 11 12 13 123 14 45678 16 15 GND CR LD CP ENT O O Q CC Q 0Q 1Q 2 Q 3 D 0D 1 D 2D 3ENP D 0D 1D 2D 3ENP V CC Q CC Q 0 Q 1 Q 2 Q 3 ENT LD CP CR 图D-17 74LS153双4选1数据选择器 图D-18 74LS161 4位二进制同步计数器 9 10 11 1212 13 314 45678 15 16 CR GND V CC D SR M 1 CP Q 4 Q 3 M 0 D L D 4Q 1 Q 2 D 3D 2D 1CR Q Q Q Q CP 1 2 3 4 S 1 S 0 D SR D D D D D L 。 1 2 3 4 8 9 10 11 111122 3 34 45 6 7 CT/LD Qc C A QA V CC Q D D B Q B Cr QD Q B QB Qc C A QA CPB GND C r CP A CP B CT /LD CP A 。 。 。 图D-19 74LS194 4位双向移位寄存器 图D-20 74LS196二-五-十进制计数器

附录三 集成电路引脚图

附录三 常用集成电路芯片引脚排列图 74LS00 74LS03 Y=AB四2输入正与非门Y=AB 集电极开路输出的四2输入正与非门 74LS04 74LS08 Y=A六反相器Y=AB 四2输入正与门

74LS10 74LS11 Y=ABC三3输入正与非门Y=ABC 三3输入正与门 74LS20 74LS21 Y=AB C D双4输入正与非门Y=ABCD双4输入正与门74LS32 74LS48 测试 输出 Y=A+B 四2输入正或门BCD-七段译码器

74LS48是具有内部上拉电阻的BCD-七段译码器/驱动器。输出高电平有效,其中,A、B、C、D是输入端,a、b、c、d、e、f是输出。 74LS51 74LS74 Y=CD AB+与或非门双D型正边沿触发器 74LS86 74LS90 2 Y=A⊕B 四2输入异或门十进制计数器(2、5分频) 74LS90是四位十进制计数器。各有两个置“0”(R01、R02)和置“9”(R91、R92)输入端,有两个计数输入端A和B,Q A-Q D为输出。若从A端输入计数脉冲,将Q A与B短接,则组成十进制计数器(分频器);若从B端输入计数脉冲,把Q D与A短接,则组成二~五混合进制计数器(或五分频器)

74LS112 74LS125 双J-K负边沿触发器(带预置和清除端)Y=A三态输出的四总线缓冲门 EN为高时禁止 74LS138 74LS153 输出 选择允许输出 数据输入 选通选择输出 3-8线译码器/分配器双4-1线数据选择器/多路开关 74LS138为3-8线译码器,包含三个允许输入端S1、 2 S、3S,可对8条线中任意一 条进行译码,这取决于三个二进制选择输入端A0、A1、A2和三个允许输入端S1、 2 S、3S 的状态。

51单片机常用芯片引脚图

常用芯片引脚图 一、单片机类 1、MCS-51 芯片介绍:MCS-51系列单片机是美国Intel公司开发的8位单片机,又可以分为多个子系列。 MCS-51系列单片机共有40条引脚,包括32 条I/O接口引脚、4条控制引脚、2条电源引 脚、2条时钟引脚。 引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为 通用I/O接口,第二功能作为存储器扩展时 的地址/数据复用口。 P1.0~P1.7:P1口8位口线,通用I/O接口 无第二功能。 P2.0~P2.7:P2口8位口线,第一功能作为 通用I/O接口,第二功能作为存储器扩展时 传送高8位地址。 P3.0~P3.7:P3口8位口线,第一功能作为 通用I/O接口,第二功能作为为单片机的控 制信号。 ALE/ PROG:地址锁存允许/编程脉冲输入信号线(输出信号) PSEN:片外程序存储器开发信号引脚(输出信号) EA/Vpp:片外程序存储器使用信号引脚/编程电源输入引脚 RST/VPD:复位/备用电源引脚 2、MCS-96 芯片介绍:MCS-96系列单片机是美国Intel公司继MCS-51系列单片机之后推出的16位单 片机系列。它含有比较丰富的软、硬件 资源,适用于要求较高的实时控制场合。 它分为48引脚和68引脚两种,以48引 脚居多。 引脚说明: RXD/P2.1 TXD/P2.0:串行数据传出分发 送和接受引脚,同时也作为P2口的两条 口线 HS1.0~HS1.3:高速输入器的输入端 HS0.0~HS0.5:高速输出器的输出端(有 两个和HS1共用) Vcc:主电源引脚(+5V) Vss:数字电路地引脚(0V) Vpd:内部RAM备用电源引脚(+5V) V REF:A/D转换器基准电源引脚(+5V) AGND:A/D转换器参考地引脚P1.0 P1.1 P1.2 P1.3 P1.4 P1.5 P1.6 P1.7 RST RXD/P3.0 TXD/P3.1 INT0/P3.2 INT1/P3.3 T0/P3.4 T1/P3.5 WR/P3.6 RD/P3.7 XTAL2 XTAL1 V SS

教你如何看懂集成电路的线路图

教你如何看懂集成电路的线路图 集成电路应用电路图具有以下功能: 1.它表达了集成电路各引脚外电路结构、元器件参数等,从而表示了某一集成电路的完整工作情况。 2.有些集成电路应用电路中,画出了集成电路的内电路方框图,这时对分析集成电路应用电路是相当方便的,但这种表示方式不多。 3.集成电路应用电路有典型应用电路和实用电路两种,前者在集成电路手册中可以查到,后者出现在实用电路中,这两种应用电路相差不大,根据这一特点,在没有实际应用电路图时可以用典型应用电路图作参考,这一方法修理中常常采用。 4.一般情况集成电路应用电路表达了一个完整的单元电路,或一个电路系统,但有些情况下一个完整的电路系统要用到两个或更多的集成电路。 集成电路应用电路具有以下特点: 1.大部分应用电路不画出内电路方框图,这对识图不利,尤其对初学者进行电路工作分析时更为不利。 2.对初学者而言,分析集成电路的应用电路比分析分立元器件的电路更为困难,这是对集成电路内部电路不了解的原缘,实际上识图也好、修理也好,集成电路比分立元器件电路更为方便。 3.对集成电路应用电路而言,大致了解集成电路内部电路和详细了解各引脚作用的情况下,识图是比较方便的。这是因为同类型集成电路具有规律性,在掌握了它们的共性后,可以方便地分析许多同功能不同型号的集成电路应用电路。 集成电路的方法和注意事项主要以下几点: 1.了解各引脚的作用是识图的关键了解各引脚的作用可以查阅有关集成电路应用手册。知道了各引脚作用之后,分析各引脚外电路工作原理和元器件作用就方便了。例如:知道①脚是输入引脚,那么与①脚所串联的电容是输入端耦合电路,与①脚相连的电路是输入电路。 2.了解集成电路各引脚作用的三种方法了解集成电路各引脚作用有三种方法:一是查阅有关资料;二是根据集成电路的内电路方框图分析;三是根据集成电路的应用电路中各引脚外电路特征进行分析。对第三种方法要求有比较好的电路分析基础。 3.集成电路应用电路分析步骤如下: ①直流电路分析。这一步主要是进行电源和接地引脚外电路的分析。