FPGA眼图

高速FPGA系统的信号完整性测试和分析

张楷

泰克科技(中国)有限公司

摘要:随着FPGA器件的速度和容量日益提高,各种高速的并行和串行接口都广泛应用在FPGA上,其中典型的高速串行总线速率超过1Gb/s,这为设计和应用人员提供了极大的灵活性,同时对于FPGA IO的测试和验证也带来了新的挑战。本文针对FPGA中各种高速串行总线的信号,提供全面的信号完整性测试和分析方法。

关键词:FPGA,高速串行信号, 信号完整性, 抖动,眼图测试,采样示波器

1. 引言

随着FPGA的设计速度和容量的明显增长,当前流行的FPGA芯片都提供高速总线,例如DDR内存总线,PCI-X总线、SPI总线;针对超高速的数据传输,FPGA通过集成SerDes提供高速串行IO,支持各种诸如PCI-E、GBE、XAUI等高速串行总线协议,为各种不同标准的高速传输提供极大的灵活性。典型的高速FPGA器件提供的每一条物理链路的速度从200Mbps到高达10Gbps,高速IO的测试和验证更成为传统专注于FPGA内部逻辑设计的设计人员面临的巨大挑战。这些挑战使设计人员非常容易会把绝大部分设计周期时间放在调试和检验设计上。

为了加速对于FPGA中高速并行和串行总线的调试和验证,它需要使用新的高速信号完整性测试工具和分析方法。本文根据当前FPGA的高速总线测试和分析,提供了最新的方法和工具。

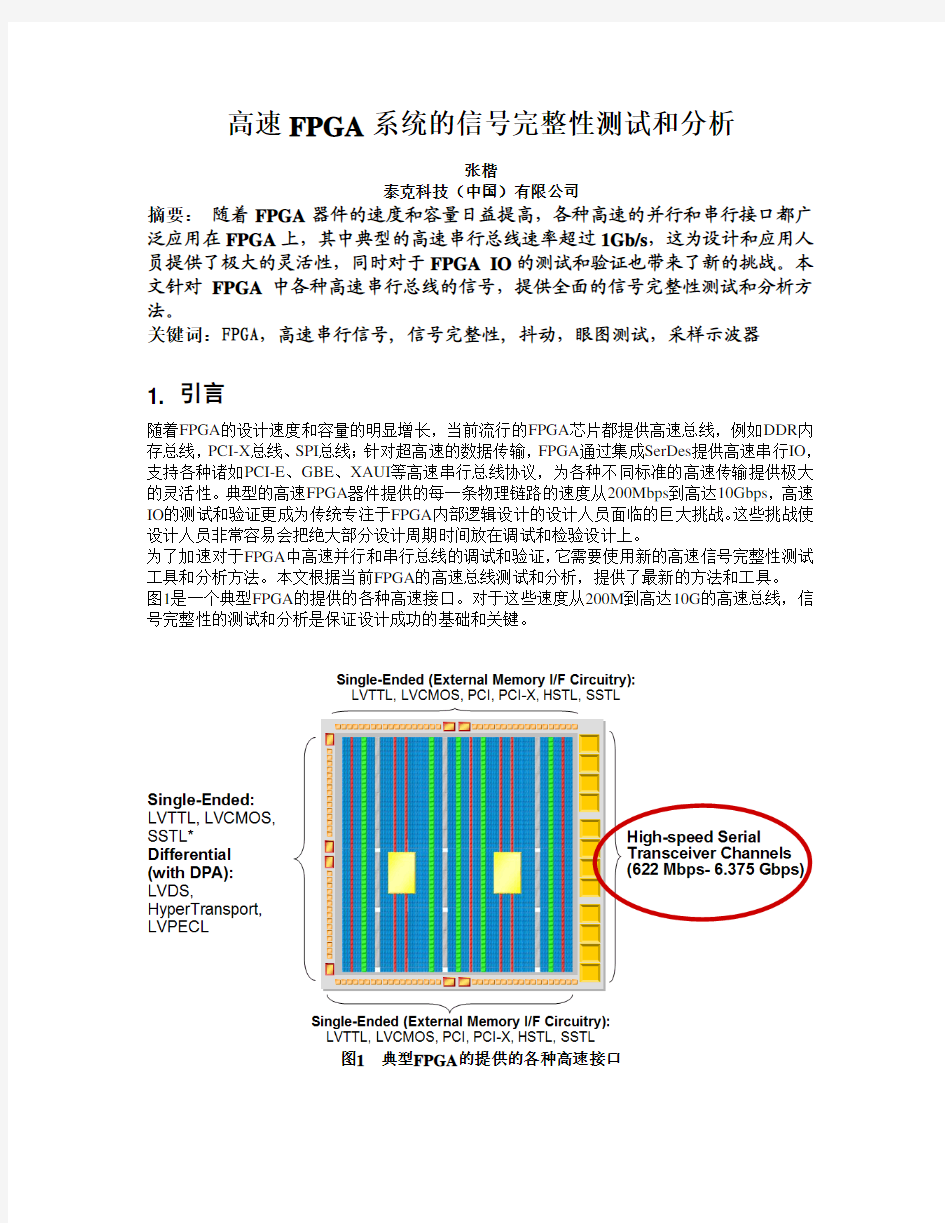

图1是一个典型FPGA的提供的各种高速接口。对于这些速度从200M到高达10G的高速总线,信号完整性的测试和分析是保证设计成功的基础和关键。

图1 典型FPGA的提供的各种高速接口

2. 高速串行总线眼图测试

对于采用内嵌SERDES电路的FPGA芯片,其高速串行信号进行测试和验证,最基本的工具是通过示波器进行对其眼图测试。因为眼图能够非常直观的反映一条被测信号路径上的整体信号质量问题,包括信号的抖动量大小(眼宽)以及幅度的大小(眼高)等重要信息。图2是一个高速数据信号的眼图形成的过程。

图2 眼图的形成过程

从眼图的形成过程可以看出,一个NRZ编码的高速数据无论传输何种码流,都可以看作一个重复信号,经过一定时间和样本数的累计,它反映整个传输链路上的总体信号质量。

3. 选择合适的眼图测试工具

3.1 示波器带宽的要求

示波器是进行高速串行信号眼图测试的首选工具。无论是用高速实时示波器还是采样示波器(Sampling Scope)得到眼图,带宽是对示波器的基本要求。以一个NRZ编码的高速串行总线为例,它理想的波形是一个方波信号,方波信号是由它的基波(正弦波)和奇次谐波(3次,5次,7次…)组成。根据信号的传输速率和上升时间,选择尽量高带宽和最快上升时间的示波器,这样测试结果保留更多的谐波分量,构建高精度的眼图测试结果。

示波器带宽反映了对被测信号幅度上的衰减,而示波器上升时间决定了对被测信号上升时间测试的误差。经典的示波器带宽和上升时间的关系为:带宽×上升时间=0.35-0.45,0.35-0.45为常系数。每一个高性能示波器除了提供带宽的指标外,还会给出上升时间,表征其对阶跃信号的测试能力和精度。示波器测试结果的经验公式为:

高速串行数据(NRZ编码)提供一般为数据率,其最高的基频为比特率的一半。即假设给定一个NRZ编码的串行信号,码型为时钟码型(即传输的数据为1-0-1-0-1),从频域的角度观测该信号,它成为一个基波为数据率一半的方波信号,这个时钟码型是数据变化最快的情况。以泰克TDS6154C 大于15GHz带宽的实时示波器为例,它可以测试保留6.25Gb/s (2×XAUI)信号的五次谐波,以及10Gb/s (XFI)信号的三次谐波。下表列出了不同的高速串行总线在不同测

试精度要求下对示波器带宽的要求。

当示波器系统不能提供足够的系统带宽时,它会衰减对高速信号的高次谐波分量。测试结果除了引入由于示波器带宽不足导致的码间干扰(ISI),电压幅度的异常(过冲和衰减),还会导致抖动量过大,最终眼图模板测试的错误或者测试容限的减小,无法真正反映信号完整性问题。图3 分别是泰克TDS6154C 15GHz带宽和传统DSO 13GHz带宽实时示波器对一个FPGA器件提供的的6.25Gb/s高速数据进行的眼图测试结果比较。图中上半部分显示的眼图有很好的对称性,上升和下降时间更快,信号抖动量很小,真实的反映信号的真实特性。

由于13GHZ的DSO示波器系统带宽不足,无法捕获信号的五次谐波分量,图中下半部分的测试结果反映出眼图上升时间过慢;同时测试的眼图还存在明显的过冲和震铃,测试仪器导致的抖动也掩盖的信号的真正抖动大小。

图3 高速串行数据测试比较(上图为泰克TDS6154C示波器测试结果)

3.2 示波器高速采集内存的要求

当使用实时示波器对于FPGA信号进行信号完整性测试时,利用一次采集的数据构建眼图,所以除了示波器硬件带宽和高速采样率外,采集的数据量的大小非常关键,这样对示波器的高速采集内存就有了更高的要求。下图是在高采样率下,不同高速内存容量下一次捕获的数据量的大小。

采样率10K内存256K内存1M内存64M内存400M内存

10GS/s1us25us100us6400us40ms

20GS/s0.5us12.5us50us3200us20ms

40GS/s0.25us 6.25us25us1600us10ms

当对FPGA的高速信号进行抖动测试时,高速内存长度不仅决定了一次抖动测试中样本数的多少,还决定了示波器能够测试的抖动频率范围。针对信号中的各种低频抖动干扰源,高速采集内存长度是示波器进行低频抖动测试的关键。下表显示的为20GSa/s高采样率下,不同内存长度分析抖动频率范围的大小。

传统高性能示波器设计构架采用将高速采集前端(多达80颗ADC)和高速内存在物理上用一颗SOC芯片实现,由于有太多功能在一个芯片内部实现,导致片内高速内存容量的限制(在20GS/s下小于1M),无论是对于高速串行数据的眼图测试还是对于时钟信号的抖动测试,都存在很大的限制,并且日后无法对内存扩展升级。

为了弥补这种设计结构的缺陷,这类示波器会采用在芯片外部添加低速存储器弥补片内高速内存的限制,但外部存储器不能在高采样率下工作,一般只能提供2GS/s,样点间隔500ps,由于绝大多数信号边沿速度都在皮秒级,2GS/s无法在信号边沿采集足够样点,甚至出现会出现混叠,所以它无法提供有意义的眼图和抖动测试结果。

泰克TDS6154C高速实时示波器采用硅锗(SiGe)半导体集成采集前端,并使用独立的高速

存储器,这样就不受内存长度的限制,并且它同时支持最大采样率和存储长度。

4. 抖动、噪声和BER测试和分析

针对FPGA中不断增长的串行数据传输速率,设计人员不仅进行眼图测试,还需要一套先进的测试和分析工具帮助他们更好地理解和改善他们设计方案的信号完整性。

针对FPGA提供的各种高速串行信号,传统的采样示波器配合抖动分析软件针对FPGA中的高速串行信号能够进行抖动的测试,测试结果的分离,后期的抖动原因的定位和分析,以及水平时间分量上的BER分析。但是,对于导致BER的另一个主要原因,即串行信号中的噪声分量,没有一个彻底的测试和分析方法。图4显示了对于一个高速串行信号的抖动分量和噪声分量影响BER

图4 抖动分量和噪声分量的分解

从事FPGA器件的设计和应用,以及背板的设计和制造的公司在开发基于超高速串行数据标准的产品时需要最高精度的抖动分析,噪声分析以及完整的BER眼图信息。泰克CSA/TDS8200系列采样示波器(Sampling Oscilloscope)测试眼图时,除了传统的眼图和抖动测试外,泰克80SJNB抖动和噪声分析软件提供了对于设计人员和调试人员更有价值的抖动、噪声、BER分析功能。

80SJNB不仅能够得到高精度的眼图测试结果,还能够通过分隔抖动和噪声,加快了识别水平和垂直眼图闭合原因的速度。由于它能够以独特的视角查看抖动和噪声的构成成分,80SJNB 可以高度精确全面地推断BER及分析眼图轮廓。在把抖动、噪声和BER分析与8000系列的模块化灵活性、完善的性能和信号保真度结合在一起时,您可以获得理想的下一代高速串行数据设计检验和一致性测试解决方案。下表列出了80SJNB软件配合泰克CSA/TDS8200系列示波器得到的抖动和噪声分析结果。

高级抖动分析

测量项目说明

TJ@BER 指定BER时的总抖动

RJ 随机抖动

RJ(h) 随机抖动的水平成分

RJ(v) 随机抖动的垂直成分

RJ(σ-σ) 根据双Dirac模型计算得出的随机抖动

DJ 确定性抖动

DDJ 数据相关抖动

DCD 占空比失真

DJ(σ-σ) 根据双Dirac模型计算得出的确定性抖动

PJ 周期抖动

PJ(h) 周期抖动的水平部分

PJ(v) 周期抖动的垂直部分

EOH@BER 指定BER时的水平眼图张开

高级噪声分析

测量项目说明

RN 随机噪声

RN(v) 随机噪声的垂直成分

RN(h) 随机噪声的水平成分

DN 确定性噪声

DDN1 逻辑电平1上的数据相关噪声

DDN0 逻辑电平0上的数据相关噪声

PN 周期噪声

PN(v) 周期噪声的垂直成分

PN(h) 周期噪声的水平成分

EOV@BER 指定BER时的垂直眼图张开

80SJNB软件除了能够得到每一个抖动和噪声分量的精确结果,针对设计和测试人员还提供了各种图形显示进行更细致的信号完整性分析。例如,抖动和噪声成分概率分布, 频谱分布, 数据相关抖动和噪声与位的关系, 数据码型波形, 抖动和噪声浴缸曲线, BER概率图, BER轮廓图, 概率分布眼图。图5是得到的分析结果。

图5 80SJNB软件得到的分析结果

5. 高速并行总线的眼图测试

对于FPGA芯片提供的高速并行总线,由于其数据传送方式并没有采用内嵌时钟的方法,时钟可以作为触发信号,观测多路并行总线的眼图。由于并行总线的通道数比较多,在示波器中手工测试多通道的眼图比较繁琐,有些传统逻辑分析仪虽然能够直接进行并行总线的眼图测试,但无论是测试精度和速度都无法和示波器进行的标准眼图测试相提并论。

除了能够通过FPGA View对简化FPGA的在线调试,TLA逻辑分析仪能够配合TDS示波器对FPGA外部信号自动进行多通道的眼图测试和分析,该功能称为iVerify眼图测试,最多可以自动的测试408个通道的眼图。

泰克为逻辑分析仪和示波器集成提供了一个信号完整性测试工具包,称为iLink工具包,分为iConnect,iView,以及iVerify眼图测试三个工具。iVerify是建立在iConnect技术和iView 技术的基础上,它能够自动对多路并行总线进行眼图测试来彻底验证被测信号。结合iConnect 技术,使用一套逻辑分析仪有源探头进行信号逻辑和模拟的同时观测,逻辑分析仪可以将被测通道分成多组,每一组3个数据通道送入到示波器中进行眼图测试,示波器的第4个通道作为外部时钟;采用iView技术,逻辑分析仪可以自动的将每一次送入示波器的3个数据信号的眼图测试数据会传到逻辑分析仪中,这样逻辑分析仪就可以再选择另外一组3个通道进行测试,对于复杂的高速总线,可以一次测试408个数据通道。最后,iVerify技术通过逻辑分析仪将最多408个数据信号的眼图测试数据叠加显示出来,彻底验证总线中出现的信号完整性问题。图

6是在TLA逻辑分析仪上自动累计的多个通道眼图数据的色温显示。

图14 TLA逻辑分析仪上显示多通道眼图测试结果

6. 小结

对于FPGA中的高速串行和并行IO信号,需要根据被测信号特点和速度来选择合适的测试和分析工具。当测试信号完整性,希望得到最精确的上升时间,下降时间,信号过冲和震铃等参数,带宽是首要选择。某种意义上带宽越高,测试精度越高。对于实时示波器而言,高速采集内存是眼图和抖动等信号完整性测试的关键。对于采样示波器,通过CSA/TDS8200配合80SJNB 抖动和噪声分析软件,不仅可以精确的测量高速串行信号的抖动和噪声,并且能够根据测量结果进行精确的抖动、噪声中每一个分量的分离,和系统的BER相关,最终为信号完整性验证人员提供有价值的信息。当测试高速时钟或数据抖动时,泰克两种示波器都配备业内推荐的抖动测试和分析软件,帮助设计人员得到抖动结果,分析抖动产生的原因,最终得到高可靠性的系统。

Altium公司的FPGA开发板的原理图

1 12 23 34 45 56 67 78 8 D D C C B B A A 1 02 1/02/20101:34:44 PM NB3000_Top.SchDoc Project Title Size: Date:File:Revision:Sheet of Time:A2Sheet Title NB3000 Top Level Assy:81 NB3000AL - Altera D-820-0053 Altium Limited 3 Minna Close Belrose NSW 2085Australia PSU PSU.SchDoc SRAM SRA M1 SRAM_256Kx 16_TSOP44 STATUS_LED U SE R _STATUS_L E DS DB_LEDS_0603 SRAM1 SRAM2 MEM_COMMON DAU_RESET_SW BUZZER ONE_WIRE_DB_PB SW DIP USERIO EXT_A RS232 KEYBOARD MOUSE TFT_IO DB_PROGRAM STATUS_LED USER_LEDS RELAY I2C CODEC VGA ETH DBSD DBUSB PWM SPDIF DAC ADC RS485 MIDI DB_JTAG DB_CLOCKS DB_SPI ISP176X PROTOTYPE SPAREIO TFT_TSC FPGA _USE R FPGA.SCHDOC INT EXT V IDE O_OU T VGA_OUT.SCHDOC CON CON_VGA CON_VGA_DB15 HOST_JTAG LED1LED2 1WID DB_PROGRAM CLK_PLL FLASH_BOOT HOSTUSB SRAM RTC SD HOST_AUDIO DB_JTAG DB_CLOCKS FLASH_USER DB_SPI PB_A EXTSPI FLASH_GOLDEN DIAGCOMMS FPGA _HOST HOST_FPGA.SchDoc HOST_JTAG HOST_JTA G HOST_JTAG.SchDoc INT EXT R S232 RS232_HIN232 EXT INT KE Y BOA RD PC_PS2 RS232# KBD#MSE# RS232 KEYBOARD EXT INT MOUSE PC_PS2 DIPSW DB_RESET CON CON_DBU SB CON_MINI_USBB_RA_KME04-USBMU03A01-1 DBUSB DBUSB# CON CON_DBSD CON_SD_KSDC012551 DBSD EXT INT DBU SB_TX RX USB_CY7C68001-56LFC.SchDoc INT EXT E TH Ethernet_RTL8201CL.SchDoc ETH CLK_PLL CL K_PL L CLK_ICS307-02_PLL 1WID NB_ID 1WB_DS2502_ID CON CON_HOST_USB CON_MINI_USBB_RA_KME04-USBMU03A01-1 TFT_TSC TFT_TOUCH L CDTFT TSC_XPT2046.SchDoc TFT_TSC TFT_IO CON CON_MOU SE CON_PS2PORT_MINIDIN6F_BLACK INT CON PDA _SW ITCHE S SW_PB_SPNOx5_SMD INT TE ST_RE SE T SW_RESET_SPNO CON USERPOWER CON_IO CON_USER_20WBOXHDRRAMx 2 UIO BUZZER CODEC_AUD AUDIO SPK_L SPK_R HOST_AUDIO AIN AOUT_PBA A UDIO_A MP AUDIO_AMP_NB2C PB_AIN AUDIO SPK_L USER_LEDS CON U SE R _L E D LED_RGB_SMDx 8.SCHDOC USER_LEDS VGA# VGA SW SRAM SRA M2 SRAM_256Kx 16_TSOP44 RELAYS CON R E L AY RELAY_X4_IM03GR RELAY PWM CON PW M PWM_5.8A_30V_X4 PWM 1V21V82V53V35V0 PBPOW E R 1V21V82V53V35V0 I2C DIGITAL CODEC_AUD AIN A UDIO_CODE C Audio_Codec.SchDoc CODEC SPK_L SPK_R CON_SPE AKE R S CON_EXT_SPK SPK_R PB_AOUT PBIO LED1LED2 LED1_EXT LED2_EXT L E D_HOST LED_RGB_SMDx 2 SPDIF CON_SPDIF CON_SPDIF_INOUT_A SPDIF SPI CON DAC DAC_DAC084S085_SPI SPI CON A DC ADC_ADC084S021_SPI DAC ADC CON CON_E TH CON_ETHERNET_RJ45_LEDS ETH# TFT_IO TFT_TOUCH CON_L CDTFT CON_FFC40_LCDTFT.SCHDOC CON CON_RE L AY CON_RELAYx 4_KMRJIO3_5MM_12WAY CON CON_RS232 CON_RS232DCE_DB9_TH BOOT_FLASH MOUNTS Mounts.SchDoc INT EXT R S485 RS485_ISL8491 CON_PSU PWJACK+SWITCH.SchDoc HOST_USB HOSTUSB# EXT INT HOST_USB_TXR X USB_CY7C68001-56LFC.SchDoc VBATT CON_BA TT CON_BATT_COIN VBATT VBATT RTC R T CL OCK CLK_PCF2123_RTC HOST_RTC USERPOWER U SE R _POW E R USERPWR.SCHDOC CON CON_HOST_SD CON_SD_KSDC012551 RS485#CON CON_RS485 CON_RS485_RJ45 INT EXT MIDI INTE RFA CE MIDI_FULL CON CON_MIDI CON_MIDI_DIN5 MIDI# MIDI RS485HOST_AUDIO PBCTRL DB_PROGRAM HOST_JTAG HOST_ID HOST_CLK HOST_SRAM HOST_LED1 HOST_LED2 HOST_SD DB_SRAM1 DB_SRAM2 DB_MEM DB_STATUS ADC# RELAYS# PWM# DAC# UIO_PWR DB_JTAG DB_CLOCKS PB_SPI USER_FLASH DB_SPI EXT ONE_WIRE_DB_PB AIN I2C SPI AOUT CTRL PBPOWER CON_PE R IPHE R AL _BRD PBCON USER_LEDS SW_PDA SPARE_IO CON_L E DKBD CON_NB3000_LEDKB SERFLASH SYSBOOT FLASH_M25PX0_SPI_8Mbit GOLD_FLASH SERFLASH GOL DE N FLASH_M25PX0_SPI_8Mbit FLASH U SE R _FL A SH FLASHSPI_M25PX0 INT SW _DIP8_SM T SW_DIP8_SMT CON CON_KE YBOAR D CON_PS2PORT_MINIDIN6F_BLACK CON CON_USB1 CON_USBA_RA_UPRIGHT LEDS# ATE DIAGCOMMS A TE INTE R FACE CON_NB3000_ATE_INTF ISP176X PORT1 PORT2 PORT3 U SB_U SE RHOST USB_ISP1760 ATE VGA#SPDIF UIO ADC#DAC#AUDIO HOST_JTAG PWM RS232#RS485#KBD#MSE#MIDI# HOST_ID A TE INTE R FACE VGA#SPDIF UIO ADC# DAC# AUDIO HOST_JTAG PWM# RS232#RS485#KBD#MSE#MOUSE ISP176X PORT1 PORT2 PORT3 PROTOTYPE U SE R _PROTOTYPE _AR E A PROTOTYPE_A PROTOTYPE CON CON_AU DIO CON_AUDIO_AC99_NOMIC.SCHDOC DIAGCOMMS MIDI# HOST_ID SW# SPAREIO MEM COMM ON_ME M OR Y CommonMemory CON CON_ADC CON_ADCx 4_KMRJIO3_5MM_6WAY CON CON_DAC CON_DACx 4_KMRJIO3_5MM_6WAY CON CON_PW M CON_PWMx4_KMRJIO3_5MM_6WAY CON CON_USB2 CON_USBA_RA_UPRIGHT CON CON_USB3 CON_USBA_RA_UPRIGHT SRAM SRA M_HOST SRAM_256Kx 16_TSOP44 TFT_TOUCH INT U SB_CL K OSC_24MHZ.SchDoc HOST_USB.XTALIN HOST_USB.XTALOUT CMOSOUT XTALIN XTALOUT OSC DBUSB.XTALIN

FPGA原理图方式设计流程图

2 Quartus II软件的使用、开发板的使用 本章将通过3个完整的例子,一步一步的手把手的方式完成设计。完成这3个设计,并得到正确的结果,将会快速、有效的掌握在Altera QuartusII软件环境下进行FPGA设计与开发的方法、流程,并熟悉开发板的使用。 2.1 原理图方式设计3-8译码器 一、设计目的 1、通过设计一个3-8译码器,掌握祝组合逻辑电路设计的方法。 2、初步了解QuartusII采用原理图方式进行设计的流程。 3、初步掌握FPGA开发的流程以及基本的设计方法、基本的仿真分析方法。 二、设计原理 三、设计内容 四、设计步骤 1、建立工程文件 1)双击桌面上的Quartus II的图标运行此软件。

开始界面 2)选择File下拉菜单中的New Project Wizard,新建一个工程。如图所 示。 新建工程向导

3)点击图中的next进入工作目录。 新建工程对话框 4)第一个输入框为工程目录输入框,用来指定工程存放路径,建议可根据自己需要更改路径,若直接使用默认路径,可能造成默认目录下存放多个工程文件影响自己的设计,本步骤结束后系统会有提示(当然你可不必理会,不会出现错误的)。第二个输入框为工程名称输入框。第三个输入框为顶层实体名称输入框,一般情况下保证工程名称与顶层实体名称相同。设定完成后点击next。

指定工程路径、名称 5)设计中需要包含的其它设计文件,在此对话框中不做任何修改,直接点 击next。 工程所需其它文件对话框

6)在弹出的对话框中进行器件的选择。在Device Family框中选用Cyclone II,然后在Available device框中选择EP2C35F484C8,点击next进入下一步。 器件选择界面 7)下面的对话框提示可以勾选其它的第三方EDA设计、仿真的工具,暂时不作任何选择,在对话框中按默认选项,点击next。

【精品博文】基于FPGA的原理图PCB设计

【精品博文】基于FPGA的原理图PCB设计 我的开发工具:Cadence 16.6,所用FPGA为Altera 家的。画FPGA原理图需准备以下资料:(1) 原理图库文件(2) 芯片手册(3) Pin out file原理图库文件可以从官网上下载,比如我用cadence画Altera家EP4CE115F29I7N原理图,就直接下载EP4CE115.OLB文件。 https://https://www.360docs.net/doc/0f11436344.html,/support/support-resources/downlo ad/board-layout-test/pcb/pcb-cadence.html原理图中,这种大量管脚的芯片一般分为多个part,包括电源、地、各个bank、配置等。芯片手册几乎给出了关于这个芯片设计(Cyclone IV Device Handbook)的所有需注意的问题,包括配置方式、全局时钟网络、专用时钟接口、lvds接口等。pin out file中有每个管脚的详细说明。(1)芯片配置配置方式主要有JTAG 或AS模式我只预留JTAG接口,有些板子上预留了两个下载接口,一个JTAG,用于下载程序,一个AS,用于固化程序,感觉这样很麻烦,我在固化时选择JIC(JTAG Indirect Configuration File)文件,尽管相对于AS模式会固化程序 会慢一点,但毕业还是JTAG方式,这样就省去了烦琐的 AS模式。JTAG方式有用的信号其实就4个:TCK(测试时钟)、TDO(测试数据输出)、TMS(测试模式选择)、TDI (测试数据输入),再加上VCC和GND,共6根线,所以

其实可以把标准10pin下载口简化为6pin,标准10pin下载口体积大,而6pin连接器可以自己选择,这样更方便。nConfig、nStatus、CONF_DONE、TMS、TDI需要上拉,TCK需要下拉。配置芯片一般为EPCS系列,如EPCS64,EPCS128,相应地,可以用ST公司的M25P64和M25P128代替,连接方式如下图所示。画完原理图,一定要检查下面16个管脚,连接是否正确,否则,板子很可能不工作(2)专用时钟专用时钟输入与输出的选择仍然需要参考,首先,专用时钟输入管脚都是可以驱动内部PLL的,可以配置为普通IO输入,但不能配置为输出管脚,之前有一次就因为没太注意,把这个管脚用作了输出,结果板子出了问题。而专用时钟输出管脚,可以用于普通IO输出,也可以用于时钟输出。设计时,最好是把专用时钟输入管脚全部用作时钟输入,把专用时钟输出管脚全部胜任专用时钟输出,毕竟,IO 资源一般不会这么紧张。(3)lvds设计关于lvds设计,需要仔细看技术手册和Pin-Out Files for Altera Devices,下载地址: https://https://www.360docs.net/doc/0f11436344.html,/support/literature/lit-dp.html#Cyclo ne-IV对于c4,rx和tx复用,见Cyclone IV Device Handbook 第133页,从pin out file里也可以看出,P和N都是确定好了的,如DIFFIO_T35P和DIFFIO_T35N。 而对于c5器件,存在专用lvds通道,rx和tx是分开的,例

FPGA最小系统原理图

电源电路:5V 转3.3V 、2.5V ;3.3V 转1.2V 。 复位电路 晶振电路 JTAG 接口 FLASH C270.1u C320.1u C90.1u C120.1u C460.1u 0 SW2 SW_PB_SPST nCONFIG C13

MAX232串口电路 P AGE : 1 of 5 DATE : March 2010 P AGE : 2 of 5 DATE : March 2010 VE RSION : 1.0P AGE : 3 of 5 DATE : March 2010 P1-3VREFB1N07VREFB2N031VREFB3N046VREFB4N065VREFB5N080VREFB6N0105 VREFB7N0119VREFB8N0 136 CLK1_23/ DIFFCLK_0N 23CLK2_24/ DIFFCLK_1P 24CLK3_25/ DIFFCLK_1N 25CLK4_91/ DIFFCLK_2P 91CLK5_90/ DIFFCLK_2N 90CLK6_89/ DIFFCLK_3P 89CLK7_88/ DIFFCLK_3N 88P AGE : 4 of 5 DATE : March 2010 P AGE : 5 of 5 DATE : March 2010 CLK 50M PIN25RST N PIN91PIN90PIN88 PIN89IO 7 IO 80 IO 65 IO 46 IO 31 IO 119 IO 105IO 136

TXD IO 142IO 141RXD IO 115IO 114IO 112IO 113IO 110IO 121IO 120IO 111IO 126IO 125IO 124IO 127IO 135IO 129IO 128DATA0IO 137IO 133IO 138IO 132 ASDO IO 99IO 103nCSO IO 86IO 87IO 101IO 98IO 31IO 7IO 80IO 65IO 46IO 136IO 119IO 105RST N CLK 50M PIN91 PIN25J2 HEADER 22x2/SM J3 HEADER 22x2/SM 2468101214161820222426283032343638404244 135791113151719212325272931333537394143

FPGA结构与原理

FPGA 结构与原理初步 查找表((Look-Up-Table)的原理与结构 一.查找表 采用这种结构的PLD芯片我们也可以称之为FPGA:如altera的ACEX,APEX系列,xilinx 的Spartan,Virtex系列等。 查找表(Look-Up-Table)简称为LUT,LUT本质上就是一个RAM。目前FPGA中多使用4输入的LUT,所以每一个LUT可以看成一个有4位地址线的16x1的RAM。当用户通过原理图或HDL语言描述了一个逻辑电路以后,PLD/FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。 下面是一个4输入与门的例子, 实际逻辑电路LUT的实现方式 a,b,c,d 输入 逻辑输出地址RAM中存储的内容 0000 0 0000 0 0001 0 0001 0 .... 0 0 1111 1 1111 1 基于查找表((LUT)的FPGA的结构 二.基于查找表 我们看一看xilinx Spartan-II的内部结构,如下图:

xilinx Spartan-II 芯片内部结构Slices结构 Spartan-II主要包括CLBs,I/O块,RAM块和可编程连线(未表示出)。在spartan-II中,一个CLB包括2个Slices,每个slices包括两个LUT,两个触发器和相关逻辑。Slices可以看成是SpartanII实现逻辑的最基本结构(xilinx其他系列,如SpartanXL,Virtex的结构与此稍有不同,具体请参阅数据手册) altera的FLEX/ACEX等芯片的结构如下图:

FPGA经典面试题

FPGA与CPLD内部结构区别? CPLD 以altraMAX7000这种PLD为例,可分为三块结构:宏单元(Marocell),可编程连线(PIA)和I/O控制块。宏单元是PLD的基本结构,由它来实现基本的逻辑功能。可编程连线负责信号传递,连接所有的宏单元。I/O控制块负责输入输出的电气特性控制,比如可以设定集电极开路输出,摆率控制,三态输出等。 这种基于乘积项(实际就是与或阵列)的PLD基本都是由EEPROM和Flash 工艺制造的,一上电就可以工作,无需其他芯片配合。布线方式是全局的,所以延时可预测。CPLD适合做逻辑设计。 FPGA FPGA基于LUT,LUT本质上就是一个RAM,每一个LUT可以看成一个有4位地址线的16x1的RAM。这也是为什么FPGA需要外接一个rom来上电配置。 以xilinx的Spartan-II为例,主要包括CLBs,I/O块,RAM块和可编程连线。在spartan-II中,一个CLB包括2个Slices,每个slices包括两个LUT,两个触发器和相关逻辑。Slices可以看成是SpartanII实现逻辑的最基本结构。 FPGA的制造工艺确定了FPGA芯片中包含的LUT和触发器的数量非常多,往往都是几千上万,PLD一般只能做到512个逻辑单元,而且如果用芯片价格除以逻辑单元数量,FPGA的平均逻辑单元成本大大低于PLD。所以如果设计

中使用到大量触发器,例如设计一个复杂的时序逻辑,那么使用FPGA就是一个很好选择。 https://www.360docs.net/doc/0f11436344.html,tch和Register区别?行为描述中Latch如何产生? 本质的区别在于:latch是电平触发,reg是边沿触发。时序设计中尽量使用reg触发。 行为描述中,如果对应所有可能输入条件,有的输入没有对应明确的输出,系统会综合出latch。 比如:always@( a or b) //缺少else语句 begin if(a==1) q <= b; end 3.对竞争冒险的理解,以及如何消除? 在组合逻辑中,由于门的输入信号通路中经过了不同的延时,导致到达该门的时间不一致叫竞争。产生毛刺叫冒险。如果布尔式中有相反的信号则可能产生竞争和冒险现象。解决方法:一是添加布尔式的消去项,二是在芯片外部加电容。 4.用Verilog设计一个5分频器。 5分频,奇数分频都可以类似这么做,只需要改div1和div2的参数。div1为奇数分频除2的余数。采用上升延和下降延分别触发不同波形,最后叠加的方式产生奇数分频。 module divfreq(clk, clk1x, rst, clk1xpose, clk1xnege, coutpose, coutnege);

1.2.1FPGA工作原理与简介如前所述,FPGA是在PAL、GAL、EPLD、CPLD等可编

1.2.1 FPGA工作原理与简介 如前所述,FPGA是在PAL、GAL、EPLD、CPLD等可编程器件的基础上进一步发展的产物。它是作为ASIC领域中的一种半定制电路而出现的,即解决了定制电路的不足,又克服了原有可编程器件门电路有限的缺点。 由于FPGA需要被反复烧写,它实现组合逻辑的基本结构不可能像ASIC那样通过固定的与非门来完成,而只能采用一种易于反复配置的结构。查找表可以很好地满足这一要求,目前主流FPGA都采用了基于SRAM工艺的查找表结构,也有一些军品和宇航级FPGA采用Flash或者熔丝与反熔丝工艺的查找表结构。通过烧写文件改变查找表内容的方法来实现对FPGA的重复配置。 根据数字电路的基本知识可以知道,对于一个n输入的逻辑运算,不管是与或非运算还是异或运算等等,最多只可能存在2n种结果。所以如果事先将相应的结果存放于一个存贮单元,就相当于实现了与非门电路的功能。FPGA的原理也是如此,它通过烧写文件去配置查找表的内容,从而在相同的电路情况下实现了不同的逻辑功能。 查找表(Look-Up-Table)简称为LUT,LUT本质上就是一个RAM。目前FPGA中多使用4输入的LUT,所以每一个LUT可以看成一个有 4位地址线的的RAM。当用户通过原理图或HDL语言描述了一个逻辑电路以后,PLD/FPGA开发软件会自动计算逻辑电路的所有可能结果,并把真值表(即结果)事先写入 RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。 下面给出一个4与门电路的例子来说明LUT实现逻辑功能的原理。 例1-1:给出一个使用LUT实现4输入与门电路的真值表。 表1-1 4输入与门的真值表 从中可以看到,LUT具有和逻辑电路相同的功能。实际上,LUT具有更快的执行速度和更大的规模。 由于基于LUT的FPGA具有很高的集成度,其器件密度从数万门到数千万门不等,可以完成极其复杂的时序与逻辑组合逻辑电路功能,所以适用于高速、高密度的高端数字逻辑电路设计领域。其组成部分主要有可编程输入/输出单元、基本可

FPGA考试复习资料

一、填空题: 1、 FPGA结构一般分为三部分:可编程逻辑块(CLB)、可编程I/O模块和可编程内部连线。 2、 CPLD的内部连线为连续式布线互连结构,任意一对输入、输出端之间的延时是固定;FPGA的内部连线为分段式布线互连结构,各功能单元间的延时不定(不可预测)。 3、大规模可编程器件主要有CPLD和FPGA两类,其中CPLD通过可编程乘积项逻辑实现其逻辑功能。基于SRAM的FPGA器件,每次上电后必须进行一次配置。FPGA内部阵列的配置一般采用在电路可重构技术,编程数据保存在静态存储器(SRAM) ,掉电易失。 4、目前世界上有十几家生产CPLD/FPGA的公司,最大的两家是:Altera,Xilinx。 5、硬件描述语言(HDL)是EDA技术的重要组成部分,是电子系统硬件行为描述、结构描述、数据流描述的语言,它的种类很多,如VHDL、Verilog HDL、AHDL 6、 WHEN_ELSE条件信号赋值语句和 IF_ELSE顺序语句的异同: * WHEN_ELSE条件信号赋值语句中无标点,只有最后有分号;必须成对出现;是并行语句,必须放在结构体中。 * IF_ELSE顺序语句中有分号;是顺序语句,必须放在进程中 7、可编程逻辑器件设计输入有原理图输入、硬件描述语言输入和波形输入三种方式。原理图输入方式是一种最直接的设计描述方式,波形设计输入适用于时序逻辑和有重复性的逻辑函数。 硬件描述语言的突出优点是: * 语言与工艺的无关性;语言的公开可利用性,便于实现大规模系统的设计; * 具有很强逻辑描述和仿真功能,而且输入效率高,在不同设计输入库之间的转换非常方便,用不着对底层的电路和PLD结构的熟悉。8、用VHDL/Veilog HDL语言开发可编程逻辑电路的完整流程:文本编辑→功能仿真→逻辑综合→布局布线→时序仿真。 *所谓综合,就是根据设计功能和实现该设计的约束条件(如面积、速度、功耗和成本等),将设计输入转换成满足要求的电路设计方案,该方案必须同时满足与其的功能和约束条件。综合的过程也是设计目标的优化过程,其目的是将多个模块化设计文件合并为一个网表文件,供布局布线使用,网表中包含了目标器件中的逻辑单元和互连的信息。 *布局布线就是根据设计者指定的约束条件(如面积、延时、时钟等)、目标器件的结构资源和工艺特性,以最优的方式对逻辑元件布局,并准确地实现元件间的互连,完成实现方案(网表)到使实际目标器件(FPGA或CPLD)的变换。 9、基于EDA软件的FPGA / CPLD设计流程为:原理图/HDL文本输入→功能仿真→综合→适配→时序仿真→编程下载→硬件测试。 * 综合是EDA设计的关键步骤,综合就是将电路的高级语言转换成低级的,可与FPGA/CPLD相映射的功能网表文件。为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束。 10、构成一个完整的VHDL语言程序的五个基本结构: 实体(ENTITY)、结构体(ARCHITECURE)、配置(CONFIGURATION) 、库(LIBRARY) 、程序包 (PACKAGE) 。 *实体的由实体说明和结构体两部分组成。实体说明部分用于描述所设计系统的外部端口信号和参数的属性和设置,而结构体部分则定义了设计单元的具体功能、行为、数据流程或内部结构。 *结构体的三种描述方式,即行为级描述、数据流级描述和结构级描述。 *结构体通常由结构体名称、定义语句和并行处理语句构成。 *程序包用于存放各设计模块能共享的数据类型、常数、子程序等。 *库用于存放已编译的实体、结构体、程序包和配置,可以通过其目录进行查询和调用。在VHDL语言中,可以存在多个不同的库,但是库与库之间是独立的,不能互相嵌套。它可由用户生成或由ASIC芯片制造商提供,以便于在设计中为大家所共享。 *库用于存放已编译的实体、结构体、程序包和配置,可以通过其目录进行查询和调用。在VHDL语言中,可以存在多个不同的库,但是库与库之间是独立的,不能互相嵌套。它可由用户生成或由ASIC芯片制造商提供,以便于在设计中为大家所共享。 常用库: (1)IEEE库:IEEE库主要包括std_logic_1164、numeric_bit、numeric_std等程序包,还有一些程序包非IEEE标准,但并入IEEE库,如 std_logic_arich、std_logic_unsigned、std_logic_signed。使用IEEE程序包,必须声明。 (2) std库:包含 standard textio程序包。Std库符合IEEE标准,应用中不必声明。 (3) work库:用户的VHDL设计先行工作库。 (4) vital 库:包含时序程序包vital_timing和vital_primitives。设计开发过程通常不用,每个设计实体都必须有各自完整的库说明语句和use语句。Use语句的使用将使说明的程序包对本设计实体部分全部开放,即是可视的。 11、VHDL的数据对象包括常量(constant)、变量(varuable) 和信号(signal) ,它们是用来存放各种类型数据的容器。 12、在VHDL的端口声明语句中,端口方向包括 in 、out 、buffer 、inout、linkage 。“BUFFER”为缓冲端口,与OUT类似,只是缓冲端口允许实体内部使用该端口信号,它可以用于输出,也可以用于端口信号的反馈。当一个结构体用“BUFFER”说明输出端口时,与其连接的另一个结构体的端口也要用BUFFER说明。以“LINKAGE”定义的端口不指定方向,无论哪个方向的信号都可以连接。 13、VHDL的PROCESS(进程)语句是由顺序语句组成的,但其本身却是并行语句。 14、VHDL的子程序有过程(PROCEDURE) 和函数(FUNCTION) 两种类型,具有可重载性特点。