74ls00 是常用的2输入四与非门集成电路

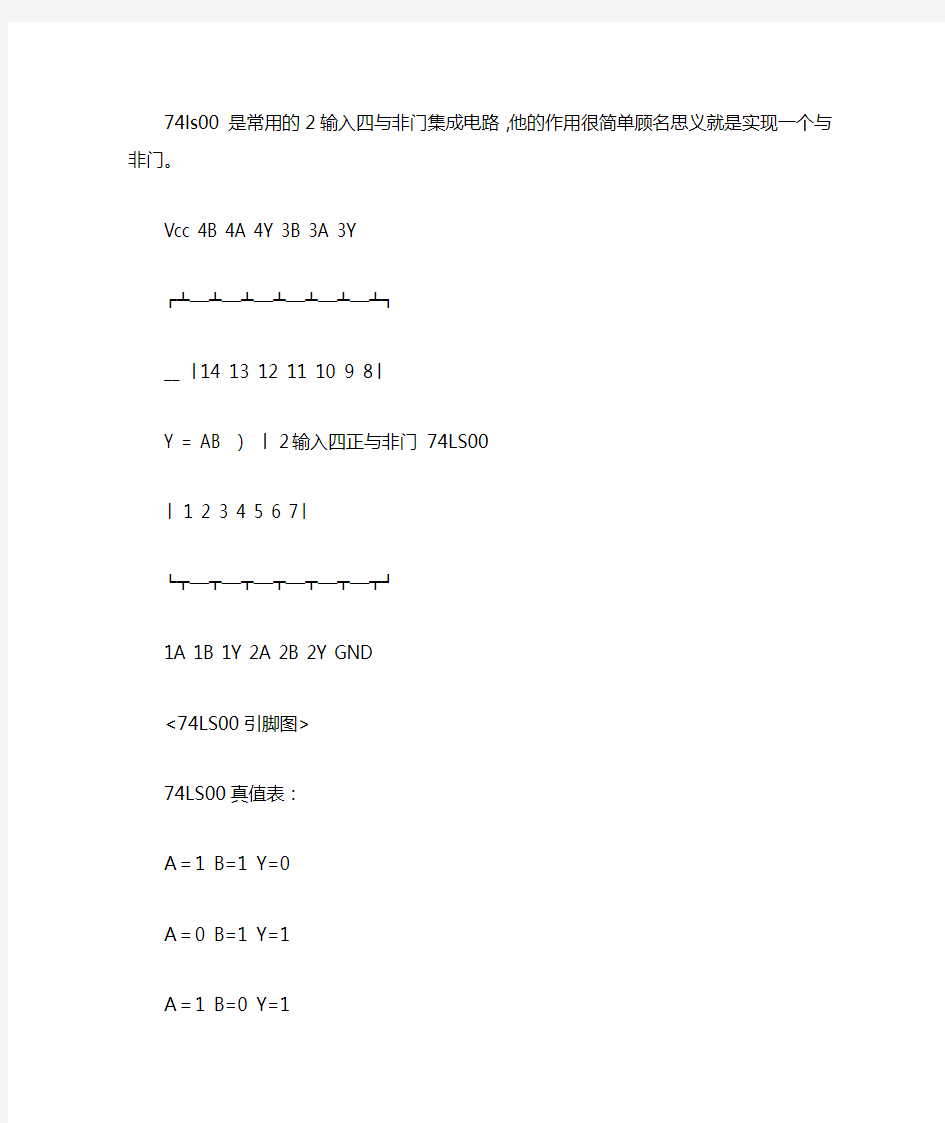

74ls00 是常用的2输入四与非门集成电路,他的作用很简单顾名思义就是实现一个与非门。

Vcc 4B 4A 4Y 3B 3A 3Y

┌┴—┴—┴—┴—┴—┴—┴┐

__ │14 13 12 11 10 9 8│

Y = AB )│ 2输入四正与非门 74LS00

│ 1 2 3 4 5 6 7│

└┬—┬—┬—┬—┬—┬—┬┘

1A 1B 1Y 2A 2B 2Y GND

<74LS00引脚图>

74LS00真值表:

A=1 B=1 Y=0

A=0 B=1 Y=1

A=1 B=0 Y=1

A=0 B=0 Y=1

Vcc 4B 4A 4Y 3B 3A 3Y

┌┴—┴—┴—┴—┴—┴—┴┐

__ │14 13 12 11 10 9 8│

Y = AB )│ 2输入四正与非门 74LS00

│ 1 2 3 4 5 6 7│

└┬—┬—┬—┬—┬—┬—┬┘

1A 1B 1Y 2A 2B 2Y GND

<74LS08引脚图>

是常用的2输入四正与门电路

74LS08真值表:

a b y

0 0 0

0 1 0

1 0 0

1 1 1

电路四输入与非门设计

课程设计任务书 学生姓名:专业班级:电子1003班 指导教师:封小钰工作单位:信息工程学院 题目: CMOS四输入与非门电路设计 初始条件: 计算机、ORCAD软件、L-EDIT软件 要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求) 1、课程设计工作量:2周 2、技术要求: (1)学习ORCAD软件、L-EDIT软件。 (2)设计一个CMOS四输入与非门电路。 (3)利用ORCAD软件、L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。 3、查阅至少5篇参考文献。按《武汉理工大学课程设计工作规范》要求撰写设计报告书。全文用A4纸打印,图纸应符合绘图规范。 时间安排: 2013.11.22布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。 2013.11.25-11.27学习ORCAD软件、L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。 2013.11.28-12.5对CMOS四输入与非门电路进行设计仿真工作,完成课设报告的撰写。 2013.12.6 提交课程设计报告,进行答辩。 指导教师签名:年月日 系主任(或责任教师)签名:年月日

摘要........................................................................ I Abstract ................................................................... II 1 绪论 (1) 2 设计内容及要求 (2) 2.1 设计的目的及主要任务 (2) 2.2 设计思想 (2) 3软件介绍 (3) 3.1 OrCAD简介 (3) 3.2 L-Edit简介 (4) 4 COMS四输入与非门电路介绍 (5) 4.1 COMS四输入与非门电路组成 (5) 4.2 四输入与非门电路真值表 (6) 5 Cadence中四输入与非门电路的设计 (7) 5.1 四输入与非门电路原理图的绘制 (7) 5.2 四输入与非门电路的仿真 (8) 6 L-EDIT中四输入与非门电路版图的设计 (10) 6.1 版图设计的基本知识 (10) 6.2 基本MOS单元的绘制 (11) 6.3 COMS四输入与非门的版图设计 (13) 7课程设计总结 (14) 参考文献 (15)

四2输入或非门74AC02

74AC02 QUAD 2-INPUT NOR GATE April 1997s HIGH SPEED:t PD =4.5ns (TYP.)at V CC =5V s LOW POWER DISSIPATION:I CC =4μA (MAX.)at T A =25o C s HIGH NOISE IMMUNITY:V NIH =V NIL =28%V CC (MIN.) s 50?TRANSMISSION LINE DRIVING CAPABILITY s SYMMETRICAL OUTPUT IMPEDANCE:|I OH |=I OL =24mA (MIN) s BALANCED PROPAGATION DELAYS:t PLH ?t PHL s OPERATING VOLTAGE RANGE:V CC (OPR)=2V to 6V s PIN AND FUNCTION COMPATIBLE WITH 74SERIES 02 s IMPROVED LATCH-UP IMMUNITY DESCRIPTION The AC02is an advanced high-speed CMOS QUAD 2-INPUT NOR GATE fabricated with sub-micron silicon gate and double-layer metal wiring C 2MOS technology.It is ideal for low power applications mantaining high speed operation similar to equivalent Bipolar Schottky TTL. The internal circuit is composed of 3stages including buffer output,which enables high noise immunity and stable output. All inputs and outputs are equipped with protection circuits against static discharge,giving them 2KV ESD immunity and transient excess voltage. PIN CONNECTION AND IEC LOGIC SYMBOLS ORDER CODES : 74AC02B 74AC02M M (Micro Package) B (Plastic Package)1/7

输入与非门电路版图设计

成绩评定表

课程设计任务书

目录 1 绪论 (1) 1.1设计背景 (1) 1.2设计目标 (1) 2 四输入与非门电路 (2) 2.1电路原理图 (2) 2.2四输入与非门电路仿真观察波形 (2) 2.3四输入与非门电路的版图绘制 (3) 2.4四输入与非门版图电路仿真观察波形 (4) 2.5LVS检查匹配 (5) 总结 (7) 参考文献 (8) 附录一:电路原理图网表 (9) 附录二:版图网表 (10)

1 绪论 1.1 设计背景 tanner是用来IC版图绘制软件,许多EDA系统软件的电路模拟部分是应用Spice程序来完成的,而tanner软件是一款学习阶段应用的版图绘制软件,对于初学者是一个上手快,操作简单的EDA软件。 Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows 平台的用于集成电路设计的工具软件。该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度。 L-Edit Pro是Tanner EDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。L-Edit Pro包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS Library、Marco Library,这些模块组成了一个完整的IC设计与验证解决方案。L-Edit Pro丰富完善的功能为每个IC设计者和生产商提供了快速、易用、精确的设计系统。 1.2设计目标 1.用tanner软件中的原理图编辑器S-Edit编辑四输入与非门电路原理图。 2.用tanner软件中的W-Edit对四输入与非门电路进行仿真,并观察波形。 3.用tanner软件中的L-Edit绘制四输入与非门版图,并进行DRC验证。 4.用W-Edit对四输入与非门的版图电路进行仿真并观察波形。 5.用tanner软件中的layout-Edit对四输入与非门进行LVS检验观察原理图与版图的匹配程度。

设计一 四位与非门的电路设计

四位与非门的电路设计 一、课程设计的目的 1、学会使用电路设计与仿真软件工具Hspice ,熟练地用网表文件来描述模拟电路,并熟悉应用Hspice 内部元件库。通过该实验,掌握Hspice 的设计方法,加深对课程知识的感性认识,增强电路设计与综合分析能力。 2、本次课程设计是用Hspice 软件来实现对四位与非门电路的设计与仿真,熟悉用MOS 器件来设计四位逻辑输入与非门电路,了解用MOS 器件设计与TTL 与非门的优缺点。 二、课程设计的内容和要求 1、内容:用仿真软件HSPICE ,用网表文件来描述模拟电路; 2、要求:用MOS 器件来设计四位逻辑输入与非门电路。 三、设计的原理 1、四输入与非门符号图及原理 A OUTPUT NAND4 1 2 3 45 D C B 真值表如下所示

A B C D Y 0 0 0 0 1 0 0 0 1 1 0 0 1 0 1 0 0 1 1 1 0 1 0 0 1 0 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1 0 0 0 1 1 0 0 1 1 1 0 1 0 1 1 0 1 1 1 1 1 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 0 四输入端CMOS与非门电路,其中包括四个串联的N沟道增强型MOS管和四个并联的P沟道增强型MOS管。每个输入端连到一个N沟道和一个P沟道MOS管的栅极。当输入端A、B、C、D中只要有一个为低电平时,就会使与它相连的NMOS管截止,与它相连的PMOS管导通,输出为高电平;仅当A、B、C、D全为高电平时,才会使四个串联的NMOS管都导通,使四个并联的PMOS管都截止,输出为低电平。设计电路图如下图所示:

最新与门电路和与非门电路原理培训资料

什么是与门电路及与非门电路原理? 什么是与门电路 从小巧的电子手表,到复杂的电子计算机,它们的许多元件被制成集成电路的形式,即把几十、几百,甚至成干上万个电子元件制作在一块半导体片或绝缘片上。每种集成电路都有它独特的作用。有一种用得最多的集成电路叫门电路。常用的门电路有与门、非门、与非门。 什么是门电路 “门”顾名思义起开关作用。任何“门”的开放都是有条件的。例如.一名学生去买书包,只买既好看又给买的,那么他的家门只对“好看”与“结实”这两个条件同时具备的书包才开放。 门电路是起开关作用的集成电路。由于开放的条件不同,而分为与门、非门、与非门等等。 与门 我们先学习与门,在这之前请大家先看图15-16,懂得什么是高电位,什么是低电位。

图15-17甲是我们实验用的与用的与门,它有两个输入端A、B和一个输出端。图15-17乙是它连人电路中的情形,发光二极管是用来显示输出端的电位高低:输出端是高电位,二极管发光;输出端是低电位,二极管不发光。 实验 照图15-18甲、乙、丙、丁的顺序做实验。图中由A、B引出的带箭头的弧线,表示把输入端接到高电位或低电位的导线。每次实验根据二极管是否发光,判定输出端电位的高低。

输入端着时,它的电位是高电位,照图15-18戊那样,让两输人端都空着,则输出瑞的电位是高电位,二极管发光。 可见,与门只在输入端A与输入端B都是高电位时,输出端才是高电位;输入端A、B只要有一个是低电位,或者两个都是低电位时,输出端也是低电位。输人端空着时,输出端是高电位。 与门的应用 图15-19是应用与门的基本电路,只有两个输入端A、B同低电位间的开关同时断开,A与B才同时是高电位,输出端也因而是高电位,用电器开始工作。

数字电路组合逻辑电路设计实验报告

数字电路组合逻辑电路设 计实验报告 The Standardization Office was revised on the afternoon of December 13, 2020

实验三组合逻辑电路设计(含门电路功能测试)

一、实验目的 1.掌握常用门电路的逻辑功能 2.掌握小规模集成电路设计组合逻辑电路的方法 3.掌握组合逻辑电路的功能测试方法 二、实验设备与器材 Multisim 、74LS00 四输入2与非门、示波器、导线 三、实验原理 TTL集成逻辑电路种类繁多,使用时应对选用的器件做简单逻辑功能检查,保证实验的顺利进行。 测试门电路逻辑功能有静态测试和动态测试两种方法。静态测试时,门电路输入端加固定的高(H)、低电平,用示波器、万用表、或发光二极管(LED)测

出门电路的输出响应。动态测试时,门电路的输入端加脉冲信号,用示波器观测输入波形与输出波形的同步关系。 下面以74LS00为例,简述集成逻辑门功能测试的方法。74LS00为四输入2与非门,电路图如3-1所示。74LS00是将四个二输入与非门封装在一个集成电路芯片中,共有14条外引线。使用时必须保证在第14脚上加+5V电压,第7脚与底线接好。 整个测试过程包括静态、动态和主要参数测试三部分。 表3-1 74LS00与非门真值表 1.门电路的静态逻辑功能测试 静态逻辑功能测试用来检查门电路的真值表,确认门电路的逻辑功能正确与否。实验时,可将74LS00中的一个与非门的输入端A、B分别作为输入逻辑变量,加高、低电平,观测输出电平是否符合74LS00的真值表(表3-1)描述功能。

7400TTL2输入端四与非门

7400TTL2输入端四与非门 7401TTL集电极开路2输入端四与非门7402TTL2输入端四或非门 7403TTL集电极开路2输入端四与非门7404TTL六反相器 7405TTL集电极开路六反相器 7406TTL集电极开路六反相高压驱动器7407TTL集电极开路六正相高压驱动器7408TTL2输入端四与门 7409TTL集电极开路2输入端四与门7410TTL3输入端3与非门

74107TTL带清除主从双J-K触发器74109TTL带预置清除正触发双J-K触发器7411TTL3输入端3与门 74112TTL带预置清除负触发双J-K触发器7412TTL开路输出3输入端三与非门74121TTL单稳态多谐振荡器 74122TTL可再触发单稳态多谐振荡器74123TTL双可再触发单稳态多谐振荡器74125TTL三态输出高有效四总线缓冲门74126TTL三态输出低有效四总线缓冲门7413TTL4输入端双与非施密特触发器

74132TTL2输入端四与非施密特触发器74133TTL13输入端与非门 74136TTL四异或门 74138TTL3-8线译码器/复工器 74139TTL双2-4线译码器/复工器7414TTL六反相施密特触发器 74145TTLBCD—十进制译码/驱动器7415TTL开路输出3输入端三与门74150TTL16选1数据选择/多路开关74151TTL8选1数据选择器 74153TTL双4选1数据选择器

74154TTL4线—16线译码器 74155TTL图腾柱输出译码器/分配器 74156TTL开路输出译码器/分配器 74157TTL同相输出四2选1数据选择器 74158TTL反相输出四2选1数据选择器7416TTL开路输出六反相缓冲/驱动器 74160TTL可预置BCD异步清除计数器74161TTL可予制四位二进制异步清除计数器74162TTL可预置BCD同步清除计数器74163TTL可予制四位二进制同步清除计数器74164TTL八位串行入/并行输出移位寄存器74165TTL八位并行入/串行输出移位寄存器

四输入或非门课程设计

四输入或非门专项实践任务书学生姓名:专业班级: 指导教师:工作单位: 题目: 四输入或非门的设计 初始条件: 计算机、ORCAD软件,L-EDIT软件 要求完成的主要任务:(包括集成电路专项实践工作量及其技术要求,以及说明书撰写 等具体要求) 1、集成电路专项实践工作量:1周 2、技术要求: (1)学习ORCAD软件,L-EDIT软件。 (2)设计一个四输入或非门电路。 (3)利用ORCAD软件,L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。 3、查阅至少5篇参考文献。按《武汉理工大学课程设计工作规范》要求撰写设计报告书。全文用A4纸打印,图纸应符合绘图规范。 时间安排: 布置集成电路专项实践任务、选题;讲解集成电路专项实践具体实施计划与课程设计报告格式的要求;集成电路专项实践答疑事项。 学习ORCAD软件,L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。 用ORCAD软件设计四输入或非门电路并进行仿真工作,再利用L-EDIT软件绘制其版图,完成集成电路专项实践报告的撰写。 提交集成电路专项实践报告,进行答辩。 指导教师签名:年月日系主任(或责任教师)签名:年月日

目录 摘要 ............................................................................................................................................................ Abstract ...................................................................................................................................................... I 1 绪论 0 2 设计内容及要求 (1) 设计的目的及主要任务 (1) 设计思路 (1) 3软件介绍 (1) OrCAD简介 (1) L-Edit简介 (3) 4四输入或非门 (4) 四输入或非门电路结构 (4) 四输入或非门电路仿真 (5) 四输入或非门的版图绘制 (6) NMOS管 (6) PMOS管 (7) 输出端口 (7) 四输入或非门 (7) 总结 (9) 参考文献 (11)

Lab 2 二与非门电路原理图设计

Lab 2 二与非门电路原理图设计 1.实验目的 1.1了解Schematic设计环境 1.2掌握二与非门电路原理图输入方法 1.3掌握逻辑符号创建方法 2.实验原理 2.1Schematic设计环境 启动Schematic Editor后,在命令解释窗口CIW中,打开任意库与单元中的Schematic视图,浏览Schematic Editing窗口如图2.1所示,顶部为菜单栏(Menu),左侧为图标栏(Icon Bar),具体介绍如下: 图2.1 Schematic Editing窗口 菜单栏 菜单栏中可选菜单有Tool、Design、Window、Edit、Add、Check、Sheet、Options等项。其中常用菜单有: Tool菜单提供设计工具以及辅助命令。比如,lab4、lab5所使用的仿真工具ADE,就在Tool下拉菜单中。 Window菜单中的各选项有调整窗口的辅助功能。比如,Zoom选项对窗口放大(Zoom in)与缩小(Zoom out),fit选项将窗口调整为居中,redraw选项为刷新。 Edit菜单实现具体的编辑功能,主要有取消操作(Undo)、重复操作(Redo)、拉伸(Stretch)、拷贝(copy)、移动(Move)、删除(Delete)、旋转(Rotate)、属性(Properties)、选择(Select)、查找(Search)等子菜单,在以下实验中将大量应用。 Add菜单用于添加编辑所需要的各种素材,比如元件(Instance)或输入输出端点(pin)等。 图标栏 图标栏内的所有命令都可以在菜单栏实现,图标栏提供使用频率较高的一些

用门电路设计一位的全加器

实验二组合逻辑设计 一、实验目的 1、掌握组合电路设计的具体步骤和方法; 2、巩固门电路的运用和电路搭建能力; 3、掌握功能表的建立与运用; 4、为体验MSI(中规模集成电路)打基础。 二、实验使用的器件和设备 四2输入异或门74LS86 1片 四2输入正与非门74LS00 1片 TDS-4数字系统综合实验平台1台 三、实验内容 1.测试四2输入异或门74LS86 一个异或门的输入和输出之间的逻辑关系。 2.测试四2输人与非门74LS00一个与非门的输入和输出之间的逻辑关系。 3.等价变换Si=Ai○十Bi○十Ci-1 Ci=AiBi +(Ai○十Bi)Ci-1 4.画出变换后的原理图和接线图。 四、实验过程 1、选择实验题目,分析逻辑功能 用门电路设计一位的全加器 一位全加器:在进行两个数的加法运算时不仅要考虑被加数和加数而且要考虑前一位(低位)向本位的进位的一种逻辑器件。 2、根据逻辑功能写出真值表; 3、根据真值表写出逻辑函数表达式; Si=Ai○十Bi○十Ci-1 Ci=AiBi +(Ai○十Bi)Ci-1 4、利用卡诺图法或布尔代数法对逻辑函数表达式进 行化简; 不需化简 Si=Ai○十Bi○十Ci-1 Ci=AiBi +(Ai○十Bi)Ci-1 5、将化简的逻辑表达式等价变换,统计出实验所需芯片;

Si=Ai○十Bi○十Ci-1 所需芯片: 四2输入异或门74LS86 1片 四2输入正与非门74LS00 1片 6、根据各芯片的引脚图,测试所有需用芯片的功能,画出各芯片的功能表; VCC VCC 74LS86接线图 74LS00接线图 74LS 86芯片测试结果74LS00 芯片测试结果

4012 CMOS 双4输入与非门

TL F 5940CD4002M CD4002C Dual 4-Input NOR Gate CD4012M CD4012C Dual 4-Input NAND Gate March 1988 CD4002M CD4002C Dual 4-Input NOR Gate CD4012M CD4012C Dual 4-Input NAND Gate General Description These NOR and NAND gates are monolithic complementa-ry MOS (CMOS)integrated circuits The N-and P-channel enhancement mode transistors provide a symmetrical cir-cuit with output swings essentially equal to the supply volt-age This results in high noise immunity over a wide supply voltage range No DC power other than that caused by leak-age current is consumed during static conditions All inputs are protected against static discharge and latching condi-tions Features Y Wide supply voltage range 3 0V to 15V Y Low power 10nW (typ )Y High noise immunity 0 45V DD (typ ) Applications Y Automotive Y Alarm system Y Data terminals Y Industrial controls Y Instrumentation Y Remote metering Y Medical Electronics Y Computers Connection Diagrams CD4002 Dual-In-Line Package TL F 5940–1Top View CD4012 Dual-In-Line Package TL F 5940–2 Top View Order Number CD4002or CD4012 C 1995National Semiconductor Corporation RRD-B30M105 Printed in U S A

CMOS与非门集成电路设计

CMOS与非门集成电路设计 目录 一、实践目的 (1) 二、实践要求 (1) 三、实验内容 (1) (一)与非门 (1) (二)Tanner Pro EDA工具简介 (1) (三)使用S-Edit设计电路原理图 (3) (四)T-Spice模拟分析 (7) (五)L-Edit版图设计 (12) (六)LVS比较 (20) 四、与非门工作曲线分析 (23) (一)直流分析 (23) (二)负载电容瞬态分析 (26) 五、实践总结 (30)

一、实践目的 根据半导体集成电路和VLSI课程所学知识,以及数字电路等课程的知识,使用集成电路工艺完成CMOS与非门单元电路的设计。希望通过此单元电路的全面学习来完全掌握数字集成电路的设计流程,熟练掌握Tanner Pro EDA工具软件的使用。 二、实践要求 所完成的电路设计包括逻辑表达式,真值表,电路原理图及仿真曲线图,版图,LVS报告,后仿真曲线及分析。负载要求可驱动1pF电容,在测试中分别加载1fF,100fF,500fF,0.5pF,1pF,2pF电容,进行延时以及曲线slop等比较。 三、实验内容 (一)与非门 与非门是与门和非门的结合,先进行与运算,再进行非运算。其电路符号、逻辑表达式和真值表如图3.1.1所示。 图3.1.1、与非门 (二)Tanner Pro EDA工具简介 Tanner Pro是一套集成电路设计软件,包括S-EDIT,T-SPICE,W-EDIT,

L-EDIT,与LVS。他们的主要功能分别如下: ↗S-Edit:编辑电路原理图 ↗T-Spice:电路分析与仿真模拟 ↗W-Edit:显示T-Spice模拟波形结果 ↗L-Edit:编辑布局图、自动配置与绕线、设计规则检查、截面观察、电路转化 ↗LVS:电路图与布局结果对比 Tanner Pro的设计流程可用图3.2.1表示。将要设计的电路先以S-Edit编辑出电路图,再将该电路图输出成SPICE文件。接着利用T-Spice将电路图模拟并输出成SPICE文件,如果模拟结果有错误,返回S-Edit检查电路图,如果T-Spice 模拟结果无误,则以L-Edit进行布局图设计。用L-Edit进行布局图设计后要以DRC 功能做设计规则检查,若违反设计规则,再将布局图进行修改直到设计规则检查无误为止。将验证过的布局图转化成SPICE文件,再利用T-Spice模拟,若有错误,再回到L-Edit修改布局图。最后利用LVS将电路图输出的SPICE文件与布局图转化的SPICE文件进行对比,若对比结果不相等,则回去修正L-Edit 或S-Edit的图。直到验证无误后,将L-Edit设计好的布局图输出成GDSII文件类型,再交由工厂去制作半导体过程中需要的掩膜版。 图3.2.1、Tanner设计流程

四输入或非门课程设计

四输入或非门专项实践任务书 学生姓名:专业班级: 指导教师:工作单位: 题目:四输入或非门的设计 初始条件: 计算机、ORCAD软件,L-EDIT软件 要求完成的主要任务:(包括集成电路专项实践工作量及其技术要求,以及说明书撰写 等具体要求) 1、集成电路专项实践工作量:1周 2、技术要求: (1)学习ORCAD软件,L-EDIT软件。 (2)设计一个四输入或非门电路。 (3)利用ORCAD软件,L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。 3、查阅至少5篇参考文献。按《武汉理工大学课程设计工作规范》要求撰写设计报告书。全文用A4纸打印,图纸应符合绘图规范。 时间安排: 2015619布置集成电路专项实践任务、选题;讲解集成电路专项实践具体实施计划与课程设计报告格式的要求;集成电路专项实践答疑事项。 2015619-6.24学习ORCAD软件,L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。 2015.6.24-7.1用ORCAD软件设计四输入或非门电路并进行仿真工作,再利用L-EDIT 软件绘制其版图,完成集成电路专项实践报告的撰写。 2015.7.1提交集成电路专项实践报告,进行答辩。 指导教师签名:年月日

系主任(或责任教师)签名: 目录 摘要 .................................................................................... I Abstract ................................................................................................................................................... II 1绪论 (1) 2设计内容及要求 (2) 2.1设计的目的及主要任务 (2) 2.2设计思路 (2) 3软件介绍 (2) 3.1 OrCAD 简介 (2) 3.2 L-Edit 简介 (4) 4四输入或非门 (5) 4.1 四输入或非门电路结构 (5) 4.2 四输入或非门电路仿真 (6) 4.3四输入或非门的版图绘制 (7) 4.3.1 NMOS 管 (7) 4.3.2 PMOS 管 (8) 4.3.3输出端口 (8) 4.3.4 四输入或非门 (8) 总结 (10) 参考文献 (12)

与非门版图设计

目录 1绪论 (2) 1.1 设计背景 (2) 1.2设计目标 (2) 2与门电路设计 (3) 2.1电路原理 (3) 2.2电路结构 (3) 2.3与门电路仿真波形 (4) 2.4与门电路的版图绘制及DRC验证 (5) 2.5与门电路版图仿真 (6) 2.6 LVS检查匹配 (6) 总结 (8) 参考文献 (9) 附录一版图网表: (10) 附录二电路图网表 (12)

1绪论 1.1 设计背景 Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows 平台的用于集成电路设计的工具软件。该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度。 L-Edit Pro是Tanner EDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。L-Edit Pro包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS Library、Marco Library,这些模块组成了一个完整的IC设计与验证解决方案。L-Edit Pro丰富完善的功能为每个IC设计者和生产商提供了快速、易用、精确的设计系统。 1.2设计目标 1.用MOS场效应管实现二输入与门电路。 2.用tanner软件中的原理图编辑器S-Edit编辑反相器电路原理图。 3.用tanner软件中的W-Edit对反相器电路进行仿真,并观察波形。 4.用tanner软件中的L-Edit绘制反相器版图,并进行DRC验证。 5.用W-Edit对反相器的版图电路进行仿真并观察波形。 6.用tanner软件中的layout-Edit对反相器进行LVS检验观察原理图与版图的 匹配程度。

二输入与非门、或非门版图设计

课程名称Course 集成电路设计技术 项目名称 Item 二输入与非门、或非门版图设 计 与非门电路的版图: .spc文件(瞬时分析): * Circuit Extracted by Tanner Research's L-Edit / Extract ; * TDB File: E:\cmos\yufeimen, Cell: Cell0 * Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\ * Extract Date and Time: 05/25/2011 - 10:03 .include H:\ VPower VDD GND 5 va A GND PULSE (0 5 0 5n 5n 100n 200n) vb B GND PULSE (0 5 0 5n 5n 50n 100n) .tran 1n 400n .print tran v(A) v(B) v(F) * WARNING: Layers with Unassigned AREA Capacitance. *

*

* * WARNING: Layers with Unassigned FRINGE Capacitance. * * * 四输入与非门课程设计任务书 学生姓名:专业班级: 指导教师:工作单位: 题目: CMOS四输入与非门电路设计 初始条件: 计算机、ORCAD软件、L-EDIT软件 要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求) 1、课程设计工作量:2周 2、技术要求: (1)学习ORCAD软件、L-EDIT软件。 (2)设计一个CMOS四输入与非门电路。 (3)利用ORCAD软件、L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。 3、查阅至少5篇参考文献。按《武汉理工大学课程设计工作规范》要求撰写设计报告书。全文用A4纸打印,图纸应符合绘图规范。 时间安排: 2013.11.22布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。 2013.11.25-11.27学习ORCAD软件、L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。 2013.11.28-12.5对CMOS四输入与非门电路进行设计仿真工作,完成课设报告的撰写。 2013.12.6 提交课程设计报告,进行答辩。 指导教师签名:年月日 系主任(或责任教师)签名:年月日 摘要........................................................................ I Abstract ................................................................... II 1 绪论 (1) 2 设计内容及要求 (2) 2.1 设计的目的及主要任务 (2) 2.2 设计思想 (2) 3软件介绍 (3) 3.1 OrCAD简介 (3) 3.2 L-Edit简介 (4) 4 COMS四输入与非门电路介绍 (5) 4.1 COMS四输入与非门电路组成 (5) 4.2 四输入与非门电路真值表 (6) 5 Cadence中四输入与非门电路的设计 (7) 5.1 四输入与非门电路原理图的绘制 (7) 5.2 四输入与非门电路的仿真 (8) 6 L-EDIT中四输入与非门电路版图的设计 (10) 6.1 版图设计的基本知识 (10) 6.2 基本MOS单元的绘制 (11) 6.3 COMS四输入与非门的版图设计 (13) 7课程设计总结 (14) 参考文献 (15) 四人表决器的设计 设计要求 某特殊足球评委会由一位教练和三位球迷组成,对裁判员的判罚进行表决时,当满足以下条件即表示同意: (1)有三人或三人以上同意; (2)有两人同意,但其中一人必须是教练。 1、方案论证与对比 1.1方案一 1.1.1设计电路如图2 1.2 方案二 用2输入与非门设计,同样可根据表2的真值表作卡诺图以及它的逻辑函数表达式,这里省略没作,因为与方案一比劣势明显。该方案的电路图如下: 图1 2输入与非门接线图 1.3 方案对比与选择 该电路的原理和方案一的区别不大,只是这个全部用的2输入与非门来实现,这个方案中其一元器件使用太过单一,而方案一中用了译码器74HC138,这就使我们更加的熟悉了译码器的适用。其二方案一也大大减少了连线的交叉程度,方案二中因为一个芯片中含有几个与非门,只用一个又太浪费,全部用连线就会有很多交叉,使得用protel布线时带来很大的困难。所以综合以上两个原因我们选择了方案一。 2、分析与设计 2、1 译码器结构分析 四人表决器即要求四个输入端,三个球迷用三线-八线的译码器,但教练的身份比较特别,为使电路简单就直接接逻辑开关[1]。 74HC138是3线-8线译码器,其功能表如表1所示。该译码器有3位二进制输入A0,A1,A2,它们共有8种状态的组合,即可译出8个输出信号Y0-Y7,输出为低电平有效。此外,还设计了E3、E2和E13个是能输入端,为电路功能的扩展提供了方便。由功能表可知,当E3=1,且E2=E1=0时,译码器处于工作状态[2]。 由功能表可得: Y0=E3*E2*E1*A2*A1*A0 根据各输出的逻辑表达式可以写出最初的逻辑表达式,根据学校元件库能提供的元件,对逻辑表达式化简,于是最终确定完成本次设计的所有元器件,然后画出原理图,见图1 该表清楚的表达出74HC138的逻辑功能,即三输入八输出和使能端的有效电平,同时说明了74HC138的工作状态和输出有效电平。 由74HC138译码器和几个非门,或非门和与门组成的原理图电路,接通电源就进入工作状态,通过开关导通或打开表示输入各评委的投票结果,后面通过发光二极管输出并显示投票结果。 课程设计任务书 学生姓名:王伟专业班级:电子1001班 指导教师:刘金根工作单位:信息工程学院题目: 基于CMOS的二输入与门电路 初始条件: 计算机、Cadence软件、L-Edit软件 要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰 写等具体要求) 1、课程设计工作量:2周 2、技术要求: (1)学习Cadence IC软件和L-Edit软件。 (2)设计一个基于CMOS的二输入的与门电路。 (3)利用Cadence和L-Edit软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。 3、查阅至少5篇参考文献。按《武汉理工大学课程设计工作规范》要求撰写设计报告书。全文用A4纸打印,图纸应符合绘图规范。 时间安排: 2013.11.22布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。 2013.11.25-11.27学习Cadence IC和L-Edit软件,查阅相关资料,复习所设计内容的基本理论知识。 2013.11.28-12.5对二输入与门电路进行设计仿真工作,完成课设报告的撰写。 2013.12.6 提交课程设计报告,进行答辩。 指导教师签名:年月日系主任(或责任教师)签名:年月日 目录 摘要 (2) 绪论 (3) 一、设计要求 (4) 二、设计原理 (4) 三、设计思路 (4) 3.1、非门电路 (4) 3.2、二输入与非门电路 (6) 3.3、二输入与门电路 (8) 四、二输入与门电路设计 (9) 4.1、原理图设计 (9) 4.2、仿真分析 (10) 4.3、生成网络表 (13) 五、版图设计................................................... (20) 5.1、PMOS管版图设计 (20) 5.2、NMOS管版图设计 (22) 5.3、与门版图设计 (23) 5.4、总版图DRC检查及SPC文件的生成 (25) 六、心得体会 (28) 七、参考文献 (29) 八、附录 (30) TL F 644154LS02 DM54LS02 DM74LS02 Quad 2-Input NOR Gates June1989 54LS02 DM54LS02 DM74LS02 Quad2-Input NOR Gates General Description This device contains four independent gates each of which performs the logic NOR function Features Y Alternate Military Aerospace device(54LS02)is avail- able Contact a National Semiconductor Sales Office Distributor for specifications Connection Diagram Dual-In-Line Package TL F 6441–1 Order Number54LS02DMQB 54LS02FMQB 54LS02LMQB DM54LS02J DM54LS02W DM74LS02M or DM74LS02N See NS Package Number E20A J14A M14A N14A or W14B Function Table Y e A a B Inputs Output A B Y L L H L H L H L L H H L H e High Logic Level L e Low Logic Level C1995National Semiconductor Corporation RRD-B30M105 Printed in U S A电路四输入与非门设计 - 副本

四人表决器的设计 课程设计报告

集成电路课程设计(CMOS二输入与门).

2输入四或非门74LS02