锁相环输出信号相位噪声噪声及杂散特性分析应用实践

锁相环输出信号相位噪声噪声及杂散特性分析应用实践

【摘要】本文详细地介绍了锁相环的鉴频鉴相器、分频器和输入参考信号的相位噪声对锁相环合成输出信号的近端相位噪声的具体贡献值。并以CDMA 1X基站系统中800MHz的FS 单板的锁相环输出信号相位噪声指标进行理论计算。为广大锁相环设计者提供理论计算方法的参考和实践设计的参考依据。

【关键词】锁相环设计,相位噪声

一、术语和缩略语

表格 1 术语和缩略语

二、问题的提出

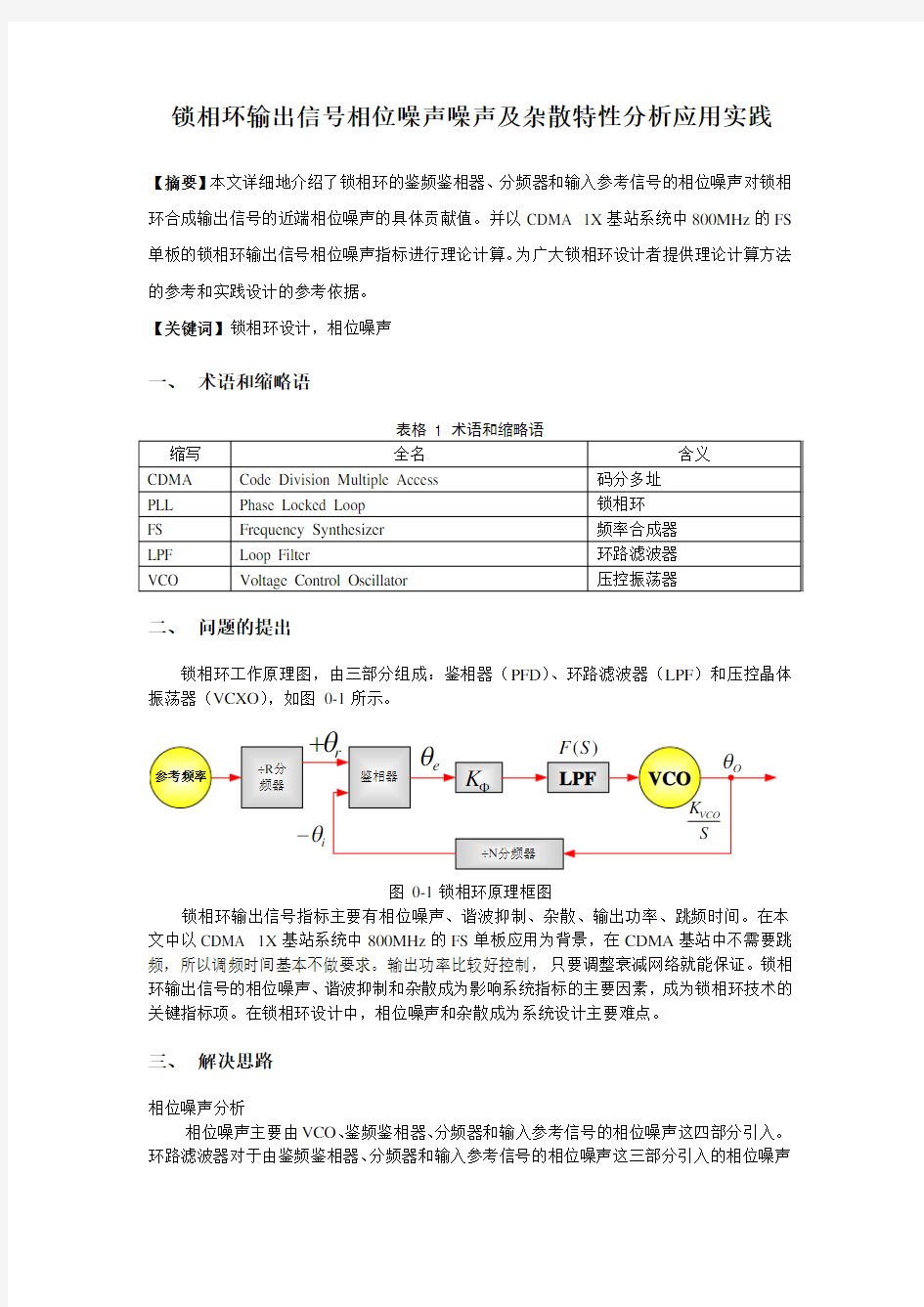

锁相环工作原理图,由三部分组成:鉴相器(PFD)、环路滤波器(LPF)和压控晶体振荡器(VCXO),如图0-1所示。

图0-1锁相环原理框图

锁相环输出信号指标主要有相位噪声、谐波抑制、杂散、输出功率、跳频时间。在本文中以CDMA1X基站系统中800MHz的FS单板应用为背景,在CDMA基站中不需要跳频,所以调频时间基本不做要求。输出功率比较好控制,只要调整衰减网络就能保证。锁相环输出信号的相位噪声、谐波抑制和杂散成为影响系统指标的主要因素,成为锁相环技术的关键指标项。在锁相环设计中,相位噪声和杂散成为系统设计主要难点。

三、解决思路

相位噪声分析

相位噪声主要由VCO、鉴频鉴相器、分频器和输入参考信号的相位噪声这四部分引入。环路滤波器对于由鉴频鉴相器、分频器和输入参考信号的相位噪声这三部分引入的相位噪声

具有低通特性,对于VCO产生的相位噪声具有高通特性。一般来说环路带宽内的相位噪声主要决定于由鉴频鉴相器、分频器和输入参考信号,环路带宽以外的相位噪声主要决定于VCO,在环路带宽周围,这四部分的噪声影响相当。所以为了尽量降低输出信号的相位噪声环路滤波器的环路带宽的最佳点是由鉴频鉴相器、分频器和输入参考信号的相位噪声这三部分引入的相位噪声总和与VCO引入的相位噪声相同时的频率。在实际运用中还礼滤波器的设计是非常重要的。对于远端相位噪声如100KHz和1MHz处的一般远远高于环路带宽,其相位噪声主要决定于VCO,要保证其指标主要是选择良好的VCO。而近端相位噪声如100Hz主要由鉴频鉴相器、分频器和输入参考信号的相位噪声决定,但如果还礼带宽取得很小的话如200Hz则VCO的影响也将非常之大。而如果环路带宽远远大于1KHz如为6KHz 以上时1KHz处的相位噪声也将主要由鉴频鉴相器、分频器和输入参考信号的相位噪声决定。下面就分别分析这三部分相位噪声。

由鉴相器引入的相位噪声

由于鉴相器引入的相位噪声为:

PD Phase Noise = ( 1 Hz Normalized Phase Noise Floor from Table )

+ 10log( Comparison Frequency ) + 20log( N )

现在FS板的中频环路采用的PLL芯片为NS的LMX2306,其相位噪声基底为-210dBc/Hz。

在CDMA 1X 基站系统800MHz的FS单板中采用的鉴相频率为30KHz,两个中频分别为69.99MHz和114.99MHz,由鉴相器产生的相位噪声为:

69.99MHz:

PD Phase Noise= -210+10log(30000)+20log(69990000/30000)= -97.9dBc/Hz 114.99MHz:

PD Phase Noise= -210+10log(30000)+20log(114990000/30000)=-93.5dBc/Hz 射频本振范围为754~779MHz。步进为30KHz,鉴相频率为240KHz。对于779MHz 的本振由鉴相器引入的相位噪声为:

PD Phase Noise= -210+10log(240000)+20log(779000000/240000)=-85.9dBc/Hz

由分频器引入的相位噪声

由分频器引入的相位噪声的计算公式入下:

DIV Phase Noise = (Device Phase Noise Floor )+ 20log( N )

PLL芯片中分频器的相位噪声在器件手册中并没有给出。一般高频分频器的相位噪声基底约为-165dBc/Hz左右。因此就假设分频器的相位噪声基底为-165dBc/Hz,于是得到分频器引起的相位噪声如下:

69.99MHz的中频频率为:

DIV Phase Noise= -165+20log(69990000/30000)= -97.6dBc/Hz

114.99MHz的中频频率为:

DIV Phase Noise= -165+20log(114990000/30000)= -93.3dBc/Hz

779MHz的射频频率为:

DIV Phase Noise= -165+20log(779000000/240000)= -94.7dBc/Hz

由参考信号引入的相位噪声

参考信号引起的相位噪声的计算公式如下

REF Phase Noise = (REF’S Phase Noise )-20log(R)+ 20log( N )

系统的参考信号都是由GPSTM模块提供的,GPSTM输出的参考信号的相位噪声为-130dBc/Hz@100Hz和-145dBc/Hz@1KHz。最后参考信号通过FDM板到FS板,FDM板输

出的参考信号的相位噪声为-120dBc/Hz@100Hz和-130dBc/Hz@1KHz。在单板调试和测试时使用的参考信号12MHz的采用了OCXO的输出,10MHz的参考信号采用了VCO/PLL测试仪4352B的10MHz参考输出,其相位噪声应该比GPSTM差些应该接近FDM的输出。这两个参考信号用4352B VCO/PLL测试仪测试出的相位噪声如下两图所示:其中图0-2为OCXO输出的相位噪声图,图0-3为VCO/PLL测试仪的10MHz参考输出相位噪声图。

图0-2用4352B测试出的OCXO的12MHz输出相位噪声

图0-3用4352B测试出的其10MHz的参考输出相位噪声

由上面两张图分析这两个输出的相位噪声在100Hz和1KHz射分别约为-80dBc/Hz和-105dBc/Hz,于刚才分析的分别约为-120dBc/Hz和-130dBc/Hz差别较大,这应该是由于测试仪器产生的,也就是说4352B VCO/PLL测试仪在100Hz和1KHz时基本只能测到-80dBc/Hz和-105dBc/Hz。

下面假定使用的参考信号的相位噪声就为上面提到的为-120dBc/Hz@100Hz和

【重要】锁相环的相位噪声分析

锁相环路相位噪声分析 张文军 电信0802 【摘要】本文对锁相电路的相位噪声进行了论述,并对其中各组成部件的相位噪声也做了较为详细的分析。文中最后提出了改进锁相环相位噪声的办法。 【关键词】锁相环;相位噪声;分析 引言 相位噪声是一项非常重要的性能指标,它对电子设备和电子系统的影响很大,从频域看它分布的载波信号两旁按幂律谱分布。用这种信号无论做发射激励信号,还是接收机本振信号以及各种频率基准,这些信号在解调过程中都会和信号一样出现在解调终端,引起基带信噪比下降。在通信系统中使环路信噪比下将,误码率增加;在雷达系统中影响目标的分辨能力,即改善因子。接收机本振的相位噪声遇到强干扰信号时,会产生“倒混频”,使接收机有效噪声系数增加。随着电子技术的发展,对频率源的信号噪声要求越来越严格,因此低相位噪声在物理、天文、无线电通信、雷达、航空、航天以及精密计量、仪器仪表等各种领域里都受到重视。 1 相位噪声概述 相位噪声 ,就是指在系统内各种噪声作用下所表现的相位随机起伏,相位的随机 起伏起必然引起频率随机起伏,这种起伏速度较快,所以又称之为短期频率稳定度。 理想情况下,合成器的输出信号在频域中为根单一的谱线,而实际上任何信号的频谱都不可能绝对纯净,总会受到噪声的调制产生调制边带。由于相位噪声的存在,使波形发生畸变。在频域中其输出信号的谱线就不再是一条单根的谱线,而是以调制边带的形式连续地分布在载波的两边,在主谱两边出现了一些附加的频谱,从而导致频谱的扩展,相位噪声的边带是双边 的,是以0f 为中心对称的,但为了研究方便,一般只取一个边带。其定义为偏离载频1Hz 带宽内单边带相位噪声的功率与载频信号功率之比,它是偏离 载频的复氏频率m f 的函 数 ,记为 () m f ζ,单位为d B c / Hz ,即 ()010lg[/](1) m SSB f P P ζ= 式中SSB P 为偏离载频m f 处,1Hz 带宽内单边带噪声功率;0P 为载波信号功率。

锁相环的基本原理和模型

1.锁相环的基本原理和模型 在并网逆变器系统中,控制器的信号需要与电网电压的信号同步,锁相环通过检测电网电压相位与输出信号相位之差,并形成反馈控制系统来消除误差,达到跟踪电网电压相位和频率的目的。一个基本的锁相环结构如图1-1所示,主要包括鉴相器,环路滤波器,压控振荡器三个部分。 图1-1 基本锁相环结构 鉴相器的主要功能是实现锁相环输出与输入的相位差检测;环路滤波器的主要作用应该是建立输入与输出的动态响应特性,滤波作用是其次;压控振荡器所产生的所需要频率和相位信息。 PLL 的每个部分都是非线性的,但是这样不便于分析设计。因此可以用近似的线性特性来表示PLL 的控制模型。 鉴相器传递函数为:)(Xo Xi Kd Vd -= 压控振荡器可以等效为一个积分环节,因此其传递函数为:S Ko 由于可以采用各种类型不同的滤波器(下文将会讲述),这里仅用)(s F 来表示滤波器的传递函数。 综合以上各个传递函数,我们可以得到,PLL 的开环传递函数,闭环传递函数和误差传递函数分别如下: S s F K K s G d o op )()(=,)()()(s F K K S s F K K s G d o d o cl +=,) ()(s F K K S S s H d o += 上述基本的传递函数就是PLL 设计和分析的基础。 2.鉴相器的实现方法 鉴相器的目的是要尽可能的得到准确的相位误差信息。可以使用线电压的过零检测实现,但是由于在电压畸变的情况下,相位信息可能受到严重影响,因此需要进行额外的信号处理,同时要检测出相位信息,至少需要一个周波的时间,动态响应性能可能受到影响。 一般也可以使用乘法鉴相器。通过将压控振荡器的输出与输入相乘,并经过一定的处理得到相位误差信息。 在实际的并网逆变器应用中还可以在在同步旋转坐标系下进行设计,其基本的目的也是要得的相差的数值。同步旋转坐标系下的控制框图和上图类似,在实际使用中,由于pq 理论在电网电压不平衡或者发生畸变使得性能较差,因而较多的使用dq 变换,将采样得到的三相交流电压信号进行变化后与给定的直流参考电压进行比较。上述两种方法都使用了近似,利用在小角度时正弦函数值约等于其角度,因而会带来误差,这个误差是人为近似导致的误差,与我们要得到的相位误差不是一个概念,最终的我们得到相位误差是要形成压控振荡器的输入信号,在次激励下获得我们所需要的频率和相位信息。 2.1乘法鉴相器

锁相环相位噪声与环路带宽的关系分析

锁相环相位噪声与环路带宽的关系分析 2009-09-09 15:13:17 作者:李仲秋曾全胜来源:现代电子技术 关键字:电荷泵锁相环相位噪声功率谱密度环路带宽 0 引言 电荷泵锁相环是闭环系统,系统各个部分都是一个噪声源,各部分噪声的大小不仅与电路本身有关,而且还与环路带宽等因素有关。因此,设计时必须分析其各频率范围内噪声源影响力的大小,权衡确定环路带宽与各噪声源的相互制约关系。以下利用锁相环的等效噪声模型,重点分析电荷泵锁相环系统的相位噪声特性,得出系统噪声特性的分布特点以及与环路带宽的关系。 1 电荷泵锁相环的基本原理 图1为电荷泵锁相环的示意图,主要由鉴相鉴频器(PFD)、电荷泵、滤波器、压控振荡器(VCO)、分频器等5部分组成,鉴相鉴频器主要用来检测输入信号x(t)与反馈信号xf(t)的频率、相位误差,并产生UP,DOWN信号控制电荷泵的开关。电荷泵由两个对称的电流源和开关组成。电荷泵的开关会对滤波器上的电容充放电,电流经过滤波器滤波后滤掉高频信号,在滤波器上产生能调整压控振荡器频率和相位的电压v(t)。当v(t)上的电压被调整为一个合适的电压值时,xi(t)的频率和相位与x(t)的一致,系统最终处于平衡状态,从而实现对输入信号的跟踪。

2 电荷泵锁相环的噪声模型与相位噪声特性分析 电荷泵锁相环的环路等效噪声模型可以用锁相环各子模块附加噪声源表示。图2给出了带有无源滤波器锁相环噪声源模的型。设fm为距离调制频率的偏移量,该图中主分频器、参考时钟分频器的均方噪声功率谱密度分别被表示为ψd(fm)和ψrcf(fm);鉴相鉴频器的相位噪声被表示为ψpd(fm);晶体振荡器的相位噪声被表示为ψx(fm);相位噪声源的单位是电荷泵的噪声被等价为电流源inp(fm)(单位: ); 滤波器的噪声被等价为电压源Vnf(fm)(单位: 的自由振荡噪声被表示为 环路输出信号的均方噪声功率谱密度被表示为它是闭环情况下所有噪声源影响的总和。输出相位噪声功率谱密度可以表示为: 式中:ψo lp2(fm)为具有低通传输函数的噪声源功率谱密度;ψohp2(fm)为具有高通传输函数的噪声源功率谱密度。 在图2所示的噪声源等效模型中,ψd(fm),ψref(fm),ψpd(fm),ψx(fm)和inp(fm)具有低通传输特性,其传输函数可以表示为: 式中:G(s)和H(s)分别为环路的开环增益函数和闭环增益函数。归一化的电荷泵相位噪声inp(fm)/Kpd和晶体振荡器噪声ψx(fm)/R对ψo lp(fm)的影响也可以用式(2)来表示。当用j2πfm代替s时,ψo2(fm)中具有低通传输函数噪声源功率谱密度的噪声分量ψo lp2 (fm)可以表示为:

锁相环中的相位噪声研究

The Research of Noise in The PLL LU Shiqiang , YANG Guoyu ( School of the Microwave engineering ,UESTC ChengDu 610054 China ) Absract This articles introducs the basic concepts and the phase noise in phase-locked loops (PLLs). It focus on a detailed examination of two critical specifications associated with PLLs : phase noise and reference spurs. What causes them and how can they be minimized? Also it inculdes an example . Key words :PLL ; Phase Noise ; Oscillator 1 . The Basic Theory of the PLL A phase-locked loop is a feedback system combining a voltage controlled oscillator and a phase comparator so connected that the oscillator maintains a constant phase angle relative to a reference signal. Phase-locked loops can be used, for example, to generate stable output frequency signals from a fixed low-frequency signal . The phase locked loop can be analyzed in general as a negative feedback system with a forward gain term and a feedback term. .A simple block diagram of a voltage-based negative-feedback system is shown in Figure 1. Figure 1. Standard negative-feedback control system model In a phase-locked loop, the error signal from the phase comparator is proportional to the relative phase of the input and feedback signals. The average output of the phase detector will be constant when the input and feedback signals are the same frequency. The usual equations for a negative-feedback system apply. Forward Gain = G(s), [s = jw = j2pif] Loop Gain = G(s) H(s) Closed Loop Gain = G(s)/[1+G(s)H(s)] Because of the integration in the loop, at low frequencies the steady state gain, G(s) is very high and VO/VI, Closed-Loop Gain =1/ H and Fo=NF REF. . The components of a PLL that contribute to the loop gain include : 1. The phase detector (PD) and charge pump (CP). 2. The loop filter, with a transfer function of Z(s) 3. The voltage-controlled oscillator (VCO), with a sensitivity of KV /s 4. The feedback divider, 1/N

锁相环的组成和工作原理

锁相环的组成和工作原理 时间:2011-11-23 来源:作者: 关键字:锁相环工作原理 1.锁相环的基本组成 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。 锁相环路是一种反馈控制电路,简称锁相环(PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。 因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。 锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,锁相环组成的原理框图如图8-4-1所示。锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压uC(t),对振荡器输出信号的频率实施控制。 2.锁相环的工作原理 锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图8-4-2所示。 鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为: 式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。则模拟乘法器的输出电压uD为: 用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压uC(t)。即uC(t)为:

式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为: 上式等于零,说明锁相环进入相位锁定的状态,此时输出和输入信号的频率和相位保持恒定不变的状态,uc(t)为恒定值。当上式不等于零时,说明锁相环的相位还未锁定,输入信号和输出信号的频率不等,uc(t)随时间而变。 因压控振荡器的压控特性如图8-4-3所示,该特性说明压控振荡器的振荡频率ωu以ω0为中心,随输入信号电压uc(t)的变化而变化。该特性的表达式 上式说明当uc(t)随时间而变时,压控振荡器的振荡频率ωu也随时间而变,锁相环进入“频率牵引”,自动跟踪捕捉输入信号的频率,使锁相环进入锁定的状态,并保持ω0=ωi的状态不变。 8.4.2锁相环的应用 1.锁相环在调制和解调中的应用 (1)调制和解调的概念 为了实现信息的远距离传输,在发信端通常采用调制的方法对信号进行调制,收信端接收到信号后必须进行解调才能恢复原信号。 所谓的调制就是用携带信息的输入信号ui来控制载波信号uC的参数,使载波信号的某一个参数随输入信号的变化而变化。载波信号的参数有幅度、频率和位相,所以,调制有调幅(AM)、调频(FM)和调相(PM)三种。 调幅波的特点是频率与载波信号的频率相等,幅度随输入信号幅度的变化而变化;调频波的特点是幅度与载波信号的幅度相等,频率随输入信号幅度的变化而变化;调相波的特点是幅度与载波信号的幅度相等,相位随输入信号幅度的变化而变化。调幅波和调频波的示意图如图8-4-4所示。

相位噪声基础及测试原理和方法

相位噪声基础及测试原理和方法 相位噪声指标对于当前的射频微波系统、移动通信系统、雷达系统等电子系统影响非常明显,将直接影响系统指标的优劣。该项指标对于系统的研发、设计均具有指导意义。相位噪声指标的测试手段很多,如何能够精准的测量该指标是射频微波领域的一项重要任务。随着当前接收机相位噪声指标越来越高,相应的测试技术和测试手段也有了很大的进步。同时,与相位噪声测试相关的其他测试需求也越来越多,如何准确的进行这些指标的测试也愈发重要。 1、引言 随着电子技术的发展,器件的噪声系数越来越低,放大器的动态范围也越来越大,增益也大有提高,使得电路系统的灵敏度和选择性以及线性度等主要技术指标都得到较好的解决。同时,随着技术的不断提高,对电路系统又提出了更高的要求,这就要求电路系统必须具有较低的相位噪声,在现代技术中,相位噪声已成为限制电路系统的主要因素。低相位噪声对于提高电路系统性能起到重要作用。 相位噪声好坏对通讯系统有很大影响,尤其现代通讯系统中状态很多,频道又很密集,并且不断的变换,所以对相位噪声的要求也愈来愈高。如果本振信号的相位噪声较差,会增加通信中的误码率,影响载频跟踪精度。相位噪声不好,不仅增加误码率、影响载频跟踪精度,还影响通信接收机信道内、外性能测量,相位噪声对邻近频道选择性有影响。如果要求接收机选择性越高,则相位噪声就必须更好,要求接收机灵敏度越高,相位噪声也必须更好。 总之,对于现代通信的各种接收机,相位噪声指标尤为重要,对于该指标的精准测试要求也越来越高,相应的技术手段要求也越来越高。 2、相位噪声基础 2.1、什么是相位噪声 相位噪声是振荡器在短时间内频率稳定度的度量参数。它来源于振荡器输出信号由噪声引起的相位、频率的变化。频率稳定度分为两个方面:长期稳定度和短期稳定度,其中,短期稳定度在时域内用艾伦方差来表示,在频域内用相位噪声来表示。 2.2、相位噪声的定义

锁相环常见问题解答要点

ADI官网下载了个资料,对于PLL学习和设计来说都非常实用的好资料,转发过来,希望对大家有帮助(原文链接 https://www.360docs.net/doc/3110805975.html,/zh/content/cast_faq_PLL/fca.html#faq_pll_01) ?参考晶振有哪些要求?我该如何选择参考源? ?请详细解释一下控制时序,电平及要求? ?控制多片PLL芯片时,串行控制线是否可以复用? ?请简要介绍一下环路滤波器参数的设置? ?环路滤波器采用有源滤波器还是无源滤波器? ?PLL对于VCO有什么要求?以及如何设计VCO输出功率分配器? ?如何设置电荷泵的极性? ?锁定指示电路如何设计? ?PLL对射频输入信号有什么要求? ?PLL芯片对电源的要求有哪些? ?内部集成了VCO的ADF4360-x,其VCO中心频率如何设定? ?锁相环输出的谐波? ?锁相环系统的相位噪声来源有哪些?减小相位噪声的措施有哪些? ?为何我测出的相位噪声性能低于ADISimPLL仿真预期值? ?锁相环锁定时间取决于哪些因素?如何加速锁定? ?为何我的锁相环在做高低温试验的时候,出现频率失锁? ?非跳频(单频)应用中,最高的鉴相频率有什么限制? ?频繁地开关锁相环芯片的电源会对锁相环有何影响? ?您能控制PLL芯片了么?,R分频和N分频配置好了么?

?您的晶振输出功率有多大?VCO的输出功率有多大? ?您的PFD鉴相极性是正还是负? ?您的VCO输出频率是在哪一点?最低频率?最高频率?还是中间的某一点?VCO 的控制电压有多大? ?您的PLL环路带宽和相位裕度有多大? ?评价PLL频率合成器噪声性能的依据是什么? ?小数分频的锁相环杂散的分布规律是什么? ?到底用小数分频好还是整数分频好? ?ADI提供的锁相环仿真工具ADISimPLL支持哪些芯片,有什么优点? ?分频–获得高精度时钟参考源? ?PLL,VCO闭环调制,短程无线发射芯片? ?PLL,VCO开环调制? ?时钟净化----时钟抖动(jitter)更小? ?时钟恢复(Clock Recovery)? 问题:参考晶振有哪些要求?我该如何选择参考源? 答案:波形:可以使正弦波,也可以为方波。 功率:满足参考输入灵敏度的要求。

相位噪声性能测试

LMK04000 系列产品的相位噪声性能测试 30082862 加权函数H(f)是低通闭环传递函数,其中包含了诸如电 荷泵增益、环路滤波器响应、VCO增益和反馈通路( 数器等参数。该式表示了图1所示的每一级PLL AN-1910 30082801 图1 具有抖动清除能力的双PLL时钟合成器的架构 https://www.360docs.net/doc/3110805975.html, ? 2009 National Semiconductor Corporation 300828

https://www.360docs.net/doc/3110805975.html, 2 A N -1910 2.0 LMK04000系列产品介绍 图2示出了LMK04000精密时钟去抖产品系列的详细的框图。其PLL1的冗余的参考时钟输入(CLKin0,CLKin1),可以支持高达400 MHz 的频率。参考时钟信号可以是单端或者差分式的信号,为了实现操作中稳定性,还可以启用其中的自动开关模式。驱动OSCin 端口的VCXO 的最大容许频率为250 MHz 。OSCin 端口的信号被反馈到PLL2相位比较器上,而且也作为相位和频率基准注入到PLL2中。虽然在图中并未示出,其内部还是可以支持分立形式的、采用外接晶振的VCXO 。PLL2的相位比较器的基准信号输入端还提供了一 个可选用的频率倍增器,这可以使得相位比较的频率得以增加一倍,从而降低了PLL2的带内噪声。PLL2集成了一个内置的VCO ,以及可选的内置环路滤波器部件,这一部分可以提供PLL2环路滤波器的3阶和4阶极点。VCO 的输出带有缓冲,最终由Fout 引脚向外提供信号,该信号也可以经过一个VCO 分频器路由到内部的时钟分发总线上。时钟分发部分则对时钟信号进行缓冲,并将其分配给各个可以独立配置的通道。每个通道具有一个分频器、延迟模块和输出缓冲器。在时钟输出端,各信号格式的组合关系可以根据具体的器件编号来确定。 30082802 图2 LMK04000系列时钟电路的框图 下面的表格示出了LMK04000系列中目前已发布的器件。正如表1所示的那样,其中包含了2个VCO 频带以及 两种可配置的时钟输出格式。本报告中所测量的器件是LMK04031。 表1 LMK04000系列产品的器件编号、输出格式和VCO 频段 NSID 工艺2VPECL/LVPECL 输出 LVDS 输出 LVCMOS 输出 VCO 频率范围LMK04011BISQ BiCMOS 51430~1570 MHz LMK04031BISQ BiCMOS 22 2 1430~1570 MHz LMK04033BISQ BiCMOS 2 2 2 1840~2160 MHz

锁相环输出信号相位噪声噪声及杂散特性分析应用实践

锁相环输出信号相位噪声噪声及杂散特性分析应用实践 【摘要】本文详细地介绍了锁相环的鉴频鉴相器、分频器和输入参考信号的相位噪声对锁相环合成输出信号的近端相位噪声的具体贡献值。并以CDMA 1X基站系统中800MHz的FS 单板的锁相环输出信号相位噪声指标进行理论计算。为广大锁相环设计者提供理论计算方法的参考和实践设计的参考依据。 【关键词】锁相环设计,相位噪声 一、术语和缩略语 表格 1 术语和缩略语 二、问题的提出 锁相环工作原理图,由三部分组成:鉴相器(PFD)、环路滤波器(LPF)和压控晶体振荡器(VCXO),如图0-1所示。 图0-1锁相环原理框图 锁相环输出信号指标主要有相位噪声、谐波抑制、杂散、输出功率、跳频时间。在本文中以CDMA1X基站系统中800MHz的FS单板应用为背景,在CDMA基站中不需要跳频,所以调频时间基本不做要求。输出功率比较好控制,只要调整衰减网络就能保证。锁相环输出信号的相位噪声、谐波抑制和杂散成为影响系统指标的主要因素,成为锁相环技术的关键指标项。在锁相环设计中,相位噪声和杂散成为系统设计主要难点。 三、解决思路 相位噪声分析 相位噪声主要由VCO、鉴频鉴相器、分频器和输入参考信号的相位噪声这四部分引入。环路滤波器对于由鉴频鉴相器、分频器和输入参考信号的相位噪声这三部分引入的相位噪声

具有低通特性,对于VCO产生的相位噪声具有高通特性。一般来说环路带宽内的相位噪声主要决定于由鉴频鉴相器、分频器和输入参考信号,环路带宽以外的相位噪声主要决定于VCO,在环路带宽周围,这四部分的噪声影响相当。所以为了尽量降低输出信号的相位噪声环路滤波器的环路带宽的最佳点是由鉴频鉴相器、分频器和输入参考信号的相位噪声这三部分引入的相位噪声总和与VCO引入的相位噪声相同时的频率。在实际运用中还礼滤波器的设计是非常重要的。对于远端相位噪声如100KHz和1MHz处的一般远远高于环路带宽,其相位噪声主要决定于VCO,要保证其指标主要是选择良好的VCO。而近端相位噪声如100Hz主要由鉴频鉴相器、分频器和输入参考信号的相位噪声决定,但如果还礼带宽取得很小的话如200Hz则VCO的影响也将非常之大。而如果环路带宽远远大于1KHz如为6KHz 以上时1KHz处的相位噪声也将主要由鉴频鉴相器、分频器和输入参考信号的相位噪声决定。下面就分别分析这三部分相位噪声。 由鉴相器引入的相位噪声 由于鉴相器引入的相位噪声为: PD Phase Noise = ( 1 Hz Normalized Phase Noise Floor from Table ) + 10log( Comparison Frequency ) + 20log( N ) 现在FS板的中频环路采用的PLL芯片为NS的LMX2306,其相位噪声基底为-210dBc/Hz。 在CDMA 1X 基站系统800MHz的FS单板中采用的鉴相频率为30KHz,两个中频分别为69.99MHz和114.99MHz,由鉴相器产生的相位噪声为: 69.99MHz: PD Phase Noise= -210+10log(30000)+20log(69990000/30000)= -97.9dBc/Hz 114.99MHz: PD Phase Noise= -210+10log(30000)+20log(114990000/30000)=-93.5dBc/Hz 射频本振范围为754~779MHz。步进为30KHz,鉴相频率为240KHz。对于779MHz 的本振由鉴相器引入的相位噪声为: PD Phase Noise= -210+10log(240000)+20log(779000000/240000)=-85.9dBc/Hz 由分频器引入的相位噪声 由分频器引入的相位噪声的计算公式入下: DIV Phase Noise = (Device Phase Noise Floor )+ 20log( N ) PLL芯片中分频器的相位噪声在器件手册中并没有给出。一般高频分频器的相位噪声基底约为-165dBc/Hz左右。因此就假设分频器的相位噪声基底为-165dBc/Hz,于是得到分频器引起的相位噪声如下: 69.99MHz的中频频率为: DIV Phase Noise= -165+20log(69990000/30000)= -97.6dBc/Hz 114.99MHz的中频频率为: DIV Phase Noise= -165+20log(114990000/30000)= -93.3dBc/Hz 779MHz的射频频率为: DIV Phase Noise= -165+20log(779000000/240000)= -94.7dBc/Hz 由参考信号引入的相位噪声 参考信号引起的相位噪声的计算公式如下 REF Phase Noise = (REF’S Phase Noise )-20log(R)+ 20log( N ) 系统的参考信号都是由GPSTM模块提供的,GPSTM输出的参考信号的相位噪声为-130dBc/Hz@100Hz和-145dBc/Hz@1KHz。最后参考信号通过FDM板到FS板,FDM板输

系统相位噪声的指标

系统相位噪声的指标 举个例子说明800MHz CDMA手机接收(参看IS-98标准) 你可以这样想, 所有的接收机的参数要求, 不管是GAIN, NF, 还是IP3 等等, 都是为了一个目的---实现一定的信噪比SNR从而能够对信号进行解调. 不论是灵敏度, 动态范围还是在有干扰信号条件下, 解调是接收机要达到的目的. 对CDMA手机接收机来说, 解调需要的SNR = -1.5 dB (大约值) IS-98里面有一个单音(Single tone)测试, 是测试CDMA接收机在一个单音强干扰情况下的性能. CDMA接收机灵敏度最低要求-104 dBm(带宽1.25 MHz). 也就是说在最差NF条件下, 热噪声功率 = -104 - SNR = -102.5 dBm/1.25MHz 单音测试条件如下 CDMA信号功率 = -101 dBm/1.25MHz 单音频偏 = 900 KHz 单音功率 = -30 dBm 如图所示, 不管是有中频还是零中频结构, 信号和LO混频后落在有用带宽内, 单音和LO 混频后还是会落在900 KHz处(会被中频或基带滤波器滤除), 单音和LO的相位噪声混频后(称为reciprocal mxing, 有人翻译为倒易混频, 即把单音当作一个本振信号, 把LO的相位噪声当作一个宽带信号进行混频, "倒易"意指单音和LO角色互换)的产物会落在有用带宽内, 这种噪声迭加在热噪声之上, 引起系统SNR下降. 接收机系统相位噪声的指标可以由此得出. 因为单音测试主要由双工器隔离度, LNA IP3和相位噪声决定, 因此计算相位噪声的指标要留裕量给其它指标(这里用 6 dB). 根据上面的计算, 我们可以对相位噪声提一个指标: 在900 KHz频偏处要求-139 dBc/Hz.

相位噪声基础及测试原理和方法

摘要: 相位噪声指标对于当前的射频微波系统、移动通信系统、雷达系统等电子系统影响非常明显,将直接影响系统指标的优劣。该项指标对于系统的研发、设计均具有指导意义。相位噪声指标的测试手段很多,如何能够精准的测量该指标是射频微波领域的一项重要任务。随着当前接收机相位噪声指标越来越高,相应的测试技术和测试手段也有了很大的进步。同时,与相位噪声测试相关的其他测试需求也越来越多,如何准确的进行这些指标的测试也愈发重要。 1、引言 随着电子技术的发展,器件的噪声系数越来越低,放大器的动态范围也越来越大,增益也大有提高,使得电路系统的灵敏度和选择性以及线性度等主要技术指标都得到较好的解决。同时,随着技术的不断提高,对电路系统又提出了更高的要求,这就要求电路系统必须具有较低的相位噪声,在现代技术中,相位噪声已成为限制电路系统的主要因素。低相位噪声对于提高电路系统性能起到重要作用。 相位噪声好坏对通讯系统有很大影响,尤其现代通讯系统中状态很多,频道又很密集,并且不断的变换,所以对相位噪声的要求也愈来愈高。如果本振信号的相位噪声较差,会增加通信中的误码率,影响载频跟踪精度。相位噪声不好,不仅增加误码率、影响载频跟踪精度,还影响通信接收机信道内、外性能测量,相位噪声对邻近频道选择性有影响。如果要求接收机选择性越高,则相位噪声就必须更好,要求接收机灵敏度越高,相位噪声也必须更好。 总之,对于现代通信的各种接收机,相位噪声指标尤为重要,对于该指标的精准测试要求也越来越高,相应的技术手段要求也越来越高。 2、相位噪声基础 2.1、什么是相位噪声 相位噪声是振荡器在短时间内频率稳定度的度量参数。它来源于振荡器输出信号由噪声引起的相位、频率的变化。频率稳定度分为两个方面:长期稳定度和短期稳定度,其中,短期稳定度在时域内用艾伦方差来表示,在频域内用相位噪声来表示。 2.2、相位噪声的定义 以载波的幅度为参考,在偏移一定的频率下的单边带相对噪声功率。这个数值是指在1Hz的带宽下的相对噪声电平,其单位为dBc/Hz。该定义最早是基于频谱仪法测试相位噪声,不区分调幅噪声和调相噪声。 单边带相位噪声L(f)定义为随机相位波动单边带功率谱密度Sφ(f)的一半,其单位为dBc/Hz。其中Sφ(f)为随机相位波动φ(t)的单边带功率谱密度,其物理量纲是rad2/Hz。

锁相环分析

几种常见锁相环分析 并网变换器对锁相环的基本要求: (1)电网电压经常发生跌落、闪变等动态电能质量问题,并且这些异常的出现均是不可预计而且需要及时补偿的。所以要求并网变换器能够对电网电压相位的变化在ms级的时间内能做出快速的响应,即要求并网变换器的锁相方法要有良好的动态性能,保证当电压跌落和骤升时不对锁相性能造成太大影响。 (2)三相电压不平衡时,要求电力电子装置的锁相方法能够捕获正序基波分量的相位,对三相不平衡情况有很强的抑制作用。 (3)锁相环应该能快速检测到电网电压发生相位、频率突变等问题。 (4)要求锁相方法对畸变电压要有很强的抑制作用。 (5)对于一些电力补偿装置如动态电压恢复器,锁相方法不仅要实时检测网侧电压的相位,而且要实时监测网侧电压的幅值变化状况用来判断并决定电力补偿装置的工作模式 1、基于低通滤波器的锁相方法 Karimi-Ghartemani.M和Reza Iravani.A提出了基于低通滤波器的锁相方法,其原理如图所示。三相电网电压从三相静止坐标系转换为两相静止坐标系,利用常见的低通滤波器滤除电网中的谐波干扰,然后对信号进行标么化处理,从而得到电网电压的相位,旋转矩阵R用于补偿滤波器所造成的相位滞后。 原理及R 优点:避免检测过零点带来的问题 缺点:1、在设计低通滤波器时,需要在系统滤波器的鲁棒性和动态响应之间做出折中的选择,较低的截止频率可以抑制系统谐波对相位检测的干扰,但是也相应的降低了系统的响应速度。2、这种方法需求得反三角函数值,计算速度较慢,尤其在系统频率变动和三相电压不平衡时,对畸变电压的抑制作用弱,因此无法正确锁相。 参考文献Method for Synchronization of Power Electronic Converters in Polluted and Variable-Frequency 2、基于空间矢量滤波器(SVF)的锁相方法 空间矢量滤波器是一种用于空间矢量滤波的新型滤波器,它是基于电网电压的αβ分量相互关系相互影响的基础上提出的。这时候电压矢量可以视为以恒定的幅值和频率旋转,有两个输入量 原理

锁相环基本原理

锁相环基本原理 一个典型的锁相环(PLL )系统,是由鉴相器(PD ),压控荡器(VCO )和低通滤波器(LPF )三个基本电路组成,如图1, Ud = Kd (θi –θo) U F = Ud F (s ) θi θo 图1 一.鉴相器(PD ) 构成鉴相器的电路形式很多,这里仅介绍实验中用到的两种鉴相器。 异或门的逻辑真值表示于表1,图2是逻辑符号图。 表1图2 从表1可知,如果输入端A 和B 分别送 2π 入占空比为50%的信号波形,则当两者 存在相位差?θ时,输出端F 的波形的 占空比与?θ有关,见图3。将F 输出波 形通过积分器平滑,则积分器输出波形 的平均值,它同样与?θ有关,这样,我 们就可以利用异或门来进行相位到电压 ?θ 的转换,构成相位检出电路。于是经积 图3 分器积分后的平均值(直流分量)为: U U=Vdd*?θ/π (1) Vcc 不同的?θ,有不同的直流分量Vd 。 ?θ与V 的关系可用图4来描述。 从图中可知,两者呈简单线形关 1/2Vcc 系: Ud = Kd *?θ (2) 1/2ππ?θ Kd 为鉴相灵敏度图4 F O o U K dt d =θV PD LPF VCO Ui Uo V A B F __F = A B + A B F B A

2. 边沿触发鉴相器 前已述及,异或门相位比较器在使用时要求两个作比较的信号必须是占空比为50%的波形,这就给应用带来了一些不便。而边沿触发鉴相器是通过比较两输入信号的上跳边沿(或下跳边沿)来对信号进行鉴相,对输入信号的占空比不作要求。 二. 压控振荡器(VCO ) 压控振荡器是振荡频率ω0受控制电压U F (t )控制的振荡器,即是一种电压——频率变换器。VCO 的特性可以用瞬时频率ω0(t )与控制电压U F (t )之间的关系曲线来表示。未加控制电压时(但不能认为就是控制直流电压为0,因控制端电压应是直流电压和控制电压的叠加),VCO 的振荡频率,称为自由振荡频率ωom ,或中心频率,在VCO 线性控制范围内,其瞬时角频率可表示为: ωo (t )= ωom + K 0U F (t ) 式中,K 0——VCO 控制特性曲线的斜率,常称为VCO 的控制灵敏度,或称压控灵敏度。 三. 环路滤波器 这里仅讨论无源比例积分滤波器如图5。 其传递函数为: 1 )(1 )()()(212+++== τττs s s U s U s K i O F 式中:τ1 =R1C τ2 = R2 C 图5 四. 锁相环的相位模型及传输函数 图6 图6为锁相环的相位模型。要注意一点,锁相环是一个相位反馈系统,在环路中流通的是相位,而不是电压。因此研究锁相环的相位模型就可得环路的完整性能。 由图6可知: R1 0640 V Kd KF(s)Ko/s i o e A -+

一种相位噪声标准介绍

一种相位噪声标准介绍 张爱敏李黎明 中国计量科学研究院100013 摘要:本文介绍一种5MHz,10MHz及100MHz相位噪声标准及相关测量方法,该标准是由FredLWalls设计发明的专利产品,可用来评价相位噪声测量承缝奉底及系统相位噪声测量的准确度,也可用来测量相位噪声测量系统中鉴相器的灵敏度。该标准的使用可必备实验室相位噪声测量系统之间的比对及测量过程变得简便,且有很高的准确度。 关键词:相位噪声,相位噪声标准 Abstract:njspaperdescribesakindofpha5cnoisestamlasdatcarrierfrequencies5MHz,10MHzand100MHz,ThisstandardisapatentdevicedesignedbyFredLwalls。Thisstandardcanbeusedtoevaluatetheaccuracyandnoisefloorofphasenoisemeasurementsystem。itcunalsobeusedtocalibratetheconversionsensitivityofthedetectorforphasenoisemeasurement。Theapplicationofthisstandardmakesthecomparisonsofthephasenoisemeasllromantsystemindifferentlaboratoriesandmemcasu他mentpmcedllres prcUyeasywithveryhighaccuracy. KeyWords:PhaseNoise,PhaseNoiscStandard 1.引言: 1.1定义 相位噪声是信号源输出频率在频域的随机起伏程度,国际上推荐的表征量为单边带相位噪声£(f)。其定义为: 当△o((Irad时s?为相位起伏功率谱密度£(f)=圭蹦厂)(dBc/Hz)旷端△(rad2/Hz) f.相对于载频的傅立叶频偏, △m。。(f):相位变化的有效值,BW:等效噪声带宽或测量带宽。(1)(2) 1.2传统的测量方法 频率源相位噪声的测量一般采用正交鉴丰目法(双源鉴相法),其基本原理是将被测源的随机相位起伏转化为与之成正比的随机电压起伏,由频谱仪进行谱分析。具体测量方法见图1。 274

锁相环的相位噪声

锁相环倍频器的一个最主要的难点就是降低相位噪声。 早射干扰具有随机性,具体分析计算极其困难。虽然我们可借助像AGINENT 的ADS 等仿真软件和MATHCAD 等大型计算软件进行分析,但我们必须借助PLL 的线性相位模型开始研究(图2)其中 F (s )为环路滤波器的传递函数;K Φ和vco K 分别为鉴相器的鉴相灵敏 度和压控振荡器的压控灵敏度 1/R K () F s VCO K 1/N OUT F 上图的PLL 的相位噪声模型可得其前向增益和反向增益分别为 () ()vco s S K K F G s Φ= (3-1) 1 H N = (3-2) 其中R 为分频器分频比。 () s F 为环路滤波器传递函数。利用现代控制理论,可得出锁相 环环路各部件的噪声源对环路噪声的贡献的传递函数。 表图为各类噪声源及其对应的传递函数 噪声部件 传递函数 晶体振荡器 ()()11S S G R G H + R 分频器 ()()1S S G G H + N 分频器 ()()1S S G G H + 鉴相器 ()()1 1S S G K G H φ+ VCO ()()1S S G G H + 从上表我们可以看出,鉴相器、N 分频器、R 分频器和参考晶体的噪声传递函数都有一 个共同的因子 () () 1s s G G +。以上的噪声源统称为带内噪声。

晶体振荡器的相位噪声晶体振荡器的相位噪声()i S Φ 对输出相位噪声 0()s Φ 的影响 为 ()0() ()() 1s i s G s NM S G Φ= Φ+ (4) 由式( 4 ) 中可以看出,晶振中心频率ω的相位噪声全部由环路输出,大于环路谐振频率 n ω的相位噪声将被衰减。由于分频次数N 与倍频次数M 受输出频率和跳频点数限制,故 主要考虑 ()i S Φ 。 晶体振荡器等效电路中的放大器固有噪声功率FKTB 经放大器后通过带宽为i B 的晶体 滤波器与信号功率s P 一起加到输入端,0m 形成相位噪声,为放大器输出端的基底噪声,可写成 010g g s FKTB L m L P = (5) 压控振荡器( VCO) 的相位噪声 压控振荡器VCO) 的相位噪声对 0()s Φ 的影响为 ()0() ()() 1s vco s G s s G Φ= Φ+ (6) ()vco s Φ 0()s Φ 对的影响具有高通特性,低于的分量环路有很强的抑制作用,高于n ω的相位噪声分量将全部输出。因此频率合成器远端的相位 噪声主要决定 ()vco s Φ ,()vco s Φ 降低是降低频率合成器远端相位噪声的主要方法。 环路滤波器的相位噪声 影响相位噪声的另一个重要因素是环路滤波器。环路滤波器对最终性能有很大影响,这是因为它决定拐点频率( 在拐点频率处来自电路不同部分的噪声开始影响输出,如图所示)。在环路带宽内,鉴相器强迫VCO 跟踪参考频率,将参考频率源的相位噪声带到VCO 上。由于鉴相器噪声基底通常比参考频率源的相位噪声高,因此这一过程受到鉴相器噪声基底的支配。由于补偿频率高于环路带宽,环路就不能很好的跟踪参考频率,总的相位噪声等于 V C O 的相位噪声,因此要将环路带宽设置在鉴相器噪声基底与VCO 自由振荡时相位噪声的交叉点上。过宽和过窄的环路带宽虽然对VCO 的相位噪声有一定的改善,但不能很好地提高PLL 的相位噪声性能。

简述锁相环

南京机电职业技术学院 毕业设计(论文) 题目 40MHz简易锁相环的设计 系部电子工程系专业电子信息技术工程 姓名王鑫学号 G1210145 指导教师吕彬森 2015 年 04 月09日

摘要 在无线收发信机电路中,除了发射机和接收机外,还有一个非常重要的部分就是本地振荡电路。为了保证本地振荡模块输出信号的频率稳定性和较低的相位噪声,通常本振采用锁相环技术来实现,特别在无线通信领域。 本文阐述了锁相环的基本结构和工作原理,从锁相环稳定性的角度出发,给出了无线通信电路中使用40MHz 锁相环的电路设计,并且将方案中锁相环电路进行了仿真,最终满足40MHz 锁相环的设计要求。 关键词:锁相环;鉴相器;压控振荡器

Abstract(外语专业的需要) 【英文摘要正文输入】 In the wireless transceiver circuit, in addition to the transmitter and the receiver, there is a very important part of the local oscillator circuit is. In order to ensure the stability of the local oscillator module, output signal frequency and low phase noise, the vibration by using phase locked loop technique, especially in the field of wireless communications. This paper introduces the basic structure and working principle of the phase-locked loop PLL, starting from the stability of the 40MHz PLL circuit design is given of the use of wireless communication circuit, and the scheme of PLL circuit simulation, and ultimately meet the design requirements of 40MHz phase locked loop. Keywords: Attenuation network; Attenuation quantity; Amplifier; broadband