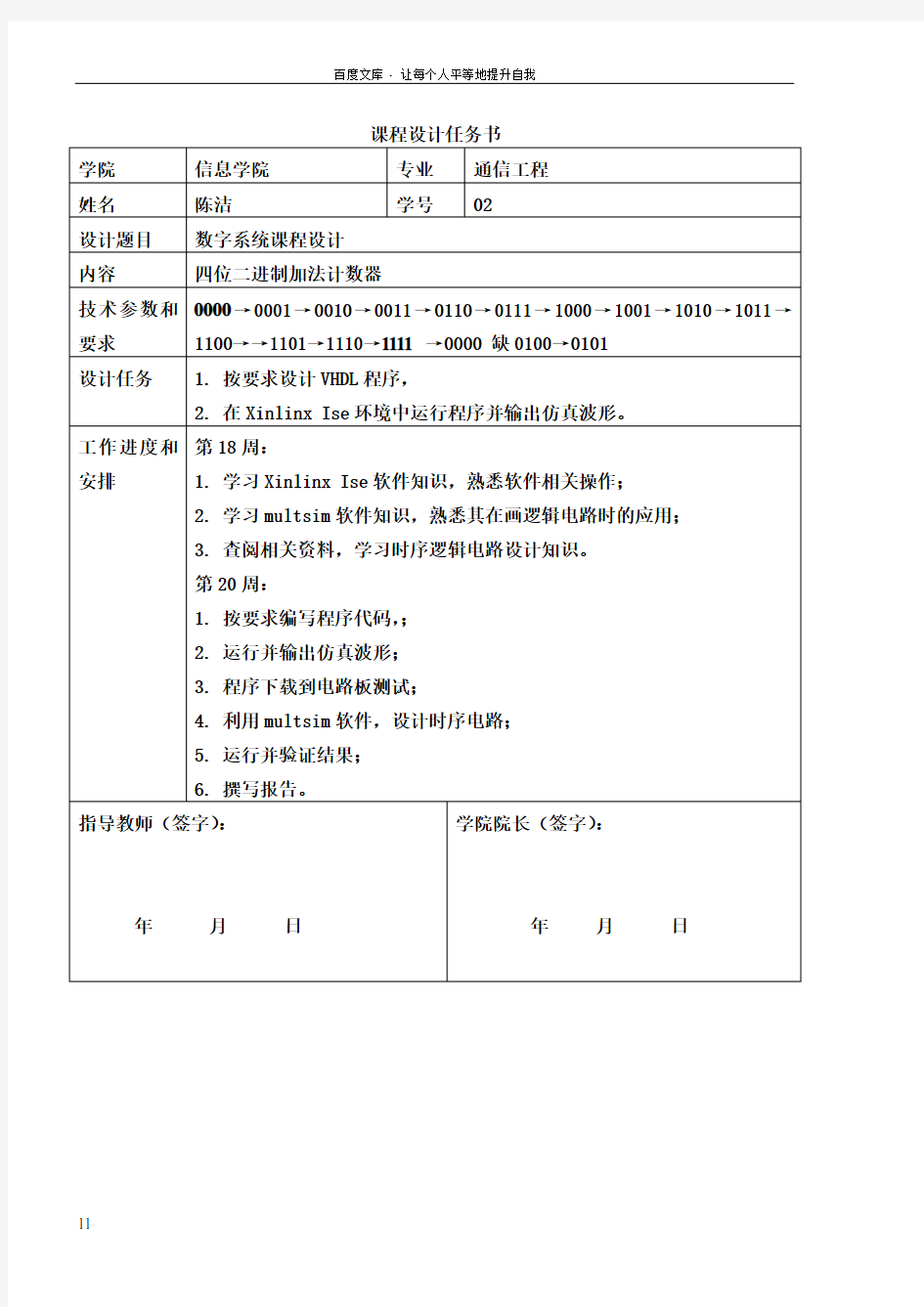

四位二进制加法计数器

学院信息学院专业通信工程姓名陈洁学号02

设计题目数字系统课程设计

内容四位二进制加法计数器

技术参数和要求0000→0001→0010→0011→0110→0111→1000→1001→1010→1011→1100→→1101→1110→1111→0000 缺0100→0101

设计任务 1.按要求设计VHDL程序,

2.在Xinlinx Ise环境中运行程序并输出仿真波形。

工作进度和安排第18周:

1.学习Xinlinx Ise软件知识,熟悉软件相关操作;

2.学习multsim软件知识,熟悉其在画逻辑电路时的应用;

3.查阅相关资料,学习时序逻辑电路设计知识。

第20周:

1.按要求编写程序代码,;

2.运行并输出仿真波形;

3.程序下载到电路板测试;

4.利用multsim软件,设计时序电路;

5.运行并验证结果;

6.撰写报告。

指导教师(签字):

年月日学院院长(签字):

年月日

目录

一.数字系统简介 (3)

二.设计目的和要求 (3)

三.设计内容 (3)

四.VHDL程序设计 (3)

五.波形仿真 (11)

六. 逻辑电路设计 (12)

六.设计体会 (13)

七.参考文献 (13)

一.数字系统简介

在数字逻辑设计领域,迫切需要一种共同的工业标准来统一对数字逻辑电路及系统的描述,这样就能把系统的设计分解为逻辑设计(前端),电路实现(后端)和验证桑相互独立而又相关的部分。由于逻辑设计的相对独立性就可以把专家们设计的各种数字逻辑电路和组件建成宏单元或软件核,即ip库共设计者引用,设计者可以利用它们的模型设计电路并验证其他电路。VHDL这种工业标准的产生顺应了历史潮流。

二.设计目的和要求

1、通过《数字系统课程设计》的课程实验使电子类专业的学生能深入了解集成中规

模芯片的使用方法。

2、培养学生的实际动手能力,并使之初步具有分析,解决工程实际问题的能力。三.设计内容

四位二进制加计数,时序图如下:

0000→0001→0010→0011→0110→0111→1000→1001→1010→1011→1100→→1101→1110→1111 →0000 缺0100→0101 。由JK触发器组成4位异步二进制加法计数器。

四.VHDL程序设计

四位二进制加计数,缺0100,0101(sw向上是0(on);灯亮为0)

LIBRARY IEEE;

USE

entity count10 is

PORT (cp,r:IN STD_LOGIC;

q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0) );

end count10;

ARCHITECTURE Behavioral OF count10 IS

SIGNAL count:STD_LOGIC_VECTOR(3 DOWNTO 0) ;

BEGIN

PROCESS (cp,r)

BEGIN

if r='0' then count<="0000";

elsiF cp'EVENT AND cp='1' THEN

if count="0011" THEN

count <="0110";

ELSE count <= count +1;

END IF;

end if;

END PROCESS;

q<= count;

end Behavioral;

(一)建立工程。File——〉New Project;Project Name:工程名(例:count10); Project Location:工程保存的位置(例:F:0603060x\count10);next——>……——>next直至finish。

(二)调试程序。右击xc95108-15pc84,选New Source,再选VHDL Module后,填加文件名(例:File name:v1)——〉next( Port Name中随便填A)——〉finish

写入程序,保存程序

双击Implement Design(或右键Run),运行程序,调试成功显示如下

(三)波形仿真。回到界面,右键点击v1 - Behavioral(),选New Source——〉Test Bench WaveForm——〉File Name:t1( 测试波形文件名t1),next(连接v1) ——next〉——〉finish