镁光16GB DDR3 1600MHZ服务器内存条jsf36c2gx72pz

DDR3 SDRAM RDIMM

MT36JSF2G72PZ – 16GB Features

?DDR3 functionality and operations supported as defined in the component data sheet

?240-pin, registered dual in-line memory module (RDIMM)

?Fast data transfer rates: PC3-14900, PC3-12800,PC3-10600, PC3-8500, or PC3-6400?16GB (2 Gig x 72)?V DD = 1.5V ±0.075V ?V DDSPD = 3.0–3.6V

?Supports ECC error detection and correction

?Nominal and dynamic on-die termination (ODT) for data and strobe signals ?Dual-rank

?8 internal device banks

?Fixed burst chop (BC) of 4 and burst length (BL) of 8via the mode register set (MRS)

?On-board I 2C temperature sensor with integrated serial presence-detect (SPD) EEPROM ?Gold edge contacts ?Halogen-free ?Fly-by topology

?Terminated control, command, and address bus Figure 1: 240-Pin RDIMM (R/C J1)

Figure 2: 240-Pin RDIMM (R/C E2)

Options

Marking

?Operating temperature

–Commercial (0°C ≤ T A ≤ 70°C)None ?Package

–240-pin DIMM (halogen-free)Z ?Frequency/CAS latency

– 1.07ns @ CL = 13 (DDR3-1866)-1G9– 1.25ns @ CL = 11 (DDR3-1600)-1G6– 1.5ns @ CL = 9 (DDR3-1333)-1G4– 1.87ns @ CL = 7 (DDR3-1066)

-1G1

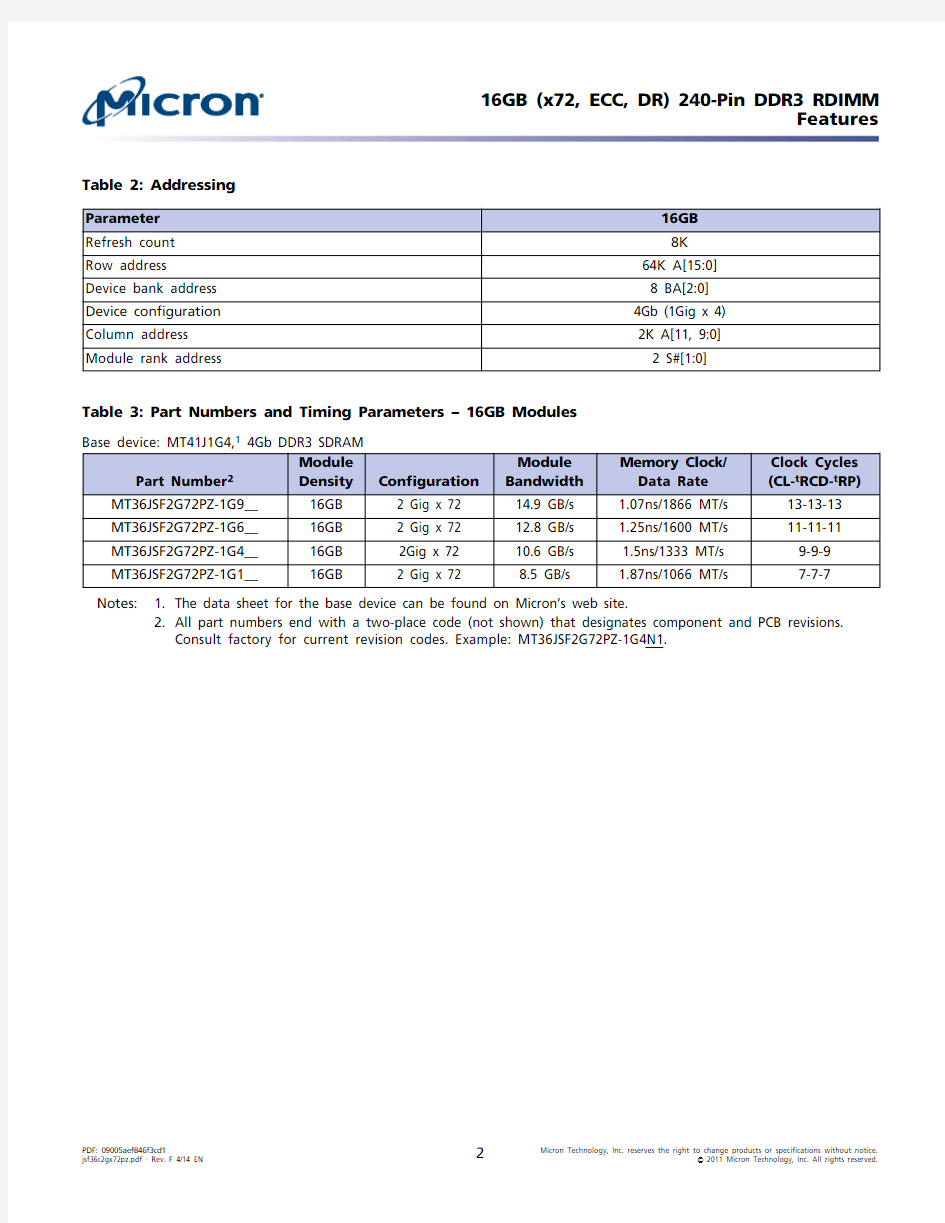

Table 1: Key Timing Parameters

Table 2: Addressing

Table 3: Part Numbers and Timing Parameters – 16GB Modules

1

Notes: 1.The data sheet for the base device can be found on Micron’s web site.

2.All part numbers end with a two-place code (not shown) that designates component and PCB revisions.

Consult factory for current revision codes. Example: MT36JSF2G72PZ-1G4N1.

Pin Assignments Table 4: Pin Assignments

Pin Descriptions

The pin description table below is a comprehensive list of all possible pins for all DDR3

modules. All pins listed may not be supported on this module. See Pin Assignments for

information specific to this module.

Table 5: Pin Descriptions

Table 5: Pin Descriptions (Continued)

DQ Maps

Table 6: Component-to-Module DQ Map (R/C J1), Front

Table 6: Component-to-Module DQ Map (R/C J1), Front (Continued)

Table 7: Component-to-Module DQ Map (R/C J1), Back

Table 7: Component-to-Module DQ Map (R/C J1), Back (Continued)

Table 8: Component-to-Module DQ Map (R/C E2), Front

Table 9: Component-to-Module DQ Map (R/C E2), Back

Functional Block Diagrams

Figure 3: Functional Block Diagram (R/C J1)

V REFCA

V SS

V DD V DDSPD

V TT V REFDQ

Clock, control, command, and address line terminations:

Rank 0: U1–U5, U8–U20 Rank 1: U21–U38

RODT[1:0], TT

DD

Note:

1.The ZQ ball on each DDR3 component is connected to an external 240Ω ±1% resistor

that is tied to ground. It is used for the calibration of the component’s ODT and output driver.

Figure 4: Functional Block Diagram (R/C E2)

V V V V V TT V Clock, control, command, and address line terminations:

Rank 0: U1–U5, U12–U16, U21–U24, U31–U34 Rank 1: U8–U11, U17–U20, U26–U30, U35–U39

RODT[1:0], R DD

Note:

1.The ZQ ball on each DDR3 component is connected to an external 240Ω ±1% resistor

that is tied to ground. It is used for the calibration of the component’s ODT and output driver.

General Description

DDR3 SDRAM modules are high-speed, CMOS dynamic random access memory mod-ules that use internally configured 8-bank DDR3 SDRAM devices. DDR3 SDRAM mod-ules use DDR architecture to achieve high-speed operation. DDR3 architecture is essen-tially an 8n -prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write access for the DDR3 SDRAM mod-ule effectively consists of a single 8n -bit-wide, one-clock-cycle data transfer at the inter-nal DRAM core and eight corresponding n -bit-wide, one-half-clock-cycle data transfers at the I/O pins.

DDR3 modules use two sets of differential signals: DQS, DQS# to capture data and CK and CK# to capture commands, addresses, and control signals. Differential clocks and data strobes ensure exceptional noise immunity for these signals and provide precise crossing points to capture input signals.

Fly-By Topology

DDR3 modules use faster clock speeds than earlier DDR technologies, making signal quality more important than ever. For improved signal quality, the clock, control, com-mand, and address buses have been routed in a fly-by topology, where each clock, con-trol, command, and address pin on each DRAM is connected to a single trace and ter-minated (rather than a tree structure, where the termination is off the module near the connector). Inherent to fly-by topology, the timing skew between the clock and DQS sig-nals can be easily accounted for by using the write-leveling feature of DDR3.

Registering Clock Driver Operation

Registered DDR3 SDRAM modules use a registering clock driver device consisting of a register and a phase-lock loop (PLL). The device complies with the JEDEC standard "Definition of the SSTE32882 Registering Clock Driver with Parity and Quad Chip Se-lects for DDR3 RDIMM Applications."

The register section of the registering clock driver latches command and address input signals on the rising clock edge. The PLL section of the registering clock driver receives and redrives the differential clock signals (CK, CK#) to the DDR3 SDRAM devices. The register(s) and PLL reduce clock, control, command, and address signals loading by iso-lating DRAM from the system controller.

Parity Operations

The registering clock driver includes an even parity function for checking parity. The memory controller accepts a parity bit at the Par_In input and compares it with the data received on A[15:0], BA[2:0], RAS#, CAS#, and WE#. Valid parity is defined as an even number of ones (1s) across the address and command inputs (A[15:0], BA[2:0], RAS#,CAS#, and WE#) combined with Par_In. Parity errors are flagged on Err_Out#.

Address and command parity is checked during all DRAM operations and during con-trol word WRITE operations to the registering clock driver. For SDRAM operations, the address is still propagated to the SDRAM even when there is a parity error. When writ-ing to the internal control words of the registering clock driver, the write will be ignored if parity is not valid. For this reason, systems must connect the Par_In pins on the DIMM and provide correct parity when writing to the registering clock driver control word configuration registers.

16GB (x72, ECC, DR) 240-Pin DDR3 RDIMM

General Description

Temperature Sensor with Serial Presence-Detect EEPROM

Thermal Sensor Operations

The temperature from the integrated thermal sensor is monitored and converts into a digital word via the I 2C bus. System designers can use the user-programmable registers to create a custom temperature-sensing solution based on system requirements. Pro-gramming and configuration details comply with JEDEC standard No. 21-C page 4.7-1,"Definition of the TSE2002av, Serial Presence Detect with Temperature Sensor."

Serial Presence-Detect EEPROM Operation

DDR3 SDRAM modules incorporate serial presence-detect. The SPD data is stored in a 256-byte EEPROM. The first 128 bytes are programmed by Micron to comply with JE-DEC standard JC-45, "Appendix X: Serial Presence Detect (SPD) for DDR3 SDRAM Mod-ules." These bytes identify module-specific timing parameters, configuration informa-tion, and physical attributes. The remaining 128 bytes of storage are available for use by the customer. System READ/WRITE operations between the master (system logic) and the slave EEPROM device occur via a standard I 2C bus using the DIMM’s SCL (clock)SDA (data), and SA (address) pins. Write protect (WP) is connected to V SS , permanently disabling hardware write protection. For further information refer to Micron technical note TN-04-42, "Memory Module Serial Presence-Detect."

16GB (x72, ECC, DR) 240-Pin DDR3 RDIMM

Temperature Sensor with Serial Presence-Detect EEPROM

Electrical Specifications

Stresses greater than those listed may cause permanent damage to the module. This is a stress rating only, and functional operation of the module at these or any other condi-tions outside those indicated in each device's data sheet is not implied. Exposure to ab-solute maximum rating conditions for extended periods may adversely affect reliability.

Table 10: Absolute Maximum Ratings

Table 11: Operating Conditions

Notes:

1.V TT termination voltage in excess of the stated limit will adversely affect the command

and address signals’ voltage margin and will reduce timing margins.2.T A and T C are simultaneous requirements.

3.For further information, refer to technical note TN-00-08: “Thermal Applications,”

available on Micron’s web site.

4.The refresh rate is required to double when 85°C < T C ≤ 95°C.

5.Inputs are terminated to V DD /2. Input current is dependent on terminating resistance se-lected in register.

16GB (x72, ECC, DR) 240-Pin DDR3 RDIMM

Electrical Specifications

DRAM Operating Conditions

Recommended AC operating conditions are given in the DDR3 component data sheets.

Component specifications are available on Micron’s web site. Module speed grades cor-

relate with component speed grades, as shown below.

Table 12: Module and Component Speed Grades

Design Considerations

Simulations

Micron memory modules are designed to optimize signal integrity through carefully de-

signed terminations, controlled board impedances, routing topologies, trace length

matching, and decoupling. However, good signal integrity starts at the system level.

Micron encourages designers to simulate the signal characteristics of the system's

memory bus to ensure adequate signal integrity of the entire memory system.

Power

Operating voltages are specified at the DRAM, not at the edge connector of the module.

Designers must account for any system voltage drops at anticipated power levels to en-

sure the required supply voltage is maintained.

I DD Specifications

Table 13: DDR3 I DD Specifications and Conditions – 16GB (Die Revision D)

Values are for the MT41J1G4 DDR3 SDRAM only and are computed from values specified in the 4Gb

Notes: 1.One module rank in the active I DD, the other rank in I DD2P0 (slow exit).

2.All ranks in this I DD condition.

Table 14: DDR3 I DD Specifications and Conditions – 16GB (Die Revisions E and J) Values are for the MT41J1G4 DDR3 SDRAM only and are computed from values specified in the 4Gb

Notes: 1.One module rank in the active I DD, the other rank in I DD2P0 (slow exit).

2.All ranks in this I DD condition.

Table 15: DDR3 I DD Specifications and Conditions – 16GB (Die Revision N)

Values are for the MT41K1G4 DDR3 SDRAM only and are computed from values specified in the 4Gb

Notes: 1.One module rank in the active I DD, the other rank in I DD2P0 (slow exit).

2.All ranks in this I DD condition.

Registering Clock Driver Specifications

Table 16: Registering Clock Driver Electrical Characteristics

Note: 1.Timing and switching specifications for the register listed are critical for proper opera-

tion of the DDR3 SDRAM RDIMMs. These are meant to be a subset of the parameters for

the specific device used on the module.

全面教你认识内存参数

全面教你认识内存参数 内存热点 Jany 2010-4-28

内存这样小小的一个硬件,却是PC系统中最必不可少的重要部件之一。而对于入门用户来说,可能从内存的类型、工作频率、接口类型这些简单的参数的印象都可能很模糊的,而对更深入的各项内存时序小参数就更摸不着头脑了。而对于进阶玩家来说,内存的一些具体的细小参数设置则足以影响到整套系统的超频效果和最终性能表现。如果不想当菜鸟的话,虽然不一定要把各种参数规格一一背熟,但起码有一个基本的认识,等真正需要用到的时候,查起来也不会毫无概念。 内存种类 目前,桌面平台所采用的内存主要为DDR 1、DDR 2和DDR 3三种,其中DDR1内存已经基本上被淘汰,而DDR2和DDR3是目前的主流。 DDR1内存 第一代DDR内存 DDR SDRAM 是 Double Data Rate SDRAM的缩写,是双倍速率同步动态随机存储器的意思。DDR内存是在SDRAM内存基础上发展而来的,仍然沿用SDRAM生产体系,因此对于内存厂商而言,只需对制造普通SDRAM 的设备稍加改进,即可实现DDR内存的生产,可有效的降低成本。 DDR2内存 第二代DDR内存

DDR2 是 DDR SDRAM 内存的第二代产品。它在 DDR 内存技术的基础上加以改进,从而其传输速度更快(可达800MHZ ),耗电量更低,散热性能更优良。 DDR3内存 第三代DDR内存 DDR3相比起DDR2有更低的工作电压,从DDR2的1.8V降落到1.5V,性能更好更为省电;DDR2的4bit 预读升级为8bit预读。DDR3目前最高能够1600Mhz的速度,由于目前最为快速的DDR2内存速度已经提升到800Mhz/1066Mhz的速度,因而首批DDR3内存模组将会从1333Mhz的起跳。 三种类型DDR内存之间,从内存控制器到内存插槽都互不兼容。即使是一些在同时支持两种类型内存的Combo主板上,两种规格的内存也不能同时工作,只能使用其中一种内存。 内存SPD芯片 内存SPD芯片

教你如何调整DDR内存参数

教你如何调整DDR内存参数 日期:2006-07-08 上传者:赵磊来源:https://www.360docs.net/doc/441462966.html, 同样的CPU,同样的频率设置,为什么别人的运行效率就比我的高呢?为什么高手能以较低CPU频率跑出更好的测试成绩呢?问题的关键就是内存参数的调校。在一般的超频中,只会调整一些基本参数,比如某超频报告中会说到内存运行状态为“520MHz、3-4-4-8 1T”,那么除频率外后5个数字就是基本参数。还有一系列参数被称之为“小参”,能起到辅助调节作用,当调节基参后仍无法提高频率,或者性能提升不明显后,调整“小参”往往会得到令人意外的惊喜。以下我们根据基本参数与小参分别介绍调校方法。 基本参数介绍 目前的内存还是使用类电容原理来存储数据,需要有充放电的过程,这个过程所带来的延迟是不可避免的。在BIOS中,所有关于内存调节的参数其实都是在调整这个充放电的时序。受颗粒品质影响,每种内存的参数几乎都不完全一样。面对这些参数,我们必须先了解其原理才能在以后的调节中做到信手拈来。以下我们讲解一些重点参数的含义。 CL CL全称CAS Latency,是数据从存储设备中输出内存颗粒的接口之间所使用的时间。一般而言是越短越好,但受于制造技术和内存控制器所限,目前的最佳值是2。

从图中,我们能够直观的看到CL值变化,对数据处理的影响。虽说在单周期内的等待的时间并不长;但在实际使用时,内存每秒要400M次以上的周期循环,此时的性能影响就相当明显了。 RAS与CAS 内存内部的存储单元是按照行(RAS)和列(CAS)排成矩阵模式,一个地址访问指令会被解码成行和列两个信号,先是行地址信号,然后是列地址信号,只有行和列地址都准备好之后才可以确定要访问的内存单元。因此内存读写第一个延迟是RAS到CAS的延迟,从行地址访问允许到读、写数据还有一个准备时间,被称为RAS转换准备时间。这也就是为什么RAS to CAS参数对性能影响要大于RAS Precharge的原因。 Tras

电脑内存时序

举例9-9-9-27,一般1600的条子spd出厂就这么设置的 前面2个9对性能很重要,第2个9又比第1个9重要,比如说 我要超1866或者2133,设置成9-10-X-X基本没有问题,但是 设置成10-9-X-X就开不了机了,很多条子都这样子的,比如说 现在很火的3星金条。 第3位9基本上是打酱油的了,设置成9,10,11都对性能木有太大影响。 第4位数字基本就无视好了,设置21-36对测试都没变化,原来稳定的 还是稳定,原来开不了机的还是开不了。 以前的ddr2时代对内存的小参数很有影响,现在ddr3了,频率才是王道哦。 2133的-11-11-11-30都要比1866的-9-9-9-27测试跑分的多。当然平时用是感觉不出来的。 最后我再鄙视下金士顿的XX神条马甲套装,当年不懂事大价钱买的,就是YY用的, 1.65v上个1866都吃力,还要参数放的烂。 对性能影响最大的是CL 第一个9对性能影响最大。l第二个9对超频稳定性影响最大 最普通的ddr3 1333内存都可以1.5V运行在7-8-6-1666 CR1,77 Z博士: 一般来说,体现内存延迟的就是我们通常说的时序,如DDR2-800内存的标准时序:5-5-5-18,但DDR3-800内存的标准时序则达到了6-6-6-

15、DDR3-1066为7-7-7- 20、而DDR3-1333更是达到了9-9-9-25! 土老冒: 俺想知道博士所说的5-5-5- 18、6-6-6-15等数字每一个都代表什么。 Z博士: 这4个数字的含义依次为: CAS Latency(简称CL值)内存CAS延迟时间,这也是内存最重要的参数之一,一般来说内存厂商都会将CL值印在产品标签上。 第二个数字是RAS-to-CAS Delay(tRCD),代表内存行地址传输到列地址的延迟时间。 第三个则是Row-precharge Delay(tRP),代表内存行地址选通脉冲预充电时间。 第四个数字则是Row-active Delay(tRAS),代表内存行地址选通延迟。 除了这四个以外,在AMD K8处理器平台和部分非Intel设计的对应Intel芯片组上,如NVIDIA nForce 680i SLI芯片组上,还支持内存的CMD 1T/2T Timing 调节,CMD调节对内存的性能影响也很大,其重要性可以和CL相比。 其实这些参数,你记得太清楚也没有太大用处,你就只需要了解,这几个参数越低,从你点菜到上菜的时间就越快。 土老冒: 好吧,俺自己也听得一头雾水,只需要记得它越低越好就行了。那么俺想问,为什么DDR3内存延迟提高了那么多,Intel和众多的内存模组厂商还要大力推广呢?

深入理解C语言变量和内存

深入理解C语言变量和内存 1、基本数据类型变量名和内存的关系: int i; scanf_s("%d", &i); int i;,在这一句就为i分配了内存(但尚未对这块内存进行初始化),所以可以通过&i直接使用这块内存。赋值就更不用说啦,i = 3;。 变量名i,是为方便编程人员使用,是这块内存的别名,指代到块内存,对编程人员i代表这块内存中存储的值(实际上是i指到这个内存,然后取值)。通常我们都是通过变量名来使用已知的内存的。 i代表取(这块内存中存储的)值,而&i代表取(这块内存的)址。程序本身是不为i这个变量名分配空间的。在最终的机器代码中,是不会出现变量名的,这一点在分析反汇编语言时可以看出(命令:dumpbin /disasm xx.obj >xx_disasm.asm 可以查看反汇编语言)。那么编译器是如何处理变量名的呢,变量名会存储在符号表中,并将符号表中的索引对应到实际物理空间(地址)上去,当调用这个变量时,查找符号表就可以找到对应的地址并取值了。 2、不同类型变量的变量名和内存间的关系: 上面分析的是基本数据类型(如int、char等)的变量名。C中除了变量名之外,还有函数名、常量名、指针名、数组名、结构名等。和变量名不同,这些标识符都是直接对应着地址的。基本数据类型的变量,和地址的对应关系需要取址符&才能得到地址,而其余的这些,名字本身就对应着地址。 例如char *pc = “se”;,就是将字符串常量”se”的首地址(位于常量存储区)赋值给了字符指针pc。这也就解释了为什么不需要为pc分配地址就可以为其赋值,而不会遇到类似下面代码所带来的野指针问题: int *pi; *pi = 1; int *pi句,是为pi分配空间,而不是开辟pi所指向的空间。 2.1 C语言中的常量: C对常量是怎么处理的呢?比如上面的i = 3;中的常量3,存储常量3的地址并不是随机分配的,是在程序中的数据段中(.data?这个我也还不是很确定,希望知道的前辈们给个指导),也就是程序本身并不为3分配内存,而是直接写入指令。3是数字常量,对于字符常量和字符串常量,又分别是怎么处理的呢? 字符常量和数字常量是一样的处理方式,都是类似汇编中的立即数,直接写入指令;

SDRAM内存详解(经典)

SDRAM内存详解(经典) 我们从内存颗粒、内存槽位接口、主板和内存之间的信号、接口几个方面来详细阐述SDRAM内存条和主板内存系统的设计思路... 虽然目前SDRAM内存条价格已经接底线,内存开始向DDR和Rambus内存过渡。但是由于DDR内存是在SDRAM基础上发展起来的,所以详细了解SDRAM内存的接口和主板设计方法对于设计基于DDR内存的主板不无裨益。下面我们就从内存颗粒、内存槽位接口、主板和内存之间的信号接口几个方面来详细阐述SDRAM内存条和主板内存系统的设计思路。 内存颗粒介绍 对于DRAM(Dynamic Random Access Memory)内存我想凡是对于计算机有所了解的读者都不会陌生。这种类型的内存都是以一个电容是否充有电荷来作为存储状态的标志,电容冲有电荷为状态1,电容没有电荷为状态0。其最大优点是集成度高,容量大,但是其速度相对于SRAM (Static Random Access Memory) 内存来说慢了许多。目前的内存颗粒封装方式有许多种,本文仅仅以大家常见的TSSOP封装的内存颗粒为例子。 其各个管脚的信号定义和我们所使用的DIMM插槽的定义是相同的,对于不同容量的内存,地址信号的位数有所不同。另外一个需要注意的地方就是其供电电路。Vcc和Vss是为内存颗粒中的存储队列供电,而VccQ和VssQ是为内存颗粒中的地址和数据缓冲区供电。两者的作用不同。 我们对内存颗粒关心的问题主要是其颗粒的数据宽度(数据位数)和容量(寻址空间大小)。而对于颗粒自检、颗粒自刷新等等逻辑并不需要特别深入的研究,所以对此我仅仅是一笔带过,如果读者有兴趣的读者可以详细研究内存颗粒的数据手册。虽然内存颗粒有这么多的逻辑命令方式,但是由于目前北桥芯片和内存颗粒的集成度非常高,只要在布线和元器件的选择上严格按照内存规范来设计和制造,需要使用逻辑分析仪来调试电路上的差错的情况比较少,并且在设计过程中尽量避免出现这种情况。 168线DIMM内存插槽的信号定义 我们目前PC和Server使用的内存大都是168 Pins的SDRAM,区别只是其工作频率有的可能是100MHz频率,有的可能是133MHz频率的。但是只要是SDRAM,其DIMM插槽的信号定义是一样的。而这些引脚得定义就是设计内存条和主板所必须遵从的规范。 内存引脚主要分为如下几类:地址引脚、数据引脚(包含校验位引脚)、片选等控制信号、时钟信号。整个内存时序系统就是这些引脚上的信号配合产生。下面的表中就是内存插槽的引脚数量和引脚定义,对于一些没有定义或者是保留以后使用的信号就没有列出来。 符号功能详细描述 DQ [0-63] I/O 数据输入/输出 CB [0-7] I/O ECC内存的ECC校验输入/输出 A [0-13] I/O 地址选择 BA [0-1] Control Bank选择 CS [0-3] Control 片选信号 RAS Control 行地址选择信号 CAS Control 列地址选择信号 DQMB [0-7] Control 数据掩码控制(DQ Mask)高有效* WE Control 写允许信号 CK [0-3] Clock 时钟信号 CKE [0-1] Clock 时钟允许信号** REGE Control 寄存器 (Registered) 允许信号

DDR系列内存详解及硬件设计规范-Michael

D D R 系列系列内存内存内存详解及硬件详解及硬件 设计规范 By: Michael Oct 12, 2010 haolei@https://www.360docs.net/doc/441462966.html,

目录 1.概述 (3) 2.DDR的基本原理 (3) 3.DDR SDRAM与SDRAM的不同 (5) 3.1差分时钟 (6) 3.2数据选取脉冲(DQS) (7) 3.3写入延迟 (9) 3.4突发长度与写入掩码 (10) 3.5延迟锁定回路(DLL) (10) 4.DDR-Ⅱ (12) 4.1DDR-Ⅱ内存结构 (13) 4.2DDR-Ⅱ的操作与时序设计 (15) 4.3DDR-Ⅱ封装技术 (19) 5.DDR-Ⅲ (21) 5.1DDR-Ⅲ技术概论 (21) 5.2DDR-Ⅲ内存的技术改进 (23) 6.内存模组 (26) 6.1内存模组的分类 (26) 6.2内存模组的技术分析 (28) 7.DDR 硬件设计规范 (34) 7.1电源设计 (34) 7.2时钟 (37) 7.3数据和DQS (38) 7.4地址和控制 (39) 7.5PCB布局注意事项 (40) 7.6PCB布线注意事项 (41) 7.7EMI问题 (42) 7.8测试方法 (42)

摘要: 本文介绍了DDR 系列SDRAM 的一些概念和难点,并分别对DDR-I/Ⅱ/Ⅲ的技术特点进行了论述,最后结合硬件设计提出一些参考设计规范。 关键字关键字::DDR, DDR, SDRAM SDRAM SDRAM, , , 内存模组内存模组内存模组, , , DQS DQS DQS, DLL, MRS, ODT , DLL, MRS, ODT , DLL, MRS, ODT Notes : Aug 30, 2010 – Added DDR III and the PCB layout specification - by Michael.Hao

内存芯片参数介绍

内存芯片参数介绍 具体含义解释: 例:SAMSUNG K4H280838B-TCB0 主要含义: 第1位——芯片功能K,代表是内存芯片。 第2位——芯片类型4,代表DRAM。 第3位——芯片的更进一步的类型说明,S代表SDRAM、H代表DDR、G代表SGRAM。 第4、5位——容量和刷新速率,容量相同的内存采用不同的刷新速率,也会使用不同的编号。64、62、63、65、66、67、6A代表64Mbit的容量;28、27、2A代表128Mbit 的容量;56、55、57、5A代表256MBit的容量;51代表512Mbit的容量。 第6、7位——数据线引脚个数,08代表8位数据;16代表16位数据;32代表32位数据;64代表64位数据。 第11位——连线“-”。 第14、15位——芯片的速率,如60为6ns;70为7ns;7B为7.5ns (CL=3);7C 为7.5ns (CL=2) ;80为8ns;10 为10ns (66MHz)。 知道了内存颗粒编码主要数位的含义,拿到一个内存条后就非常容易计算出它的容量。例如一条三星DDR内存,使用18片SAMSUNG K4H280838B-TCB0颗粒封装。颗粒编号第4、5位“28”代表该颗粒是128Mbits,第6、7位“08”代表该颗粒是8位数据带宽,这样我们可以计算出该内存条的容量是128Mbits(兆数位)× 16片/8bits=256MB(兆字节)。 注:“bit”为“数位”,“B”即字节“byte”,一个字节为8位则计算时除以8。关于内存容量的计算,文中所举的例子中有两种情况:一种是非ECC内存,每8片8位数据宽度的颗粒就可以组成一条内存;另一种ECC内存,在每64位数据之后,还增加了8位的ECC 校验码。通过校验码,可以检测出内存数据中的两位错误,纠正一位错误。所以在实际计算容量的过程中,不计算校验位,具有ECC功能的18片颗粒的内存条实际容量按16乘。在购买时也可以据此判定18片或者9片内存颗粒贴片的内存条是ECC内存。 Hynix(Hyundai)现代 现代内存的含义: HY5DV641622AT-36 HY XX X XX XX XX X X X X X XX 1 2 3 4 5 6 7 8 9 10 11 12 1、HY代表是现代的产品 2、内存芯片类型:(57=SDRAM,5D=DDR SDRAM); 3、工作电压:空白=5V,V=3.3V,U=2.5V 4、芯片容量和刷新速率:16=16Mbits、4K Ref;64=64Mbits、8K Ref;65=64Mbits、4K Ref;128=128Mbits、8K Ref;129=128Mbits、4K Ref;256=256Mbits、16K Ref; 257=256Mbits、8K Ref 5、代表芯片输出的数据位宽:40、80、16、32分别代表4位、

4.实例变量和类变量内存分配

实例变量和类变量内存分配 Java向程序员许下一个承诺:无需关心内存回收,java提供了优秀的垃圾回收机制来回收已经分配的内存。大部分开发者肆无忌惮的挥霍着java程序的内存分配,从而造成java程序的运行效率低下! java内存管理分为两方面: 1,内存的分配:指创建java对象时,jvm为该对象在堆内存中所分配的内存空间。 2,内存的回收:指当该java对象失去引用,变成垃圾时,jvm的垃圾回收机制自动清理该对象,并回收该对象占用的内存。 jvm的垃圾回收机制由一条后台线程完成。不断分配内存使得系统中内存减少,从而降低程序运行性能。大量分配内存的回收使得垃圾回收负担加重,降低程序运行性能。 一,实例变量和类变量(静态变量) java程序的变量大体可分为成员变量和局部变量。 其中局部变量有3类:形参、方法内的局部变量、代码块内的局部变量。 局部变量被存储在方法的栈内存中,生存周期随方法或代码块的结束而消亡。 在类内定义的变量被称为成员变量。没使用static修饰的称为成员变量,用static修饰的称为静态变量或类变量。 1.1实例变量和类变量的属性 在同一个jvm中,每个类只对应一个Class对象,但每个类可以创建多个java对象。 【其实类也是一个对象,所有类都是Class实例,每个类初始化后,系统都会为该类创建一个对应的Class实例,程序可以通过反射来获取某个类所对应的Class实例(Person.class 或Class.forName(“Person”))】 因此同一个jvm中的一个类的类变量只需要一块内存空间;但对实例变量而言,该类每创建一次实例,就需要为该实例变量分配一块内存空间。 非静态函数需要通过对象调用,静态函数既可以通过类名调用,也可以通过对象调用,其实用对象调用静态函数,底层还是用类名调用来实现的! 1.2实例变量的初始化时机 对实例变量而言,它属于java对象本身,每次创建java对象时都需要为实例变量分配内存空间,并执行初始化。

内存篇-三个影响内存性能的重要参数

内存篇-三个影响内存性能的重要参数 组装电脑选购内存时,还有一些影响其性能的重要参数需要注意,比如容量、电压和CL 值等。 ◎容量:容量是选购内存时优先考虑的性能指标,因为它代表了内存可以存储数据的多少,通常以GB 为单位。单根内存容量越大则越好。目前市面上主流的内存容量分为单条(容量为2GB、4GB、8GB、16GB)和套装(容量为2×2GB、2×4GB、2×8GB、8×4GB、4×4GB、16×2GB)两种。 ◎工作电压:内存的工作电压是指内存正常工作所需要的电压值,不同类型的内存电压不同,DDR2 内存的工作电压一般在1.8V 左右;DDR3 内存的工作电压一般在1.5V 左右;DDR4 内存的工作电压一般在1.2V 左右。电压越低,对电能的消耗越少,也就更符合目前节能减排的要求。 ◎CL 值:CL(CAS Latency,列地址控制器延迟)是指从读命令有效(在时钟上升沿发出)开始,到输出端可提供数据为止的这一段时间。对于普通用户来说,没必要太过在意CL 值,只需要了解在同等工作频率下,CL 值低的内存更具有速度优势。 小知识: 什么是内存超频?内存超频就是让内存外频运行在比它被设定的更高的速度下。一般情况下,CPU外频与内存外频是一致的,所以在提升CPU外频进行超频时,也必须相应提升内存外频,使之与CPU同频工作。内存超频技术目前在很多DDR4内存中应用,比如金士顿内存的PnP和XMP就是目前使用较多的内存自动超频技术。 CL值的含义 内存CL值通常采用4个数字表示,中间用“-”隔开,以“5-4-4-12”为例,第一个数代表CAS(Column Address Strobe)延迟时间,也就是内存存取数据所需的延迟时间,即通常说的CL值;第二个数代表RAS(Row Address Strobe)-to-CAS延迟,表示内存行地址传输到列地址的延迟时间;第三个数表示RAS Prechiarge延迟(内存行地址脉冲预充电时间);最后一个数则是Act-to-Prechiarge延迟(内存行地址选择延迟)。其中最重要的指标是第一个参数CAS,它代表内存接收到一条指令后要等待多少个时间周期才能执行任务。 1

超频内存时序表

内存时序 一种参数,一般存储在内存条的SPD上。2-2-2-8 4个数字的含义依次为:CAS Latency(简称CL值)内存CAS延迟时间,他是内存的重要参数之一,某些牌子的内存会把CL值印在内存条的标签上。RAS-to-CAS Delay(tRCD),内存行地址传输到列地址的延迟时间。Row-precharge Delay(tRP),内存行地址选通脉冲预充电时间。Row-active Delay(tRAS),内存行地址选通延迟。这是玩家最关注的4项时序调节,在大部分主板的BIOS中可以设定,内存模组厂商也有计划的推出了低于JEDEC认证标准的低延迟型超频内存模组,在同样频率设定下,最低“2-2-2-5”这种序列时序的内存模组确实能够带来比“3-4-4-8”更高的内存性能,幅度在3至5个百分点。 在一些技术文章里介绍内存设置时序参数时,一般数字“A-B-C-D”分别对应的参数是 “CL-tRCD-tRP-tRAS”,现在你该明白“2-3-3-6”是什么意思了吧?!^_^下面就这几个参数及BIOS设置中影响内存性能的其它参数逐一给大家作一介绍: 一、内存延迟时序“CL-tRCD-tRP-tRAS”的设置 首先,需要在BIOS中打开手动设置,在BIOS设置中找到“DRAM Timing Selectable”,BIOS设置中可能出现的其他描述有:Automatic Configuration、DRAM Auto、Timing Selectable、Timing Configuring By SPD等,将其值设为“Menual”(视BIOS的不同可能的选项有:On/Off或Enable/Disable),如果要调整内存时序,应该先打开手动设置,之后会自动出现详细的时序参数列表: Command Per Clock(CPC) 可选的设置:Auto,Enable(1T),Disable(2T)。 Command Per Clock(CPC:指令比率,也有翻译为:首命令延迟),一般还被描述为DRAM Command Rate、CMD Rate等。由于目前的DDR内存的寻址,先要进行P-Bank的选择(通过DIMM上CS片选信号进行),然后才是L-Bank/行激活与列地址的选择。这个参数的含义就是指在P-Bank选择完之后多少时间可以发出具体的寻址的L-Bank/行激活命令,单位是时钟周期。 显然,也是越短越好。但当随着主板上内存模组的增多,控制芯片组的负载也随之增加,过短的命令间隔可能会影响稳定性。因此当你的内存插得很多而出现不太稳定的时间,才需要将此参数调长。目前的大部分主板都会自动设置这个参数。 该参数的默认值为Disable(2T),如果玩家的内存质量很好,则可以将其设置为Enable(1T)。CAS Latency Control(tCL) 可选的设置:Auto,1,1.5,2,2.5,3,3.5,4,4.5。 一般我们在查阅内存的时序参数时,如“3-4-4-8”这一类的数字序列,上述数字序列分别对应的参数是“CL-tRCD-tRP-tRAS”。这个3就是第1个参数,即CL参数。 CAS Latency Control(也被描述为tCL、CL、CAS Latency Time、CAS Timing Delay),CAS latency是“内存读写操作前列地址控制器的潜伏时间”。CAS控制从接受一个指令到执行指令之间的时间。因为CAS主要控制十六进制的地址,或者说是内存矩阵中的列地址,所以它是最为重要的参数,在稳定的前提下应该尽可能设低。 内存是根据行和列寻址的,当请求触发后,最初是tRAS(Activeto Precharge Delay),预充电后,内存才真正开始初始化RAS。一旦tRAS激活后,RAS(Row Address Strobe )开始进行需要数据的寻址。首先是行地址,然后初始化tRCD,周期结束,接着通过CAS访问所需数据的精确十六进制地址。期间从CAS开始到CAS结束就是CAS延迟。所以CAS是找到数据的最后一个步骤,也是内存参数中最重要的。 这个参数控制内存接收到一条数据读取指令后要等待多少个时钟周期才实际执行该指令。同时该参数也决定了在一次内存突发传送过程中完成第一部分传送所需要的时钟周期数。这个参数越小,则内存的速度越快。必须注意部分内存不能运行在较低的延迟,可能会丢失数据,因此在提醒大家把CAS延迟设为2或2.5的同时,如果不稳定就只有进一步提高它了。而且提高延迟能使内存运行在更高的频率,所以需要对内存超频时,应该试着提高CAS延迟。

内存参数

内存 内存的主流品牌 目前市场上的主流品牌有金士顿(Kingston)、金邦(GEIL)、宇瞻(Apacer)、微刚(ADATA)、刚胜(Kingmax)、现代(Nynex)、三星(Samsung)、海盗船(Corsair)、芝奇(G.skill)、OCE、金泰克等。这些内存采用的工艺略有不同,性能上也多少有些差异。 内存的分类 现在市场上内存可以分为两种。 ①SDRAM: SDRAM又称为同步动态存储器,可以与CPU外频同步运作,有PC100、PC133、PC150等规格,目前的SDRAM都是以168Pin DIMM的内存模块出现。 ②DDR SDRAM: DDR是指Double Data Rate,它的传输速率是SDRAM的两倍,DDR标准包括DDR I、DDRII和DDRIII。DDR插槽与SDRAM插槽两侧的线数不同,DDR应用184pins(针脚)。因此,DDR内存和SDRAM的内存不能换插。 DDR I的主要型号有DDR266,工作频率为133MHz;DDR333,工作频率从为166MHz;DDR400,工作频率为200MHz。 现在DDRII正在逐渐占领主流市场,其频率在533MHz以上。从长远来说,DDRII最终会取代DDR 1,但就目前来说,DDRII的优势还不是特别明显,虽然在频率上有很大提高,但是在时间延迟上却长于DDR400,所以目前的DDR400和DDRII(533)性能差不多,除非选择高端的DDR II(800)。 预计DDRIII将在不久的将来正是面世,工作电压将下降,并且将会使用更

新的信号技术,实现更高的宽带,初始频率预计将达到800MHz,甚至更高。 内存的主要性能参数 ①容量 每个时期的内存条的容量都多种规格、例如,早期的30线内存条有256KB、1MB、4MB等容量,后来72线的EDD内存有4MB、8MB、16MB等容量,目前流行的168线SDRAM内存常见的内存容量有32MB、64MB、128MB、256MB、512MB、1GB等。 数据带宽 数据带宽指内存的数据传输速度,是衡量内存性能的重要指标。PCI00 SDRAM在额定频率(100MHz)下工作时,其峰值数据传输速度可以达到800MB/s。而PCI33SDRAM其峰值数据传输速度可达1.06GB/s,比PCI00内存提高了200MB/s。对于DDR DRAM,由于在同一个时钟周期的上升和下降沿都能传输数据,所以工作在133MHz时,实际传输速度可达2.1GB/s。 ②时钟周期 时钟周期代表了SDRAM所能运行的最大频率。显然,这个数字越小,说明SDRAM芯片所能运行的频率越高。对于一普通的PC 100 SDRAM来说,它芯片上的标识“-10”代表了它运行的时钟周期为10ns,即可以在100MHz的外频下正常工作。为什么说SDRAM 的时钟周期代表可它能运行的最大频率呢?SDRAM时钟周期的单位是ns(纳秒),而其最大工作频率则为MHz(兆赫兹),这两者有何关联呢?两者的关系其实很简单,遵循了“频率=1/周期”的原理。由于ns时10-9秒,而MHz是106Hz,因为以ns为单位的周期数值与以MHz为单位的频率数值的乘积应为1 000。所以说时钟周期为10ns的SDRAM可以在100MHz的外频下工作。根据同样的道理,我们可以算出各个时钟周期下的

DDR内存时序设置详解

内存时序设置详解 内容概要 关键词:内存时序参数设置 导言:是否正确地设置了内存时序参数,在很大程度上决定了系统的基本性能。本文详细介绍了内存时序相关参数的基本涵义及设置要点。 与传统的SDRAM相比,DDR(Dual date rate SDRSM:双倍速率SDRAM),最重要的改变是在界面数据传输上,其在时钟信号上升缘与下降缘时各传输一次数据,这使得DDR 的数据传输速率为传统SDRAM的两倍。同样地,对于其标称的如DDR400,DDR333,DDR266数值,代表其工作频率其实仅为那些数值的一半,也就是说DDR400 工作频率为200MHz。 FSB与内存频率的关系 首先请大家看看FSB(Front Side Bus:前端总线)和内存比率与内存实际运行频率的关系。 FSB/MEM比率实际运行频率 1/1 200MHz 1/2 100MHz 2/3 133MHz 3/4 150MHz 3/05 120MHz 5/6 166MHz 7/10 140MHz 9/10 180MHz 对于大多数玩家来说,FSB和内存同步,即1:1是使性能最佳的选择。而其他的设置都是异步的。同步后,内存的实际运行频率是FSBx2,所以,DDR400的内存和200MHz的FSB正好同步。如果你的FSB为240MHz,则同步后,内存的实际运行频率为240MHz x 2 = 480MHz。

FSB与不同速度的DDR内存之间正确的设置关系 强烈建议采用1:1的FSB与内存同步的设置,这样可以完全发挥内存带宽的优势。内存时序设置 内存参数的设置正确与否,将极大地影响系统的整体性能。下面我们将针对内存关于时序设置参数逐一解释,以求能让大家在内存参数设置中能有清晰的思路,提高电脑系统的性能。 涉及到的参数分别为: ?CPC : Command Per Clock ?tCL : CAS Latency Control ?tRCD : RAS to CAS Delay ?tRAS : Min RAS Active Timing ?tRP : Row Precharge Timing ?tRC : Row Cycle Time ?tRFC : Row Refresh Cycle Time ?tRRD : Row to Row Delay(RAS to RAS delay) ?tWR : Write Recovery Time ?……及其他参数的设置 CPC : Command Per Clock 可选的设置:Auto,Enable(1T),Disable(2T)。 Command Per Clock(CPC:指令比率,也有翻译为:首命令延迟),一般还被描述为DRAM Command Rate、CMD Rate等。由于目前的DDR内存的寻址,先要进行P-Bank的选择(通过DIMM上CS片选信号进行),然后才是L-Bank/行激活与列地址的选择。这个参数的含义就是指在P-Bank选择完之后多少时间可以发出具体的寻址的L-Bank/行激活命令,单位是时钟周期。

变量名有两个重要属性数据类型和组织结构数据类型指出属于数据

IDL中的变量类型 变量名有两个重要属性:数据类型和组织结构。数据类型指出属于数据类型中的哪一种。在IDL中有14种基本数据类型。在图表1中将看到每一种数据类型,每个类型创建的变量的字节大小,变量创建方式,数据类型之间强制转换的IDL函数名称。除了数据类型外,一个变量有一个组织结构。有效的组织结构有标量(例如单个数值)、矢量(真正的一维数组)、数组(最高可达8维)和IDL结构(能包含各种数据类型的变量和组织结构,结构中独立的组成部分称为字段)。 数据类型字节数创建变量数据类型函数 字节型 1 Var=0B thisVar=Byte(variab le) 16位有符号整 型2 Var=0 thisVar=Fix(variabl e) 32位有符号长 整型4 Var=0L thisVar=Long(variab le) 64位有符号整 型8 Var=0LL thisVar=Long64(vari able) 16位无符号整 型2 Var=0U thisVar=UInt(variab le) 32位无符号长 4 Var=0UL thisVar=ULong(varia

整型ble) 64位无符号整 型8 Var=0ULL thisVar=Ulong64(var iable) 浮点型 4 Var=0.0 thisVar=Float(varia ble) 双精度浮点型8 Var=0.0D thisVar=Double(vari able) 复数8 Var=Complex(0.0 ,0.0) thisVar=Complex(var iable) 双精度复数16 Var=Dcomplex(0. 0D,0.0D) thisVar=DComplex(va riable) 字符串 0-3276 7 Var=’’或Var=”” thisVar=String(vari able) 指针 4 Var=Ptr_New() None 对象 4 Var=Obj_New() None 表1:IDL中的14种基本数据类型。表中显示了每种数据类型的字节数,创建变量的方法,用语数据类型之间强制转换的IDL函数 数据类型初始化函数产生索引值的函数 字节型BytArr BIndGen 16位有符号整型IntArr IndGen

内存规格参数

内存规格参数 内存这样小小的一个硬件,却是PC系统中最必不可少的重要部件之一。而对于入门用户来说,可能从内存的类型、工作频率、接口类型这些简单的参数的印象都可能很模糊的,而对更深入的各项内存时序小参数就更摸不着头脑了。而对于进阶玩家来说,内存的一些具体的细小参数设置则足以影响到整套系统的超频效果和最终性能表现。如果不想当菜鸟的话,虽然不一定要把各种参数规格一一背熟,但起码有一个基本的认识,等真正需要用到的时候,查起来也不会毫无概念。 内存种类 目前,桌面平台所采用的内存主要为DDR 1、DDR 2和DDR 3三种,其中DDR1内存已经基本上被淘汰,而DDR2和DDR3是目前的主流。 DDR1内存 第一代DDR内存 DDR SDRAM 是 Double Data Rate SDRAM的缩写,是双倍速率同步动态随机存储器的意思。DDR内存是在SDRAM内存基础上发展而来的,仍然沿用SDRAM生产体系,因此对于内存厂商而言,只需对制造普通SDRAM 的设备稍加改进,即可实现DDR内存的生产,可有效的降低成本。 DDR2内存

第二代DDR内存 DDR2 是 DDR SDRAM 内存的第二代产品。它在 DDR 内存技术的基础上加以改进,从而其传输速度更快(可达800MHZ ),耗电量更低,散热性能更优良。 DDR3内存 第三代DDR内存 DDR3相比起DDR2有更低的工作电压,从DDR2的1.8V降落到1.5V,性能更好更为省电;DDR2的4bit 预读升级为8bit预读。DDR3目前最高能够1600Mhz的速度,由于目前最为快速的DDR2内存速度已经提升到800Mhz/1066Mhz的速度,因而首批DDR3内存模组将会从1333Mhz的起跳。

SDRAM时序控制

SDRAM的时序控制 一、SDRAM的外在物理结构 (1)P-Bank 为保证CPU的正常工作,SDRAM必须一次传输完CPU在一个传输周期内所需要的数据量,也就是CPU数据总线的位宽(bit),这个位宽也就是物理Bank(Physical Bank, P-Bank)的位宽,所以内存需要组成P-Bank来与CPU打交道。 (2)芯片位宽与芯片数量 然而每个内存芯片都有自己的位宽,即每个传输周期能提供的数据量。由于技术要求、成本和实用性等方面限制,内存芯片的位宽一般都小于P-Bank的位宽,这就需要多颗内存芯片并联工作,以提供CPU正常工作时一个传输周期内所需要的数据量。所以,P-Bank实际上就是一组内存芯片的集合,这个集合的位宽总和=P-Bank的位宽=CPU数据位宽,但这个集合的数据容量没有限制。 一个SDRAM只有一个P-Bank已经不能满足容量的需要,所以,多个芯片组可以支持多个P-Bank,一次选择一个P-Bank工作。 (3)SDRAM的封装 SIMM: Single In-line Memory Module,单列内存模组,内存模组就是我们常说的内存条,所谓单列是指模组电路板与主板插槽的接口只有一列引脚(虽然两侧都有金手指pin)DIMM: Double In-line Memory Module, 双列内存模组,所谓双列是指模组电路板与主板插槽的接口有两列引脚,模组电路板的每侧金手指对应一列引脚。 DIMM是SDRAM集合形式的最终体现。前文讲过P-Bank对芯片集合的位宽有要求,对芯片集合的容量则没有任何限制。高位宽的芯片可以让DIMM的设计简单一些(因为所用的芯片少),但在芯片容量相同时,这种DIMM的容量就肯定比不上采用低位宽芯片的模组,因为后者在一个P-Bank中可以容纳更多的芯片。 SDRAM的引脚与封装: 二、SDRAM内部逻辑结构 (1)L-Bank SDRAM的内部实际上是一个存储阵列,就如同表格一样,而每个单元格就称为存储单元,这张表格就成为逻辑Bank(Logical Bank, L-Bank)。考虑到技术、成本、执行效率等方面原因,不可能只需要一个全容量的L-Bank,所以人们在SDRAM内部分割多个L-Bank,目前基本都是4个,内存访问时,一次只能是一个L-Bank。

教你看懂内存编码

教你看懂内存编码! 内存大小识别方法(详) 内存芯片如按厂家所属地域来分主要有日,韩厂家,欧美及中国(含台湾省)厂家等等。看编号识内存芯片是了解内存的一个好方法,下面就是内存识别资料,供大家参考: 主要的内存芯片厂商的名称既芯片代号如下: 现代电子HYUNDAI:HY[注:代号] 三星SAMSUNG:KM或M NBM:AAA 西门子SIEMENS:HYB 高士达LG-SEMICON:GM HITSUBISHI:M5M 富士通FUJITSU:MB 摩托罗拉MOTOROLA:MCM MATSUSHITA:MN OKI:MSM 美凯龙MICRON:MT 德州仪器TMS:TI 东芝TOSHIBA:TD 或TC 日立HITACHI:HM STI:TM 日电NEC:uPD IBM:BM NPNX:NN 一.日本产系列: 主要厂家有Hitachi[日立],Toshiba[东芝],NEC[日电],Mitsubishi [三菱]等等,日产晶圆的特点是品质不错,价格稍高。 1.HITACHI[日立]。1 日立内存质量不错,许多PC100的皆可稳上133MHz。它的稳定性好,做工精细,日立内存芯片的编号有HITACHI HM521XXXXXCTTA60或B60,区别是A60的CL是2,B60的CL是3。市面上B60的多,但完全可超133MHz外频, HITACHI的SDRAM芯片上的标识为以下格式: HM 52 XX XX 5 X X TT-XX HM代表是日立的产品,52是SDRAM,如为51则为EDO DRAM。 第1、2个X代表容量。 第3、4个X表示数据位宽,40、80、16分别代表4位、8位、16位。 第5个X表示是第几个版本的内核,现在至少已经排到"F"了。 第6个X如果是字母"L"就是低功耗。空白则为普通。 TT为TSOII封装。 最后XX代表速度: 75:7.5ns[133MHz] 80:8ns[125MHz] A60:10ns[PC-100 CL2或3] B60:10ns[PC-100 CL3] 例如:HM5264805F-B60,是64Mbit,8位输出,100MHZ时CL是3。 2.NEC。 NEC的SDRAM芯片上的标识通常为以下格式: μPD45 XX X X XG5-AXX X-XXX

内存的时序以及内存时序优化

一种参数,一般存储在内存条的SPD上。2-2-2-8 4个数字的含义依次为:CAS Latency(简称CL值)内存CAS延迟时间,他是内存的重要参数之一,某些牌子的内存会把CL值印在内存条的标签上。RAS-to-CAS Delay(tRCD),内存行地址传输到列地址的延迟时间。Row-precharge Delay(tRP),内存行地址选通脉冲预充电时间。Row-active Delay(tRAS),内存行地址选通延迟。这是玩家最关注的4项时序调节,在大部分主板的BIOS中可以设定,内存模组厂商也有计划的推出了低于JEDEC认证标准的低延迟型超频内存模组,在同样频率设定下,最低“2-2-2-5”这种序列时序的内存模组确实能够带来比“3-4-4-8”更高的内存性能,幅度在3至5个百分点。 在一些技术文章里介绍内存设置时序参数时,一般数字“A-B-C-D”分别对应的参数是“CL-tRCD-tRP-tRAS”,现在你该明白“2-3-3-6”是什么意思了吧?!^_^下面就这几个参数及BIOS设置中影响内存性能的其它参数逐一给大家作一介绍: 一、内存延迟时序“CL-tRCD-tRP-tRAS”的设置 首先,需要在BIOS中打开手动设置,在BIOS设置中找到“DRAM Timing Selectable”,BIOS设置中可能出现的其他描述有:Automatic Configuration、DRAM Auto、Timing Selectable、Timing Configuring By SPD等,将其值设为“Menual”(视BIOS的不同可能的选项有:On/Off 或Enable/Disable),如果要调整内存时序,应该先打开手动设置,之后会自动出现详细的时序参数列表: Command Per Clock(CPC) 可选的设置:Auto,Enable(1T),Disable(2T)。 Command Per Clock(CPC:指令比率,也有翻译为:首命令延迟),一般还被描述为DRAM Command Rate、CMD Rate等。由于目前的DDR内存的寻址,先要进行P-Bank的选择(通过DIMM上CS片选信号进行),然后才是L-Bank/行激活与列地址的选择。这个参数的含义就是指在P-Bank选择完之后多少时间可以发出具体的寻址的L-Bank/行激活命令,单位是时钟周期。 显然,也是越短越好。但当随着主板上内存模组的增多,控制芯片组的负载也随之增加,过短的命令间隔可能会影响稳定性。因此当你的内存插得很多而出现不太稳定的时间,才需要将此参数调长。目前的大部分主板都会自动设置这个参数。 该参数的默认值为Disable(2T),如果玩家的内存质量很好,则可以将其设置为Enable(1T)。 CAS Latency Control(tCL) 可选的设置:Auto,1,1.5,2,2.5,3,3.5,4,4.5。 一般我们在查阅内存的时序参数时,如“3-4-4-8”这一类的数字序列,上述数字序列分别对应的参数是“CL-tRCD-tRP-tRAS”。这个3就是第1个参数,即CL参数。 CAS Latency Control(也被描述为tCL、CL、CAS Latency Time、CAS Timing Delay),CAS latency 是“内存读写操作前列地址控制器的潜伏时间”。CAS控制从接受一个指令到执行指令之间的时间。因为CAS主要控制十六进制的地址,或者说是内存矩阵中的列地址,所以它是最为重要的参数,在稳定的前提下应该尽可能设低。 内存是根据行和列寻址的,当请求触发后,最初是tRAS(Activeto Precharge Delay),预充电后,内存才真正开始初始化RAS。一旦tRAS激活后,RAS(Row Address Strobe )开始进行需要数据的寻址。首先是行地址,然后初始化tRCD,周期结束,接着通过CAS访问所需数据的精确十六进制地址。期间从CAS开始到CAS结束就是CAS延迟。所以CAS是找到数据的最后一个步骤,也是内存参数中最重要的。 这个参数控制内存接收到一条数据读取指令后要等待多少个时钟周期才实际执行该指令。同时该参数也决定了在一次内存突发传送过程中完成第一部分传送所需要的时钟周期数。这个参数越小,则内存的速度越快。必须注意部分内存不能运行在较低的延迟,可能会丢失